Lecture 5 FAN and SOCRATES FAN Multiple Backtrace

Lecture 5 FAN and SOCRATES § § § FAN – Multiple Backtrace (1983) SOCRATES – Learning (1988) Test Generation Systems Test Compaction Summary Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 1

FAN -- Fujiwara and Shimono (1983) § New concepts: § Immediate assignment of uniquely- § § § determined signals Unique sensitization Stop Backtrace at head lines Multiple Backtrace Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 2

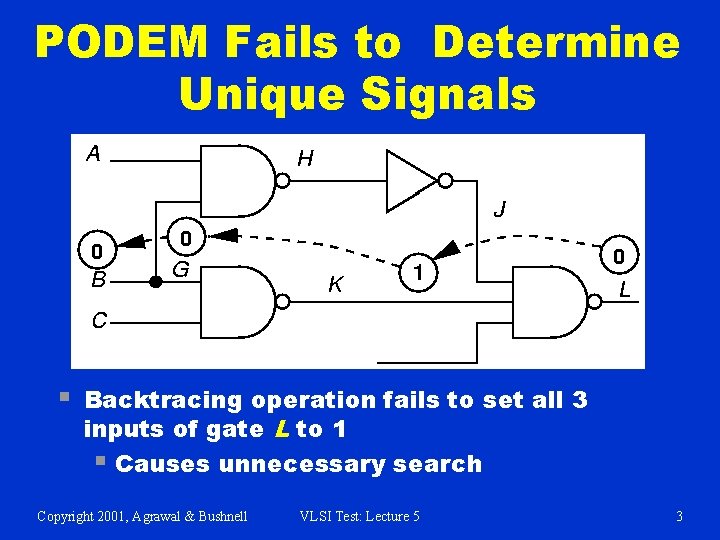

PODEM Fails to Determine Unique Signals § Backtracing operation fails to set all 3 inputs of gate L to 1 § Causes unnecessary search Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 3

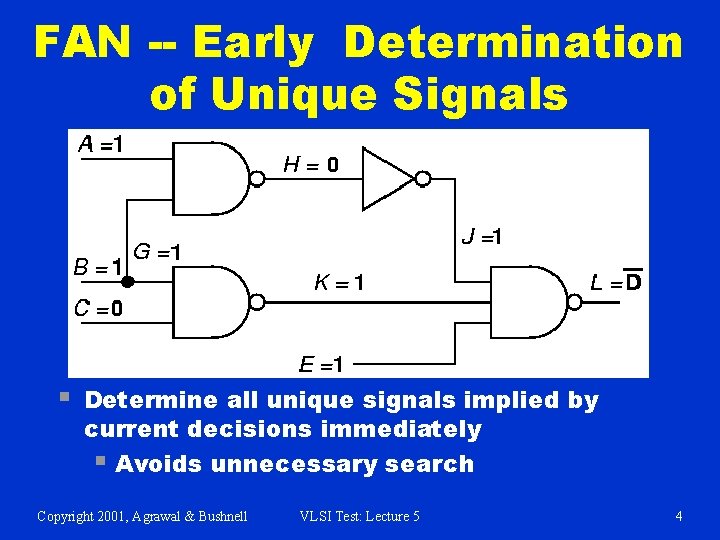

FAN -- Early Determination of Unique Signals § Determine all unique signals implied by current decisions immediately § Avoids unnecessary search Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 4

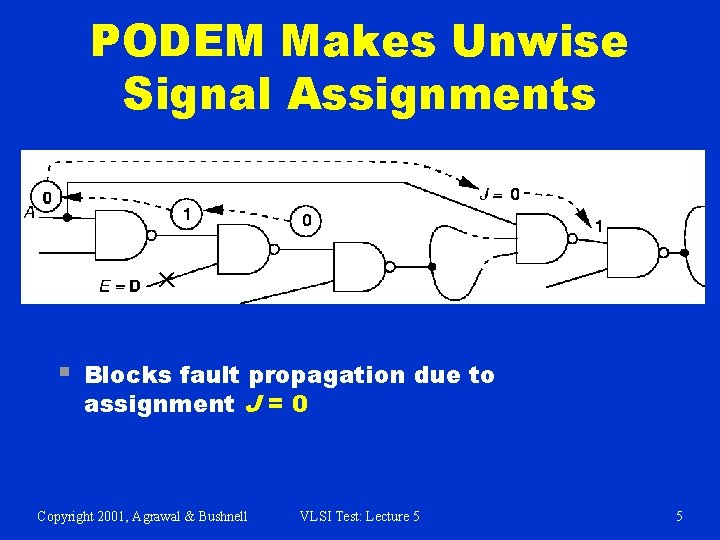

PODEM Makes Unwise Signal Assignments § Blocks fault propagation due to assignment J = 0 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 5

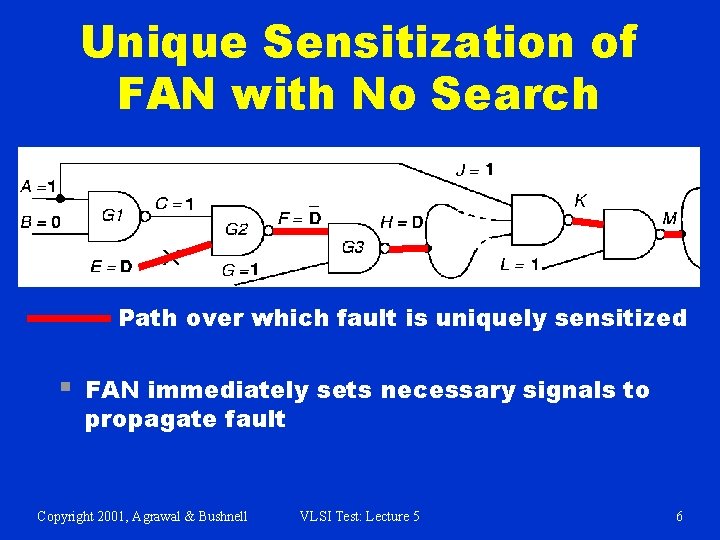

Unique Sensitization of FAN with No Search Path over which fault is uniquely sensitized § FAN immediately sets necessary signals to propagate fault Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 6

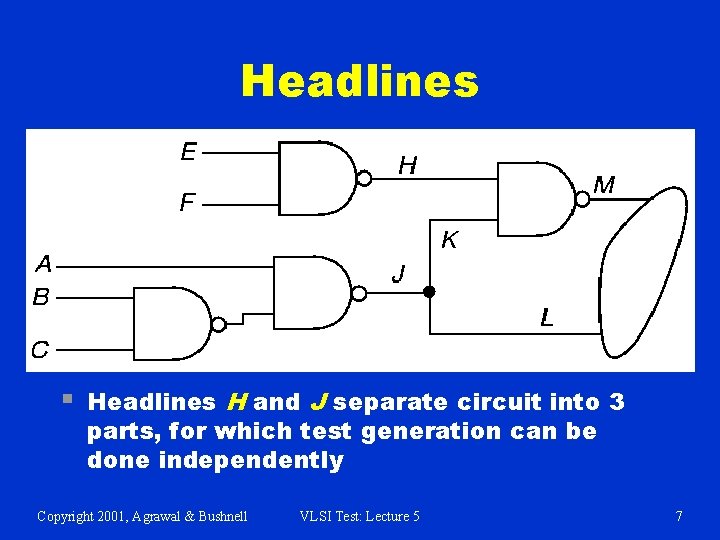

Headlines § Headlines H and J separate circuit into 3 parts, for which test generation can be done independently Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 7

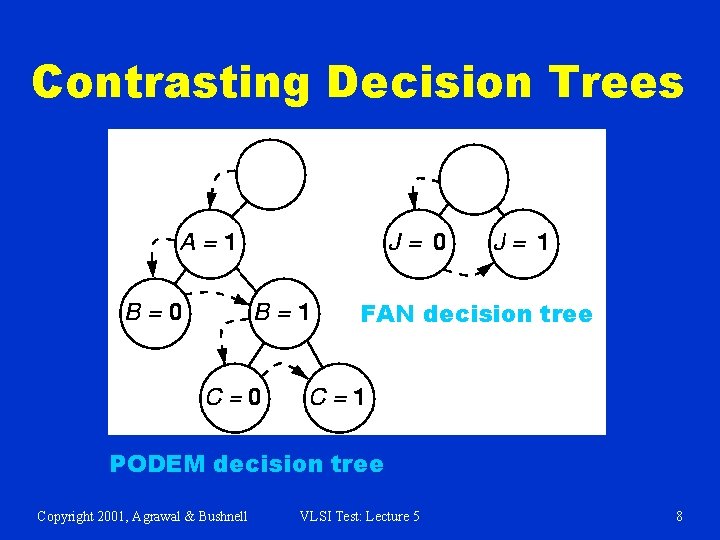

Contrasting Decision Trees FAN decision tree PODEM decision tree Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 8

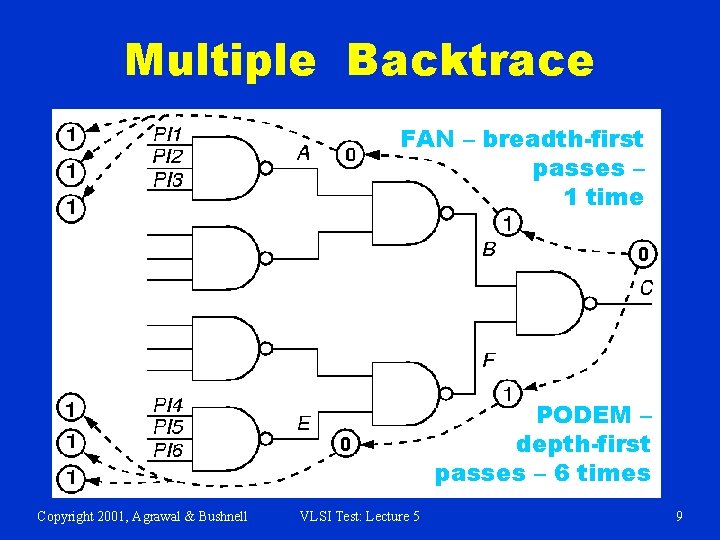

Multiple Backtrace FAN – breadth-first passes – 1 time PODEM – depth-first passes – 6 times Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 9

![AND Gate Vote Propagation [5, 3] [0, 3] § AND Gate § Easiest-to-control Input AND Gate Vote Propagation [5, 3] [0, 3] § AND Gate § Easiest-to-control Input](http://slidetodoc.com/presentation_image_h2/e54263c962f7610fbb1d763c9c35b992/image-10.jpg)

AND Gate Vote Propagation [5, 3] [0, 3] § AND Gate § Easiest-to-control Input – § # 0’s = OUTPUT # 0’s § # 1’s = OUTPUT # 1’s § All other inputs -- § # 0’s = 0 § # 1’s = OUTPUT # 1’s Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 10

![Multiple Backtrace Fanout Stem Voting [5, 1] [1, 1] [3, 2] [18, 6] [4, Multiple Backtrace Fanout Stem Voting [5, 1] [1, 1] [3, 2] [18, 6] [4,](http://slidetodoc.com/presentation_image_h2/e54263c962f7610fbb1d763c9c35b992/image-11.jpg)

Multiple Backtrace Fanout Stem Voting [5, 1] [1, 1] [3, 2] [18, 6] [4, 1] [5, 1] § Fanout Stem -- § # 0’s = S Branch # 0’s, § # 1’s = S Branch # 1’s Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 11

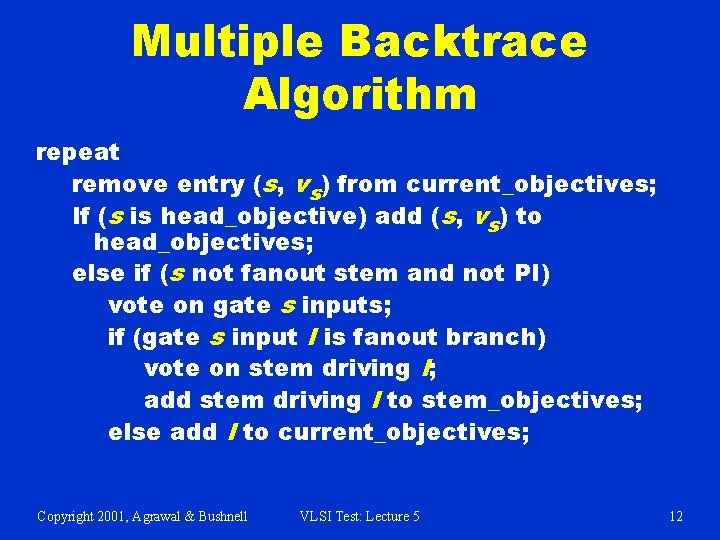

Multiple Backtrace Algorithm repeat remove entry (s, vs) from current_objectives; If (s is head_objective) add (s, vs) to head_objectives; else if (s not fanout stem and not PI) vote on gate s inputs; if (gate s input I is fanout branch) vote on stem driving I; add stem driving I to stem_objectives; else add I to current_objectives; Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 12

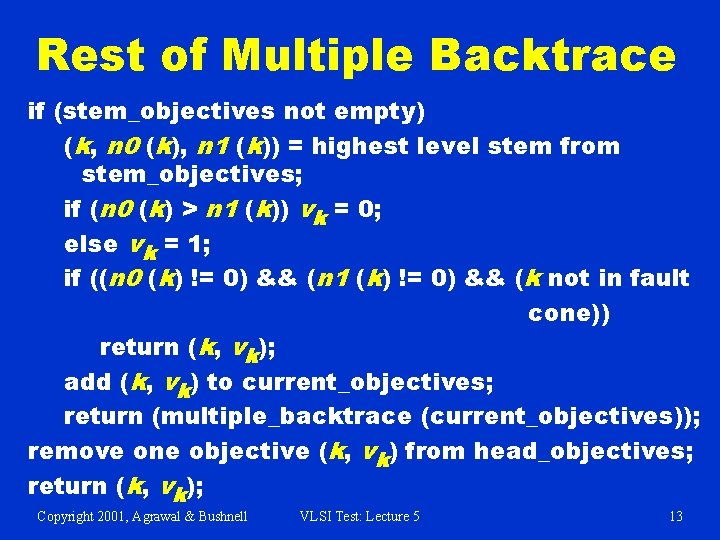

Rest of Multiple Backtrace if (stem_objectives not empty) (k, n 0 (k), n 1 (k)) = highest level stem from stem_objectives; if (n 0 (k) > n 1 (k)) vk = 0; else vk = 1; if ((n 0 (k) != 0) && (n 1 (k) != 0) && (k not in fault cone)) return (k, vk); add (k, vk) to current_objectives; return (multiple_backtrace (current_objectives)); remove one objective (k, vk) from head_objectives; return (k, vk); Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 13

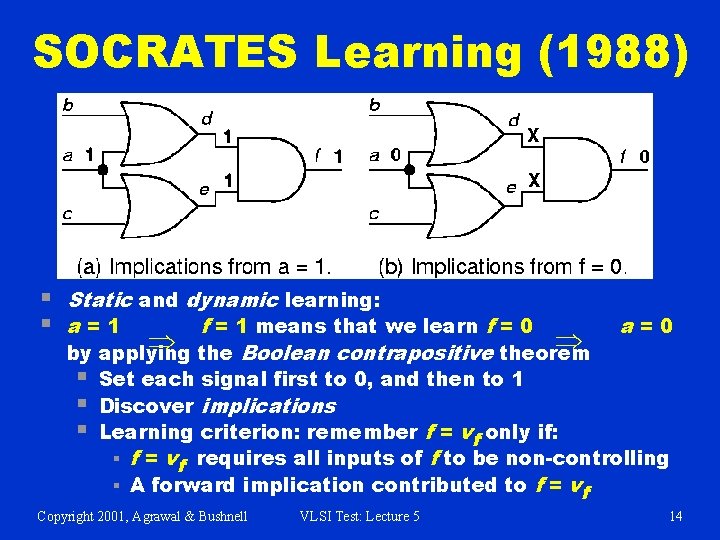

SOCRATES Learning (1988) § § Static and dynamic learning: a=1 f = 1 means that we learn f = 0 Þ Þ the Boolean contrapositive theorem by applying § § § a=0 Set each signal first to 0, and then to 1 Discover implications Learning criterion: remember f = vf only if: § f = vf requires all inputs of f to be non-controlling § A forward implication contributed to f = vf Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 14

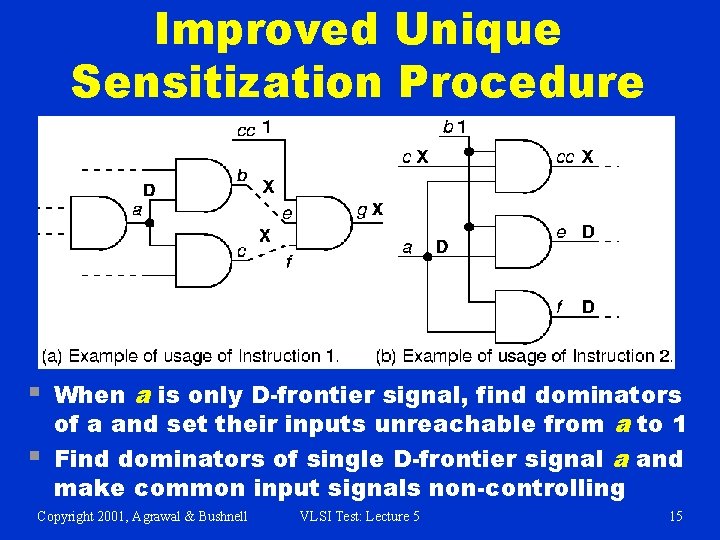

Improved Unique Sensitization Procedure § § When a is only D-frontier signal, find dominators of a and set their inputs unreachable from a to 1 Find dominators of single D-frontier signal a and make common input signals non-controlling Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 15

![Constructive Dilemma § [(a = 0) (i = 0)] [(a = 1) (i = Constructive Dilemma § [(a = 0) (i = 0)] [(a = 1) (i =](http://slidetodoc.com/presentation_image_h2/e54263c962f7610fbb1d763c9c35b992/image-16.jpg)

Constructive Dilemma § [(a = 0) (i = 0)] [(a = 1) (i = 0)] (i = 0) Þ Ù Þ Þ § If both assignments 0 and 1 to a make i = 0, then i = 0 is implied independently of a Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 16

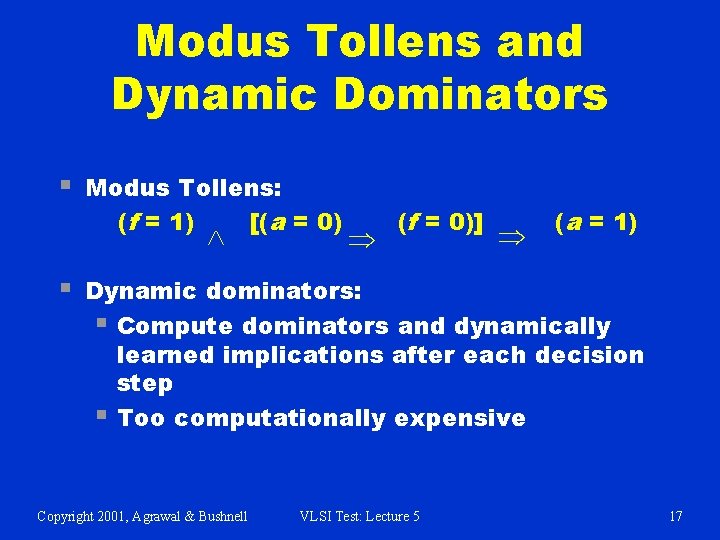

Modus Tollens and Dynamic Dominators § Modus Tollens: (f = 1) [(a = 0) Ù § Þ (f = 0)] Þ (a = 1) Dynamic dominators: § Compute dominators and dynamically learned implications after each decision step § Too computationally expensive Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 17

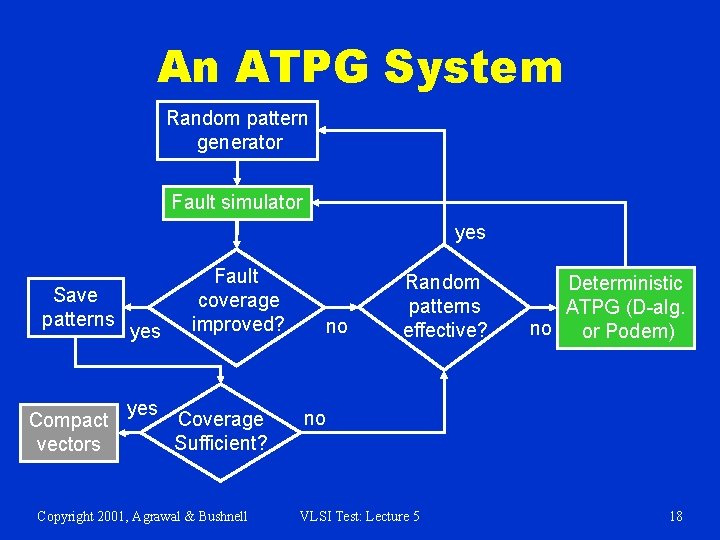

An ATPG System Random pattern generator Fault simulator yes Save patterns Compact vectors yes Fault coverage improved? Coverage Sufficient? Copyright 2001, Agrawal & Bushnell no Random patterns effective? Deterministic ATPG (D-alg. no or Podem) no VLSI Test: Lecture 5 18

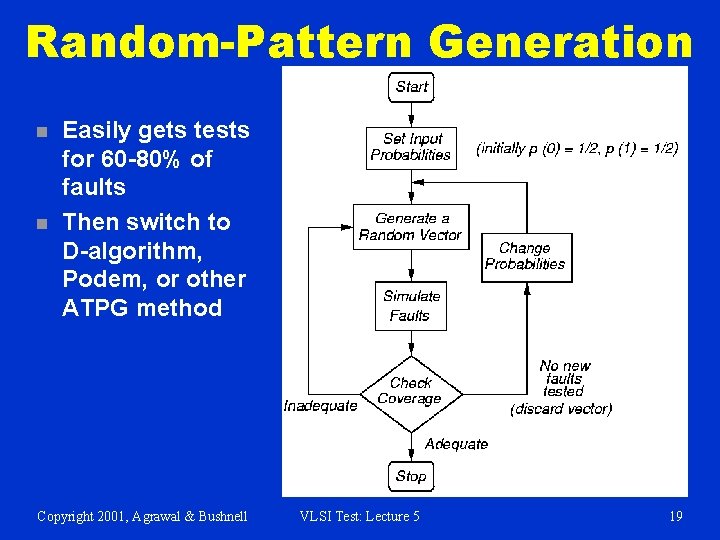

Random-Pattern Generation n n Easily gets tests for 60 -80% of faults Then switch to D-algorithm, Podem, or other ATPG method Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 19

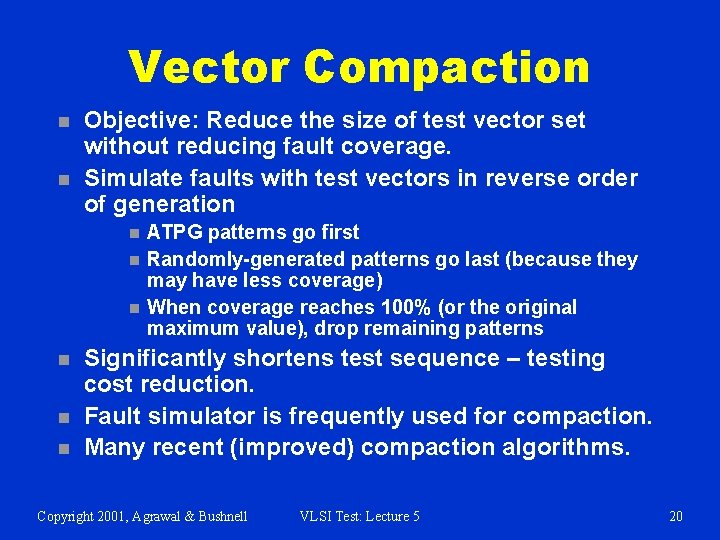

Vector Compaction n n Objective: Reduce the size of test vector set without reducing fault coverage. Simulate faults with test vectors in reverse order of generation n n n ATPG patterns go first Randomly-generated patterns go last (because they may have less coverage) When coverage reaches 100% (or the original maximum value), drop remaining patterns Significantly shortens test sequence – testing cost reduction. Fault simulator is frequently used for compaction. Many recent (improved) compaction algorithms. Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 20

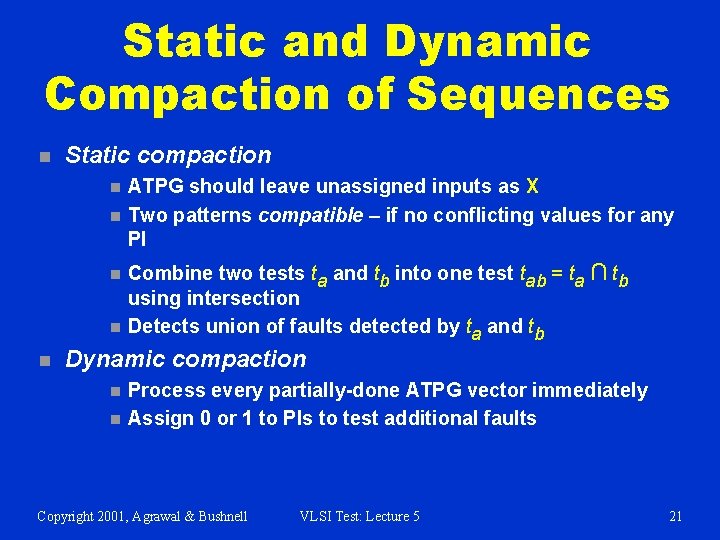

Static and Dynamic Compaction of Sequences n Static compaction n n ATPG should leave unassigned inputs as X Two patterns compatible – if no conflicting values for any PI Combine two tests ta and tb into one test tab = ta ∩ tb using intersection Detects union of faults detected by ta and tb Dynamic compaction n n Process every partially-done ATPG vector immediately Assign 0 or 1 to PIs to test additional faults Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 21

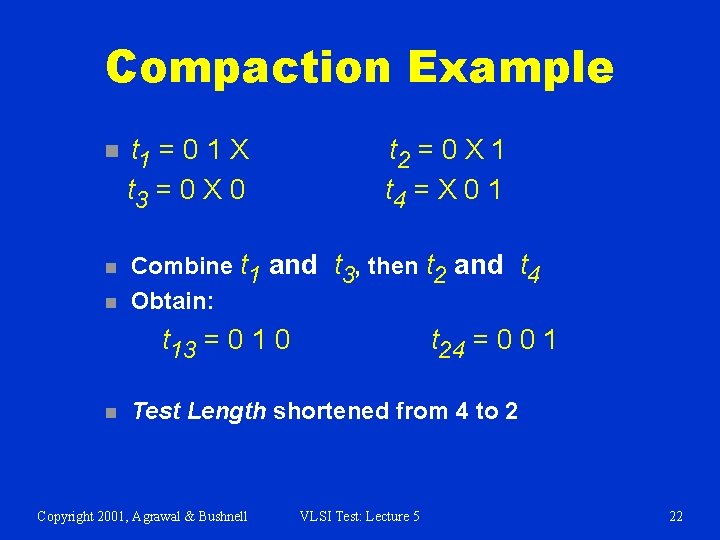

Compaction Example n t 1 =01 X t 3 = 0 X 0 n n t 2 = 0 X 1 t 4 = X 0 1 Combine t 1 and t 3, then t 2 and t 4 Obtain: t 13 = 0 1 0 n t 24 = 0 0 1 Test Length shortened from 4 to 2 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 22

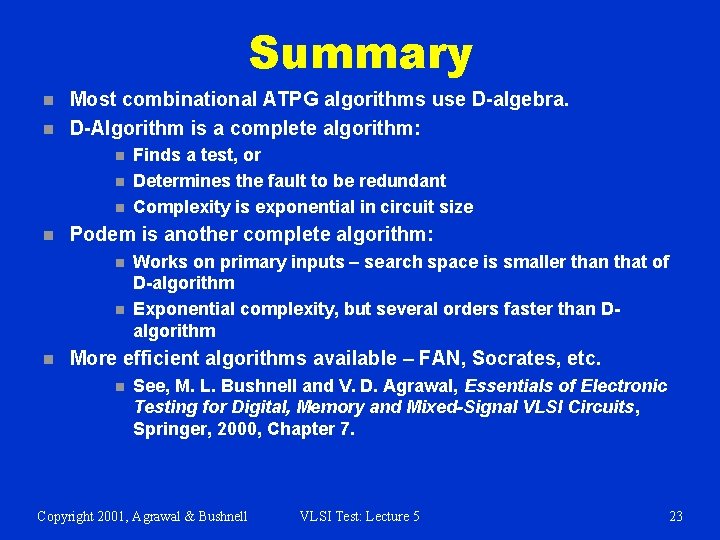

Summary n n Most combinational ATPG algorithms use D-algebra. D-Algorithm is a complete algorithm: n n Podem is another complete algorithm: n n n Finds a test, or Determines the fault to be redundant Complexity is exponential in circuit size Works on primary inputs – search space is smaller than that of D-algorithm Exponential complexity, but several orders faster than Dalgorithm More efficient algorithms available – FAN, Socrates, etc. n See, M. L. Bushnell and V. D. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, Springer, 2000, Chapter 7. Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 5 23

- Slides: 23