Lecture 23 Switch Mode Power Supplies Pulse Width

- Slides: 24

Lecture 23 • Switch Mode Power Supplies • Pulse Width Modulation – What is PWM – Why PWM? – When to PWM? – CPU controlled PWM SMPS • Design idea: Using the ATMEGA 128 PWM to make an efficient SMPS.

Simple DC-DC Converter Topologies Buck Converter or Step Down Converter Boost Converter or Step Up converter Buck-Boost Converter

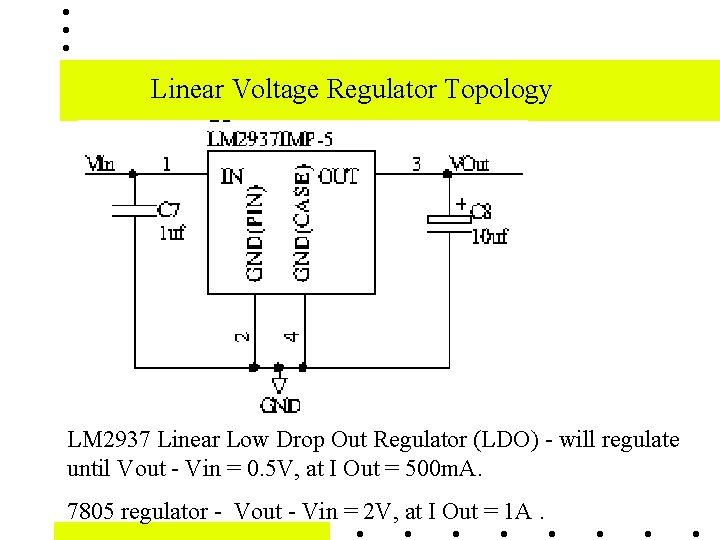

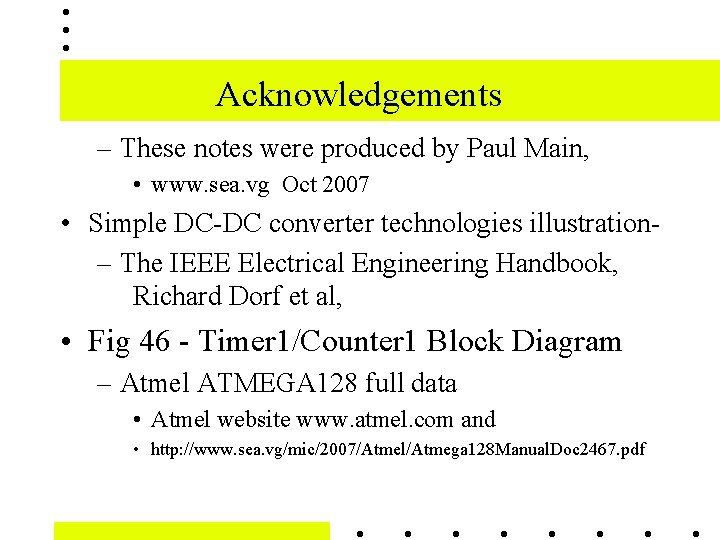

Linear Voltage Regulator Topology LM 2937 Linear Low Drop Out Regulator (LDO) - will regulate until Vout - Vin = 0. 5 V, at I Out = 500 m. A. 7805 regulator - Vout - Vin = 2 V, at I Out = 1 A.

Why Pulse Width Modulation? • Doesn’t the design complexity of a SMPS counter any benefits in power efficiency? • What about all that electromagnetic noise? • Don’t you need to follow very careful circuit layout to achieve a good low noise design? • Do switch mode converters fail more than linear converters?

Higher Efficiency • A linear voltage regulator may typically achieve an efficiency of 50% to 65%. • A Switch-Mode Power Supply (SMPS) regulator typically achieves an efficiency of 75% to 95%.

SMPS benefits – Very wide input voltage range. • For example: most personal computer power supplies are SMPSs - accepting AC input 90 V to 250 V. – Lower Quiescent Current than linear regulators – Less heat than an equivalent linear regulator. • Much Lower Green House Gas emissions – Overall Smaller geometry components are used – Lighter Weight – Lower running cost - Lower total cost of ownership (TCO). – Battery operated devices - longer lifetime.

SMPS disadvantages – Significant Output Ripple • May need a post filter to decrease ripple • May need a secondary linear low drop out regulator to ensure damaging voltage transients keep away from voltage sensitive elements - electronics. • An SMPS May add too much cost. – How much is too much?

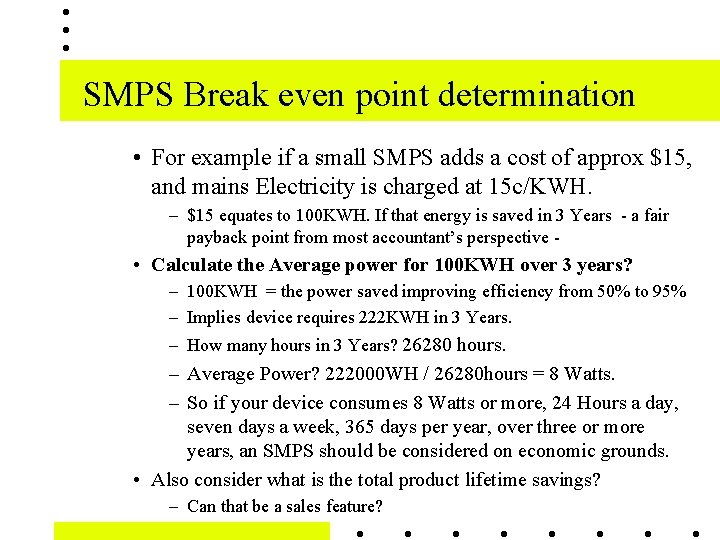

SMPS Break even point determination • For example if a small SMPS adds a cost of approx $15, and mains Electricity is charged at 15 c/KWH. – $15 equates to 100 KWH. If that energy is saved in 3 Years - a fair payback point from most accountant’s perspective - • Calculate the Average power for 100 KWH over 3 years? – 100 KWH = the power saved improving efficiency from 50% to 95% – Implies device requires 222 KWH in 3 Years. – How many hours in 3 Years? 26280 hours. – Average Power? 222000 WH / 26280 hours = 8 Watts. – So if your device consumes 8 Watts or more, 24 Hours a day, seven days a week, 365 days per year, over three or more years, an SMPS should be considered on economic grounds. • Also consider what is the total product lifetime savings? – Can that be a sales feature?

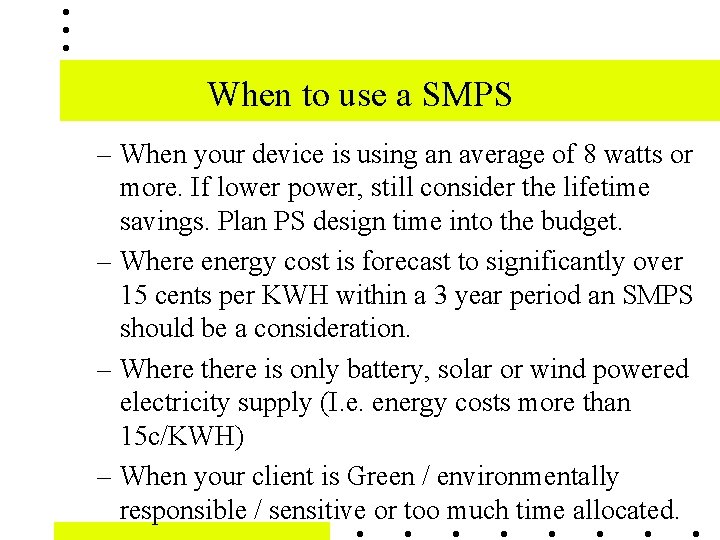

When to use a SMPS – When your device is using an average of 8 watts or more. If lower power, still consider the lifetime savings. Plan PS design time into the budget. – Where energy cost is forecast to significantly over 15 cents per KWH within a 3 year period an SMPS should be a consideration. – Where there is only battery, solar or wind powered electricity supply (I. e. energy costs more than 15 c/KWH) – When your client is Green / environmentally responsible / sensitive or too much time allocated.

When not to use a SMPS • An SMPS May be totally un-neccessary – For power requirements - micro amps to pico amps - an ultra low power linear regulator would be a better choice. • In some battery powered systems, no regulation may be acceptable if the working range of the semiconductors is chosen carefully. (Eg 2 x. AA / CR 2032 battery systems) • Particularly cost sensitive clients may not appreciate their time spent on something they see as costly - use your judgement - the world has limited resources • Initial Prototyping of RF, Analog or Microprocessor systems. The switching noise could make it difficult or impossible to debug the complete system. • Project deadline has passed.

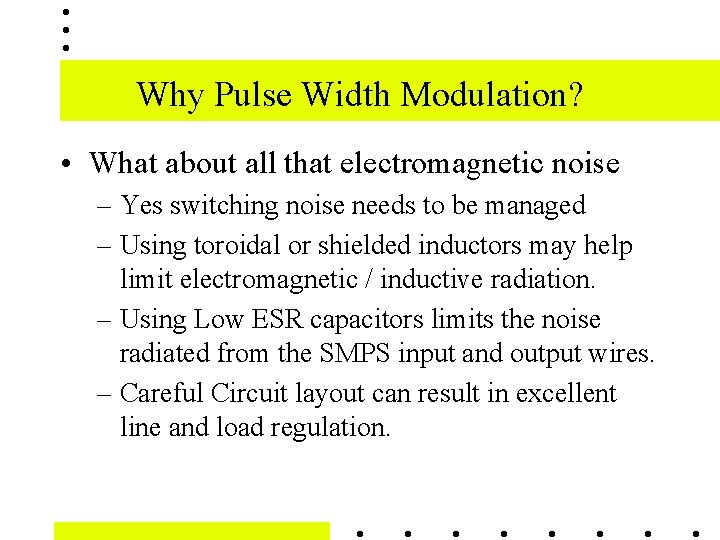

Why Pulse Width Modulation? • What about all that electromagnetic noise – Yes switching noise needs to be managed – Using toroidal or shielded inductors may help limit electromagnetic / inductive radiation. – Using Low ESR capacitors limits the noise radiated from the SMPS input and output wires. – Careful Circuit layout can result in excellent line and load regulation.

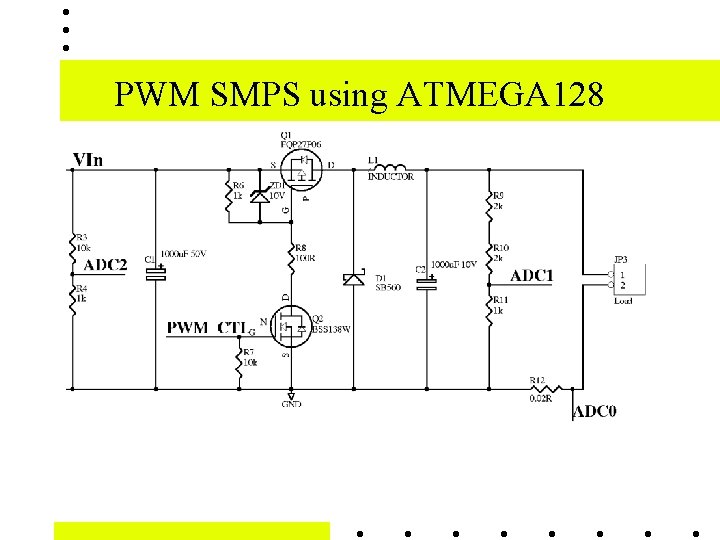

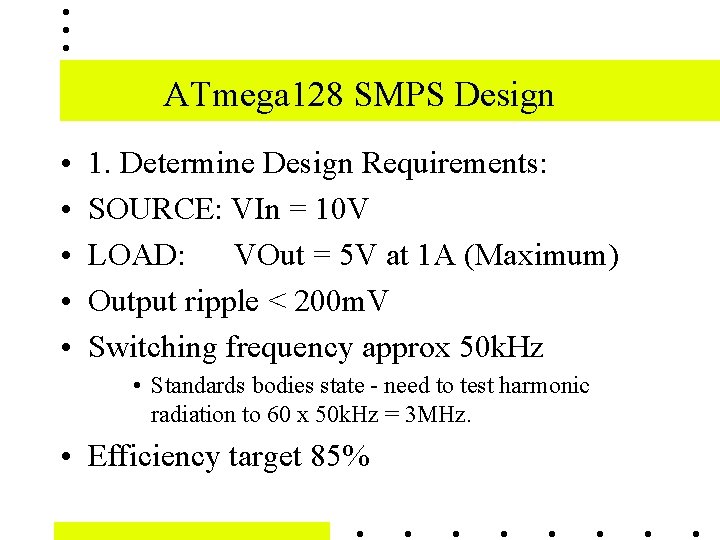

ATmega 128 SMPS Design • • • 1. Determine Design Requirements: SOURCE: VIn = 10 V LOAD: VOut = 5 V at 1 A (Maximum) Output ripple < 200 m. V Switching frequency approx 50 k. Hz • Standards bodies state - need to test harmonic radiation to 60 x 50 k. Hz = 3 MHz. • Efficiency target 85%

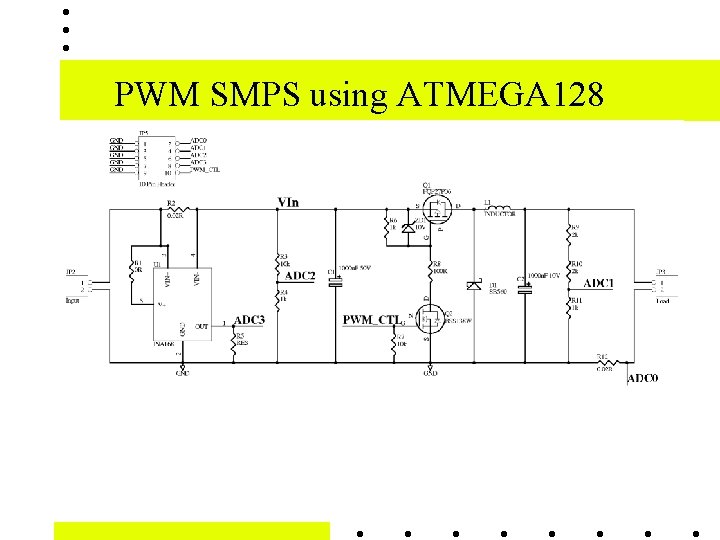

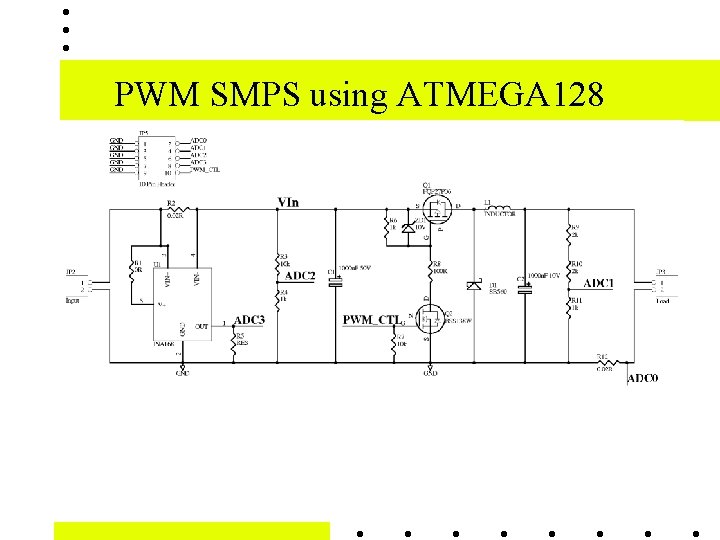

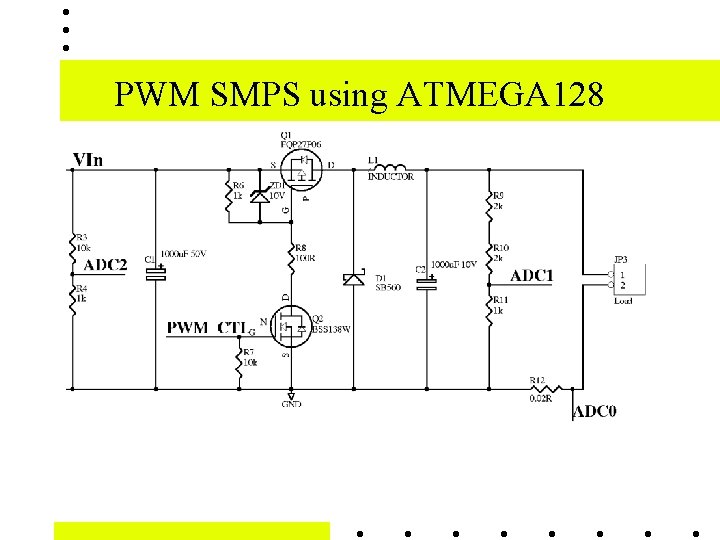

PWM SMPS using ATMEGA 128

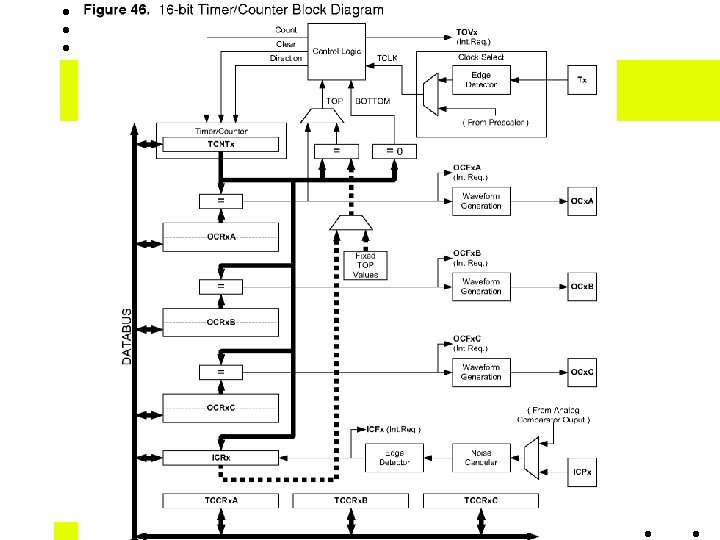

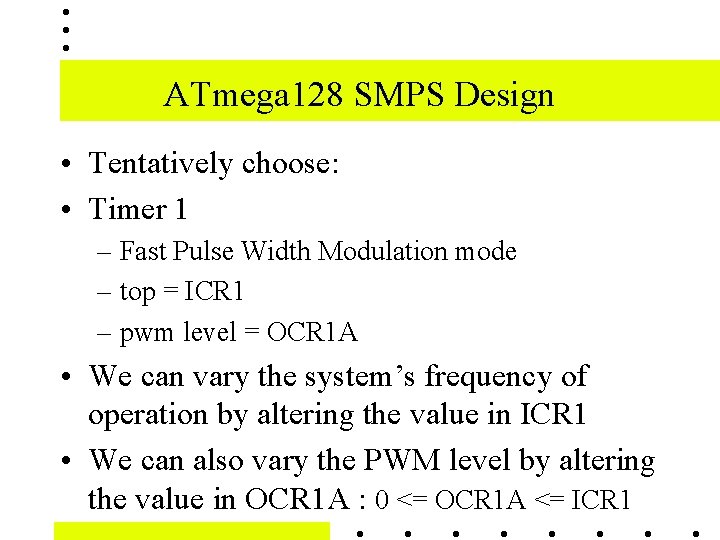

ATmega 128 SMPS Design • Tentatively choose: • Timer 1 – Fast Pulse Width Modulation mode – top = ICR 1 – pwm level = OCR 1 A • We can vary the system’s frequency of operation by altering the value in ICR 1 • We can also vary the PWM level by altering the value in OCR 1 A : 0 <= OCR 1 A <= ICR 1

PWM SMPS using ATMEGA 128

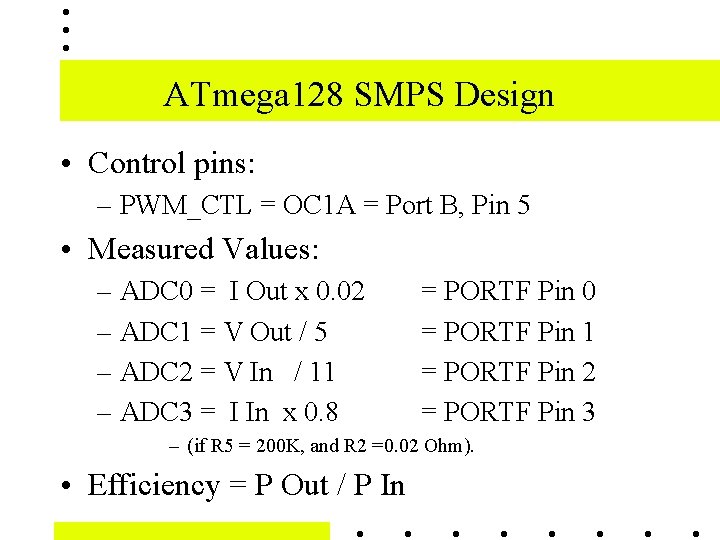

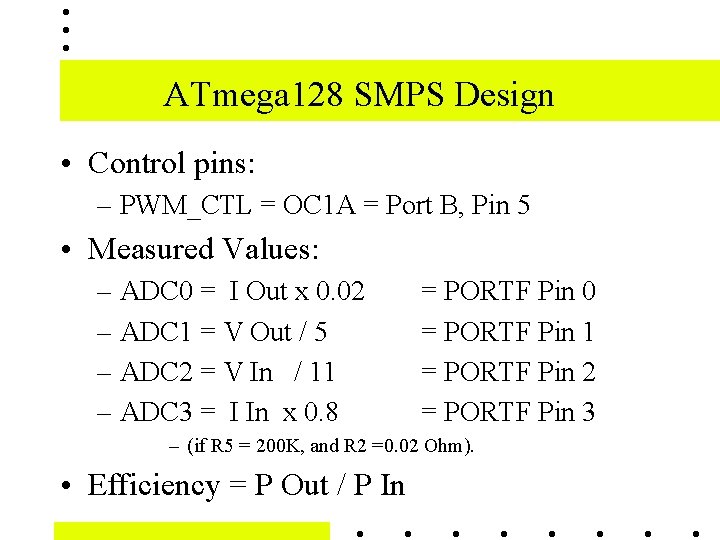

ATmega 128 SMPS Design • Control pins: – PWM_CTL = OC 1 A = Port B, Pin 5 • Measured Values: – ADC 0 = I Out x 0. 02 – ADC 1 = V Out / 5 – ADC 2 = V In / 11 – ADC 3 = I In x 0. 8 = PORTF Pin 0 = PORTF Pin 1 = PORTF Pin 2 = PORTF Pin 3 – (if R 5 = 200 K, and R 2 =0. 02 Ohm). • Efficiency = P Out / P In

PWM SMPS using ATMEGA 128

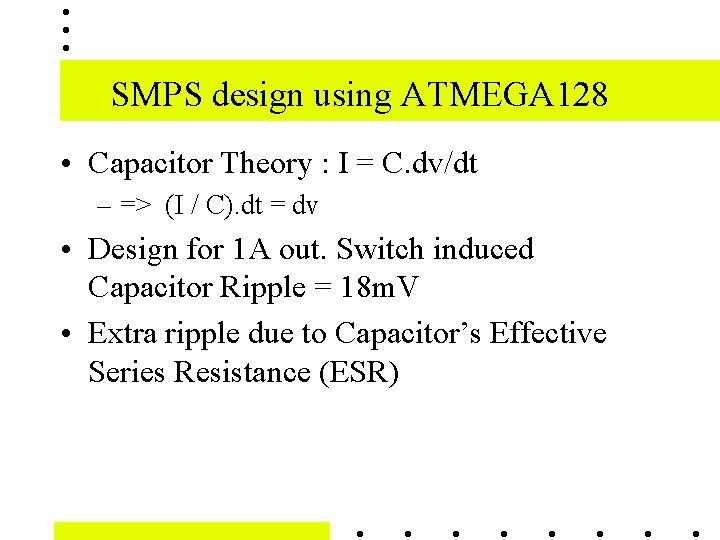

SMPS design using ATMEGA 128 • Capacitor Theory : I = C. dv/dt – => (I / C). dt = dv • Design for 1 A out. Switch induced Capacitor Ripple = 18 m. V • Extra ripple due to Capacitor’s Effective Series Resistance (ESR)

SMPS design using ATMEGA 128 • Inductor Theory : V = L. di/dt • Design V Out = 5 V at I Out = 1 A. • Vin = 10 V; We can expect I In about 0. 6 A. • From National Semiconductor AN 1197 • Calculate L >= 100 u. H, – Choose Pulse Engineering Toroidal Inductor PE 92108 K: 100 u. H, 3. 6 A (because we had them on hand).

SMPS design using ATMEGA 128 • So the circuit works by initially switching on transistor Q 2 (via node PWM_CTL) which in turn switches on Q 1. • Current flows through inductor L 1, and charges capacitor C 2, and provides the load on JP 3 with current. • Energy is stored in L 1’s magnetic core as current starts to rise. If the core saturates, current plateaus, and no more energy is stored.

SMPS design using ATMEGA 128 • After a period, determined by ATMEGA 128 counter 1 - ICR 1, the voltage on PWM_CTL, Q 1 is switched off, Charge is bled off Q 2’s Gate & it also switches off. • When Q 1 & Q 2 are switched off current continues to flow through L 1, and through the schottky diode D 1, until the energy from L 1 is returned to the output load and/or Capacitor C 2.

A PWM SMPS using ATMEGA 128 • We need to frequently measure the output voltage, compare that with the desired output voltage, and adjust the PWM level to suit. • How could we improve the feedback responsiveness of the circuit? • How can we guarantee stability? • Load Regulation? • Line Regulation?

More SMPS Resources • TI, National Semiconductor, On-Semi, Linear Tech • National Semiconductor Application Notes: – AN 1149 - Layout Guidelines for Switching Power Supplies – AN 1197 - Selecting Inductors for Buck Regulators • Reference Design Software – Power Supply design, layout & simulation tools • http: //www. national. com/appinfo/power/webench. html • Switchers Made Simple, Web Sim, Web Therm

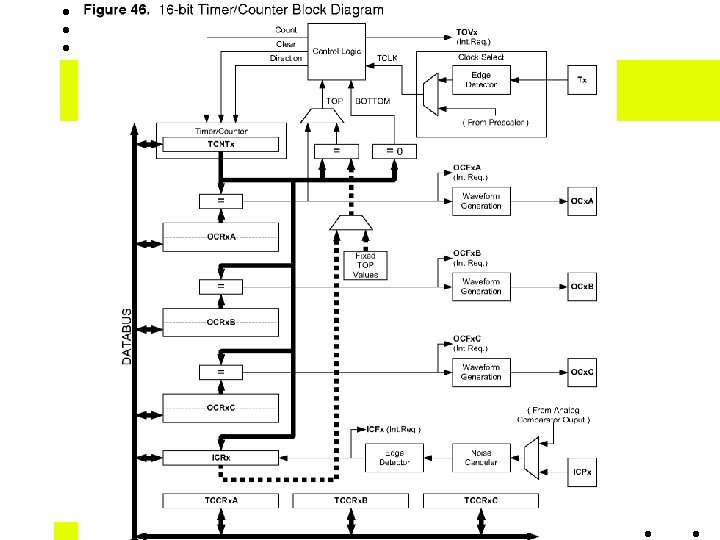

Acknowledgements – These notes were produced by Paul Main, • www. sea. vg Oct 2007 • Simple DC-DC converter technologies illustration– The IEEE Electrical Engineering Handbook, Richard Dorf et al, • Fig 46 - Timer 1/Counter 1 Block Diagram – Atmel ATMEGA 128 full data • Atmel website www. atmel. com and • http: //www. sea. vg/mic/2007/Atmel/Atmega 128 Manual. Doc 2467. pdf