Koprocesor Reprezentacja zmiennoprzecinkowa liczb rzeczywistych Reprezentacja liczby rzeczywistej

Koprocesor. Reprezentacja zmiennoprzecinkowa liczb rzeczywistych.

Reprezentacja liczby rzeczywistej zapisanej za pomocą notacji naukowej. Ze względu na wygodę operowania na takich liczbach, przyjmuje się ograniczony zakres na mantysę i cechę. Powoduje to, że reprezentacja liczby rzeczywistej jest tylko przybliżona, a jedna liczba zmiennoprzecinkowa może reprezentować różne liczby rzeczywiste z pewnego zakresu. liczba zmiennoprzecinkowa = mantysa * podstawacecha

Wartość liczby zmiennoprzecinkowej (różnej od zera) określa wyrażenie: Mantysę Mx z kolei można przedstawić w postaci: Mx=Ix+Fx gdzie: Ix - część całkowita mantysy, Fx - jej częścią ułamkowa.

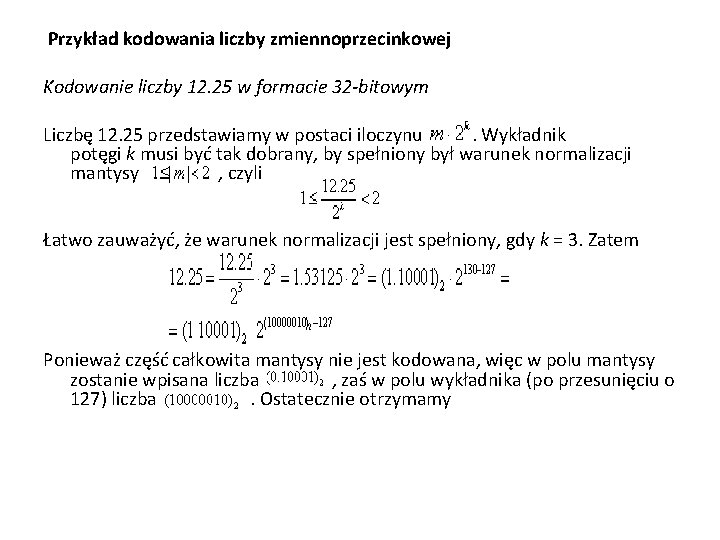

Przykład kodowania liczby zmiennoprzecinkowej Kodowanie liczby 12. 25 w formacie 32 -bitowym Liczbę 12. 25 przedstawiamy w postaci iloczynu . Wykładnik potęgi k musi być tak dobrany, by spełniony był warunek normalizacji mantysy , czyli Łatwo zauważyć, że warunek normalizacji jest spełniony, gdy k = 3. Zatem Ponieważ część całkowita mantysy nie jest kodowana, więc w polu mantysy zostanie wpisana liczba , zaś w polu wykładnika (po przesunięciu o 127) liczba . Ostatecznie otrzymamy

Jednostka zmiennopozycyjna, FPU(angielskie Floating Point Unit), blok funkcjonalny procesora, zaopatrzony we własne rejestry zmiennopozycyjne (zmiennoprzecinkowe), wykonujący działania w arytmetyce zmiennopozycyjnej. Jednostka zmiennopozycyjna występuje w większych procesorach 32 -bitowych i 64 -bitowych. Prostsze systemy mikroprocesorowe w celu wykonywania obliczeń zmiennopozycyjnych kooperują z układami współprocesorów arytmetycznych lub korzystają z ich emulatorów.

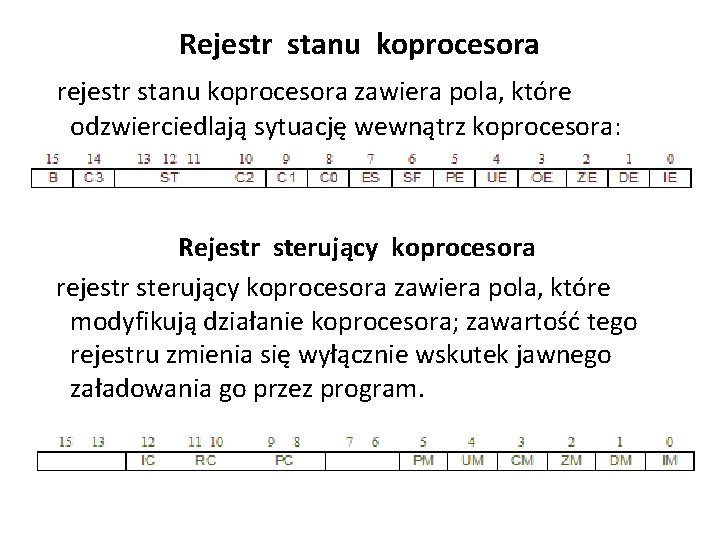

Rejestr stanu koprocesora rejestr stanu koprocesora zawiera pola, które odzwierciedlają sytuację wewnątrz koprocesora: Rejestr sterujący koprocesora rejestr sterujący koprocesora zawiera pola, które modyfikują działanie koprocesora; zawartość tego rejestru zmienia się wyłącznie wskutek jawnego załadowania go przez program.

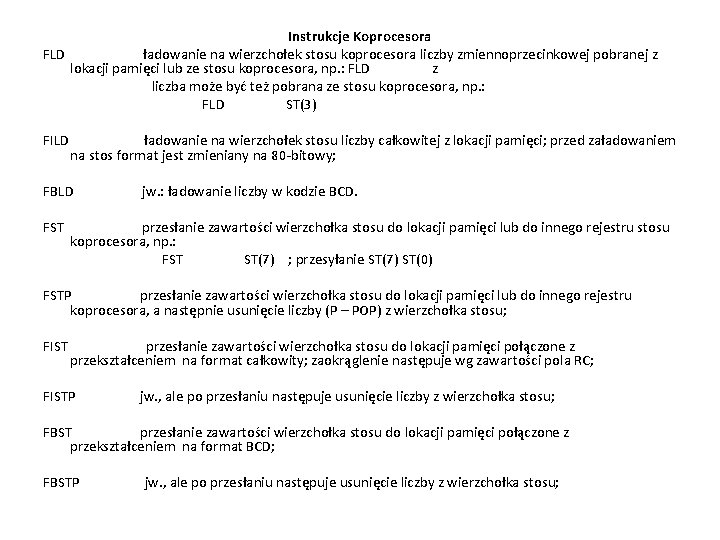

Instrukcje Koprocesora FLD ładowanie na wierzchołek stosu koprocesora liczby zmiennoprzecinkowej pobranej z lokacji pamięci lub ze stosu koprocesora, np. : FLD z liczba może być też pobrana ze stosu koprocesora, np. : FLD ST(3) FILD ładowanie na wierzchołek stosu liczby całkowitej z lokacji pamięci; przed załadowaniem na stos format jest zmieniany na 80 -bitowy; FBLD jw. : ładowanie liczby w kodzie BCD. FST przesłanie zawartości wierzchołka stosu do lokacji pamięci lub do innego rejestru stosu koprocesora, np. : FST ST(7) ; przesyłanie ST(7) ST(0) FSTP przesłanie zawartości wierzchołka stosu do lokacji pamięci lub do innego rejestru koprocesora, a następnie usunięcie liczby (P – POP) z wierzchołka stosu; FIST przesłanie zawartości wierzchołka stosu do lokacji pamięci połączone z przekształceniem na format całkowity; zaokrąglenie następuje wg zawartości pola RC; FISTP jw. , ale po przesłaniu następuje usunięcie liczby z wierzchołka stosu; FBST przesłanie zawartości wierzchołka stosu do lokacji pamięci połączone z przekształceniem na format BCD; FBSTP jw. , ale po przesłaniu następuje usunięcie liczby z wierzchołka stosu;

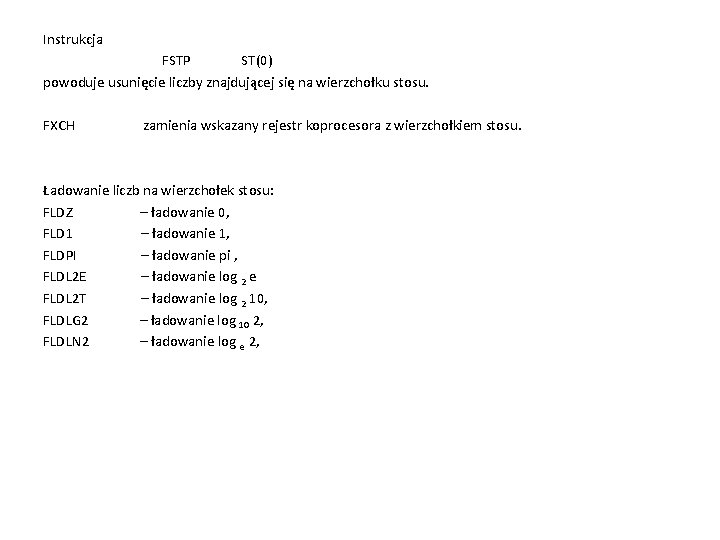

Instrukcja FSTP ST(0) powoduje usunięcie liczby znajdującej się na wierzchołku stosu. FXCH zamienia wskazany rejestr koprocesora z wierzchołkiem stosu. Ładowanie liczb na wierzchołek stosu: FLDZ – ładowanie 0, FLD 1 – ładowanie 1, FLDPI – ładowanie pi , FLDL 2 E – ładowanie log 2 e FLDL 2 T – ładowanie log 2 10, FLDLG 2 – ładowanie log 10 2, FLDLN 2 – ładowanie log e 2,

- Slides: 11