Integrated Retiming and Mapping for Sequential Optimization Shauki

- Slides: 12

Integrated Retiming and Mapping for Sequential Optimization Shauki Elassaad EE 290 A 2/18/2021 S. Elassaad - EE 290 A 1

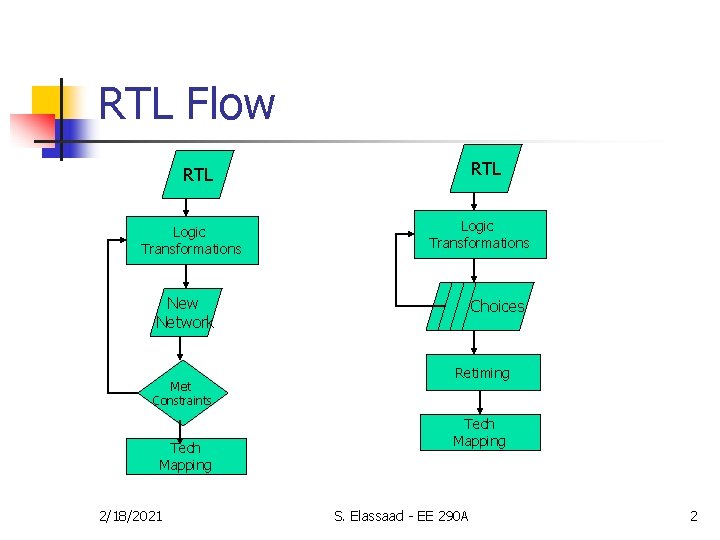

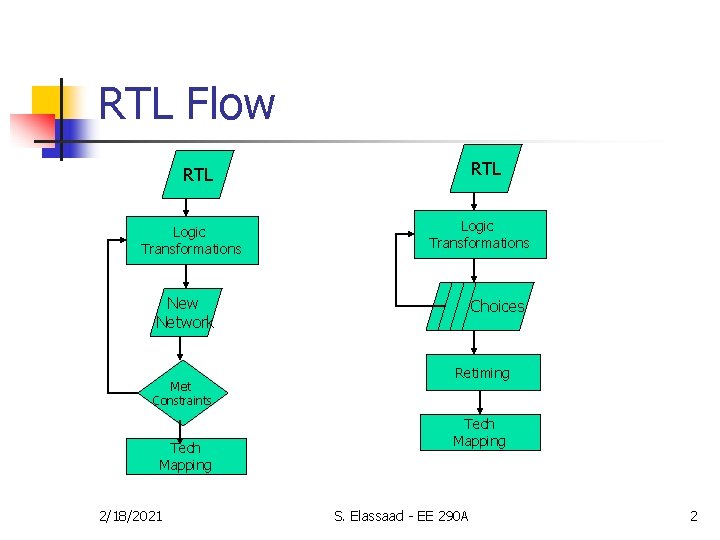

RTL Flow RTL Logic Transformations New Network Met Constraints Tech Mapping 2/18/2021 Choices Retiming Tech Mapping S. Elassaad - EE 290 A 2

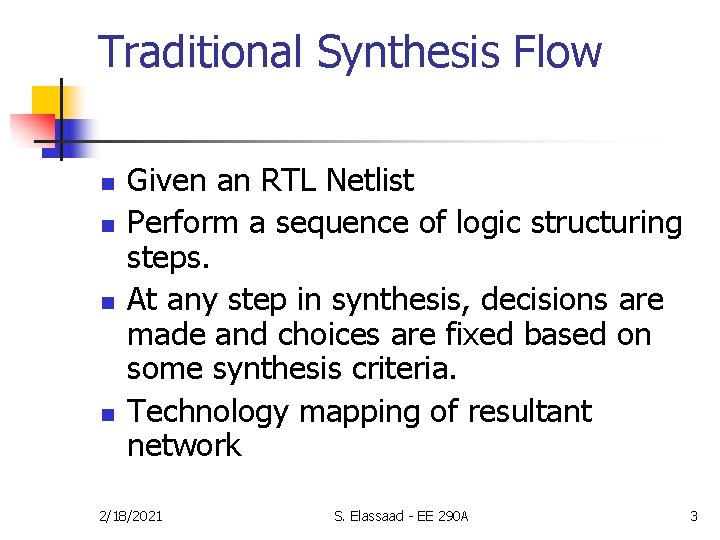

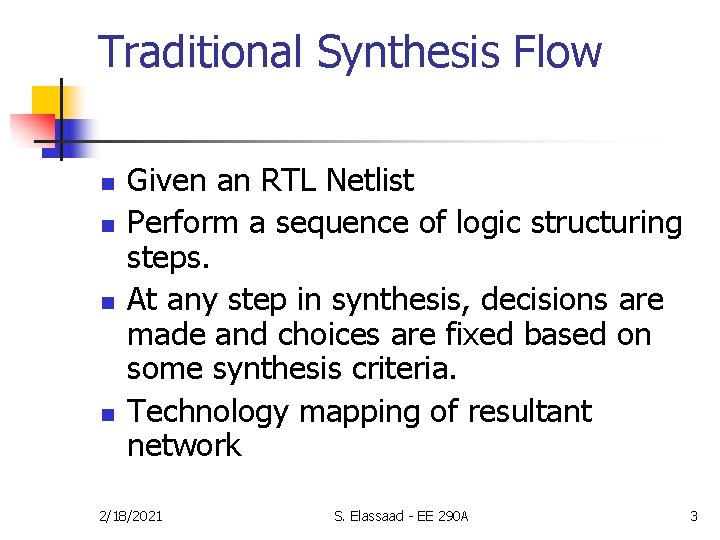

Traditional Synthesis Flow n n Given an RTL Netlist Perform a sequence of logic structuring steps. At any step in synthesis, decisions are made and choices are fixed based on some synthesis criteria. Technology mapping of resultant network 2/18/2021 S. Elassaad - EE 290 A 3

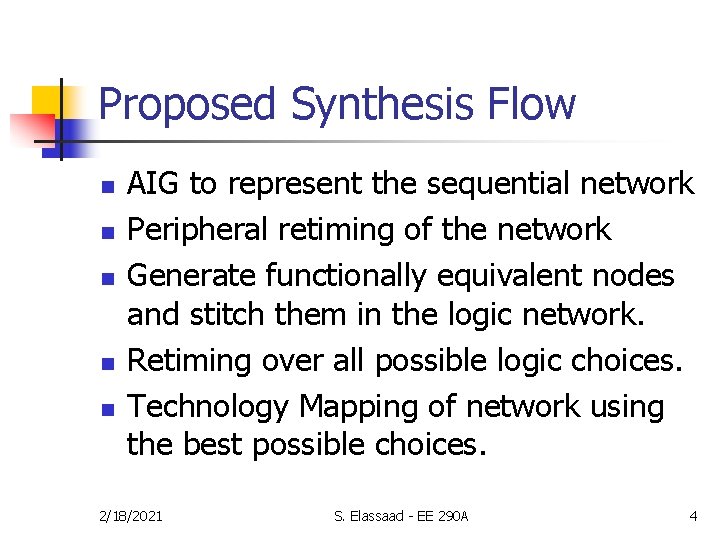

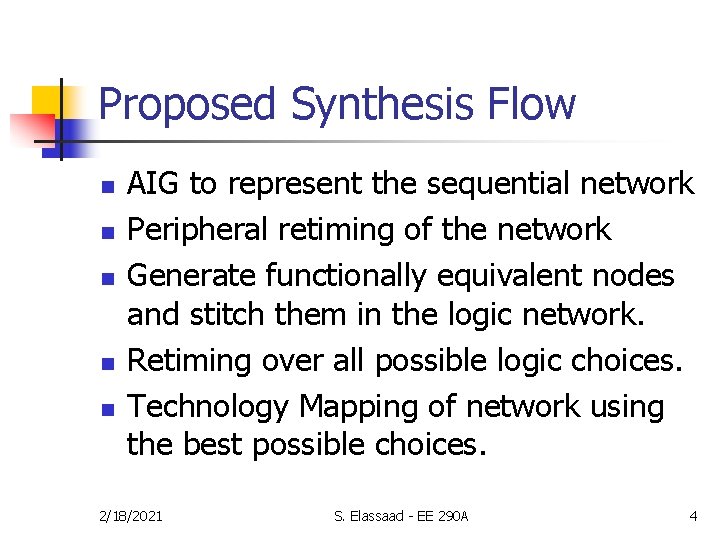

Proposed Synthesis Flow n n n AIG to represent the sequential network Peripheral retiming of the network Generate functionally equivalent nodes and stitch them in the logic network. Retiming over all possible logic choices. Technology Mapping of network using the best possible choices. 2/18/2021 S. Elassaad - EE 290 A 4

Project Goal n Compare area and delay of mapped networks: n n n New Retiming Algorithm for a Choice-free Fraig Network. Accumulate Choices via a variety of logic transformations. Retiming over all possible logic transformations Technology-mapped network of choice-free logic network Technology-mapped network of logic network with choice nodes attached to it. 2/18/2021 S. Elassaad - EE 290 A 5

Choice Nodes Generation n Cuts can be defined by register outputs (primay inputs) and register inputs (primary outputs). Generate choice-nodes for all logic cuts using MVSIS. Accumulate all choices. 2/18/2021 S. Elassaad - EE 290 A 6

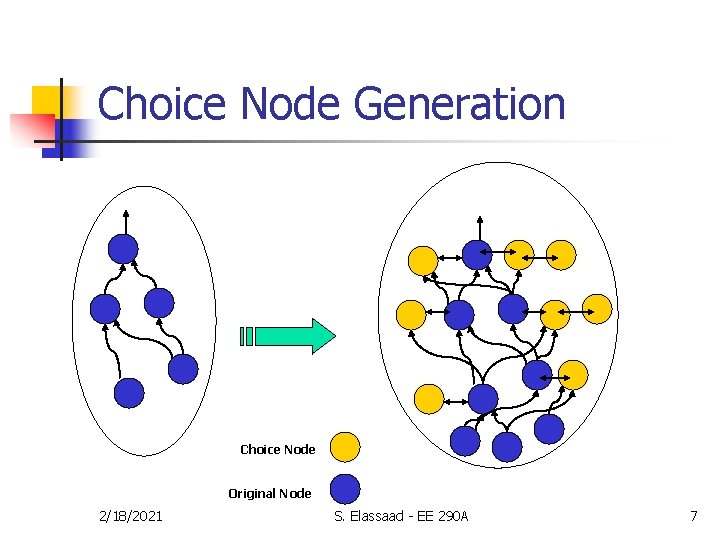

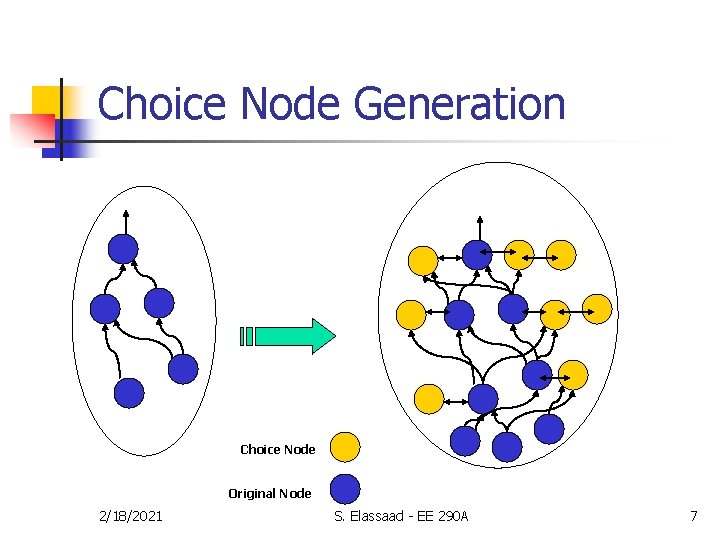

Choice Node Generation Choice Node Original Node 2/18/2021 S. Elassaad - EE 290 A 7

Retiming & Mapping n n Stitch Choices back into AIG Detect and record different AIG structures of Boolean functions n n Use them as additional mapping choices to achieve better quality Technology Mapping of resultant network. 2/18/2021 S. Elassaad - EE 290 A 8

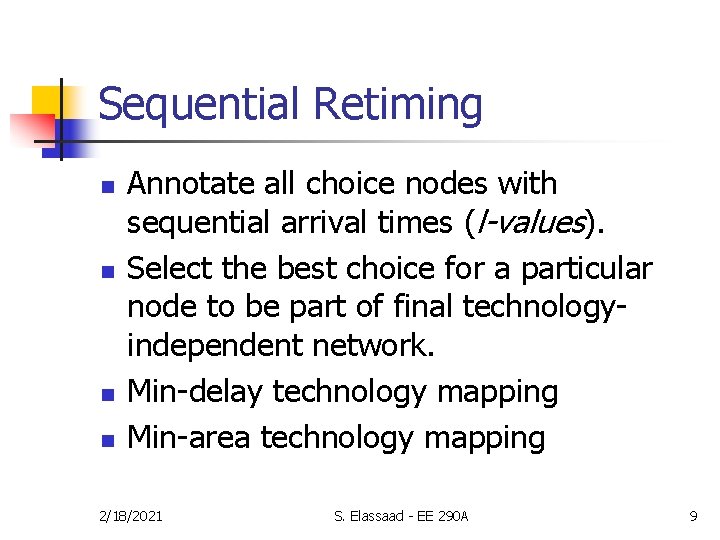

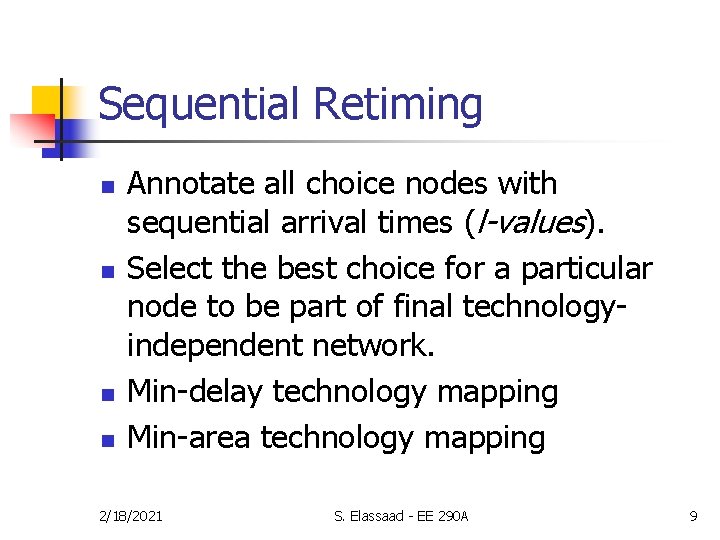

Sequential Retiming n n Annotate all choice nodes with sequential arrival times (l-values). Select the best choice for a particular node to be part of final technologyindependent network. Min-delay technology mapping Min-area technology mapping 2/18/2021 S. Elassaad - EE 290 A 9

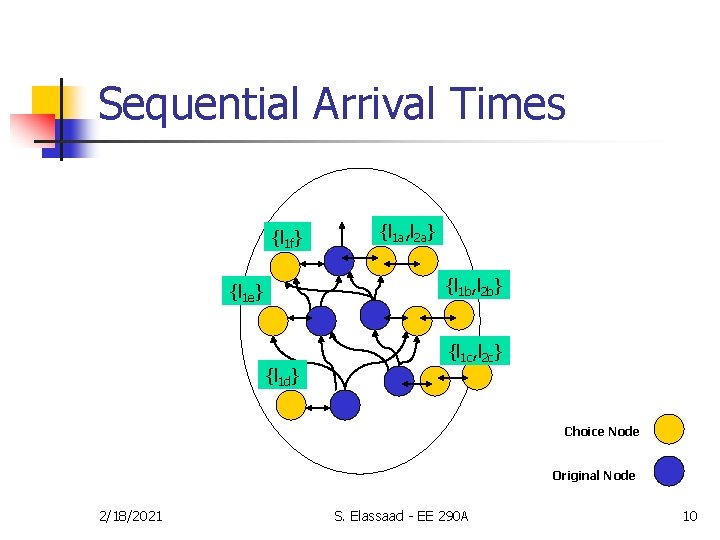

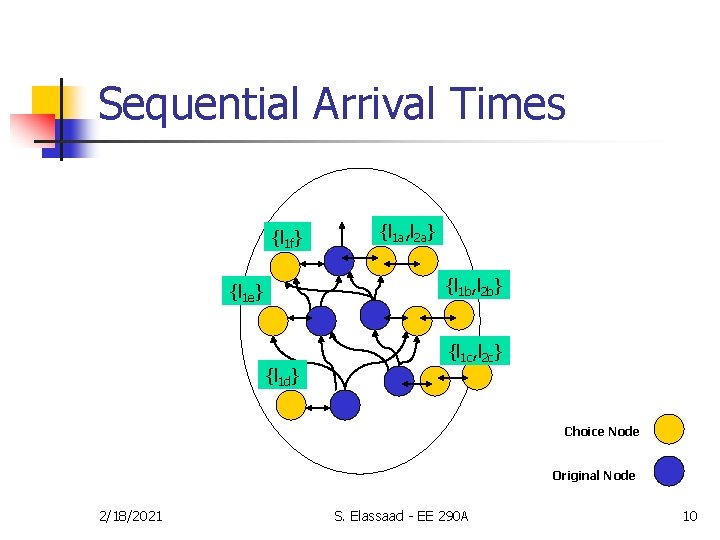

Sequential Arrival Times {l 1 f} {l 1 a, l 2 a} {l 1 b, l 2 b} {l 1 e} {l 1 d} {l 1 c, l 2 c} Choice Node Original Node 2/18/2021 S. Elassaad - EE 290 A 10

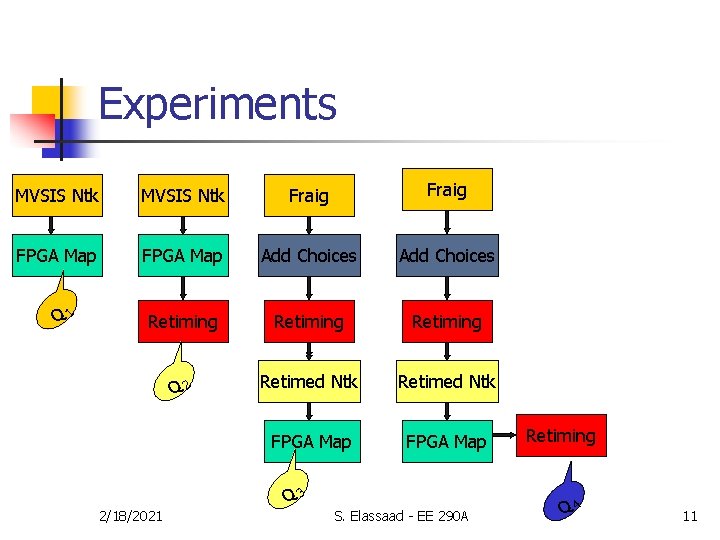

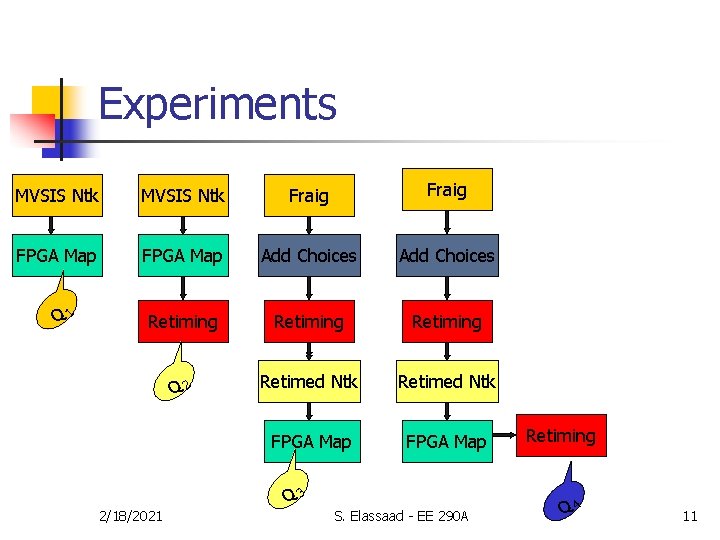

Experiments MVSIS Ntk Fraig FPGA Map Add Choices Retiming Retime Retiming Q 2 Retimed Ntk FPGA Map Q 1 2/18/2021 Q 3 S. Elassaad - EE 290 A Retiming Q 4 11

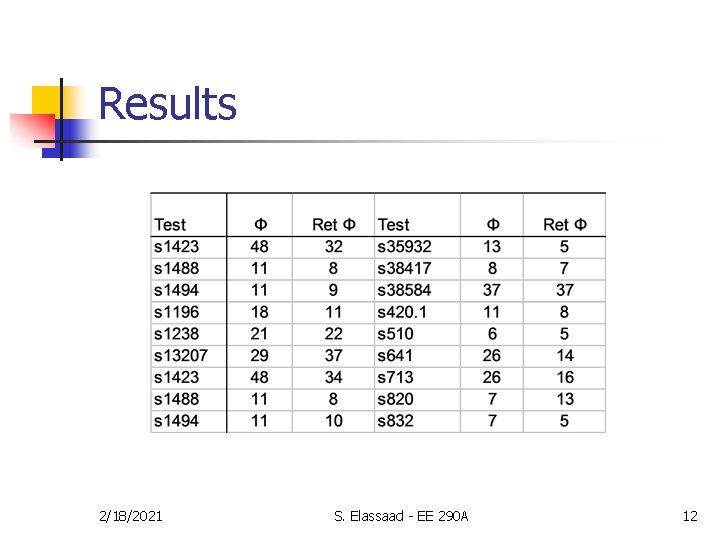

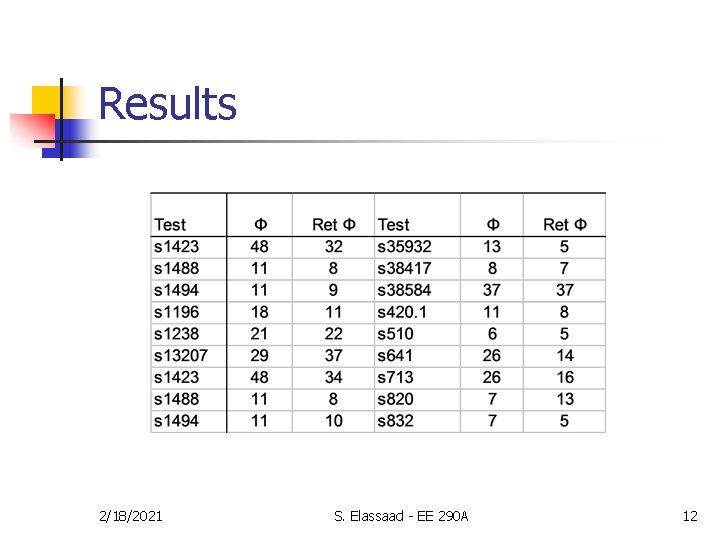

Results 2/18/2021 S. Elassaad - EE 290 A 12