IAS 0600 DIGITAL SYSTEMS DESIGN LABS Dmitri Mihhailov

IAS 0600 DIGITAL SYSTEMS DESIGN LABS Dmitri Mihhailov Tallinn University of Technology

Digital Systems Design Labs Staff n Lecturer: Alexander Sudnitson (associate professor) Ø aleksander. sudnitson@taltech. ee Ø ICT-503 (620 2255) n Lab Assistant: Dmitri Mihhailov Ø dmitri. mihhailov@taltech. ee Ø ICT-505 (no phone) 2

IAS 0600 Digital Systems Design Labs (1) n Lab Room: Ø ICT-501 (~30 working places) Ø Lab PCs require the same password that is used to access other computers in TTU network n Lab Time: Ø IASM 11 & IASM 12 Wednesdays 16: 00 - 17: 30 ICT-501 Ø Unused/Reserve Tuesdays 8: 00 - 9: 30 ICT-501 3

IAS 0600 Digital Systems Design Labs (2) n Xilinx Design Software: Ø Vivado Design Suite (7 -Series and newer) System Edition (in the lab) Web. PACK Edition (free) n FPGA boards: Ø Digilent Nexys-4 DDR (Xilinx Artix-7 FPGA) ~18 boards used for all labs (labs 1 -6) 4

IAS 0600 Digital Systems Design Labs (3) n Installing Vivado: Ø create Xilinx account (should be free) Ø be sure to have 40+ GB of free space Ø download installation files (Windows or Linux) https: //www. xilinx. com/support/download. html Ø select “Vivado HL Web. PACK” edition Ø select required features: Design Tools => Vivado Design Suite => Vivado Devices => 7 -Series => Artix 7 Installation Options => Install Cable Drivers Ø the complete step-by-step instruction can be found at (also available on the labs web-page): https: //reference. digilentinc. com/vivado/installingvivado/start 5

IAS 0600 Digital Systems Design Labs (4) n Remote Connection: Ø as described in ‘General Instructions’ for the last year’s ‘IAS 0340 Digital Systems. Modeling and Synthesis’ course at http: //ati. ttu. ee/IAS 0340/labs/GI. html) 6

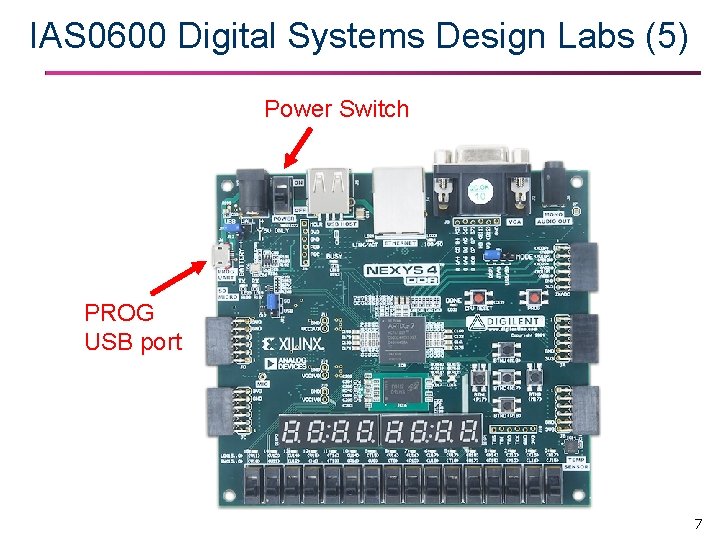

IAS 0600 Digital Systems Design Labs (5) Power Switch PROG USB port 7

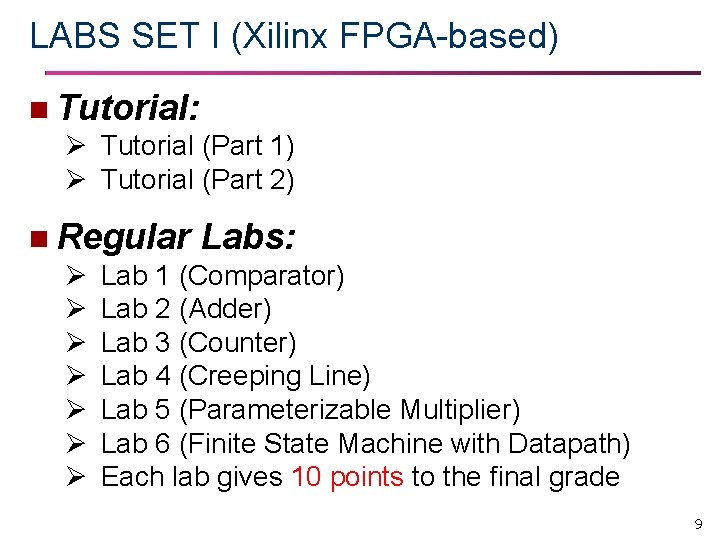

IAS 0600 Digital Systems Design Labs (6) n Lab Course webpage: Ø http: //ati. ttu. ee/~alsu/ IAS 0600 l Digital Systems Design with VHDL (WORKSHOPS) Ø http: //ati. ttu. ee/~alsu/IAS 0600 l. html Ø Lab Syllabus n The target lab course: Ø LABS SET I (Xilinx FPGA-based) n The lab course consists Ø Tutorial Ø Regular Labs (6 in total) of 7 labs: 8

LABS SET I (Xilinx FPGA-based) n Tutorial: Ø Tutorial (Part 1) Ø Tutorial (Part 2) n Regular Labs: Ø Lab 1 (Comparator) Ø Lab 2 (Adder) Ø Lab 3 (Counter) Ø Lab 4 (Creeping Line) Ø Lab 5 (Parameterizable Multiplier) Ø Lab 6 (Finite State Machine with Datapath) Ø Each lab gives 10 points to the final grade 9

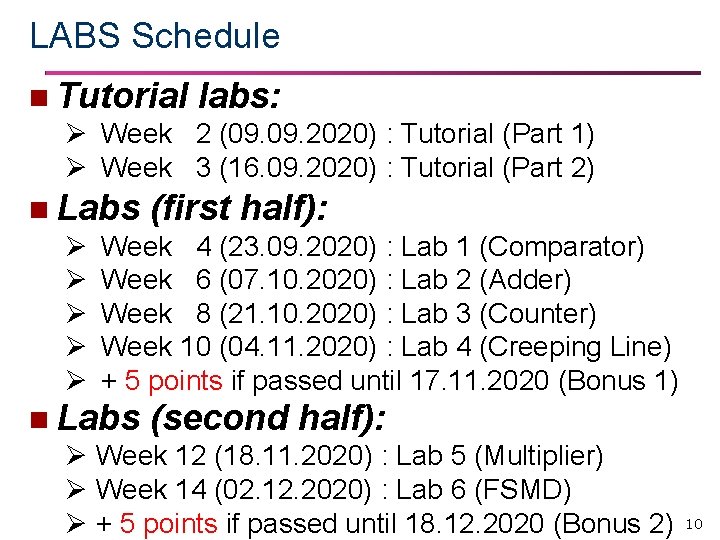

LABS Schedule n Tutorial labs: Ø Week 2 (09. 2020) : Tutorial (Part 1) Ø Week 3 (16. 09. 2020) : Tutorial (Part 2) n Labs (first half): Ø Week 4 (23. 09. 2020) : Lab 1 (Comparator) Ø Week 6 (07. 10. 2020) : Lab 2 (Adder) Ø Week 8 (21. 10. 2020) : Lab 3 (Counter) Ø Week 10 (04. 11. 2020) : Lab 4 (Creeping Line) Ø + 5 points if passed until 17. 11. 2020 (Bonus 1) n Labs (second half): Ø Week 12 (18. 11. 2020) : Lab 5 (Multiplier) Ø Week 14 (02. 12. 2020) : Lab 6 (FSMD) Ø + 5 points if passed until 18. 12. 2020 (Bonus 2) 10

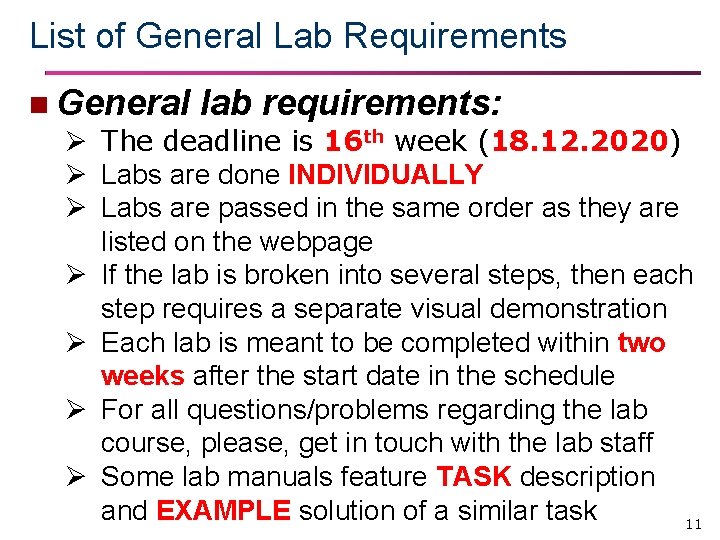

List of General Lab Requirements n General lab requirements: Ø The deadline is 16 th week (18. 12. 2020) Ø Labs are done INDIVIDUALLY Ø Labs are passed in the same order as they are listed on the webpage Ø If the lab is broken into several steps, then each step requires a separate visual demonstration Ø Each lab is meant to be completed within two weeks after the start date in the schedule Ø For all questions/problems regarding the lab course, please, get in touch with the lab staff Ø Some lab manuals feature TASK description and EXAMPLE solution of a similar task 11

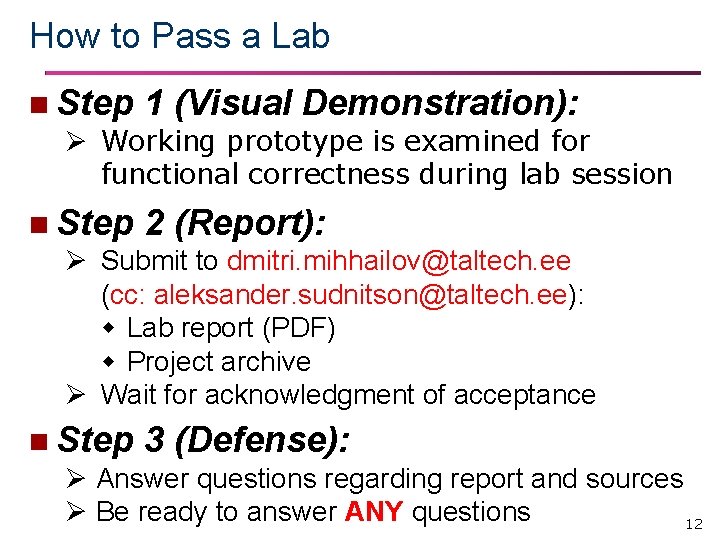

How to Pass a Lab n Step 1 (Visual Demonstration): Ø Working prototype is examined for functional correctness during lab session n Step 2 (Report): Ø Submit to dmitri. mihhailov@taltech. ee (cc: aleksander. sudnitson@taltech. ee): Lab report (PDF) Project archive Ø Wait for acknowledgment of acceptance n Step 3 (Defense): Ø Answer questions regarding report and sources Ø Be ready to answer ANY questions 12

How to Write a Report (1) n Reports are written in FREE form n The goals of lab report: Ø Document the workflow Ø Describe the results and their significance Ø Demonstrate writer’s comprehension n List of topics to cover in the Ø Introduction Ø Background Ø Workflow Ø Results and discussion Ø Conclusion (including feedback) Ø References and appendices report: 13

How to Write a Report (2) n In is highly advised to start working on the reports BEFORE the lab n Prepare before the lab: Ø Introduction Ø Background and References Ø Workflow (part that can be done before the lab) n Prepare during the lab: Ø Workflow (remaining part) n Prepare after the lab: Ø Results and discussion Ø Conclusion 14

List of General Report Requirements n General report requirements: Ø Lab report MUST feature things that are specifically required to be included in the task Ø All objects in the text MUST be numbered, labeled and referenced Ø All figures, tables, code listings, statements, results MUST be explicitly explained within text Ø Complete source codes MUST NOT be part of the report (even in appendices) Ø All materials taken from external sources MUST be referenced (also within the text) Ø Functional simulation MUST always be performed and described 15

- Slides: 15