HRORC The new HRORC 170206 HRORC Torsten Alt

- Slides: 12

H-RORC The new H-RORC 17/02/06 H-RORC Torsten Alt KIP Heidelberg

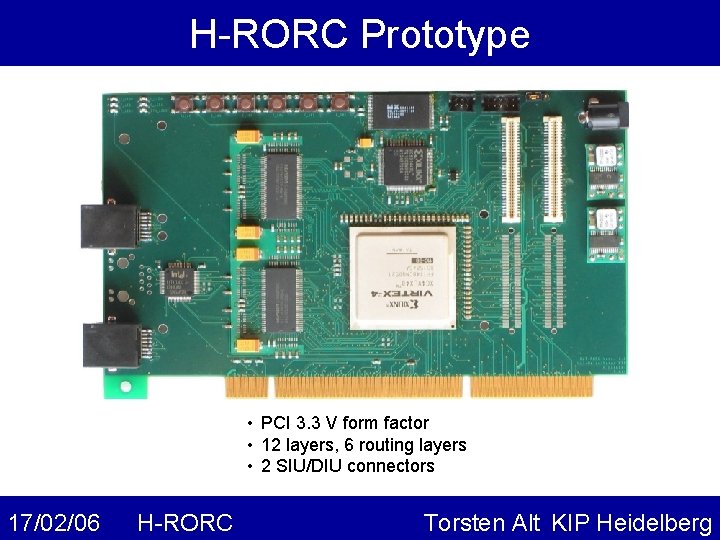

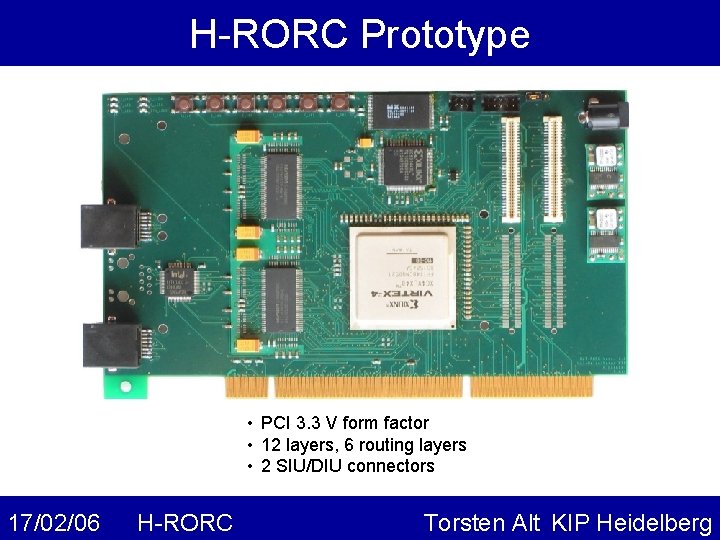

H-RORC Prototype • PCI 3. 3 V form factor • 12 layers, 6 routing layers • 2 SIU/DIU connectors 17/02/06 H-RORC Torsten Alt KIP Heidelberg

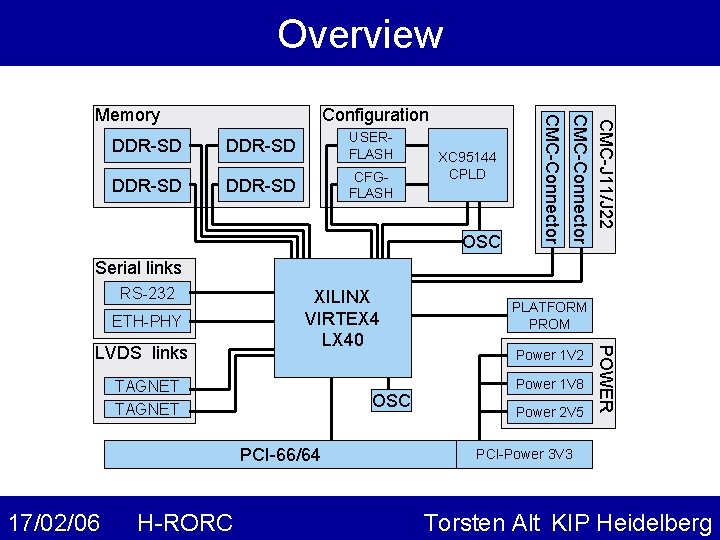

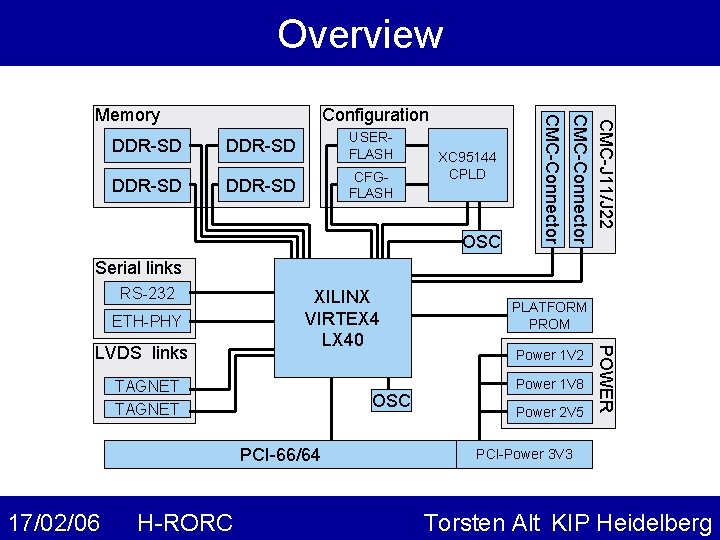

H-RORC • H-RORC : HLT Read-Out Receiver Card • Tasks: – Receiving of the raw detector data – Injecting the data into the main memory of the hosts of the HLT framework – Online processing of the data in hardware – Sending processed data out of the HLT • Implementation: – – 17/02/06 PCI card 64 bit/66 MHz with XILINX Virtex 4 2 (half) Common Mezzanine Connectors (CMC) 2 fast serial links : TAGNET DDR-SDRAM / ETHERNET / FLASH H-RORC Torsten Alt KIP Heidelberg

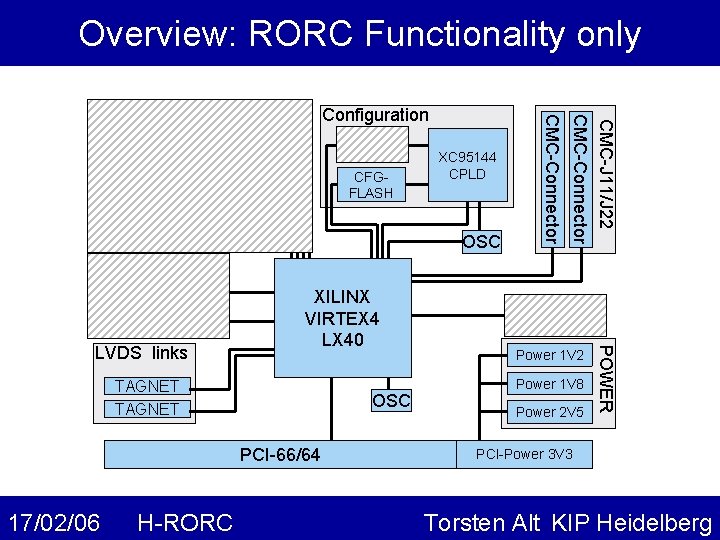

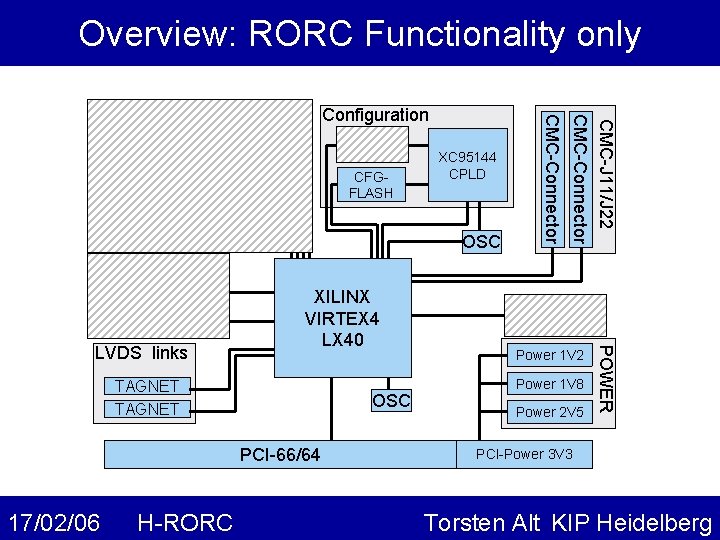

H-RORC Details • RORC functionality – – – Xilinx Virtex 4 LX 40 FPGA “Secure. Configuration” with FLASH memory and CPLD PCI interface with 64 bit / 66 MHz – XILINX Logi. CORE 2 x half CMC interface to two SIU/DIU cards fast serial links to connect multiple RORCs • Additional functionality – 4 independent DDR-SDRAM modules with up to 1 Gb – Optinal Xilinx Prom for standalone programming – “Ready for Linux” (Ethernet interface, RS 232, FLASH memory) 17/02/06 H-RORC Torsten Alt KIP Heidelberg

Overview DDR-SD USERFLASH DDR-SD CFGFLASH XC 95144 CPLD OSC CMC-J 11/J 22 CMC-Connector Configuration CMC-Connector Memory Serial links RS-232 ETH-PHY TAGNET OSC PCI-66/64 17/02/06 H-RORC PLATFORM PROM Power 1 V 2 Power 1 V 8 Power 2 V 5 POWER LVDS links XILINX VIRTEX 4 LX 40 PCI-Power 3 V 3 Torsten Alt KIP Heidelberg

Overview: RORC Functionality only DDR-SD USERFLASH DDR-SD CFGFLASH XC 95144 CPLD OSC CMC-J 11/J 22 CMC-Connector Configuration CMC-Connector Memory Serial links RS-232 ETH-PHY TAGNET OSC PCI-66/64 17/02/06 H-RORC PLATFORM PROM Power 1 V 2 Power 1 V 8 Power 2 V 5 POWER LVDS links XILINX VIRTEX 4 LX 40 PCI-Power 3 V 3 Torsten Alt KIP Heidelberg

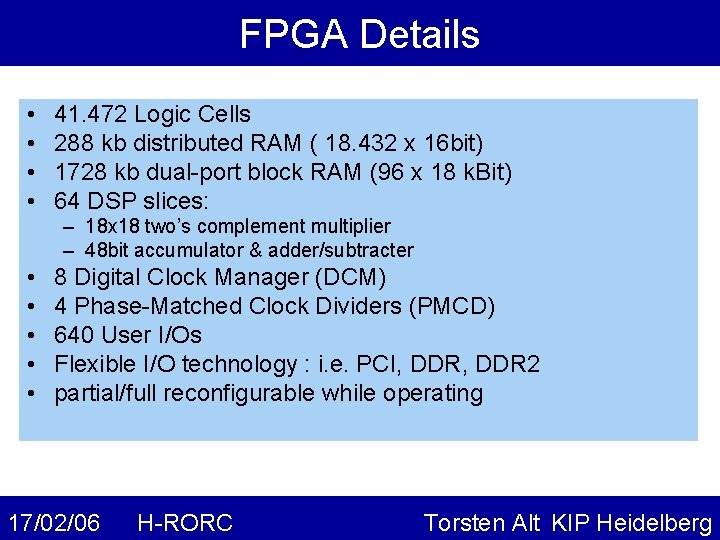

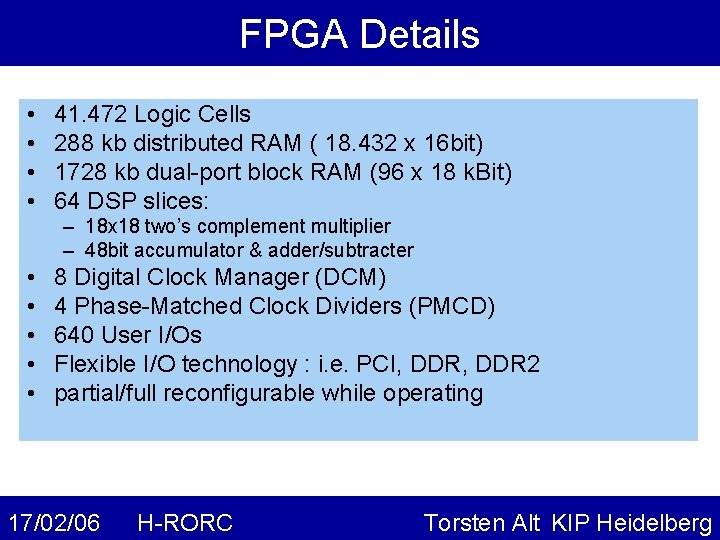

FPGA Details • • 41. 472 Logic Cells 288 kb distributed RAM ( 18. 432 x 16 bit) 1728 kb dual-port block RAM (96 x 18 k. Bit) 64 DSP slices: – 18 x 18 two’s complement multiplier – 48 bit accumulator & adder/subtracter • • • 8 Digital Clock Manager (DCM) 4 Phase-Matched Clock Dividers (PMCD) 640 User I/Os Flexible I/O technology : i. e. PCI, DDR 2 partial/full reconfigurable while operating 17/02/06 H-RORC Torsten Alt KIP Heidelberg

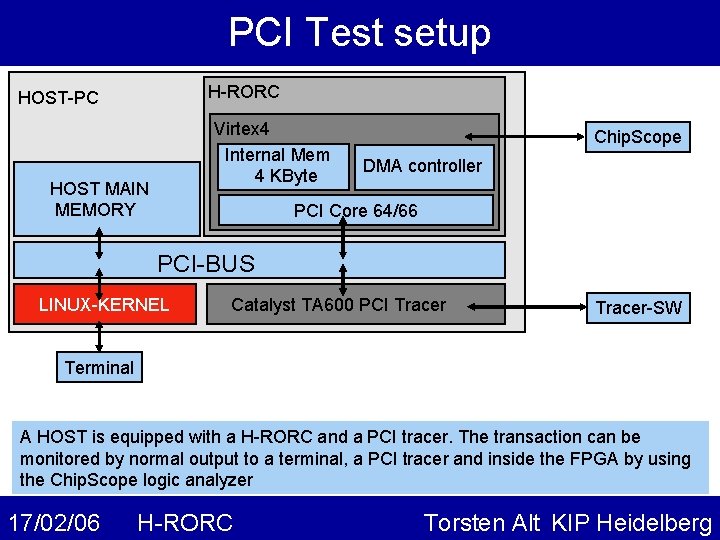

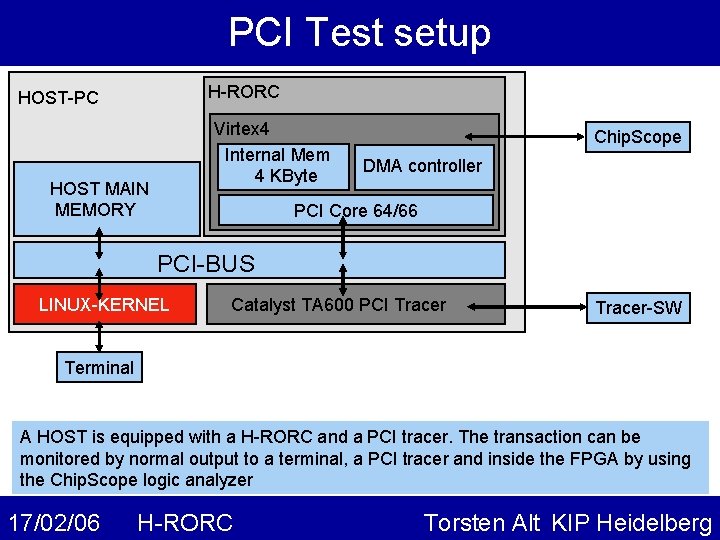

PCI Test setup H-RORC HOST-PC Virtex 4 Internal Mem 4 KByte HOST MAIN MEMORY Chip. Scope DMA controller PCI Core 64/66 PCI-BUS LINUX-KERNEL Catalyst TA 600 PCI Tracer-SW Terminal A HOST is equipped with a H-RORC and a PCI tracer. The transaction can be monitored by normal output to a terminal, a PCI tracer and inside the FPGA by using the Chip. Scope logic analyzer 17/02/06 H-RORC Torsten Alt KIP Heidelberg

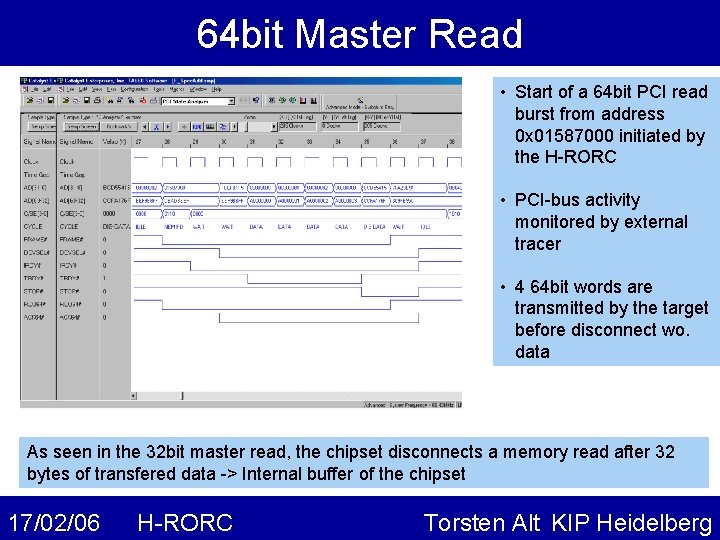

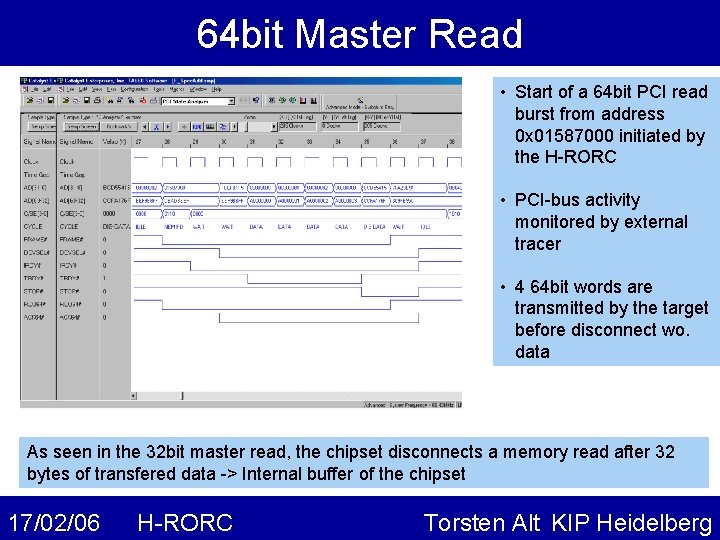

64 bit Master Read • Start of a 64 bit PCI read burst from address 0 x 01587000 initiated by the H-RORC • PCI-bus activity monitored by external tracer • 4 64 bit words are transmitted by the target before disconnect wo. data As seen in the 32 bit master read, the chipset disconnects a memory read after 32 bytes of transfered data -> Internal buffer of the chipset 17/02/06 H-RORC Torsten Alt KIP Heidelberg

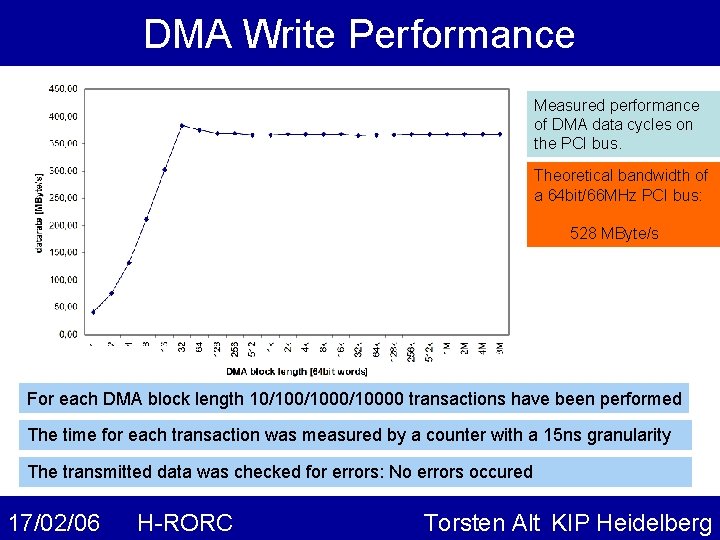

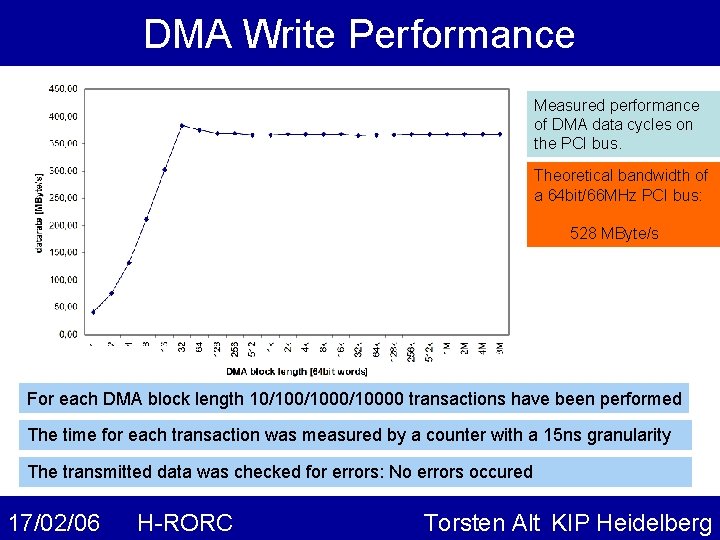

DMA Write Performance Measured performance of DMA data cycles on the PCI bus. Theoretical bandwidth of a 64 bit/66 MHz PCI bus: 528 MByte/s For each DMA block length 10/1000/10000 transactions have been performed The time for each transaction was measured by a counter with a 15 ns granularity The transmitted data was checked for errors: No errors occured 17/02/06 H-RORC Torsten Alt KIP Heidelberg

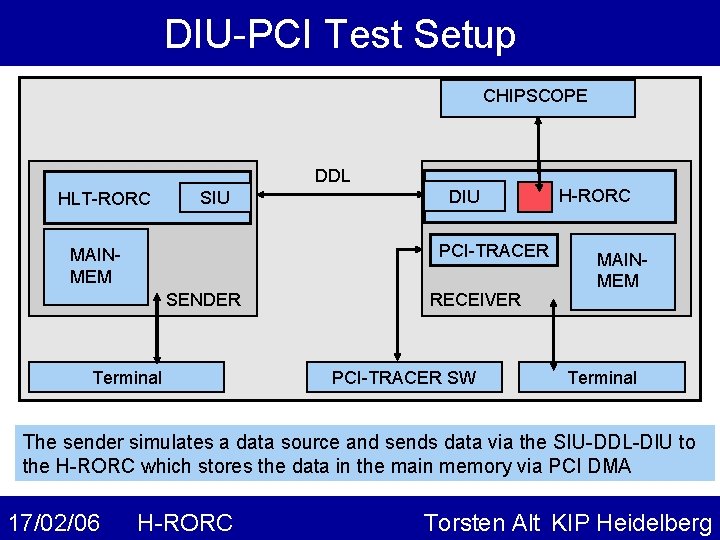

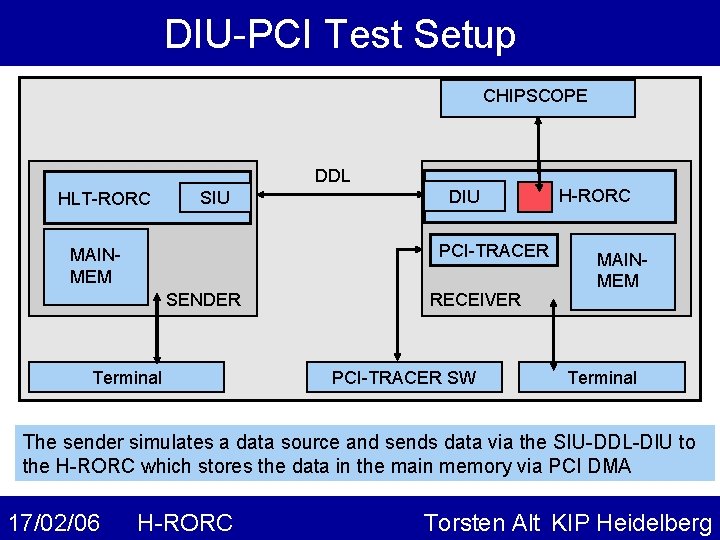

DIU-PCI Test Setup CHIPSCOPE DDL HLT-RORC SIU DIU PCI-TRACER MAINMEM SENDER Terminal RECEIVER PCI-TRACER SW H-RORC MAINMEM Terminal The sender simulates a data source and sends data via the SIU-DDL-DIU to the H-RORC which stores the data in the main memory via PCI DMA 17/02/06 H-RORC Torsten Alt KIP Heidelberg

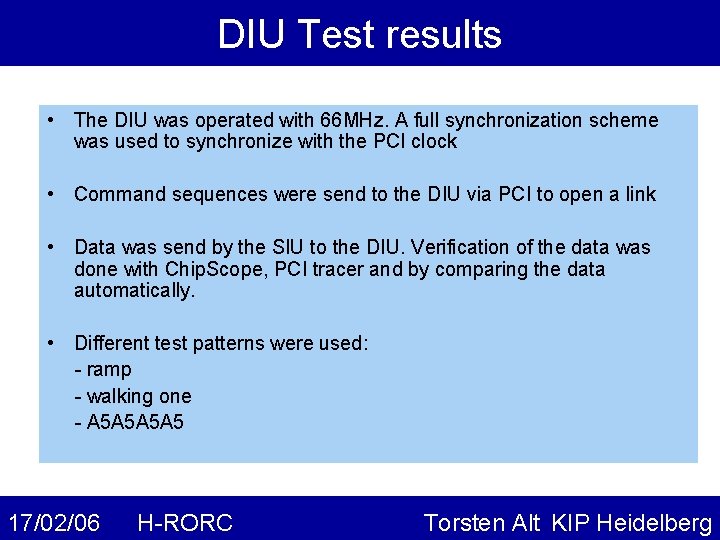

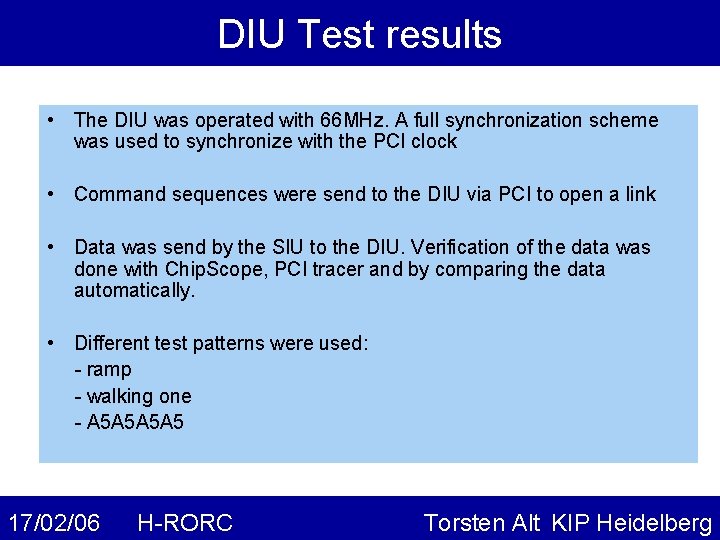

DIU Test results • The DIU was operated with 66 MHz. A full synchronization scheme was used to synchronize with the PCI clock • Command sequences were send to the DIU via PCI to open a link • Data was send by the SIU to the DIU. Verification of the data was done with Chip. Scope, PCI tracer and by comparing the data automatically. • Different test patterns were used: - ramp - walking one - A 5 A 5 17/02/06 H-RORC Torsten Alt KIP Heidelberg