Exceptions and Interrupts Storage and IO CS 3432

- Slides: 21

Exceptions and Interrupts Storage and I/O CS 3432 Fall 2020 Shirley Moore, Instructor svmoore@utep. edu November 19, 2020 1

Schedule for Today’s Class • Announcements • Midterm retake results • Quiz 4 on memory design due date extended to Friday, Nov. 20, 11: 59 pm and three attempts • Quiz 5 on pipeline hazards ready Friday, due after Thanksgiving • Memory design homework solutions and hints for Quiz 4 (10 minutes) • Exceptions and Interrupts (30 minutes) • Midterm retake part 2 problem discussion (30 minutes) • Wrapup • Homework for next class: P&H Exercises 4. 28, 4. 29, 4. 30 2

Definitions • exception – an unscheduled event that disrupts execution • Examples: undefined instruction, hardware malfunction • interrupt – an exception that comes from outside the processor • Example: I/O device request 3

Exception Handling • The processor saves the address of the “current” instruction and transfers control to the operating system at a specified address. • The operating system takes the appropriate action and either terminates the program or resumes its execution. • In order for the operating system to know how to handle the exception, it needs to know the reason for it. • Two ways to inform the operating system of the reason • Cause register with a field that indicates the reason • Vectored interrupts – the address to which control is transferred is determined by the cause of the exception 4

Exception Handling Hardware in RISC-V • Supervisor exception program counter (SEPC) • 64 -bit register that holds the address of the affected instruction • Supervisor exception cause register (SCAUSE) • 64 -bit register used to record the cause of the exception 5

Exceptions in a Pipelined Implementation • Exception treated as a control hazard • Must flush the instructions that follow the one where the exception occurred • Add ID. flush and EX. flush control lines • Add an input to the PC multiplexer that sends the RISC-V exception address 6

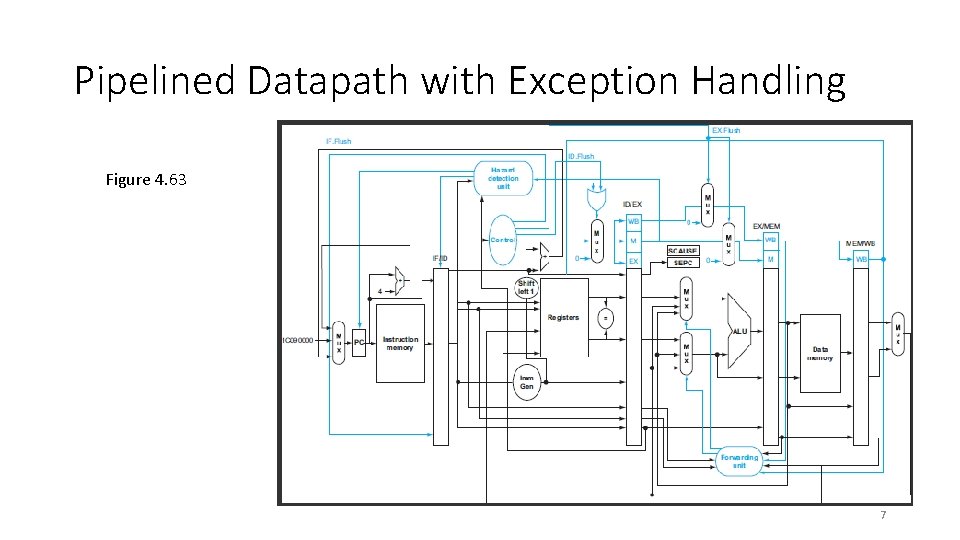

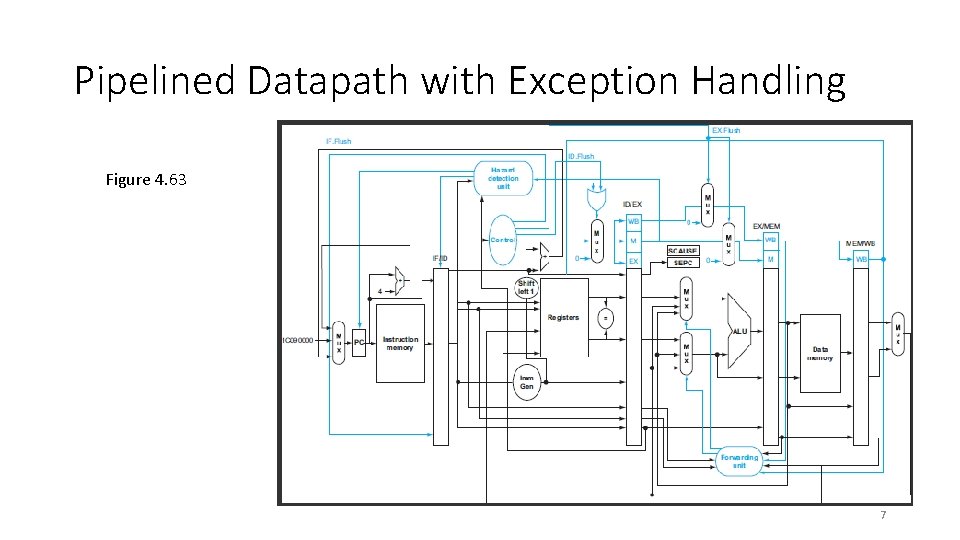

Pipelined Datapath with Exception Handling Figure 4. 63 7

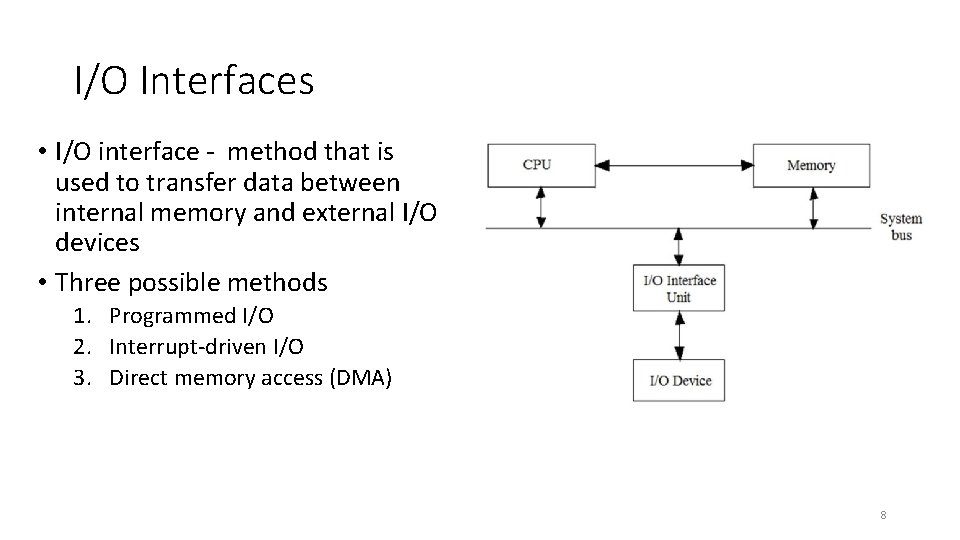

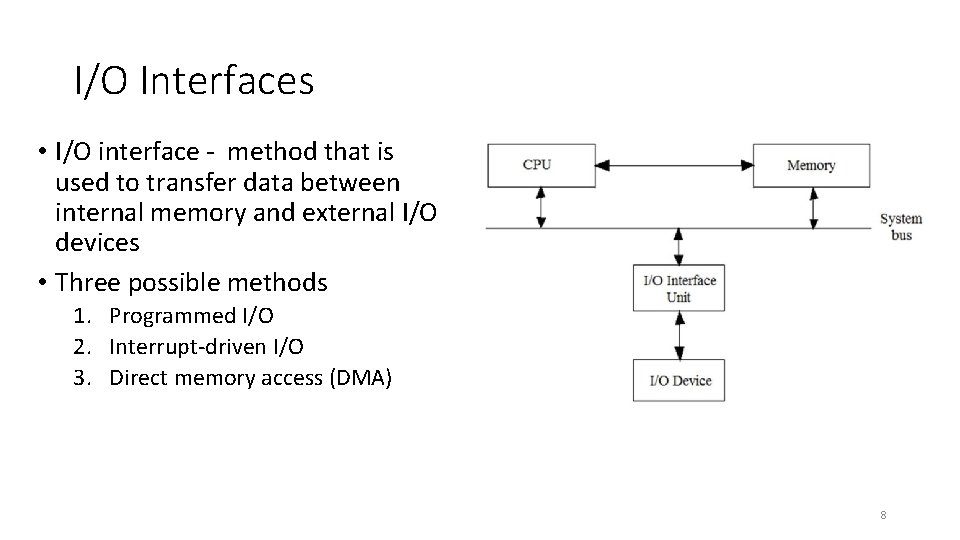

I/O Interfaces • I/O interface - method that is used to transfer data between internal memory and external I/O devices • Three possible methods 1. Programmed I/O 2. Interrupt-driven I/O 3. Direct memory access (DMA) 8

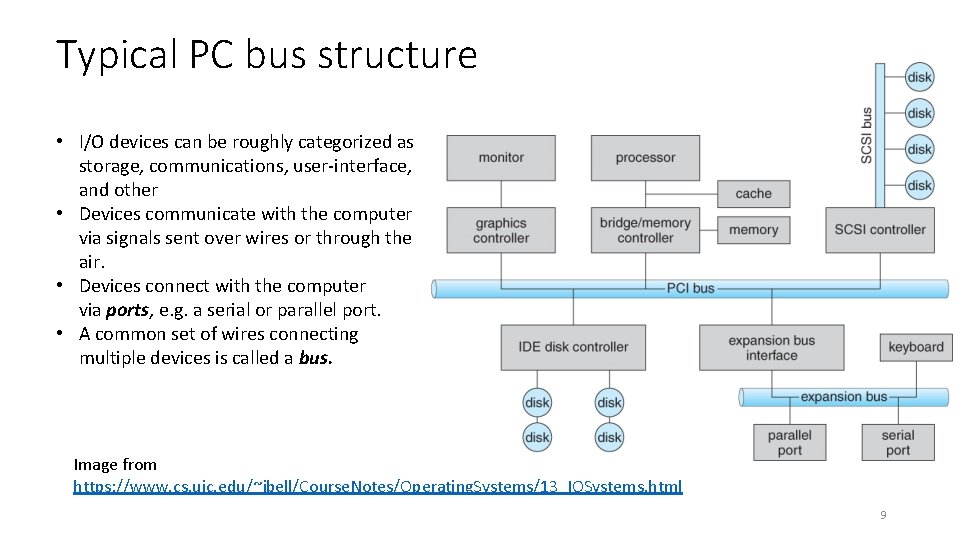

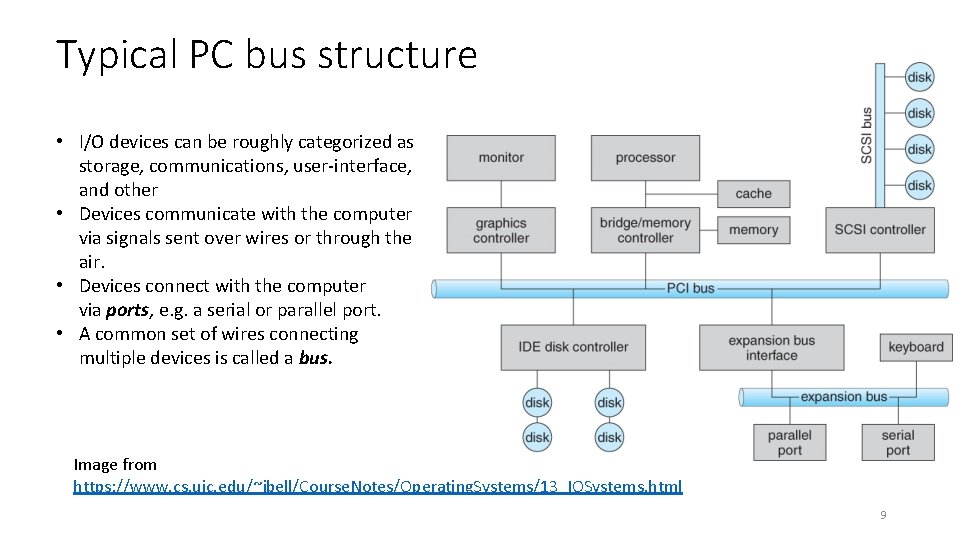

Typical PC bus structure • I/O devices can be roughly categorized as storage, communications, user-interface, and other • Devices communicate with the computer via signals sent over wires or through the air. • Devices connect with the computer via ports, e. g. a serial or parallel port. • A common set of wires connecting multiple devices is called a bus. Image from https: //www. cs. uic. edu/~jbell/Course. Notes/Operating. Systems/13_IOSystems. html 9

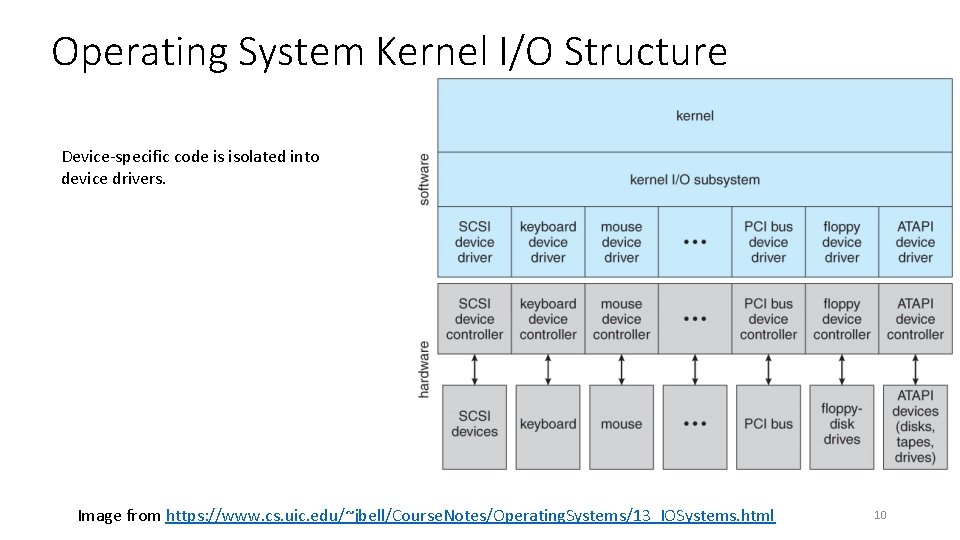

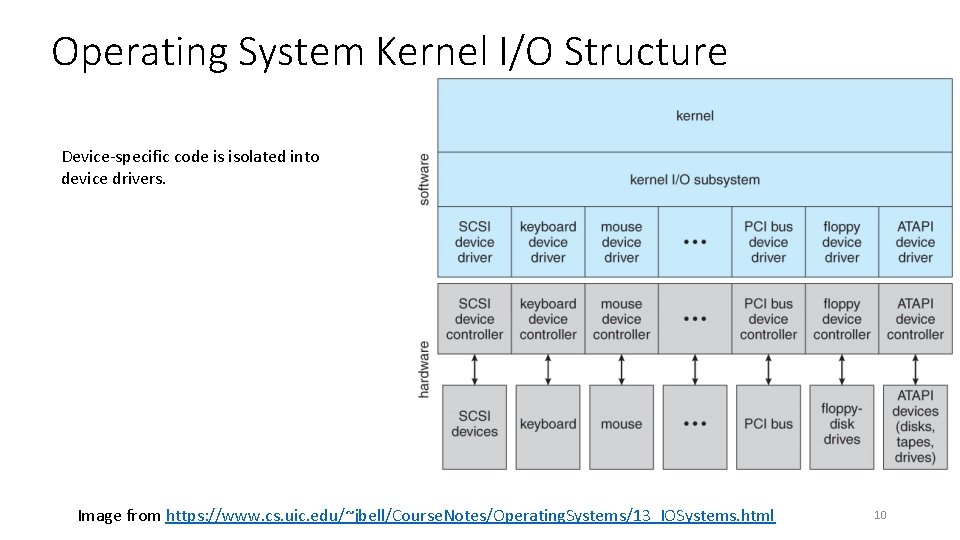

Operating System Kernel I/O Structure Device-specific code is isolated into device drivers. Image from https: //www. cs. uic. edu/~jbell/Course. Notes/Operating. Systems/13_IOSystems. html 10

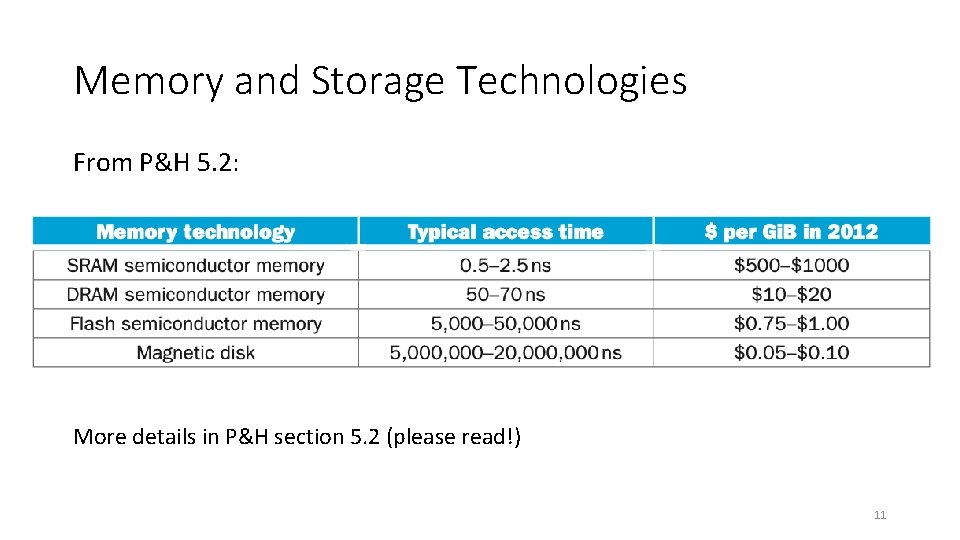

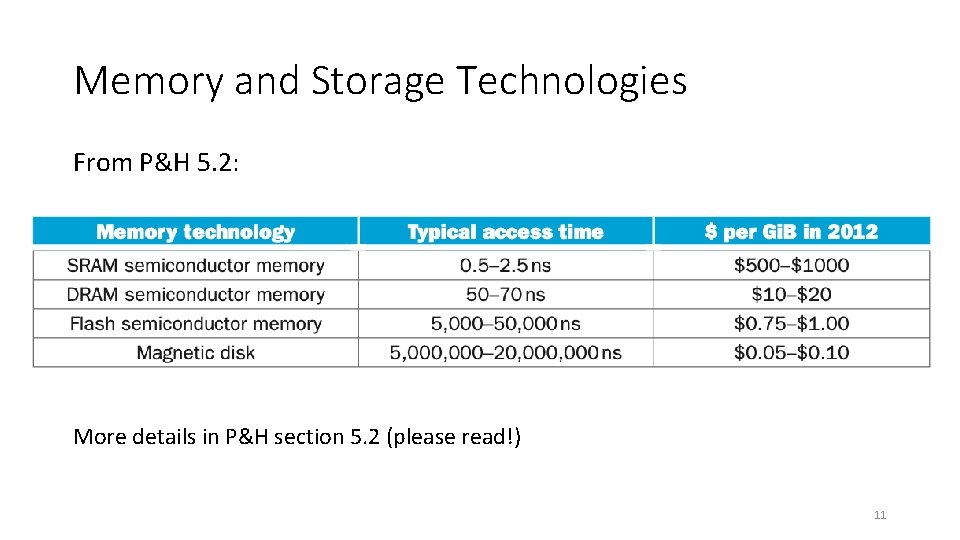

Memory and Storage Technologies From P&H 5. 2: More details in P&H section 5. 2 (please read!) 11

Programmed I/O • Data transfer carried out by I/O instructions that are part of the normal execution flow of the program being executed • Requires monitoring of the peripheral devices by the CPU, called polling • CPU repeatedly checks device status register to see if data is ready for transfer • Keeps the CPU busy-waiting instead of doing useful work 12

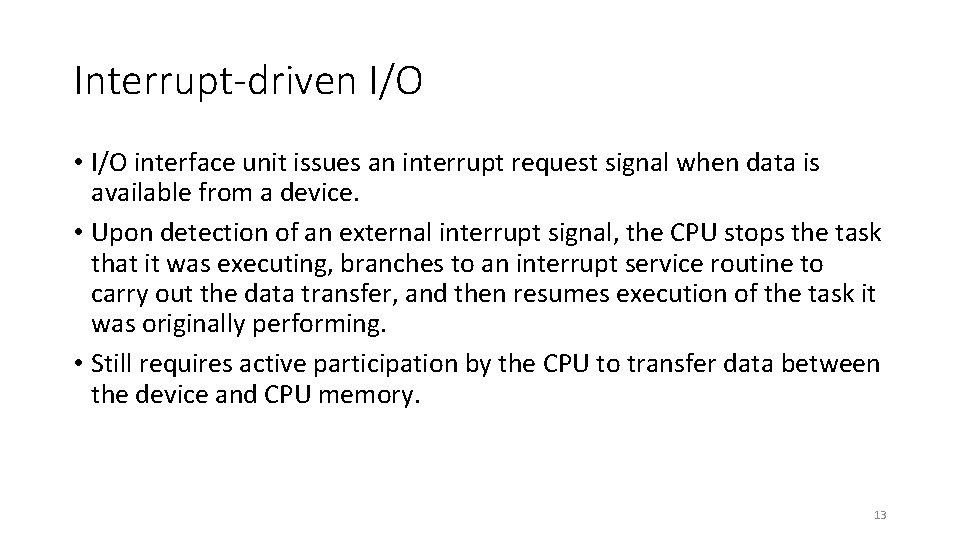

Interrupt-driven I/O • I/O interface unit issues an interrupt request signal when data is available from a device. • Upon detection of an external interrupt signal, the CPU stops the task that it was executing, branches to an interrupt service routine to carry out the data transfer, and then resumes execution of the task it was originally performing. • Still requires active participation by the CPU to transfer data between the device and CPU memory. 13

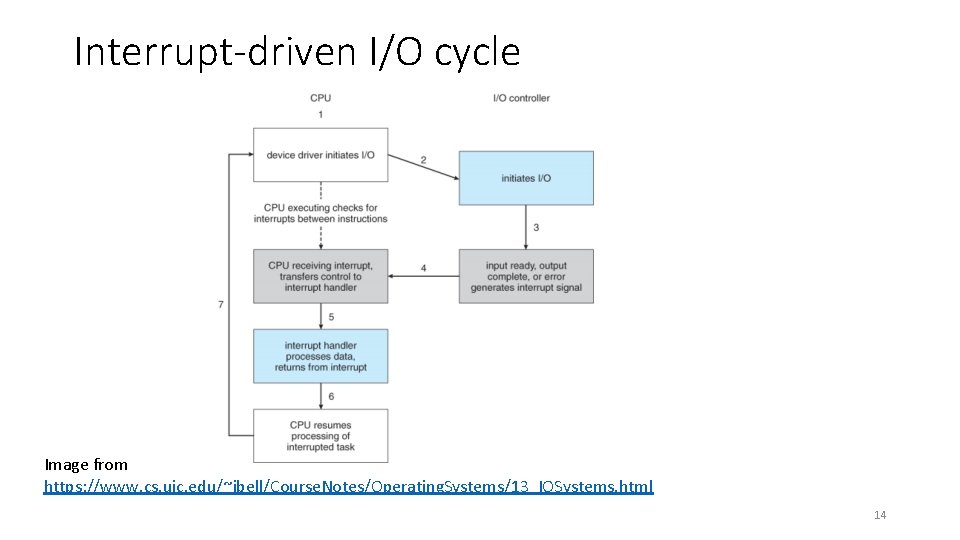

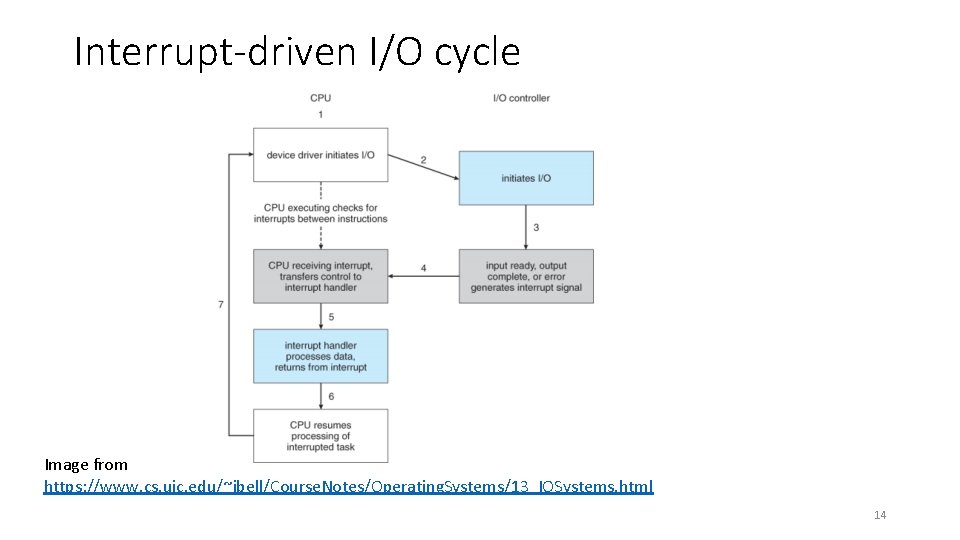

Interrupt-driven I/O cycle Image from https: //www. cs. uic. edu/~jbell/Course. Notes/Operating. Systems/13_IOSystems. html 14

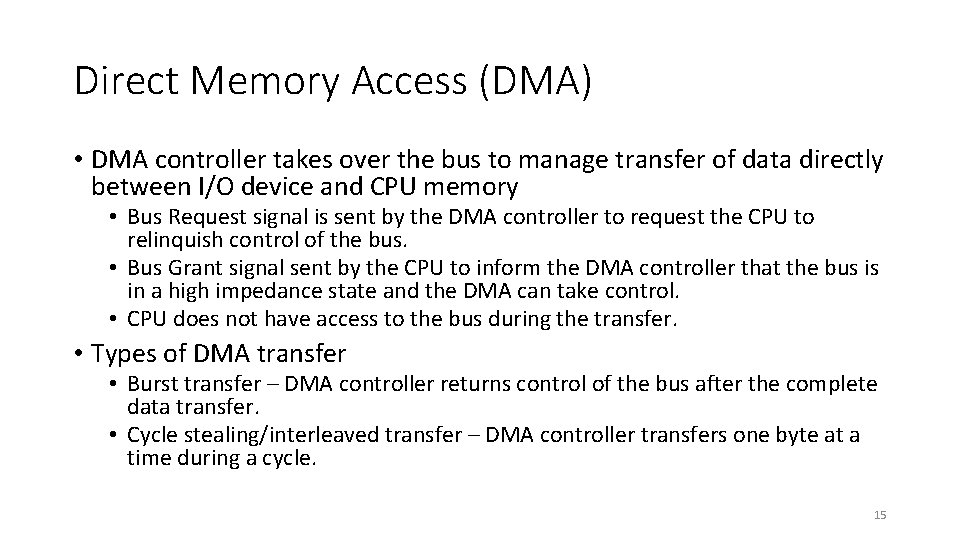

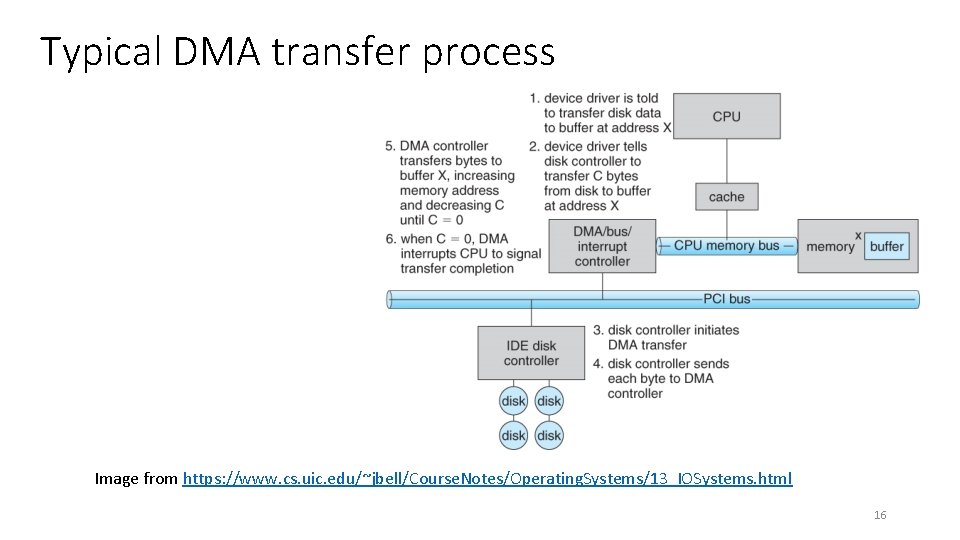

Direct Memory Access (DMA) • DMA controller takes over the bus to manage transfer of data directly between I/O device and CPU memory • Bus Request signal is sent by the DMA controller to request the CPU to relinquish control of the bus. • Bus Grant signal sent by the CPU to inform the DMA controller that the bus is in a high impedance state and the DMA can take control. • CPU does not have access to the bus during the transfer. • Types of DMA transfer • Burst transfer – DMA controller returns control of the bus after the complete data transfer. • Cycle stealing/interleaved transfer – DMA controller transfers one byte at a time during a cycle. 15

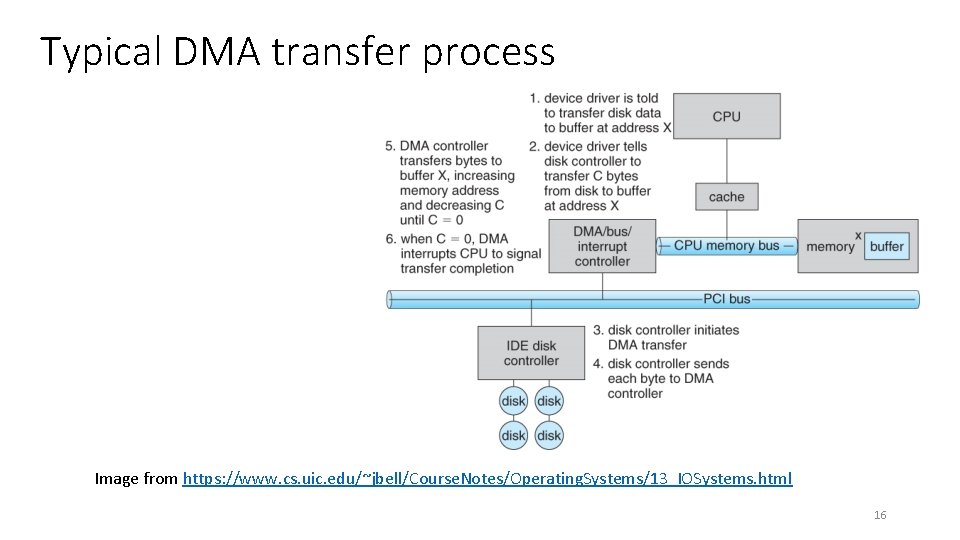

Typical DMA transfer process Image from https: //www. cs. uic. edu/~jbell/Course. Notes/Operating. Systems/13_IOSystems. html 16

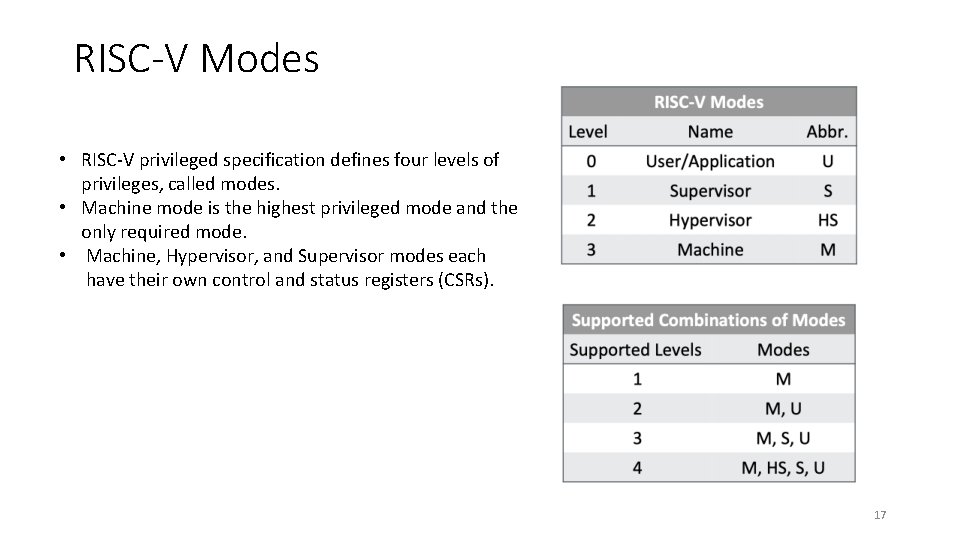

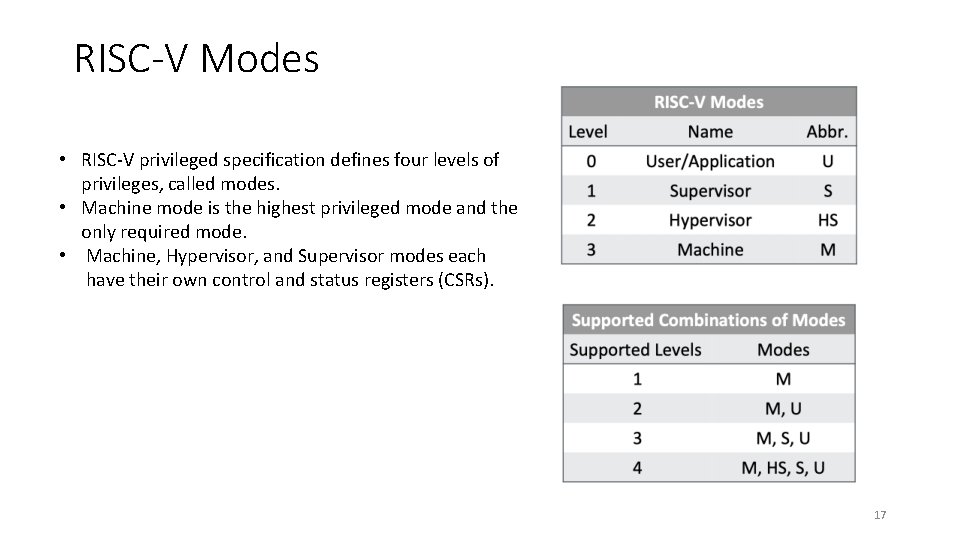

RISC-V Modes • RISC-V privileged specification defines four levels of privileges, called modes. • Machine mode is the highest privileged mode and the only required mode. • Machine, Hypervisor, and Supervisor modes each have their own control and status registers (CSRs). 17

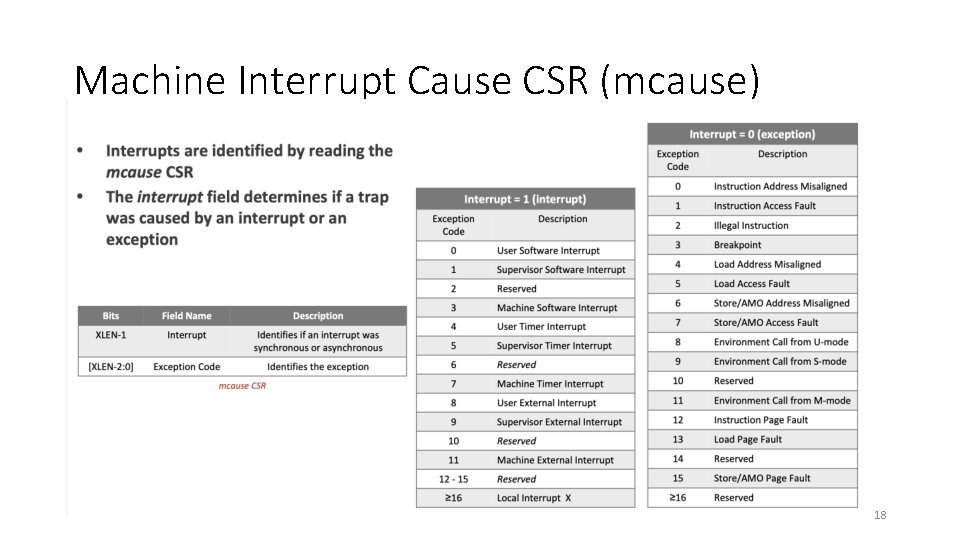

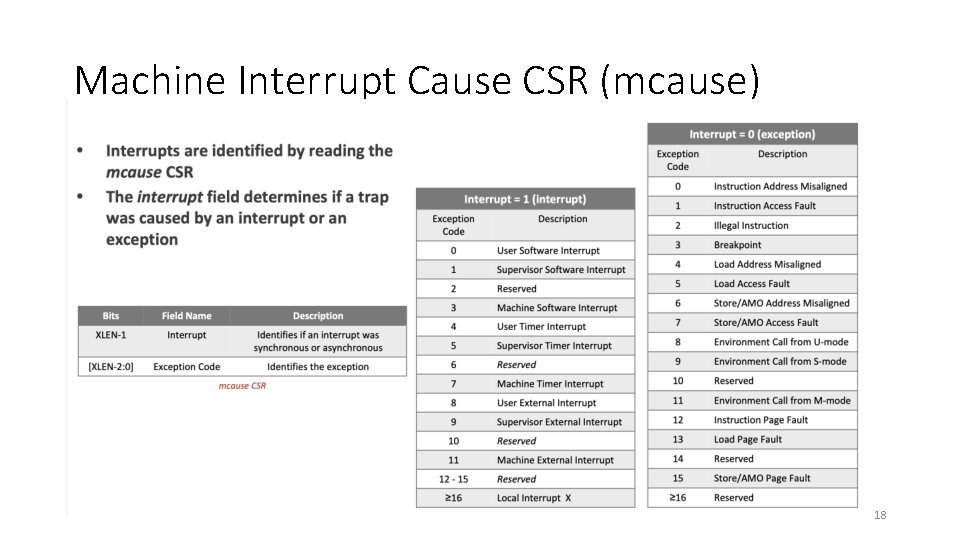

Machine Interrupt Cause CSR (mcause) 18

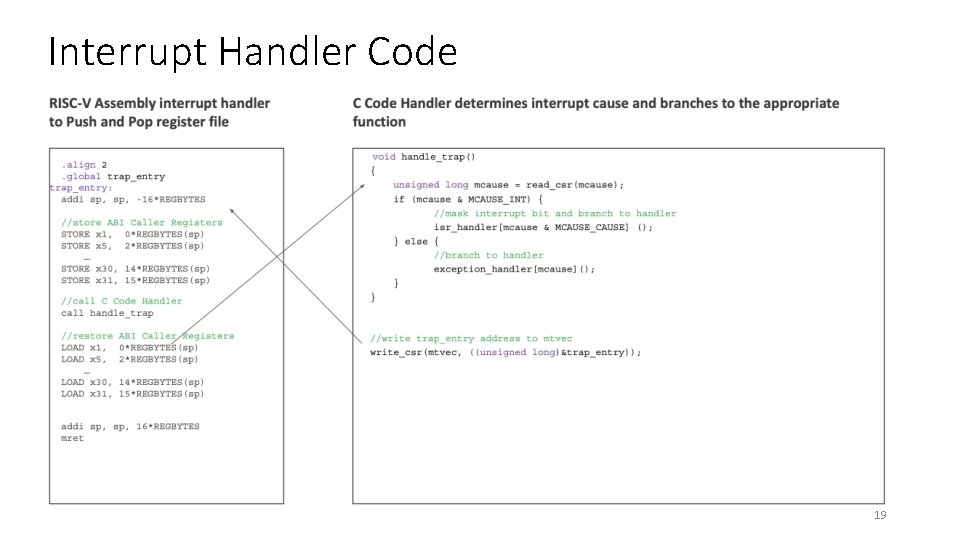

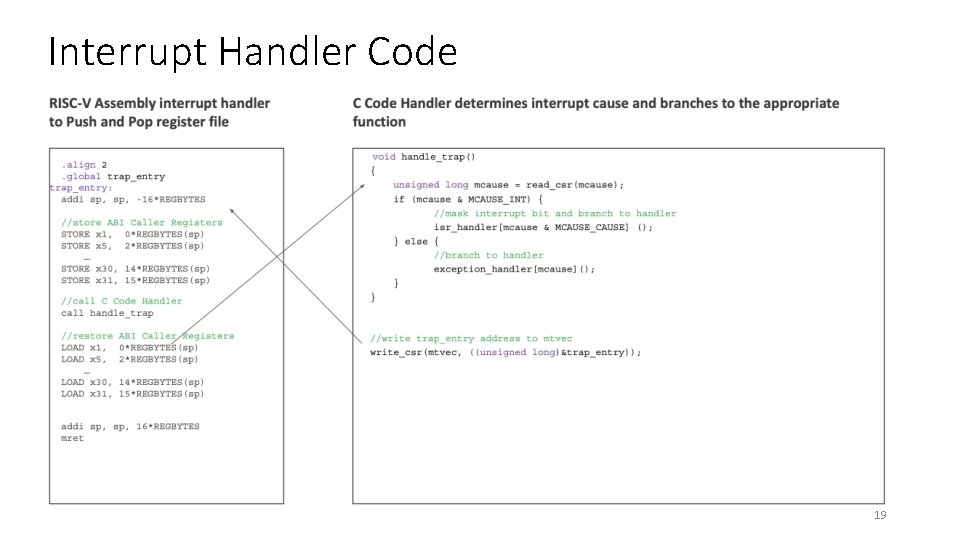

Interrupt Handler Code 19

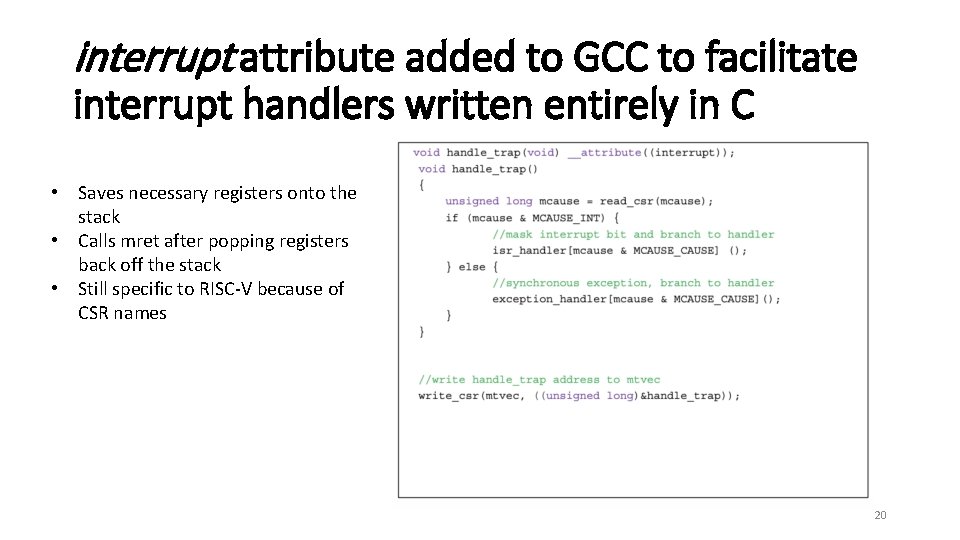

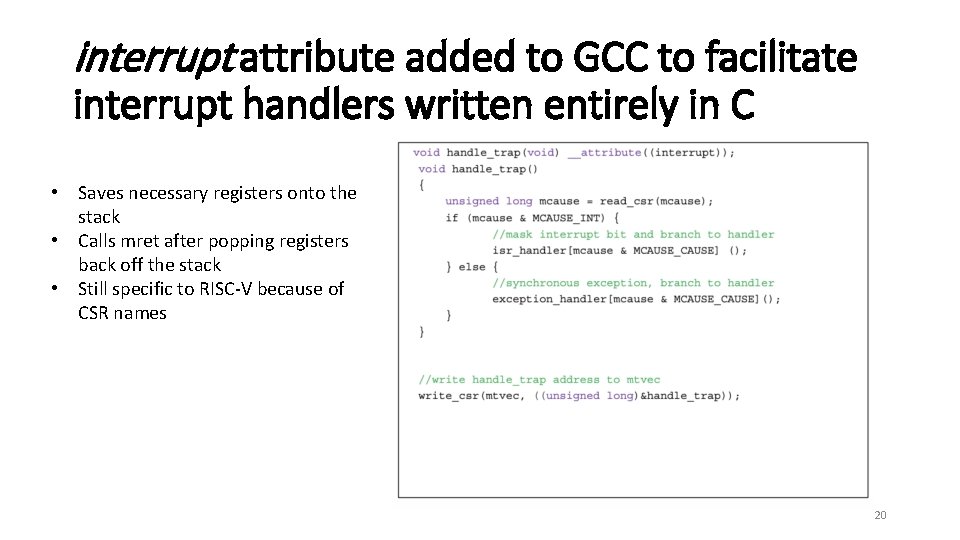

interrupt attribute added to GCC to facilitate interrupt handlers written entirely in C • Saves necessary registers onto the stack • Calls mret after popping registers back off the stack • Still specific to RISC-V because of CSR names 20

More information on RISC-V interrupt handling for embedded systems and microcontrollers • https: //sifive. com • Si. Five Interrupt Cookbook • https: //sifive. cdn. prismic. io/sifive/0 d 163928 -2128 -42 be-a 75 a 464 df 65 e 04 e 0_sifive-interrupt-cookbook. pdf 21