CSE 431 Computer Architecture Fall 2005 Lecture 01

- Slides: 20

CSE 431 Computer Architecture Fall 2005 Lecture 01: Introduction Mary Jane Irwin ( www. cse. psu. edu/~mji ) www. cse. psu. edu/~cg 431 [Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005, UCB] CSE 431 L 01 Introduction. 1 Irwin, PSU, 2005

Course Administration q Instructor: Mary Jane Irwin mji@cse. psu. edu 348 C IST Building Office Hrs: T 11: 30 -1: 00 & W 12: 30 -2: 00 q TA: q Labs: IST Accounts on machines in 218 and 222 q URL: www. cse. psu. edu/~cg 431 q Text: q Slides: Reetuparna Das rdas@cse. psu. edu 111 A IST Office Hrs: posted on the course web page Required: Computer Org and Design, 3 rd Edition, Patterson and Hennessy © 2005 Optional: Superscalar Microprocessor Design Johnson, © 1991 CSE 431 L 01 Introduction. 2 pdf on the course web page after. Irwin, lecture PSU, 2005

Grading Information q Grade determinates l Midterm Exam ~30% - Tuesday, October 18 th , 20: 15 to 22: 15, Location: 113 IST l Final Exam ~30% - ? ? ? , December ? ? th, ? ? : ? ? to ? ? : ? ? , Location TBD l Homeworks (5) ~30% - Due at the beginning of class (or, if its code to be submitted electronically, by 17: 00 on the due date). No late assignments will be accepted. l Class participation & pop quizzes ~10% Let me know about midterm exam conflicts ASAP q Grades will be posted on the course homepage q l l Must submit email request for change of grade after discussions with the TA (Homeworks/Quizzes) or instructor (Exams) December 9 th deadline for filing grade corrections; no requests for grade changes will be accepted after this date CSE 431 L 01 Introduction. 3 Irwin, PSU, 2005

Course Content q Content l q Course goals l q Principles of computer architecture: CPU datapath and control unit design (single-issue pipelined, superscalar, VLIW), memory hierarchies and design, I/O organization and design, advanced processor design (multiprocessors and SMT) To learn the organizational paradigms that determine the capabilities and performance of computer systems. To understand the interactions between the computer’s architecture and its software so that future software designers (compiler writers, operating system designers, database programmers, …) can achieve the best cost-performance trade -offs and so that future architects understand the effects of their design choices on software applications. Course prerequisites l CSE 331. Computer Organization and Design CSE 431 L 01 Introduction. 4 Irwin, PSU, 2005

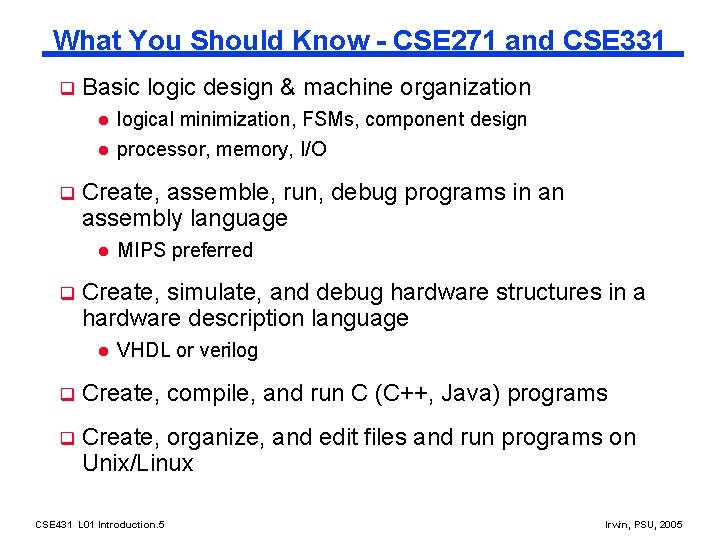

What You Should Know - CSE 271 and CSE 331 q Basic logic design & machine organization l l q Create, assemble, run, debug programs in an assembly language l q logical minimization, FSMs, component design processor, memory, I/O MIPS preferred Create, simulate, and debug hardware structures in a hardware description language l VHDL or verilog q Create, compile, and run C (C++, Java) programs q Create, organize, and edit files and run programs on Unix/Linux CSE 431 L 01 Introduction. 5 Irwin, PSU, 2005

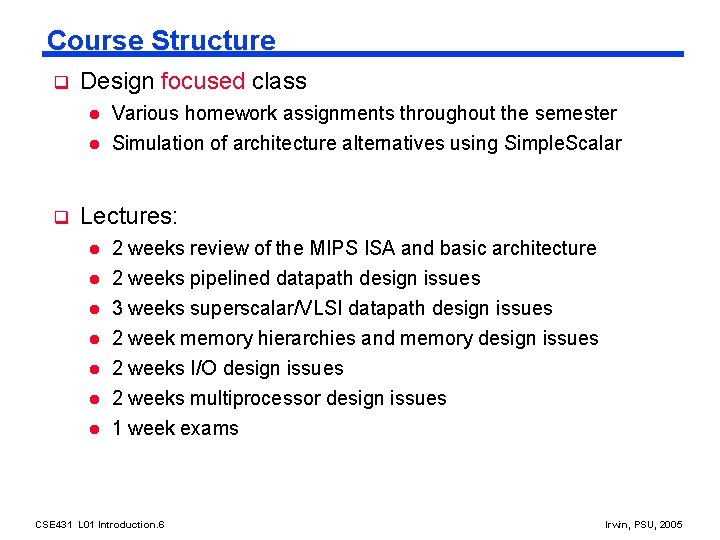

Course Structure q Design focused class l l q Various homework assignments throughout the semester Simulation of architecture alternatives using Simple. Scalar Lectures: l 2 weeks review of the MIPS ISA and basic architecture l 2 weeks pipelined datapath design issues l 3 weeks superscalar/VLSI datapath design issues l 2 week memory hierarchies and memory design issues 2 weeks I/O design issues 2 weeks multiprocessor design issues 1 week exams l l l CSE 431 L 01 Introduction. 6 Irwin, PSU, 2005

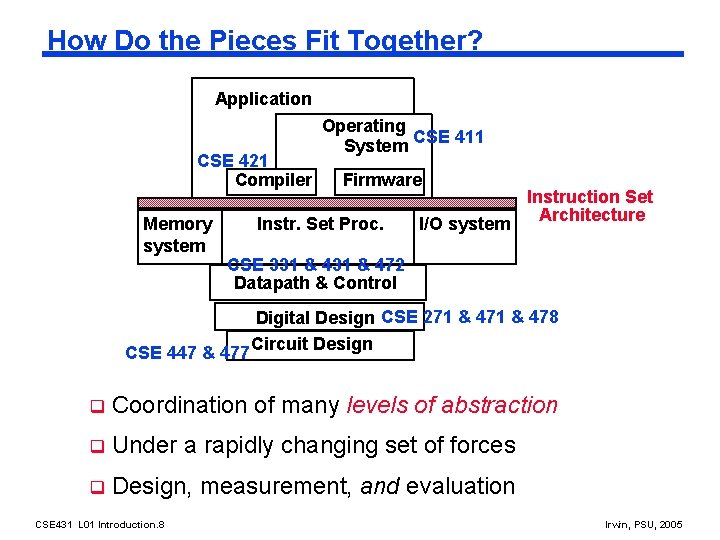

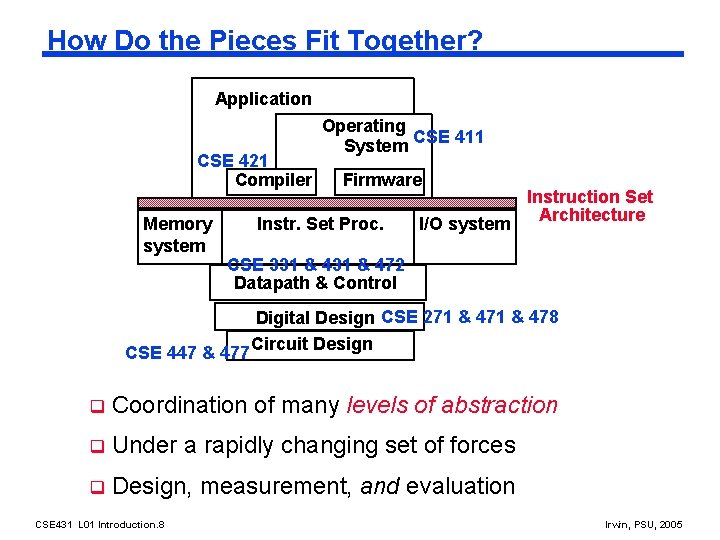

How Do the Pieces Fit Together? Application CSE 421 Compiler Memory system Operating CSE 411 System Firmware Instr. Set Proc. Instruction Set Architecture I/O system CSE 331 & 472 Datapath & Control CSE 447 & 477 Digital Design CSE 271 & 478 Circuit Design q Coordination of many levels of abstraction q Under a rapidly changing set of forces q Design, measurement, and evaluation CSE 431 L 01 Introduction. 8 Irwin, PSU, 2005

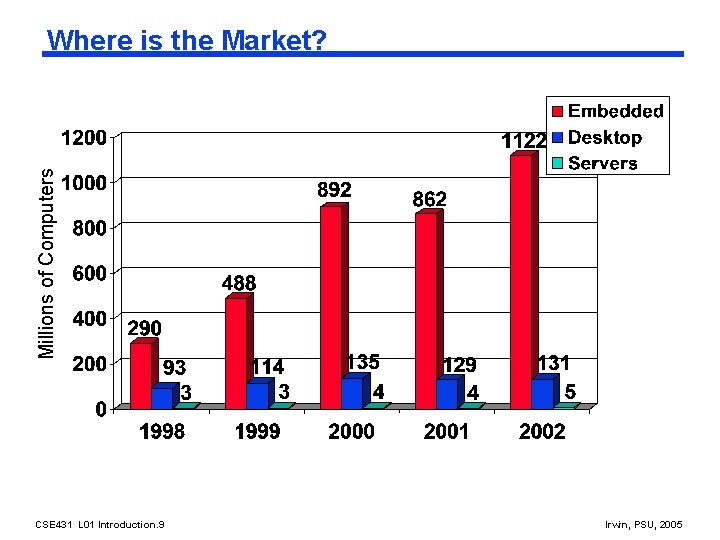

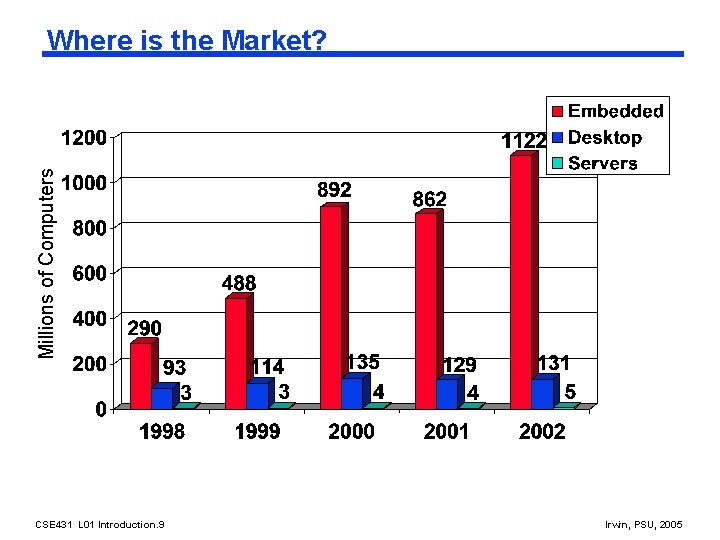

Millions of Computers Where is the Market? CSE 431 L 01 Introduction. 9 Irwin, PSU, 2005

By the architecture of a system, I mean the complete and detailed specification of the user interface. … As Blaauw has said, “Where architecture tells what happens, implementation tells how it is made to happen. ” The Mythical Man-Month, Brooks, pg 45 CSE 431 L 01 Introduction. 10 Irwin, PSU, 2005

Instruction Set Architecture (ISA) q ISA: An abstract interface between the hardware and the lowest level software of a machine that encompasses all the information necessary to write a machine language program that will run correctly, including instructions, registers, memory access, I/O, and so on. “. . . the attributes of a [computing] system as seen by the programmer, i. e. , the conceptual structure and functional behavior, as distinct from the organization of the data flows and controls, the logic design, and the physical implementation. ” – Amdahl, Blaauw, and Brooks, 1964 l q Enables implementations of varying cost and performance to run identical software ABI (application binary interface): The user portion of the instruction set plus the operating system interfaces used by application programmers. Defines a standard for binary portability across computers. CSE 431 L 01 Introduction. 11 Irwin, PSU, 2005

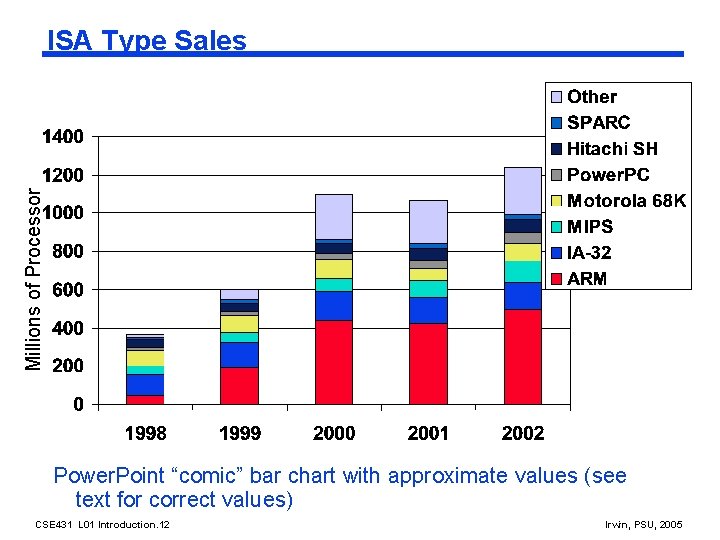

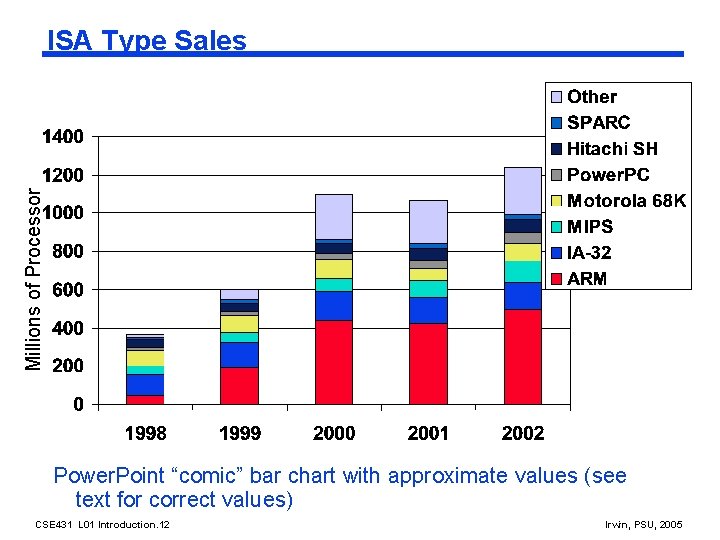

Millions of Processor ISA Type Sales Power. Point “comic” bar chart with approximate values (see text for correct values) CSE 431 L 01 Introduction. 12 Irwin, PSU, 2005

Moore’s Law q In 1965, Gordon Moore predicted that the number of transistors that can be integrated on a die would double every 18 to 24 months (i. e. , grow exponentially with time). q Amazingly visionary – million transistor/chip barrier was crossed in the 1980’s. l 2300 transistors, 1 MHz clock (Intel 4004) - 1971 l 16 Million transistors (Ultra Sparc III) 42 Million transistors, 2 GHz clock (Intel Xeon) – 2001 55 Million transistors, 3 GHz, 130 nm technology, 250 mm 2 die (Intel Pentium 4) - 2004 140 Million transistor (HP PA-8500) l l l CSE 431 L 01 Introduction. 13 Irwin, PSU, 2005

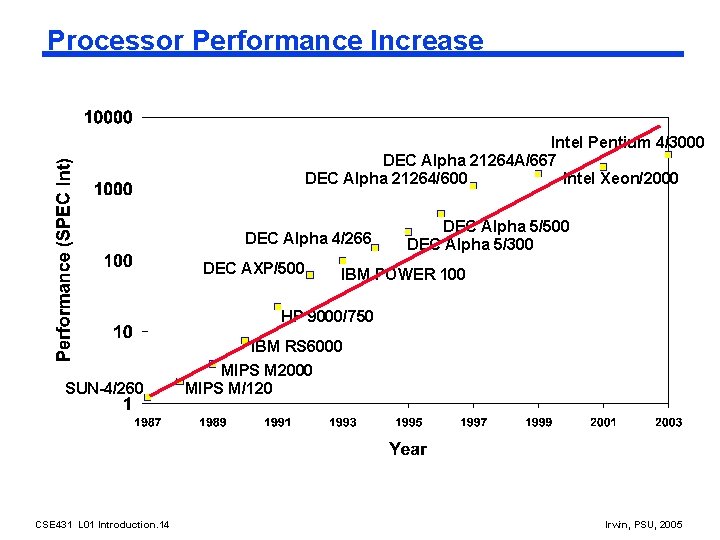

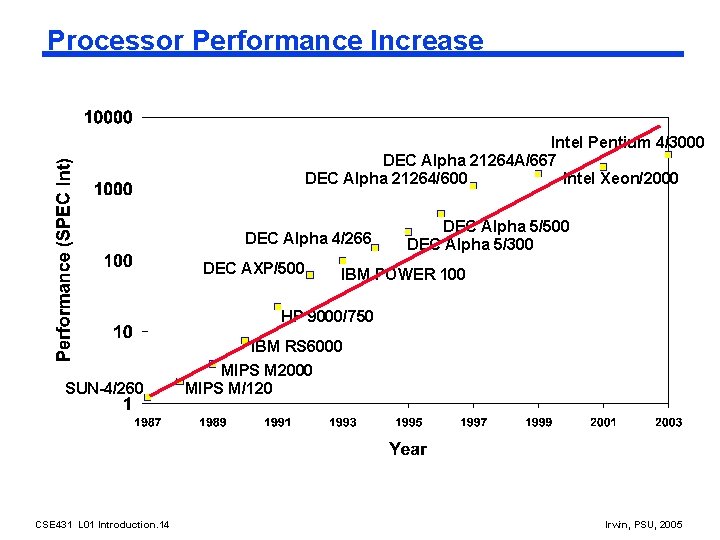

Processor Performance Increase Intel Pentium 4/3000 DEC Alpha 21264 A/667 DEC Alpha 21264/600 Intel Xeon/2000 DEC Alpha 4/266 DEC AXP/500 DEC Alpha 5/300 IBM POWER 100 HP 9000/750 SUN-4/260 CSE 431 L 01 Introduction. 14 IBM RS 6000 MIPS M 2000 MIPS M/120 Irwin, PSU, 2005

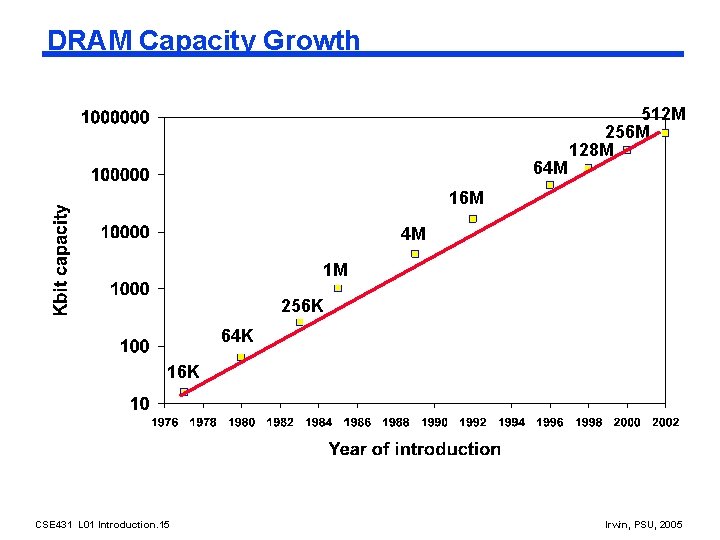

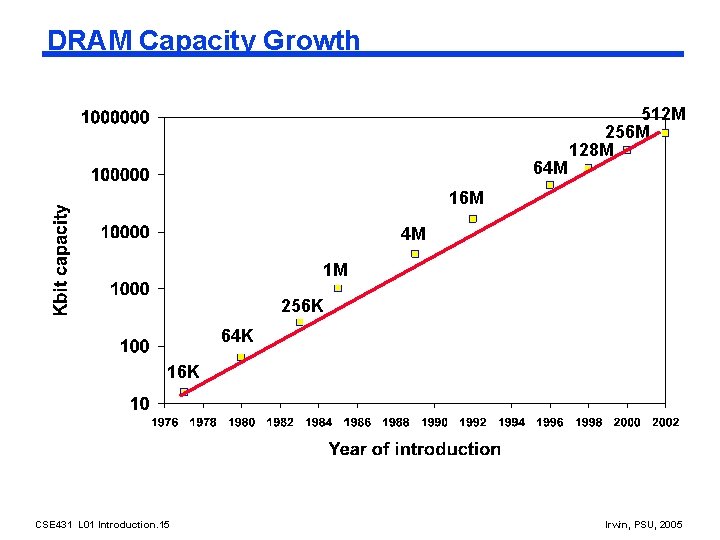

DRAM Capacity Growth 64 M 512 M 256 M 128 M 16 M 4 M 1 M 256 K 64 K 16 K CSE 431 L 01 Introduction. 15 Irwin, PSU, 2005

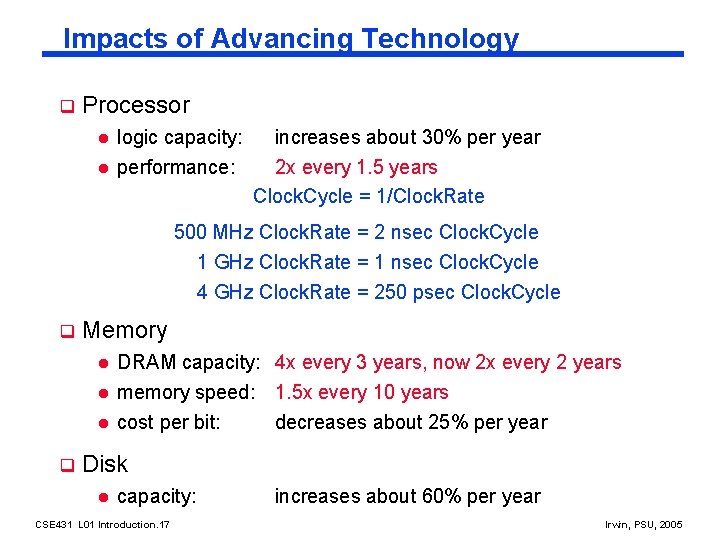

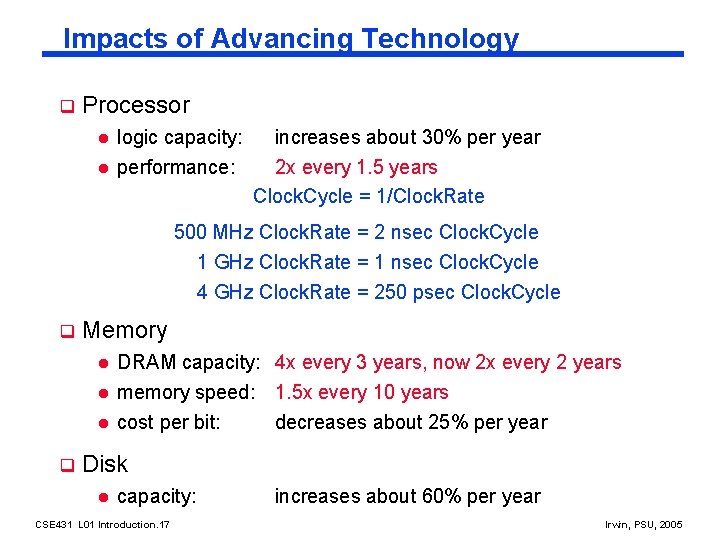

Impacts of Advancing Technology q Processor l l logic capacity: performance: increases about 30% per year 2 x every 1. 5 years Clock. Cycle = 1/Clock. Rate 500 MHz Clock. Rate = 2 nsec Clock. Cycle 1 GHz Clock. Rate = 1 nsec Clock. Cycle 4 GHz Clock. Rate = 250 psec Clock. Cycle q Memory l l l q DRAM capacity: 4 x every 3 years, now 2 x every 2 years memory speed: 1. 5 x every 10 years cost per bit: decreases about 25% per year Disk l capacity: CSE 431 L 01 Introduction. 17 increases about 60% per year Irwin, PSU, 2005

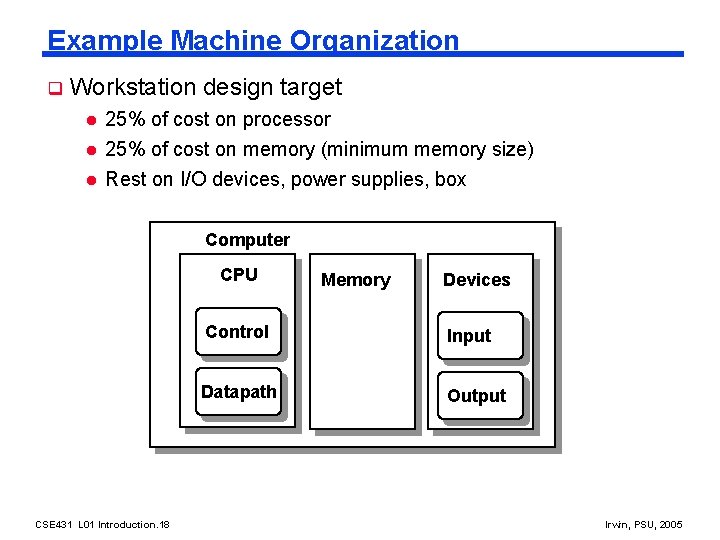

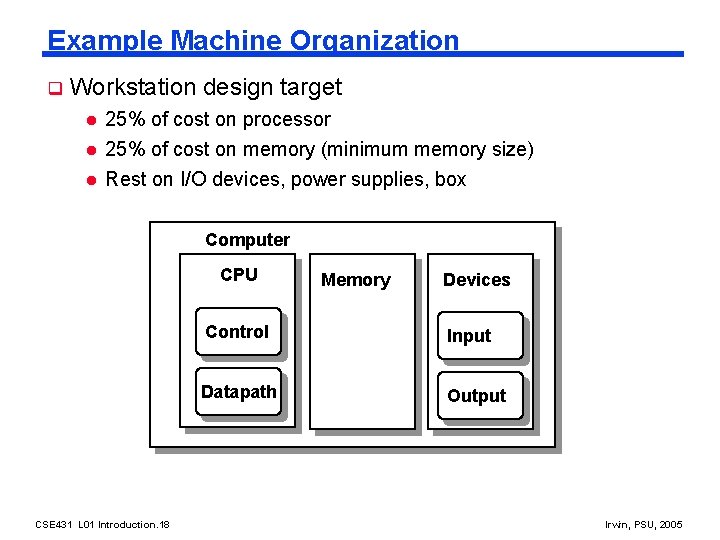

Example Machine Organization q Workstation design target l l l 25% of cost on processor 25% of cost on memory (minimum memory size) Rest on I/O devices, power supplies, box Computer CPU CSE 431 L 01 Introduction. 18 Memory Devices Control Input Datapath Output Irwin, PSU, 2005

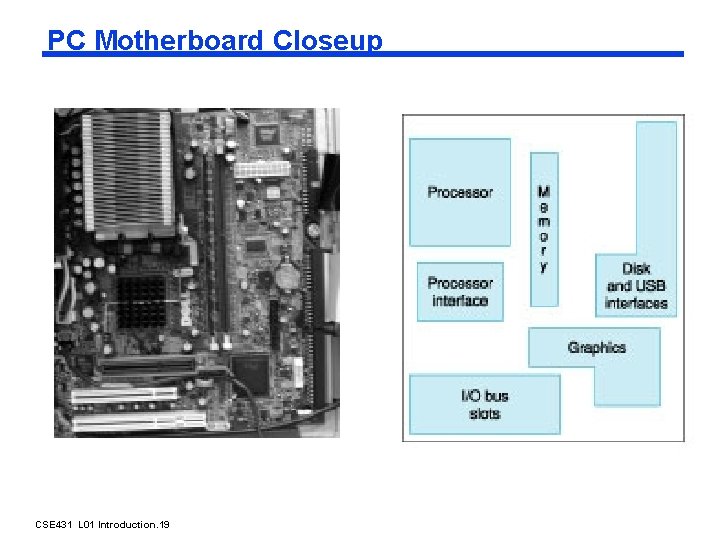

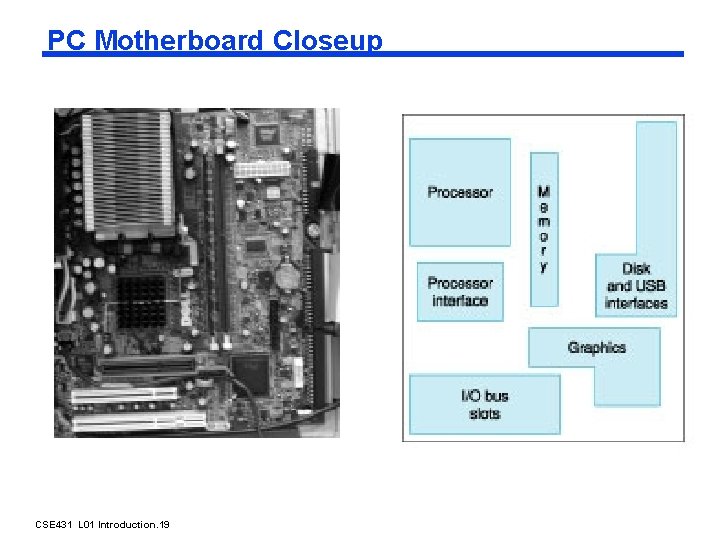

PC Motherboard Closeup CSE 431 L 01 Introduction. 19 Irwin, PSU, 2005

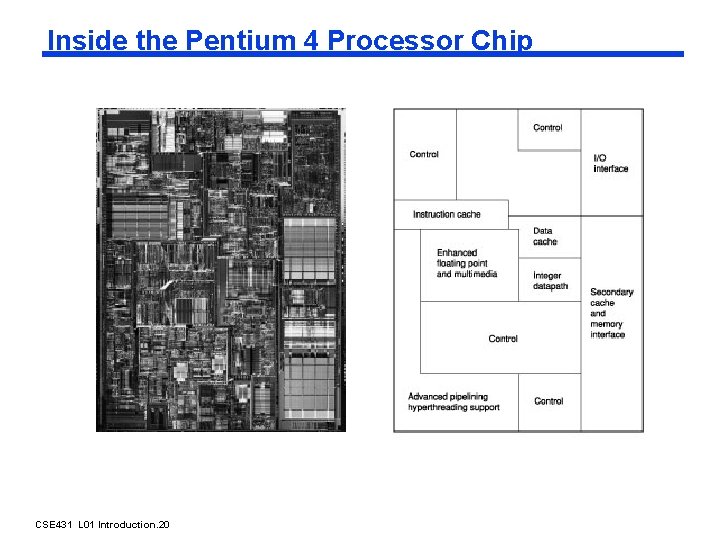

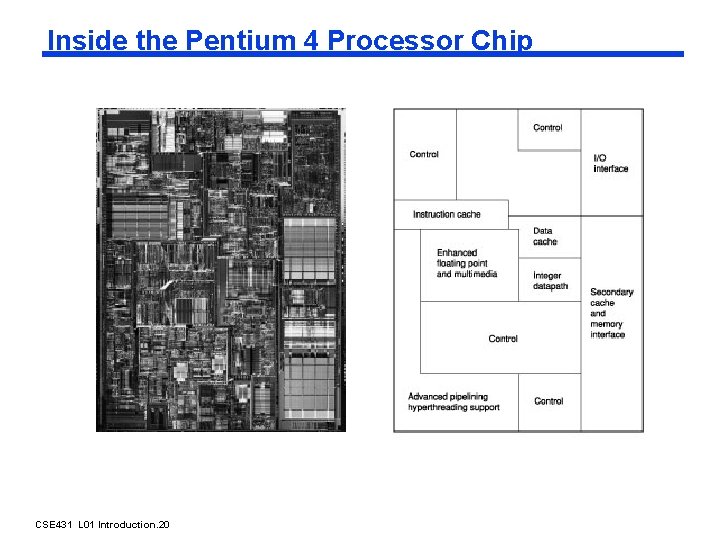

Inside the Pentium 4 Processor Chip CSE 431 L 01 Introduction. 20 Irwin, PSU, 2005

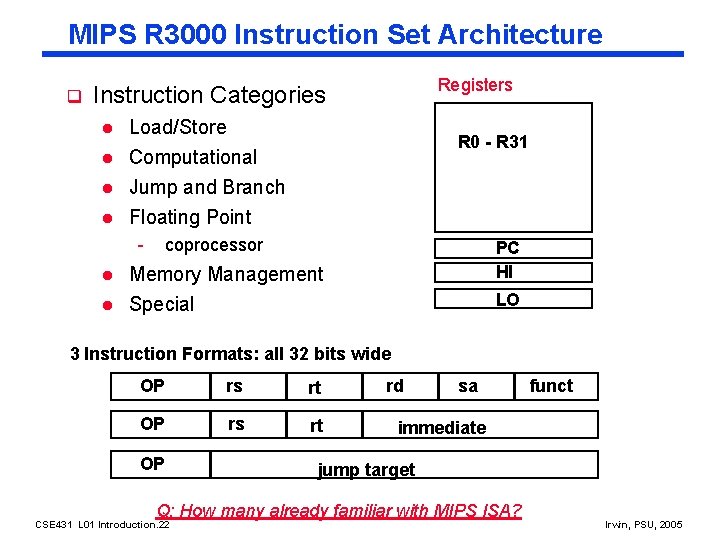

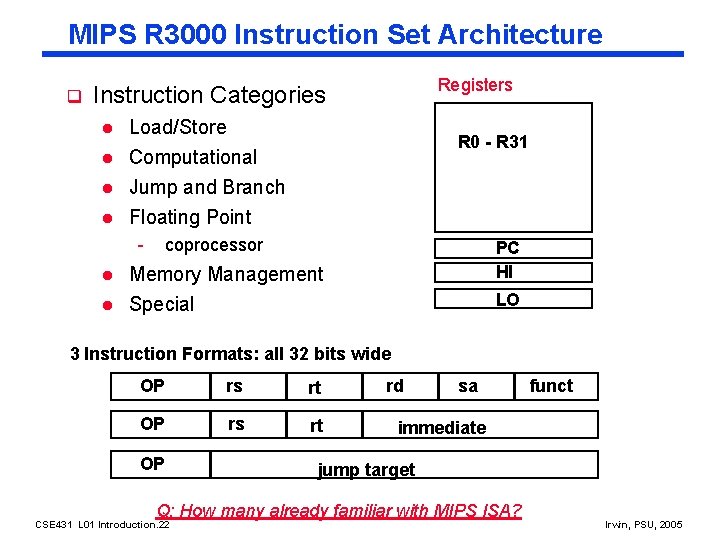

MIPS R 3000 Instruction Set Architecture q Registers Instruction Categories l Load/Store Computational Jump and Branch l Floating Point l l - R 0 - R 31 coprocessor l Memory Management PC HI l Special LO 3 Instruction Formats: all 32 bits wide OP rs rt OP rd sa immediate jump target Q: How many already familiar with MIPS ISA? CSE 431 L 01 Introduction. 22 funct Irwin, PSU, 2005

Next Lecture and Reminders q Next lecture l MIPS ISA Review - Reading assignment – PH, Chapter 2 q Reminders l HW 1 out next lecture, due September 13 th l Evening midterm exam scheduled - Tuesday, October 18 th , 20: 15 to 22: 15, Location 113 IST - Please let me know ASAP (via email) if you have a conflict CSE 431 L 01 Introduction. 23 Irwin, PSU, 2005