CSE 171 Lab 11 Digital Voltmeter Objective a

CSE 171 Lab 11 Digital Voltmeter

Objective: • a Xilinx XC 95108 PC 84 CPLD chip • a PLDT-3 Trainer Board with a 4 MHz clock • an ADC 0831 Analog-to Digital Converter chip

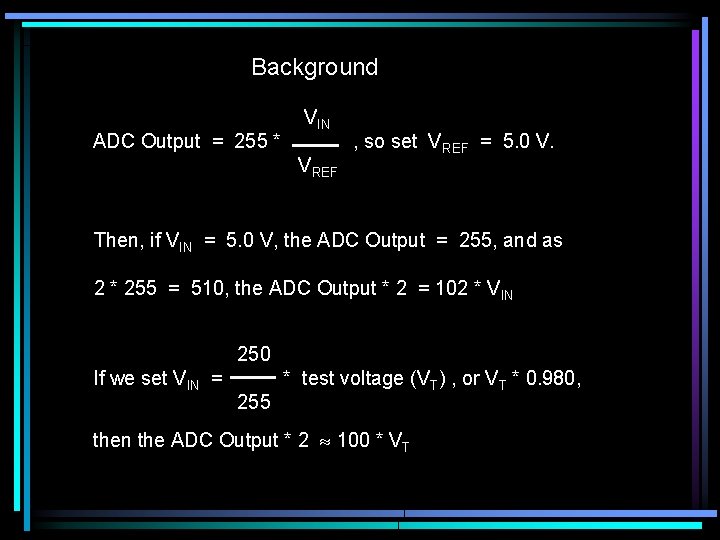

Background ADC Output = 255 * VIN V REF , so set VREF = 5. 0 V. Then, if VIN = 5. 0 V, the ADC Output = 255, and as 2 * 255 = 510, the ADC Output * 2 = 102 * VIN 250 If we set VIN = 255 * test voltage (VT) , or VT * 0. 980, then the ADC Output * 2 100 * VT

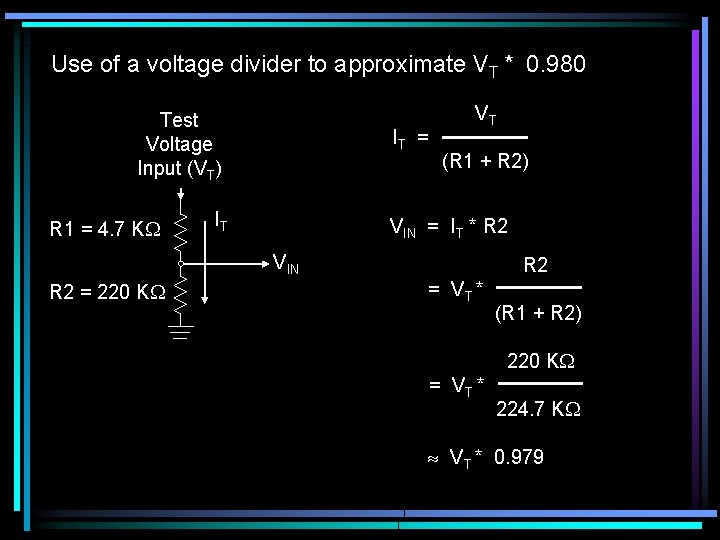

Use of a voltage divider to approximate VT * 0. 980 Test Voltage Input (VT) R 1 = 4. 7 K IT = IT VT (R 1 + R 2) VIN = IT * R 2 VIN R 2 = 220 K R 2 = VT * (R 1 + R 2) 220 K = VT * 224. 7 K VT * 0. 979

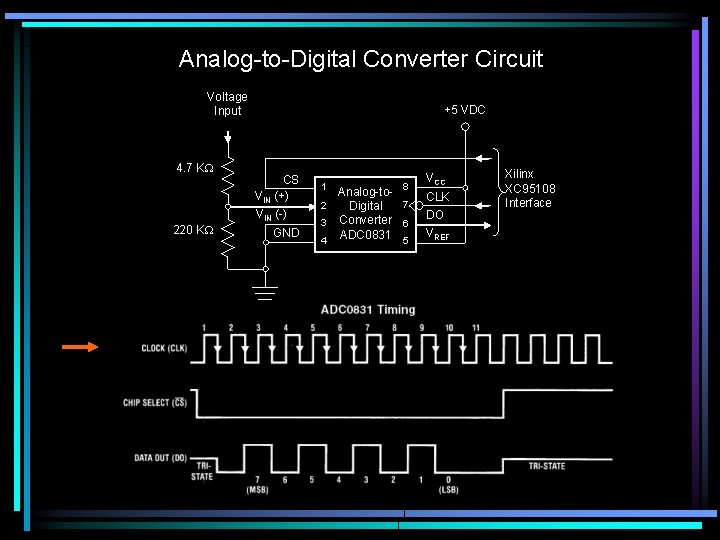

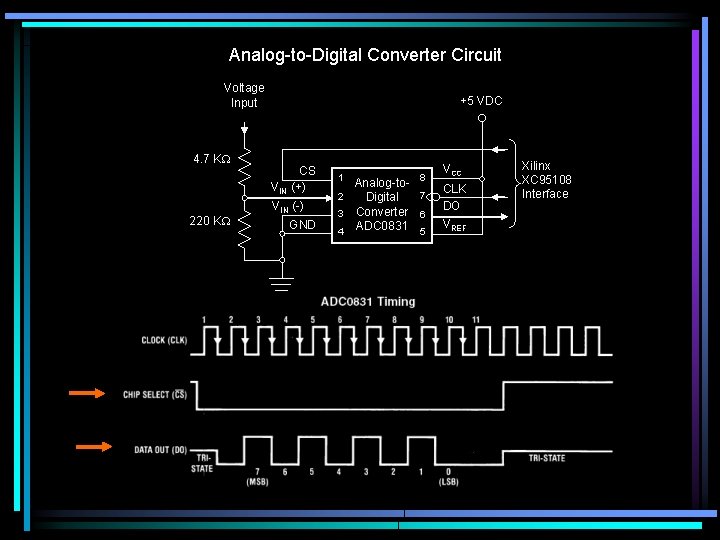

Analog-to-Digital Converter Circuit Voltage Input 4. 7 K +5 VDC CS VIN (+) VIN (-) 220 K GND 1 8 Analog-to 7 2 Digital 3 Converter 6 ADC 0831 5 4 VCC CLK DO VREF Xilinx XC 95108 Interface

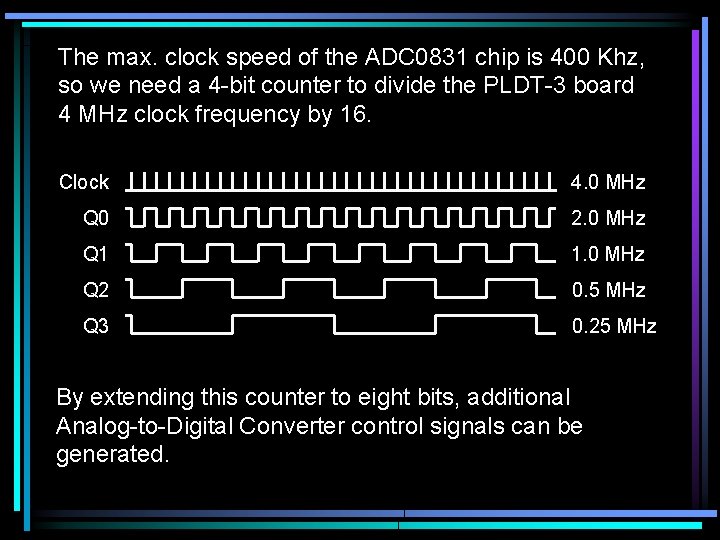

The max. clock speed of the ADC 0831 chip is 400 Khz, so we need a 4 -bit counter to divide the PLDT-3 board 4 MHz clock frequency by 16. Clock 4. 0 MHz Q 0 2. 0 MHz Q 1 1. 0 MHz Q 2 0. 5 MHz Q 3 0. 25 MHz By extending this counter to eight bits, additional Analog-to-Digital Converter control signals can be generated.

Analog-to-Digital Converter Circuit Voltage Input 4. 7 K +5 VDC CS VIN (+) VIN (-) 220 K GND 1 8 Analog-to 7 2 Digital 3 Converter 6 ADC 0831 5 4 VCC CLK DO VREF Xilinx XC 95108 Interface

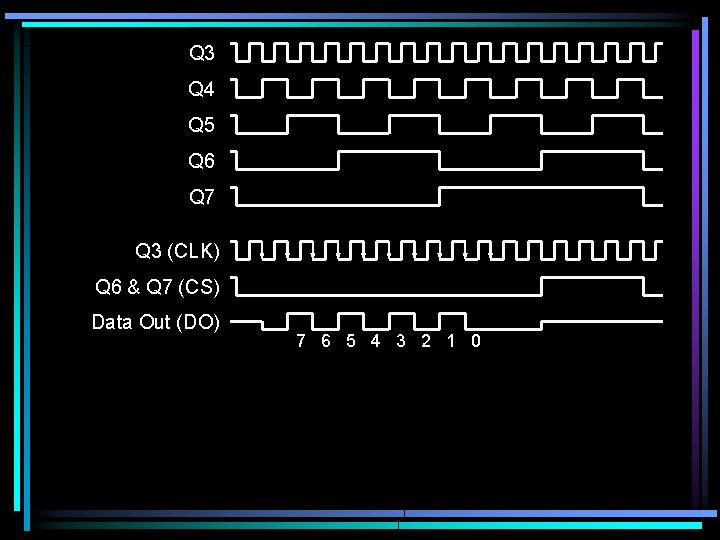

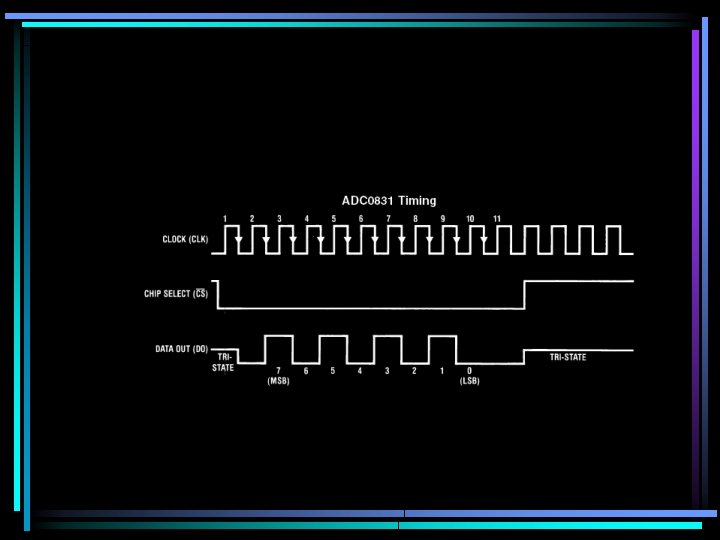

Q 3 Q 4 Q 5 Q 6 Q 7 Q 3 (CLK) Q 6 & Q 7 (CS) Data Out (DO) 7 6 5 4 3 2 1 0

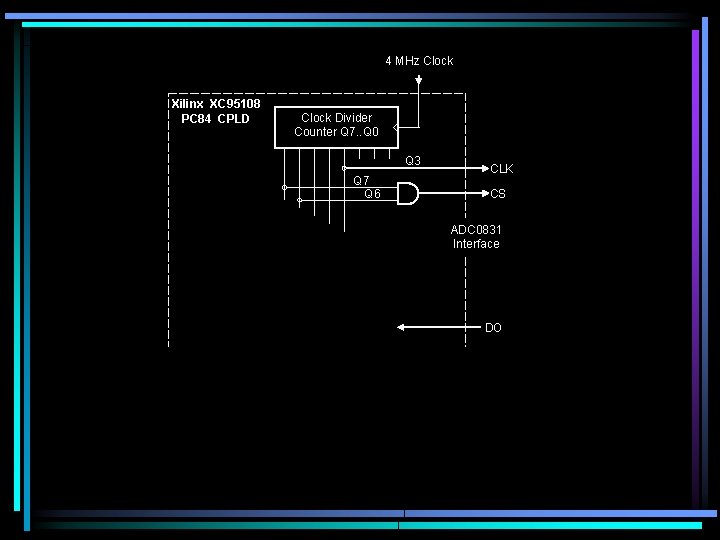

4 MHz Clock Xilinx XC 95108 PC 84 CPLD Clock Divider Counter Q 7. . Q 0 Q 3 Q 7 Q 6 CLK CS ADC 0831 Interface DO

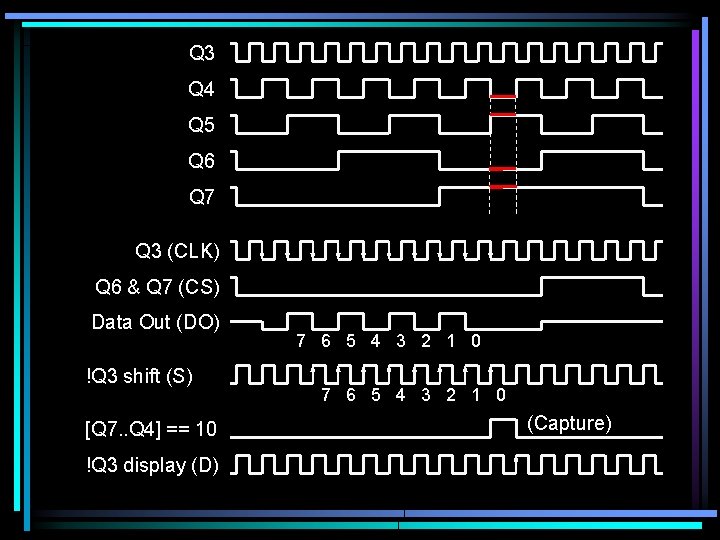

Q 3 Q 4 Q 5 Q 6 Q 7 Q 3 (CLK) Q 6 & Q 7 (CS) Data Out (DO) !Q 3 shift (S) [Q 7. . Q 4] == 10 !Q 3 display (D) 7 6 5 4 3 2 1 0 (Capture)

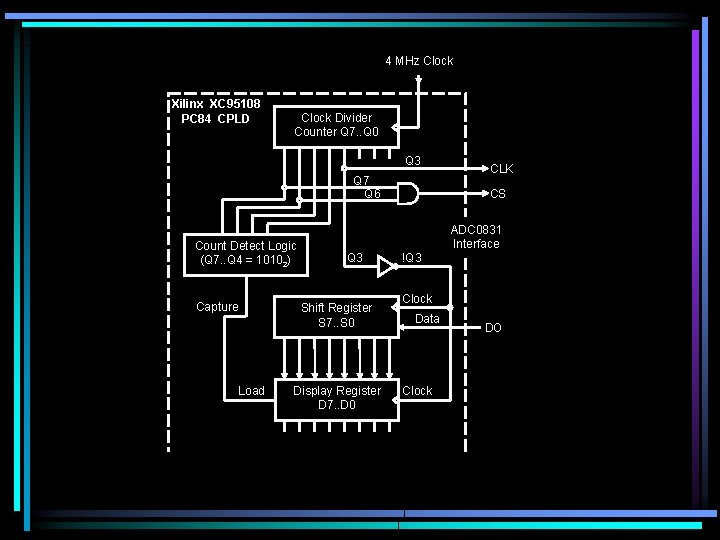

4 MHz Clock Xilinx XC 95108 PC 84 CPLD Clock Divider Counter Q 7. . Q 0 Q 3 Q 7 Q 6 Count Detect Logic (Q 7. . Q 4 = 10102) Capture CS ADC 0831 Interface Q 3 Shift Register S 7. . S 0 Load CLK Display Register D 7. . D 0 !Q 3 Clock Data Clock DO

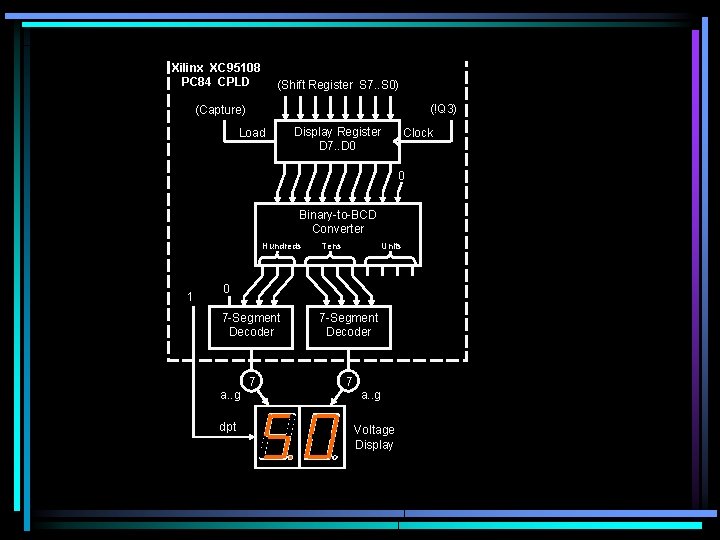

Xilinx XC 95108 PC 84 CPLD (Shift Register S 7. . S 0) (!Q 3) (Capture) Load Display Register D 7. . D 0 Clock 0 Binary-to-BCD Converter Hundreds 1 Tens Units 0 7 -Segment Decoder 7 7 a. . g dpt a. . g Voltage Display

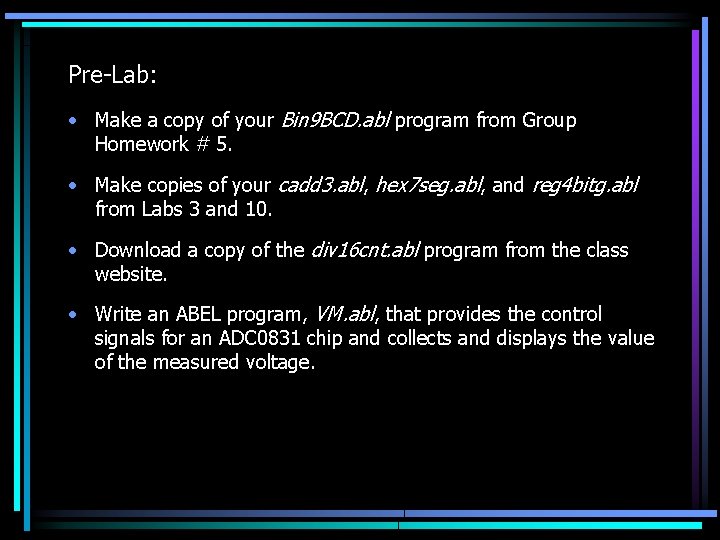

Pre-Lab: • Make a copy of your Bin 9 BCD. abl program from Group Homework # 5. • Make copies of your cadd 3. abl, hex 7 seg. abl, and reg 4 bitg. abl from Labs 3 and 10. • Download a copy of the div 16 cnt. abl program from the class website. • Write an ABEL program, VM. abl, that provides the control signals for an ADC 0831 chip and collects and displays the value of the measured voltage.

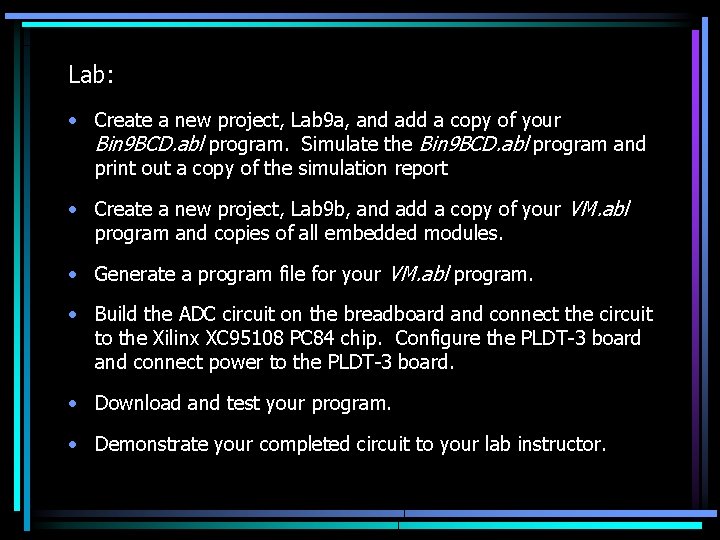

Lab: • Create a new project, Lab 9 a, and add a copy of your Bin 9 BCD. abl program. Simulate the Bin 9 BCD. abl program and print out a copy of the simulation report • Create a new project, Lab 9 b, and add a copy of your VM. abl program and copies of all embedded modules. • Generate a program file for your VM. abl program. • Build the ADC circuit on the breadboard and connect the circuit to the Xilinx XC 95108 PC 84 chip. Configure the PLDT-3 board and connect power to the PLDT-3 board. • Download and test your program. • Demonstrate your completed circuit to your lab instructor.

- Slides: 16