CPE 626 The System C Language Aleksandar Milenkovic

![Arrays sc_in<sc_logic> a[32]; // // sc_signal<sc_logic> i[16]; // // creates ports a[0] to a[31] Arrays sc_in<sc_logic> a[32]; // // sc_signal<sc_logic> i[16]; // // creates ports a[0] to a[31]](https://slidetodoc.com/presentation_image_h2/5ee8f2ccdb0630378adecee9fb9e9fde/image-10.jpg)

- Slides: 13

CPE 626 The System. C Language Aleksandar Milenkovic E-mail: Web: milenka@ece. uah. edu http: //www. ece. uah. edu/~milenka

Outline Ø Ø Ø Writing testbenches System. C types Arrays Resolved Logic Vector Clocks A. Milenkovic 2

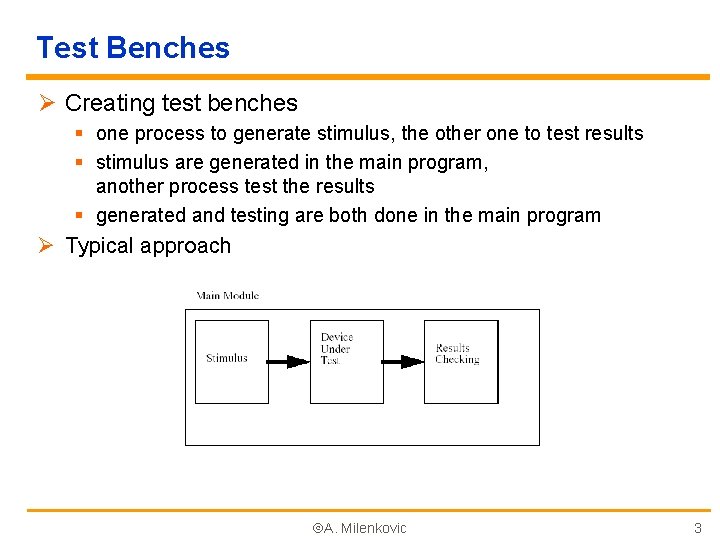

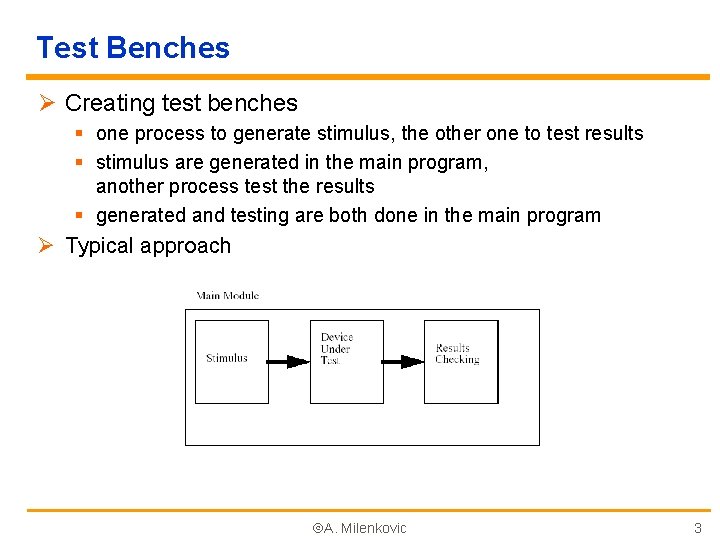

Test Benches Ø Creating test benches § one process to generate stimulus, the other one to test results § stimulus are generated in the main program, another process test the results § generated and testing are both done in the main program Ø Typical approach A. Milenkovic 3

Example: Counter // Filename : count. h #include "systemc. h" SC_MODULE(count) { sc_in<bool> load; sc_in<int> din; sc_in<bool> clock; sc_out<int> dout; // Filename : count. cpp #include "count. h" // input ports // output port int count_val; // internal data st. void count_up(); SC_CTOR(count) { SC_METHOD(count_up); // Method proc. // Sensitive to Rising edge clock sensitive_pos << clock; } void count: : count_up() { if (load) { count_val = din; } else { // Read/Write of local storage count_val = count_val + 1; } // Write to Output port dout = count_val; } }; A. Milenkovic 4

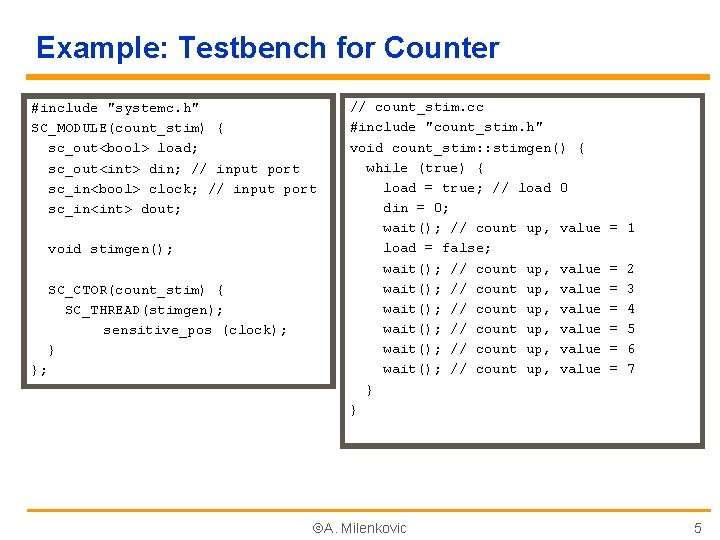

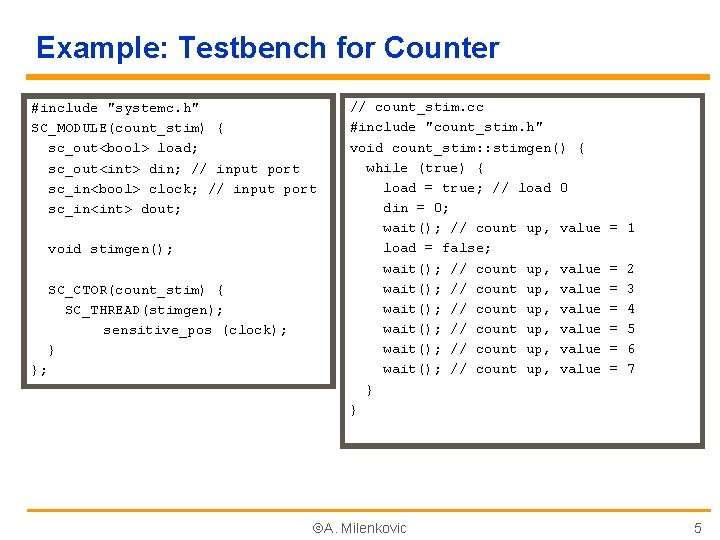

Example: Testbench for Counter #include "systemc. h" SC_MODULE(count_stim) { sc_out<bool> load; sc_out<int> din; // input port sc_in<bool> clock; // input port sc_in<int> dout; void stimgen(); SC_CTOR(count_stim) { SC_THREAD(stimgen); sensitive_pos (clock); } }; // count_stim. cc #include "count_stim. h" void count_stim: : stimgen() { while (true) { load = true; // load 0 din = 0; wait(); // count up, value load = false; wait(); // count up, value wait(); // count up, value } } A. Milenkovic = 1 = = = 2 3 4 5 6 7 5

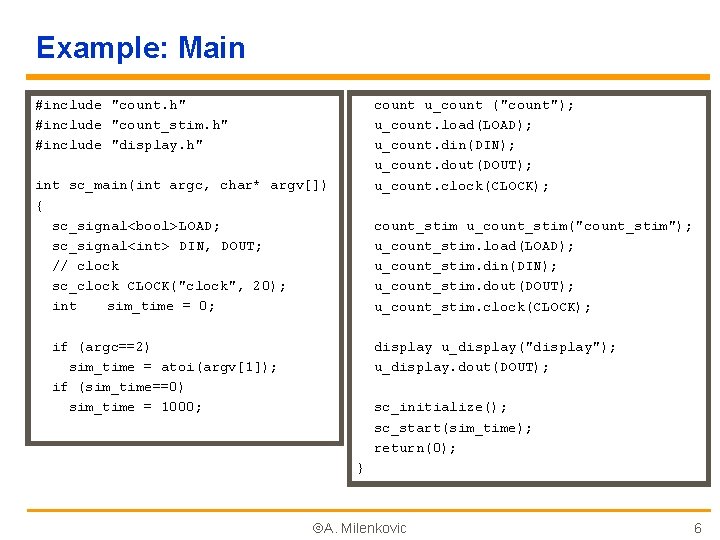

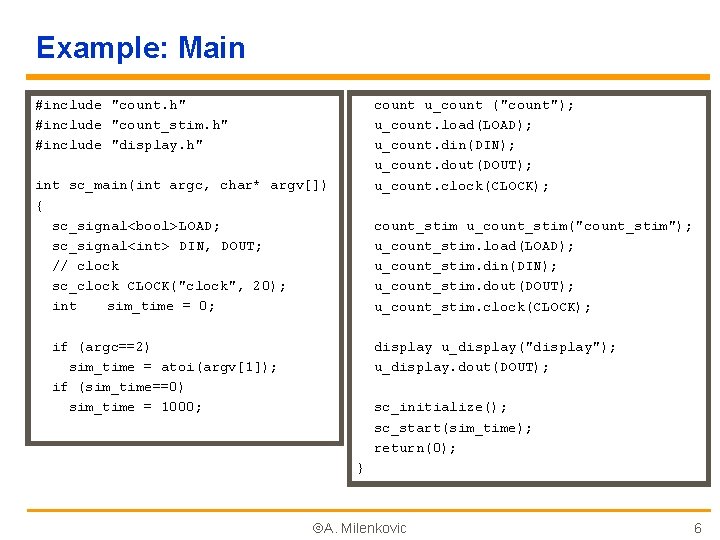

Example: Main #include "count. h" #include "count_stim. h" #include "display. h" count u_count ("count"); u_count. load(LOAD); u_count. din(DIN); u_count. dout(DOUT); u_count. clock(CLOCK); int sc_main(int argc, char* argv[]) { sc_signal<bool>LOAD; sc_signal<int> DIN, DOUT; // clock sc_clock CLOCK("clock", 20); int sim_time = 0; count_stim u_count_stim("count_stim"); u_count_stim. load(LOAD); u_count_stim. din(DIN); u_count_stim. dout(DOUT); u_count_stim. clock(CLOCK); if (argc==2) sim_time = atoi(argv[1]); if (sim_time==0) sim_time = 1000; display u_display("display"); u_display. dout(DOUT); sc_initialize(); sc_start(sim_time); return(0); } A. Milenkovic 6

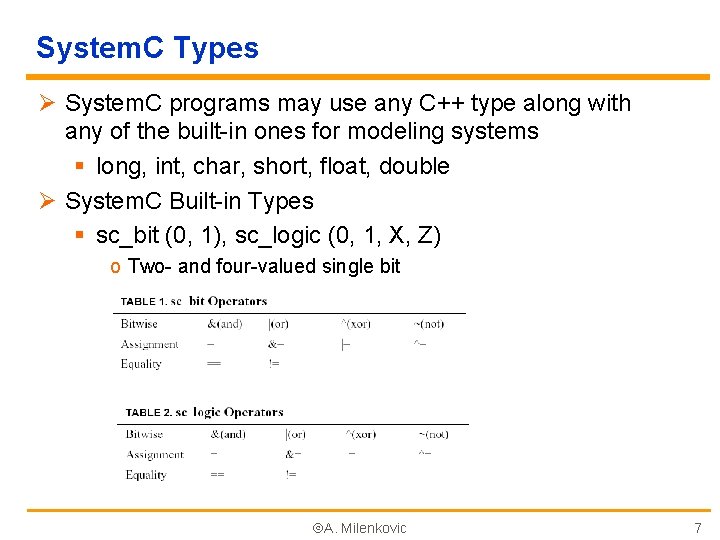

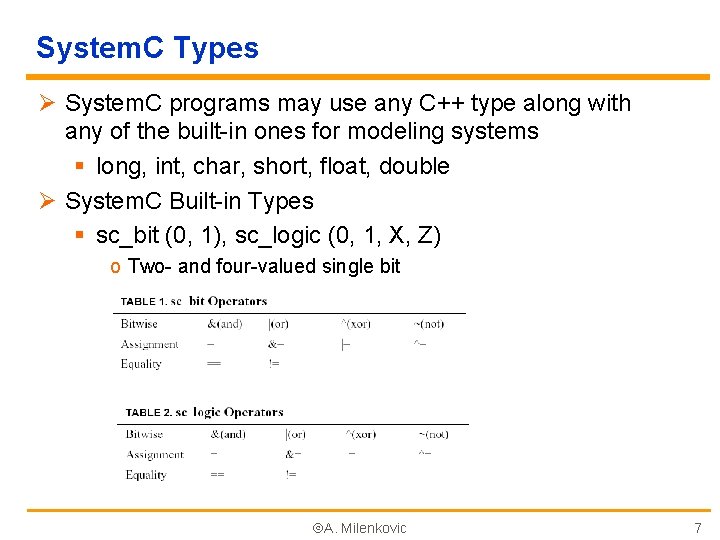

System. C Types Ø System. C programs may use any C++ type along with any of the built-in ones for modeling systems § long, int, char, short, float, double Ø System. C Built-in Types § sc_bit (0, 1), sc_logic (0, 1, X, Z) o Two- and four-valued single bit A. Milenkovic 7

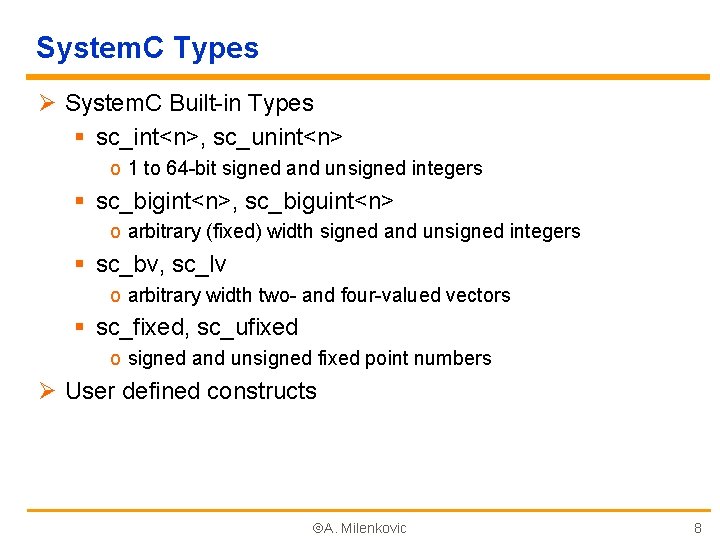

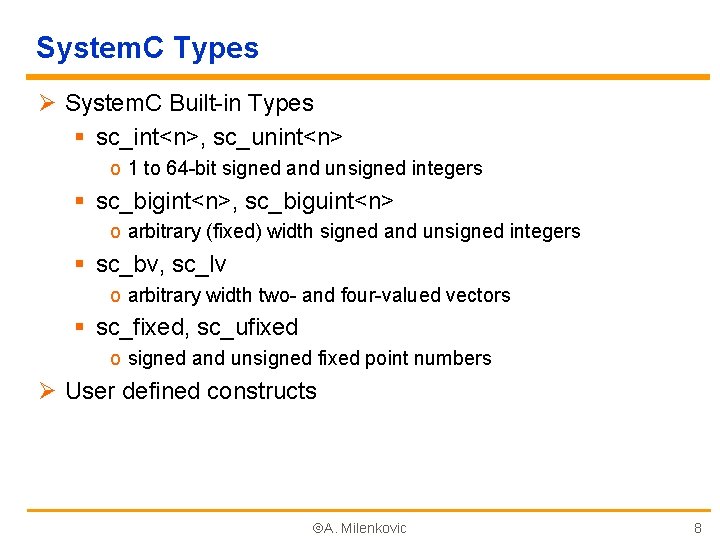

System. C Types Ø System. C Built-in Types § sc_int<n>, sc_unint<n> o 1 to 64 -bit signed and unsigned integers § sc_bigint<n>, sc_biguint<n> o arbitrary (fixed) width signed and unsigned integers § sc_bv, sc_lv o arbitrary width two- and four-valued vectors § sc_fixed, sc_ufixed o signed and unsigned fixed point numbers Ø User defined constructs A. Milenkovic 8

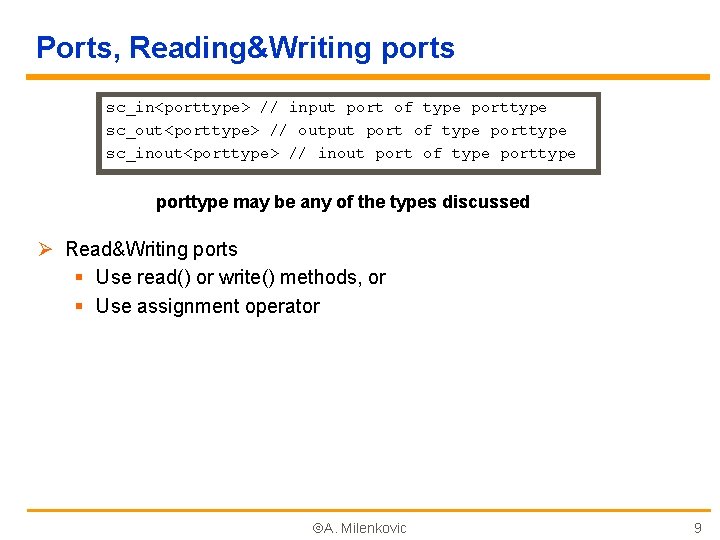

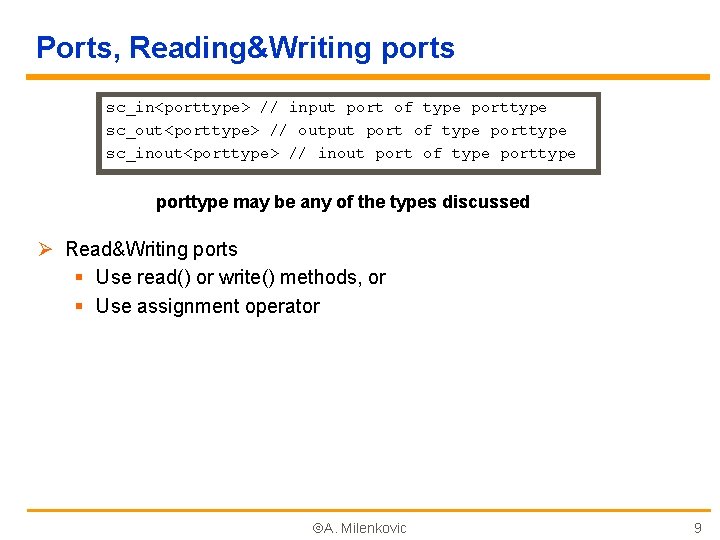

Ports, Reading&Writing ports sc_in<porttype> // input port of type porttype sc_out<porttype> // output port of type porttype sc_inout<porttype> // inout port of type porttype may be any of the types discussed Ø Read&Writing ports § Use read() or write() methods, or § Use assignment operator A. Milenkovic 9

![Arrays scinsclogic a32 scsignalsclogic i16 creates ports a0 to a31 Arrays sc_in<sc_logic> a[32]; // // sc_signal<sc_logic> i[16]; // // creates ports a[0] to a[31]](https://slidetodoc.com/presentation_image_h2/5ee8f2ccdb0630378adecee9fb9e9fde/image-10.jpg)

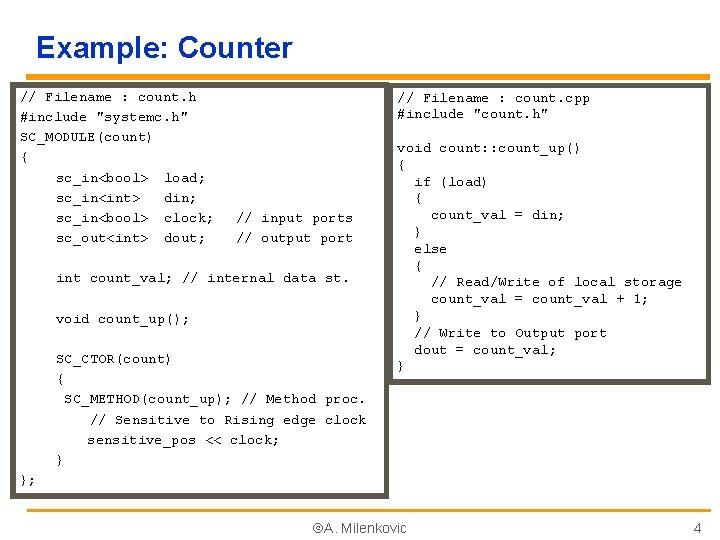

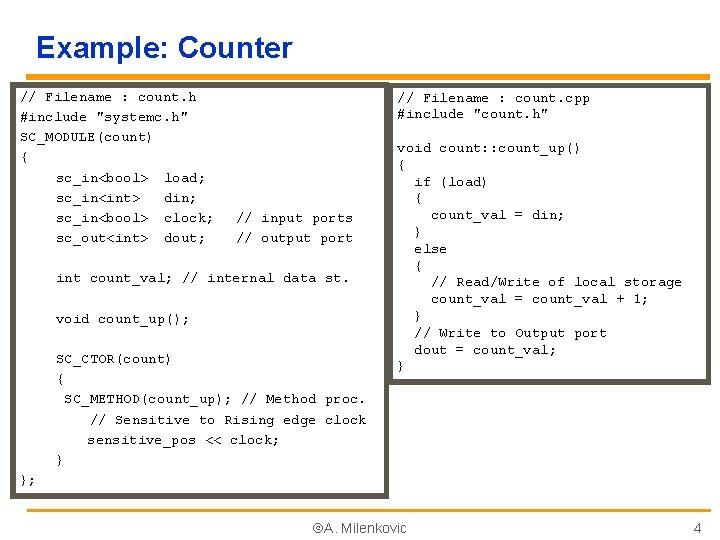

Arrays sc_in<sc_logic> a[32]; // // sc_signal<sc_logic> i[16]; // // creates ports a[0] to a[31] of type sc_logic creates signals i[0] to i[15] of type sc_logic A. Milenkovic 10

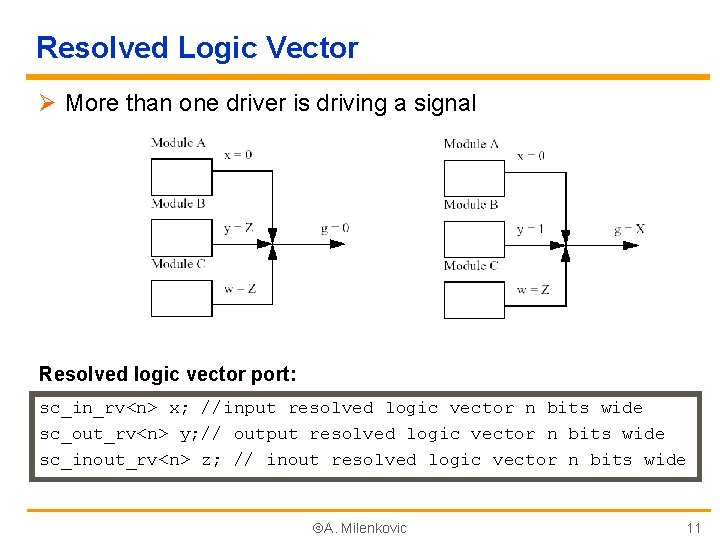

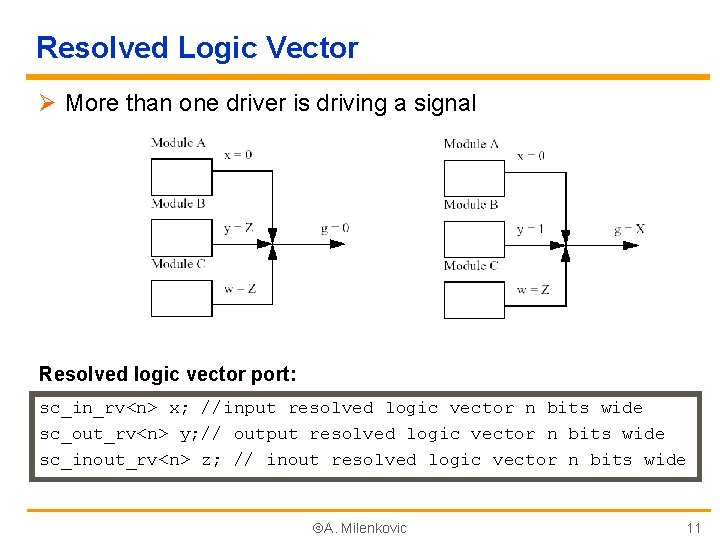

Resolved Logic Vector Ø More than one driver is driving a signal Resolved logic vector port: sc_in_rv<n> x; //input resolved logic vector n bits wide sc_out_rv<n> y; // output resolved logic vector n bits wide sc_inout_rv<n> z; // inout resolved logic vector n bits wide A. Milenkovic 11

Resolved Vector Signals Ø Used to connect resolved logic vector ports Resolved logic vector signal: sc_signal_rv<n> sig 3; // resolved logic vector signal // n bits wide A. Milenkovic 12

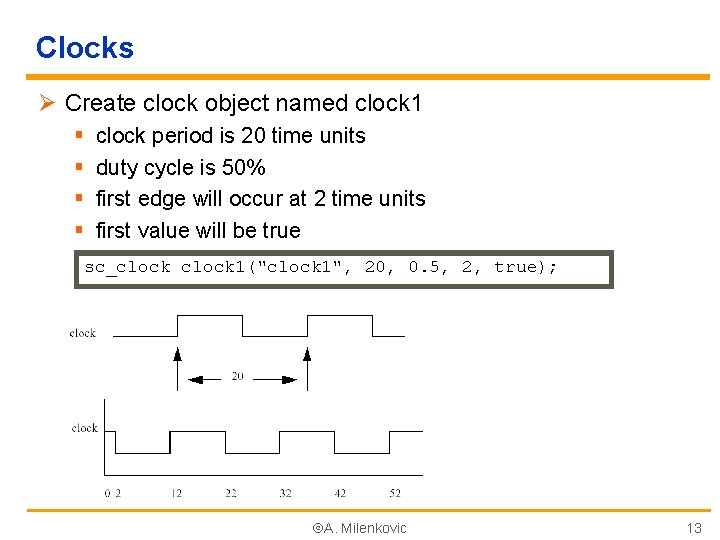

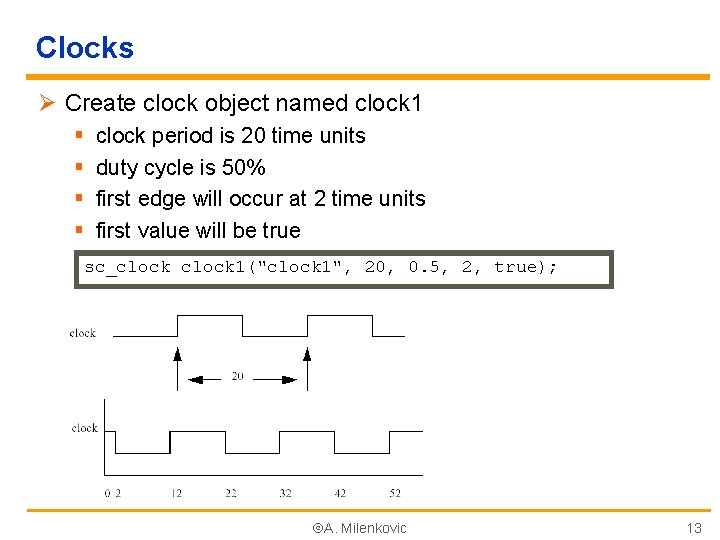

Clocks Ø Create clock object named clock 1 § § clock period is 20 time units duty cycle is 50% first edge will occur at 2 time units first value will be true sc_clock 1("clock 1", 20, 0. 5, 2, true); A. Milenkovic 13