Constructive Computer Architecture Sequential Circuits 2 Arvind Computer

![Dynamic selection requires a mux i a a[i] when the selection indices are regular Dynamic selection requires a mux i a a[i] when the selection indices are regular](https://slidetodoc.com/presentation_image_h2/921d221fd8cf667514ec37d553cc7200/image-11.jpg)

- Slides: 20

Constructive Computer Architecture Sequential Circuits - 2 Arvind Computer Science & Artificial Intelligence Lab. Massachusetts Institute of Technology September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -1

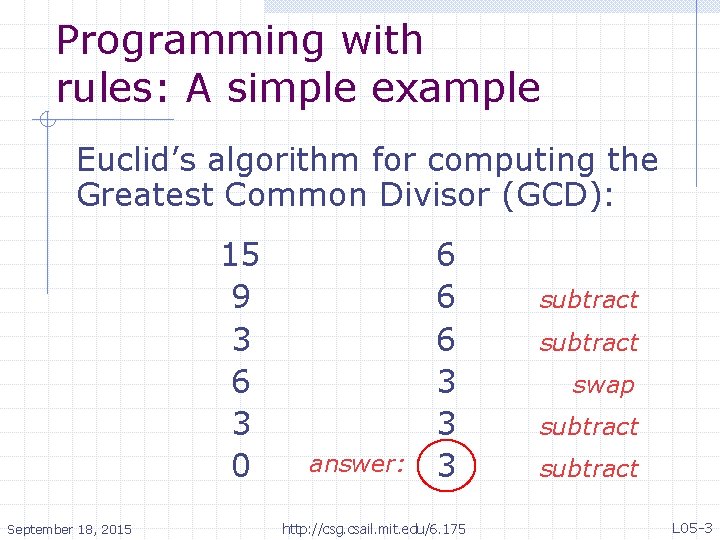

Content So far we have seen modules with methods which are called by rules outside the body Now we will see examples where a module may also contain rules n gcd A common way to implement large combinational circuits is by folding where registers hold the state from one iteration to the next n n Implementing imperative loops Multiplication September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -2

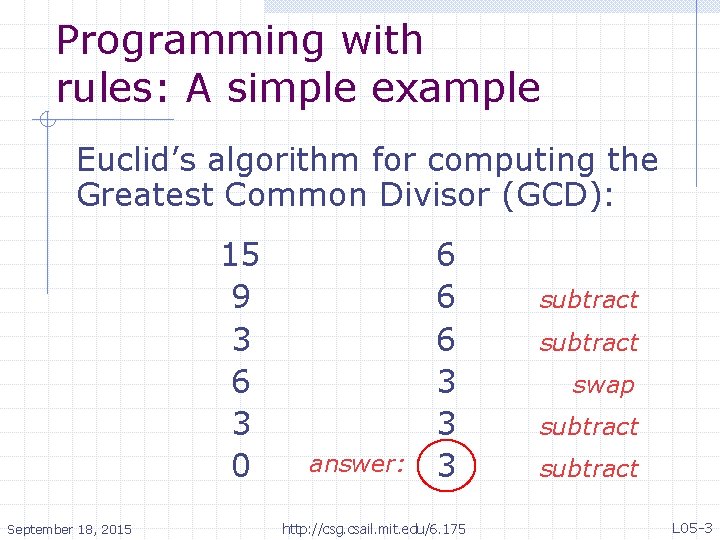

Programming with rules: A simple example Euclid’s algorithm for computing the Greatest Common Divisor (GCD): 15 9 3 6 3 0 September 18, 2015 answer: 6 6 6 3 3 3 http: //csg. csail. mit. edu/6. 175 subtract swap subtract L 05 -3

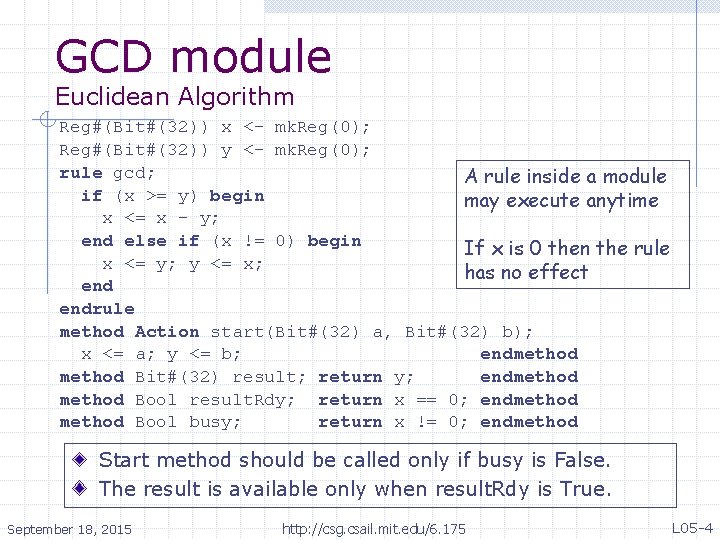

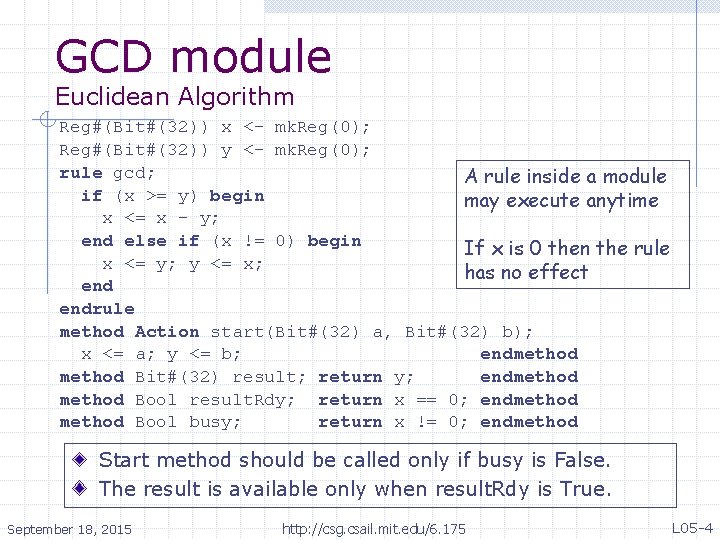

GCD module Euclidean Algorithm Reg#(Bit#(32)) x <- mk. Reg(0); Reg#(Bit#(32)) y <- mk. Reg(0); rule gcd; A rule inside a module if (x >= y) begin may execute anytime x <= x – y; end else if (x != 0) begin If x is 0 then the rule x <= y; y <= x; has no effect endrule method Action start(Bit#(32) a, Bit#(32) b); x <= a; y <= b; endmethod Bit#(32) result; return y; endmethod Bool result. Rdy; return x == 0; endmethod Bool busy; return x != 0; endmethod Start method should be called only if busy is False. The result is available only when result. Rdy is True. September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -4

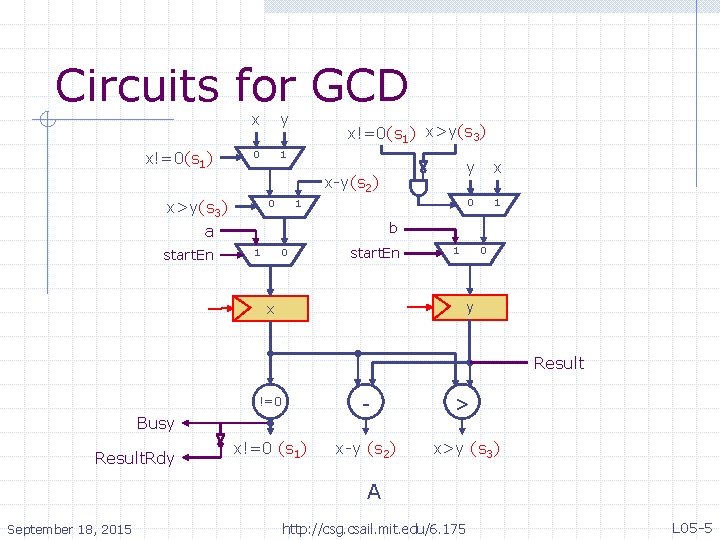

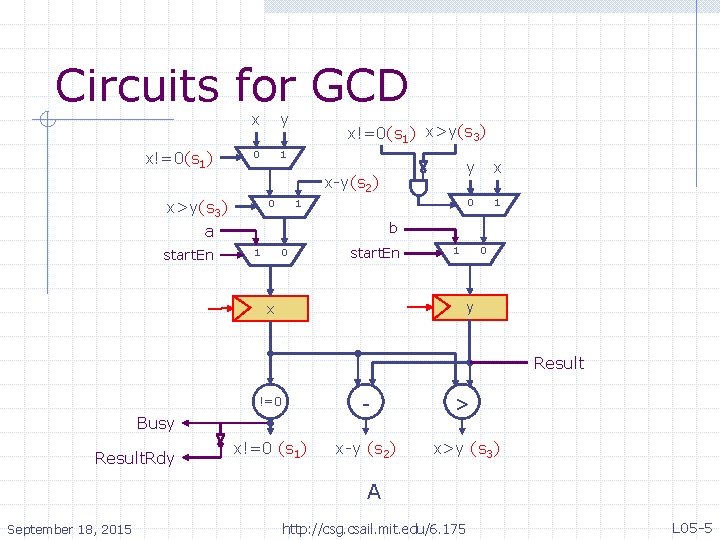

Circuits for GCD x!=0(s 1) x y 0 1 x!=0(s 1) x>y(s 3) x-y(s 2) x>y(s 3) a start. En 0 1 y x 0 1 b 1 0 start. En 1 0 y x Result !=0 - > x!=0 (s 1) x-y (s 2) x>y (s 3) Busy Result. Rdy A September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -5

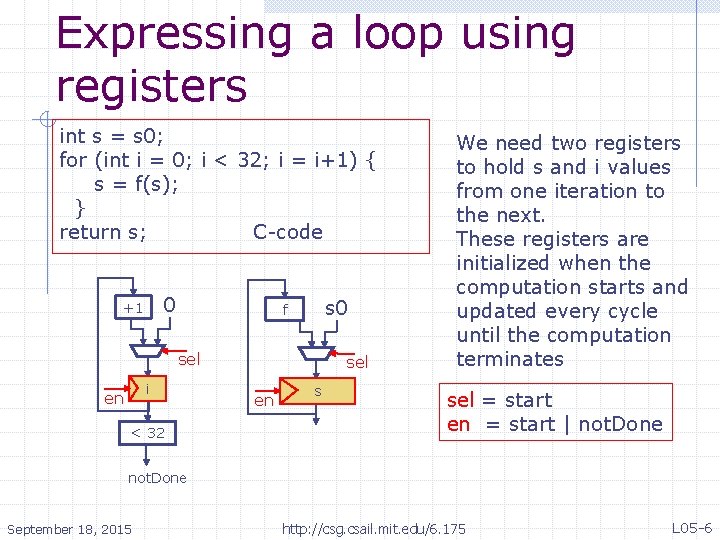

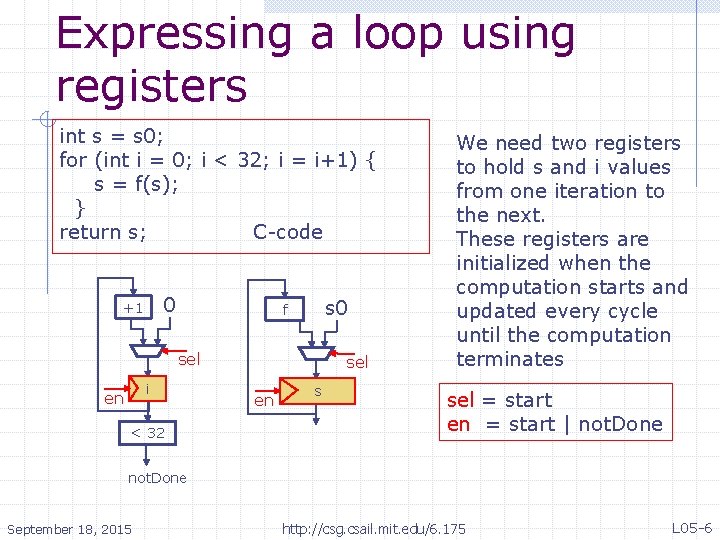

Expressing a loop using registers int s = s 0; for (int i = 0; i < 32; i = i+1) { s = f(s); } return s; C-code 0 +1 s 0 f sel i en < 32 sel en s We need two registers to hold s and i values from one iteration to the next. These registers are initialized when the computation starts and updated every cycle until the computation terminates sel = start en = start | not. Done September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -6

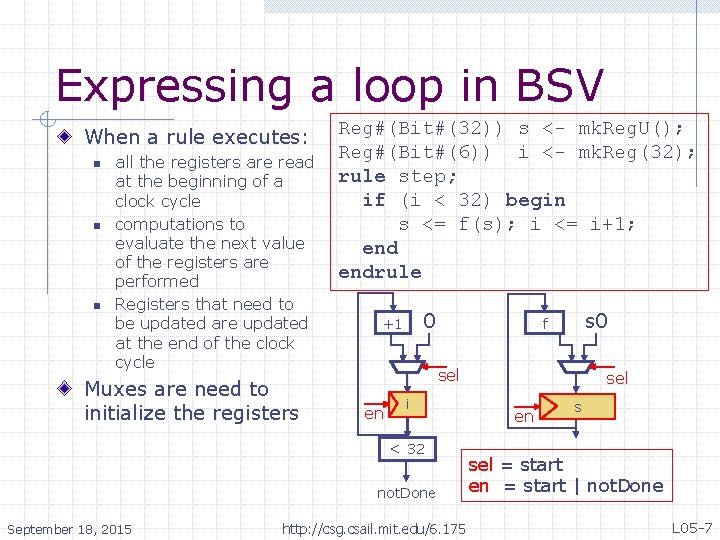

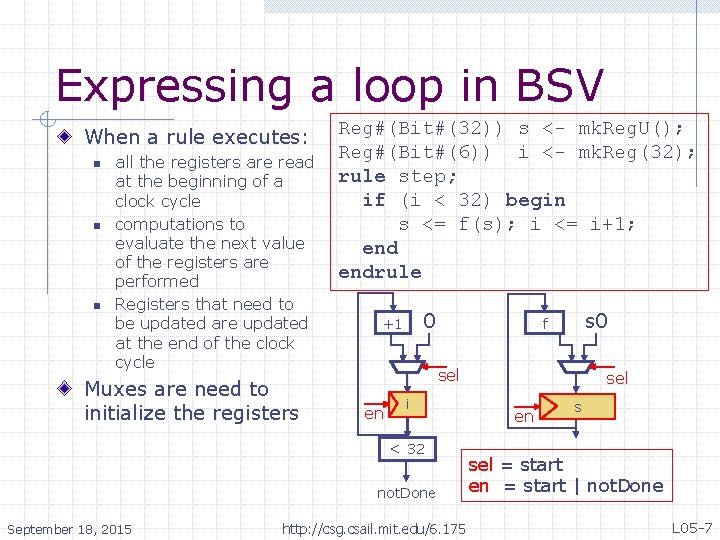

Expressing a loop in BSV When a rule executes: n n n all the registers are read at the beginning of a clock cycle computations to evaluate the next value of the registers are performed Registers that need to be updated are updated at the end of the clock cycle Muxes are need to initialize the registers Reg#(Bit#(32)) s <- mk. Reg. U(); Reg#(Bit#(6)) i <- mk. Reg(32); rule step; if (i < 32) begin s <= f(s); i <= i+1; endrule 0 +1 sel en i < 32 not. Done September 18, 2015 s 0 f http: //csg. csail. mit. edu/6. 175 sel en s sel = start en = start | not. Done L 05 -7

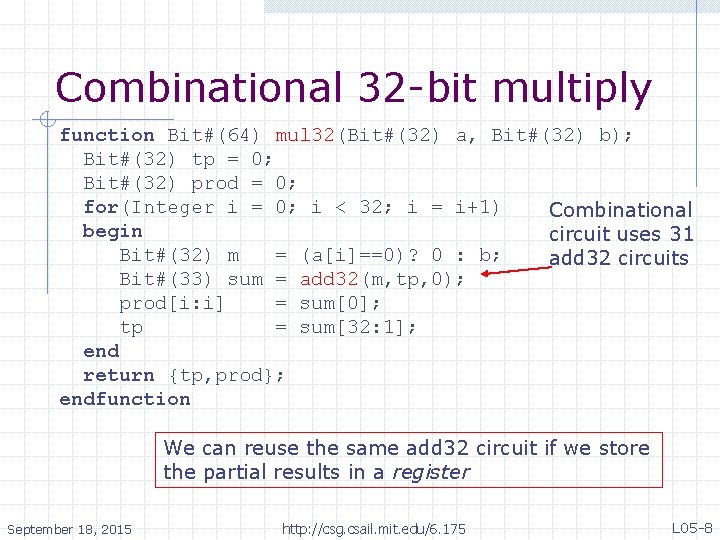

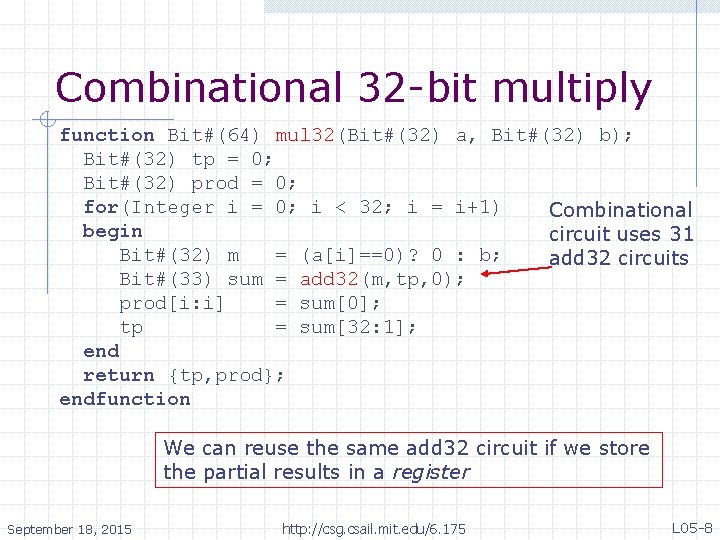

Combinational 32 -bit multiply function Bit#(64) mul 32(Bit#(32) a, Bit#(32) b); Bit#(32) tp = 0; Bit#(32) prod = 0; for(Integer i = 0; i < 32; i = i+1) Combinational begin circuit uses 31 Bit#(32) m = (a[i]==0)? 0 : b; add 32 circuits Bit#(33) sum = add 32(m, tp, 0); prod[i: i] = sum[0]; tp = sum[32: 1]; end return {tp, prod}; endfunction We can reuse the same add 32 circuit if we store the partial results in a register September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -8

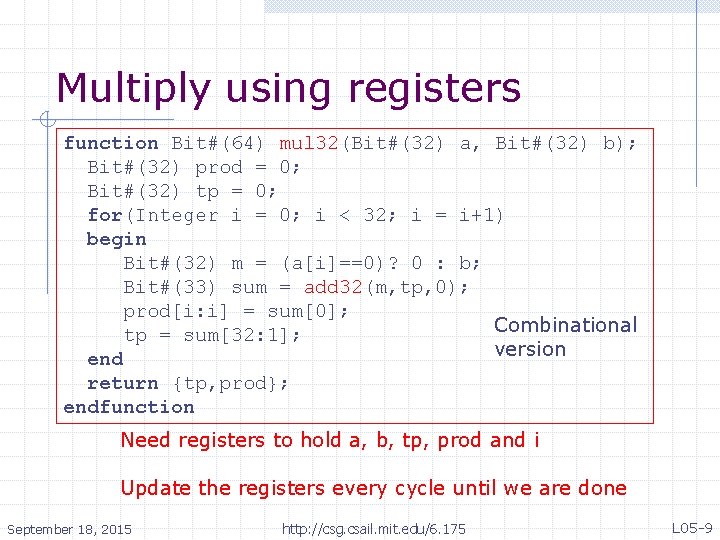

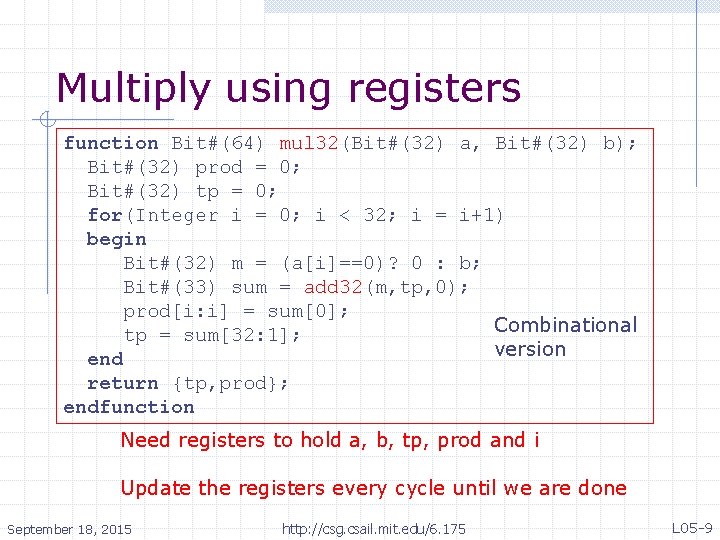

Multiply using registers function Bit#(64) mul 32(Bit#(32) a, Bit#(32) b); Bit#(32) prod = 0; Bit#(32) tp = 0; for(Integer i = 0; i < 32; i = i+1) begin Bit#(32) m = (a[i]==0)? 0 : b; Bit#(33) sum = add 32(m, tp, 0); prod[i: i] = sum[0]; Combinational tp = sum[32: 1]; version end return {tp, prod}; endfunction Need registers to hold a, b, tp, prod and i Update the registers every cycle until we are done September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -9

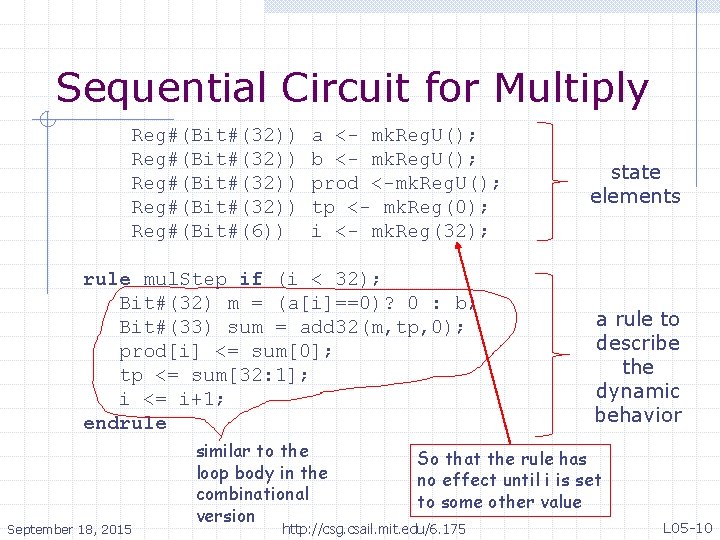

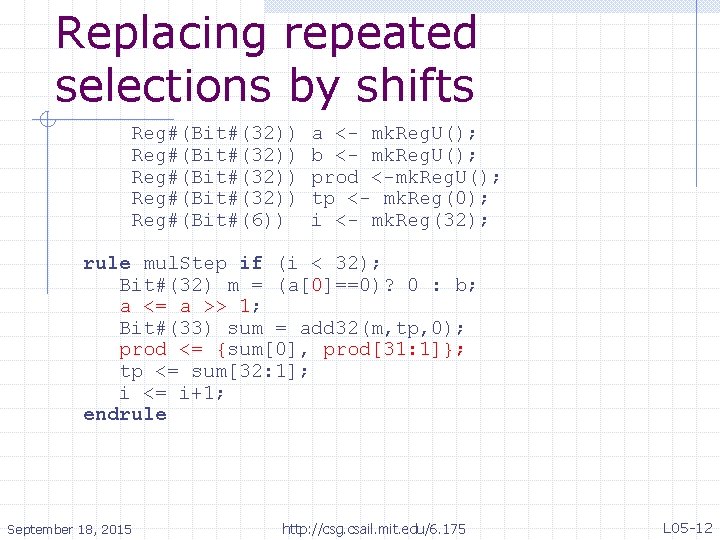

Sequential Circuit for Multiply Reg#(Bit#(32)) Reg#(Bit#(6)) a <- mk. Reg. U(); b <- mk. Reg. U(); prod <-mk. Reg. U(); tp <- mk. Reg(0); i <- mk. Reg(32); rule mul. Step if (i < 32); Bit#(32) m = (a[i]==0)? 0 : b; Bit#(33) sum = add 32(m, tp, 0); prod[i] <= sum[0]; tp <= sum[32: 1]; i <= i+1; endrule September 18, 2015 similar to the loop body in the combinational version state elements a rule to describe the dynamic behavior So that the rule has no effect until i is set to some other value http: //csg. csail. mit. edu/6. 175 L 05 -10

![Dynamic selection requires a mux i a ai when the selection indices are regular Dynamic selection requires a mux i a a[i] when the selection indices are regular](https://slidetodoc.com/presentation_image_h2/921d221fd8cf667514ec37d553cc7200/image-11.jpg)

Dynamic selection requires a mux i a a[i] when the selection indices are regular then it is better to use a shift operator (no gates!) >> a 0 September 18, 2015 a[0], a[1], a[2], … http: //csg. csail. mit. edu/6. 175 L 05 -11

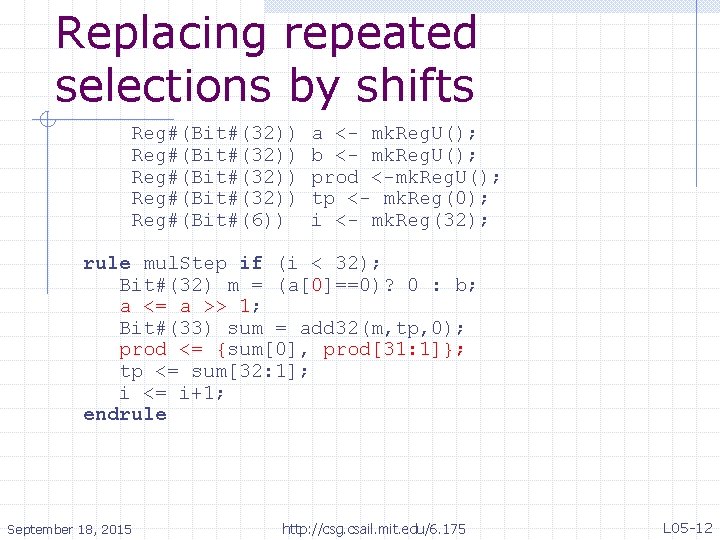

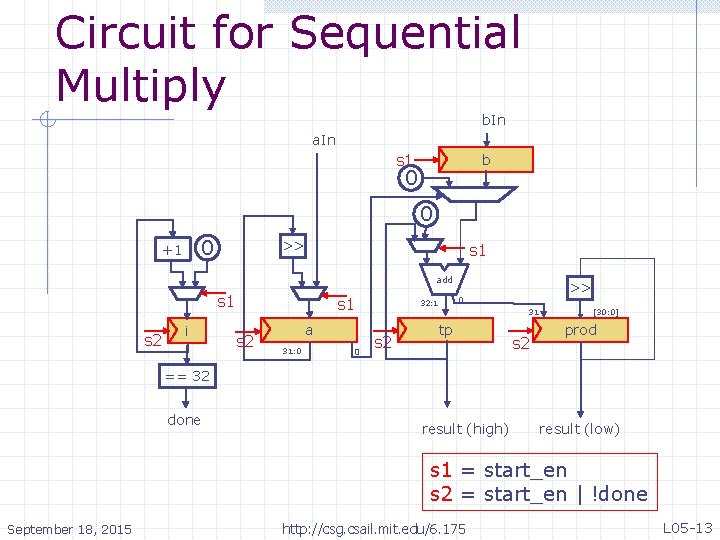

Replacing repeated selections by shifts Reg#(Bit#(32)) Reg#(Bit#(6)) a <- mk. Reg. U(); b <- mk. Reg. U(); prod <-mk. Reg. U(); tp <- mk. Reg(0); i <- mk. Reg(32); rule mul. Step if (i < 32); Bit#(32) m = (a[0]==0)? 0 : b; a <= a >> 1; Bit#(33) sum = add 32(m, tp, 0); prod <= {sum[0], prod[31: 1]}; tp <= sum[32: 1]; i <= i+1; endrule September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -12

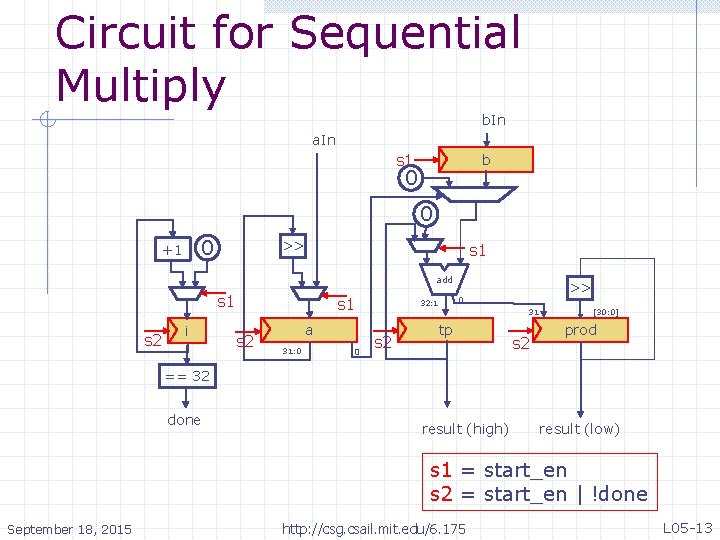

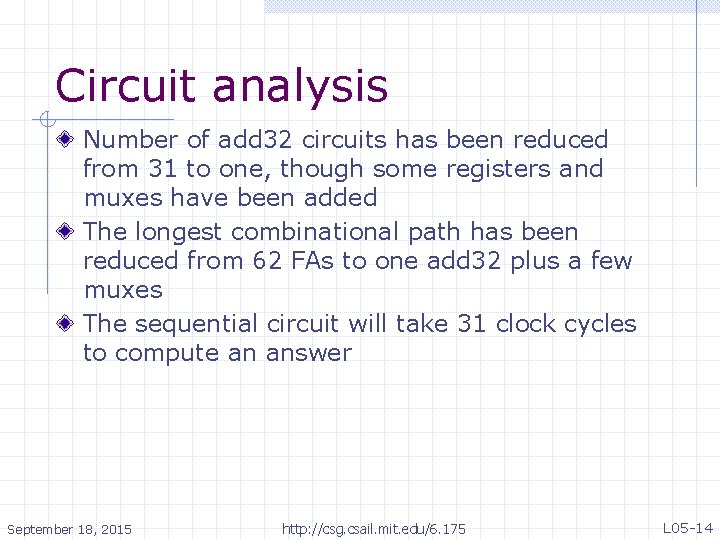

Circuit for Sequential Multiply b. In a. In s 1 b 0 0 0 << +1 s 1 add s 2 i s 1 s 2 a 31: 0 0 32: 1 s 2 << s 1 0 tp 31 s 2 [30: 0] prod == 32 done result (high) result (low) s 1 = start_en s 2 = start_en | !done September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -13

Circuit analysis Number of add 32 circuits has been reduced from 31 to one, though some registers and muxes have been added The longest combinational path has been reduced from 62 FAs to one add 32 plus a few muxes The sequential circuit will take 31 clock cycles to compute an answer September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -14

Observations These programs are not very complex and yet it would have been tedious to express these programs in a state table or as a circuit directly BSV method calls are not available in Verilog/VHDL, and thus such programs sometimes require tedious programming Even the meaning of double-write errors is not standardized across tool implementations in Verilog September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -15

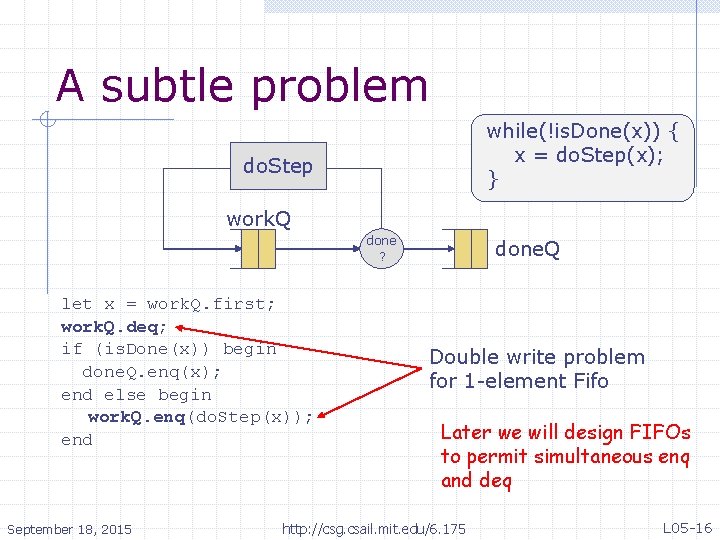

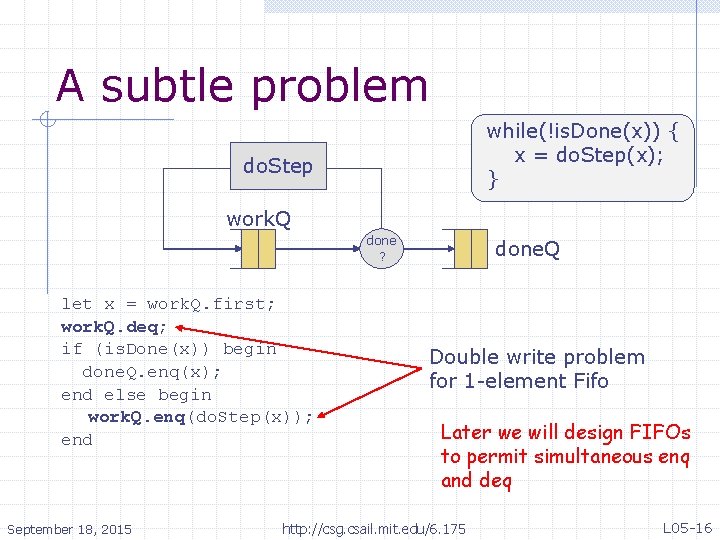

A subtle problem while(!is. Done(x)) { x = do. Step(x); } do. Step work. Q done ? let x = work. Q. first; work. Q. deq; if (is. Done(x)) begin done. Q. enq(x); end else begin work. Q. enq(do. Step(x)); end September 18, 2015 done. Q Double write problem for 1 -element Fifo Later we will design FIFOs to permit simultaneous enq and deq http: //csg. csail. mit. edu/6. 175 L 05 -16

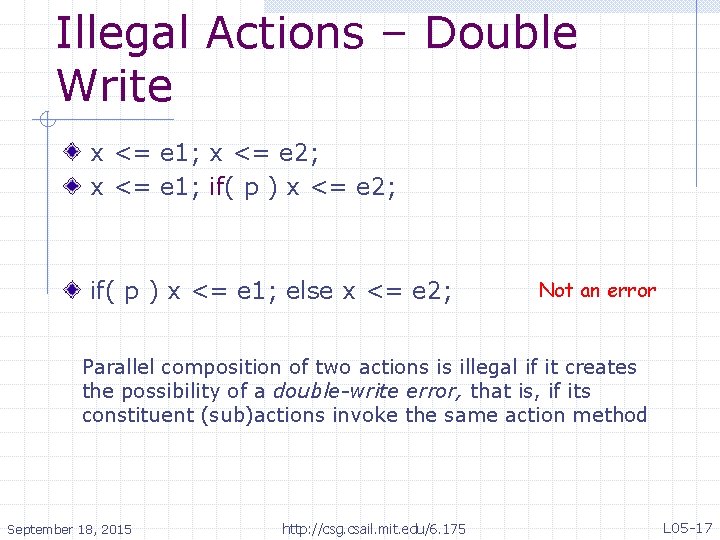

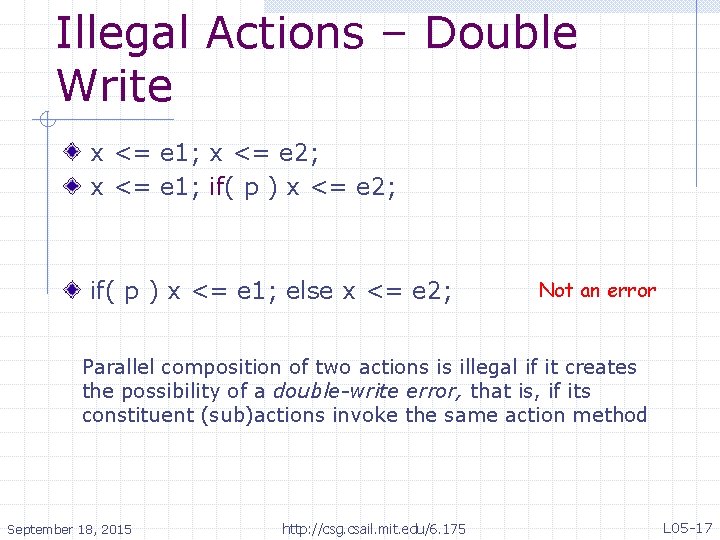

Illegal Actions – Double Write x <= e 1; x <= e 2; x <= e 1; if( p ) x <= e 2; if( p ) x <= e 1; else x <= e 2; Not an error Parallel composition of two actions is illegal if it creates the possibility of a double-write error, that is, if its constituent (sub)actions invoke the same action method September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -17

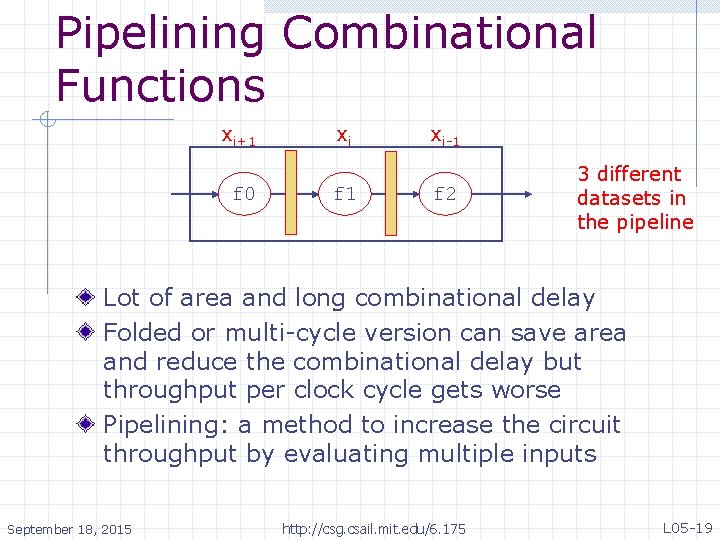

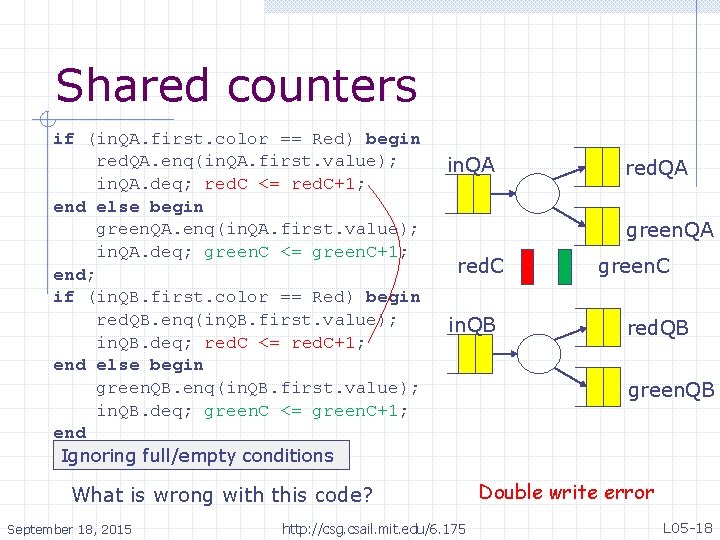

Shared counters if (in. QA. first. color == Red) begin red. QA. enq(in. QA. first. value); in. QA. deq; red. C <= red. C+1; end else begin green. QA. enq(in. QA. first. value); in. QA. deq; green. C <= green. C+1; end; if (in. QB. first. color == Red) begin red. QB. enq(in. QB. first. value); in. QB. deq; red. C <= red. C+1; end else begin green. QB. enq(in. QB. first. value); in. QB. deq; green. C <= green. C+1; end Ignoring full/empty conditions in. QA green. QA red. C in. QB What is wrong with this code? September 18, 2015 red. QA http: //csg. csail. mit. edu/6. 175 green. C red. QB green. QB Double write error L 05 -18

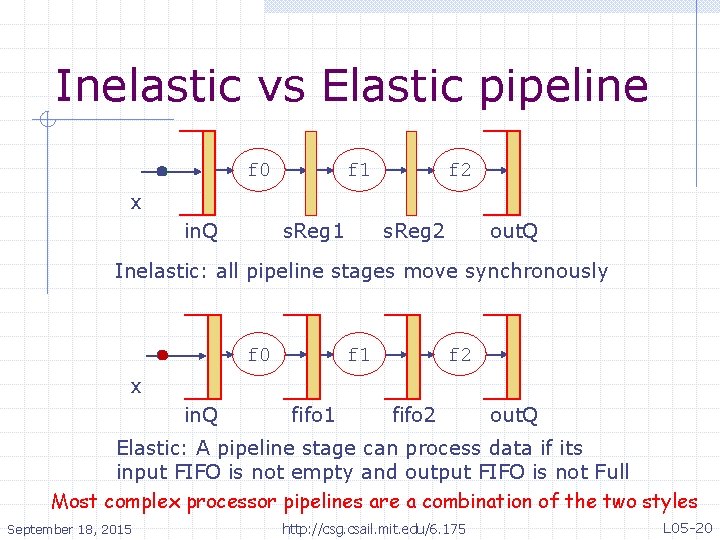

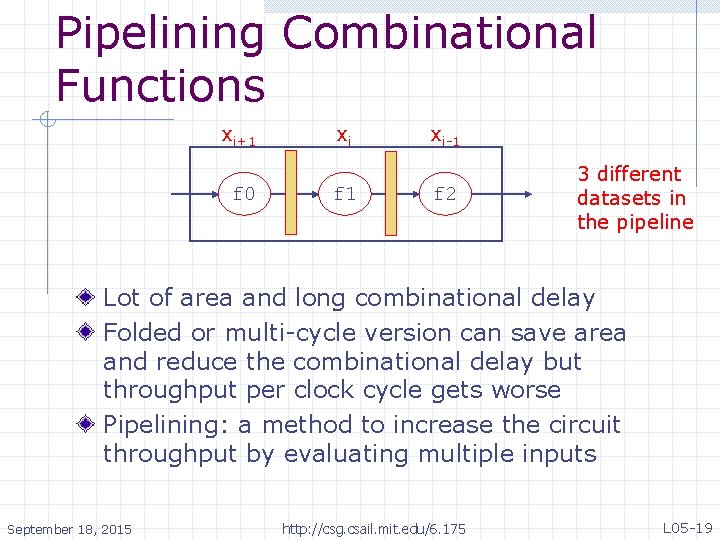

Pipelining Combinational Functions xi+1 f 0 xi f 1 xi-1 f 2 3 different datasets in the pipeline Lot of area and long combinational delay Folded or multi-cycle version can save area and reduce the combinational delay but throughput per clock cycle gets worse Pipelining: a method to increase the circuit throughput by evaluating multiple inputs September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -19

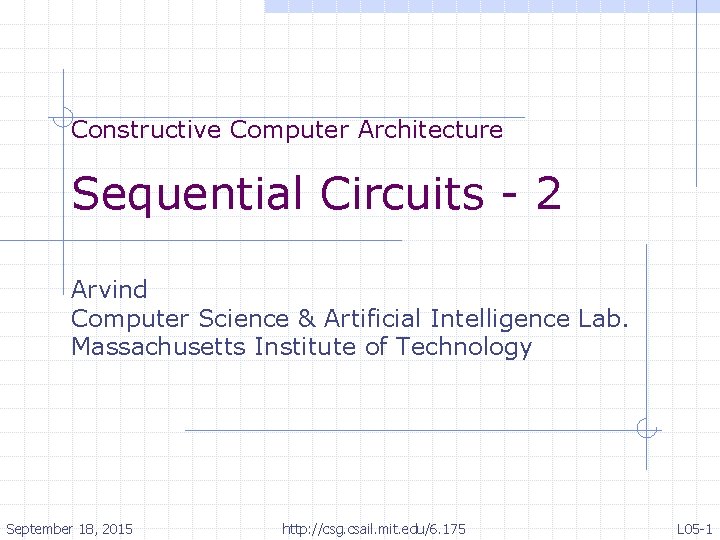

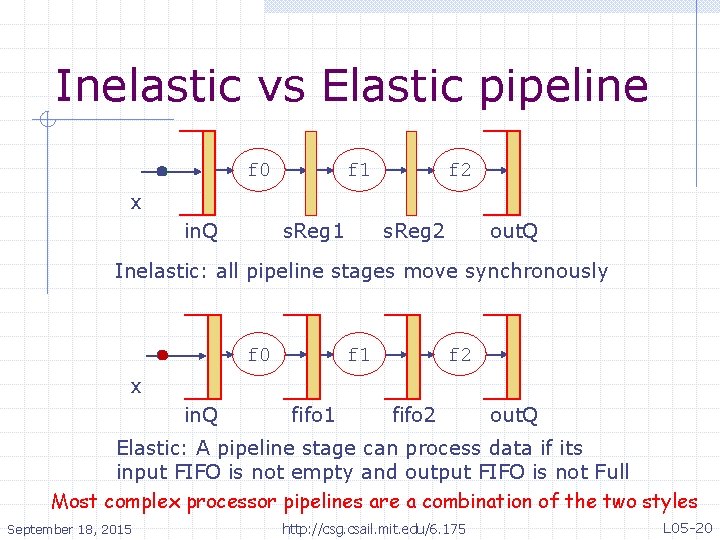

Inelastic vs Elastic pipeline f 0 f 1 f 2 x s. Reg 1 in. Q s. Reg 2 out. Q Inelastic: all pipeline stages move synchronously f 0 f 1 f 2 x in. Q fifo 1 fifo 2 out. Q Elastic: A pipeline stage can process data if its input FIFO is not empty and output FIFO is not Full Most complex processor pipelines are a combination of the two styles September 18, 2015 http: //csg. csail. mit. edu/6. 175 L 05 -20