Configuration DB Pixel Control Pixel Detector configuration Complex

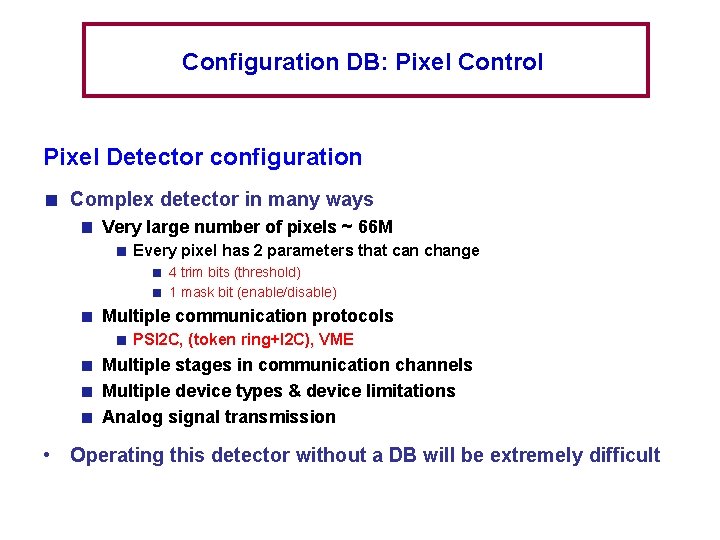

Configuration DB: Pixel Control Pixel Detector configuration Complex detector in many ways Very large number of pixels ~ 66 M Every pixel has 2 parameters that can change 4 trim bits (threshold) 1 mask bit (enable/disable) Multiple communication protocols PSI 2 C, (token ring+I 2 C), VME Multiple stages in communication channels Multiple device types & device limitations Analog signal transmission • Operating this detector without a DB will be extremely difficult

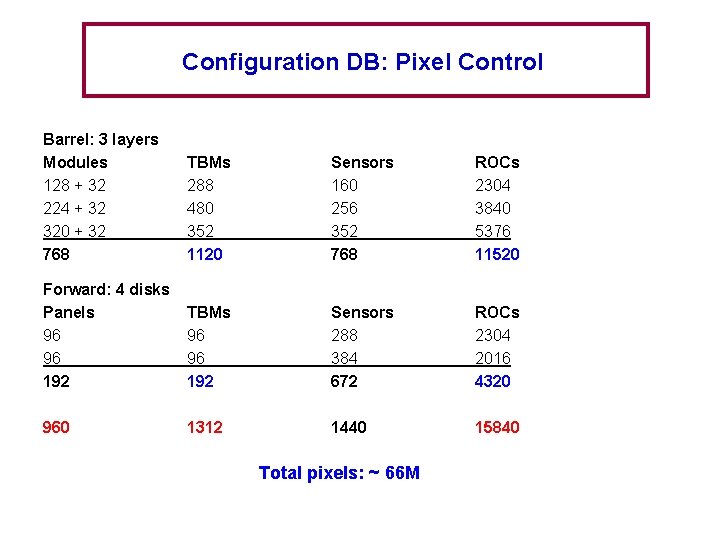

Configuration DB: Pixel Control Barrel: 3 layers Modules 128 + 32 224 + 32 320 + 32 768 TBMs 288 480 352 1120 Sensors 160 256 352 768 ROCs 2304 3840 5376 11520 Forward: 4 disks Panels 96 96 192 TBMs 96 96 192 Sensors 288 384 672 ROCs 2304 2016 4320 960 1312 1440 15840 Total pixels: ~ 66 M

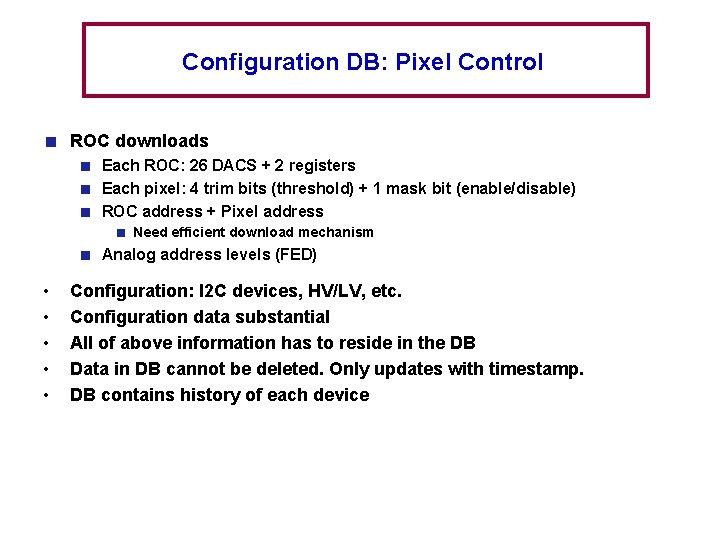

Configuration DB: Pixel Control ROC downloads Each ROC: 26 DACS + 2 registers Each pixel: 4 trim bits (threshold) + 1 mask bit (enable/disable) ROC address + Pixel address Need efficient download mechanism Analog address levels (FED) • • • Configuration: I 2 C devices, HV/LV, etc. Configuration data substantial All of above information has to reside in the DB Data in DB cannot be deleted. Only updates with timestamp. DB contains history of each device

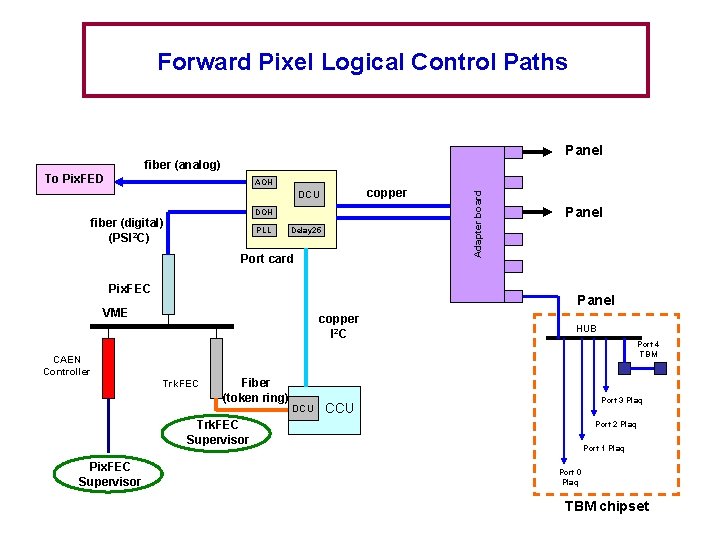

Forward Pixel Logical Control Paths Panel AOH copper DCU DOH fiber (digital) (PSI 2 C) PLL Delay 25 Port card Pix. FEC Adapter board fiber (analog) To Pix. FED Panel VME copper I 2 C CAEN Controller Trk. FEC Fiber (token ring) DCU HUB Port 4 TBM Port 3 Plaq CCU Trk. FEC Supervisor Pix. FEC Supervisor Port 2 Plaq Port 1 Plaq Port 0 Plaq TBM chipset

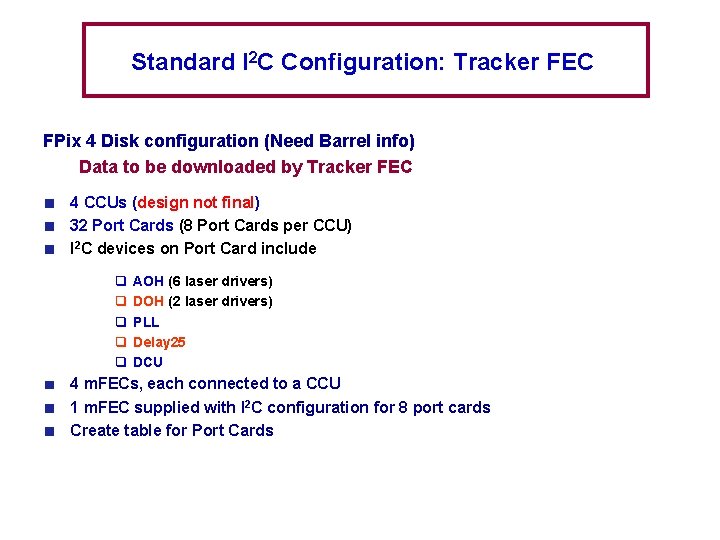

Standard I 2 C Configuration: Tracker FEC FPix 4 Disk configuration (Need Barrel info) Data to be downloaded by Tracker FEC 4 CCUs (design not final) 32 Port Cards (8 Port Cards per CCU) I 2 C devices on Port Card include q q q AOH (6 laser drivers) DOH (2 laser drivers) PLL Delay 25 DCU 4 m. FECs, each connected to a CCU 1 m. FEC supplied with I 2 C configuration for 8 port cards Create table for Port Cards

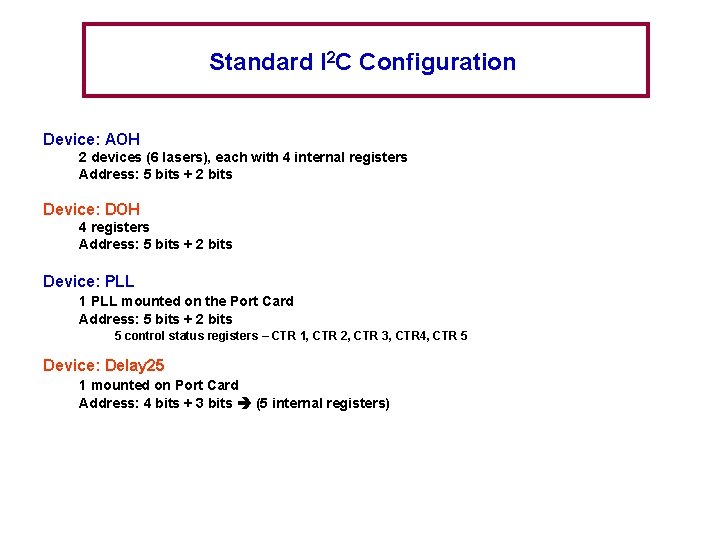

Standard I 2 C Configuration Device: AOH 2 devices (6 lasers), each with 4 internal registers Address: 5 bits + 2 bits Device: DOH 4 registers Address: 5 bits + 2 bits Device: PLL 1 PLL mounted on the Port Card Address: 5 bits + 2 bits 5 control status registers – CTR 1, CTR 2, CTR 3, CTR 4, CTR 5 Device: Delay 25 1 mounted on Port Card Address: 4 bits + 3 bits (5 internal registers)

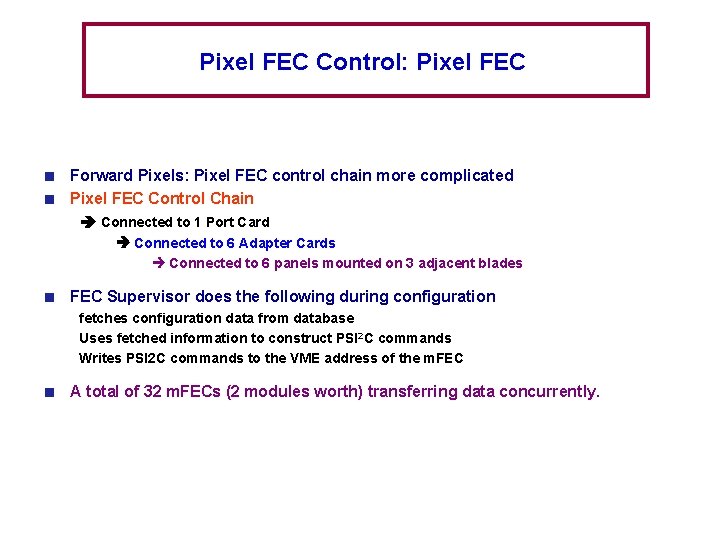

Pixel FEC Control: Pixel FEC Forward Pixels: Pixel FEC control chain more complicated Pixel FEC Control Chain Connected to 1 Port Card Connected to 6 Adapter Cards è Connected to 6 panels mounted on 3 adjacent blades FEC Supervisor does the following during configuration fetches configuration data from database Uses fetched information to construct PSI 2 C commands Writes PSI 2 C commands to the VME address of the m. FEC A total of 32 m. FECs (2 modules worth) transferring data concurrently.

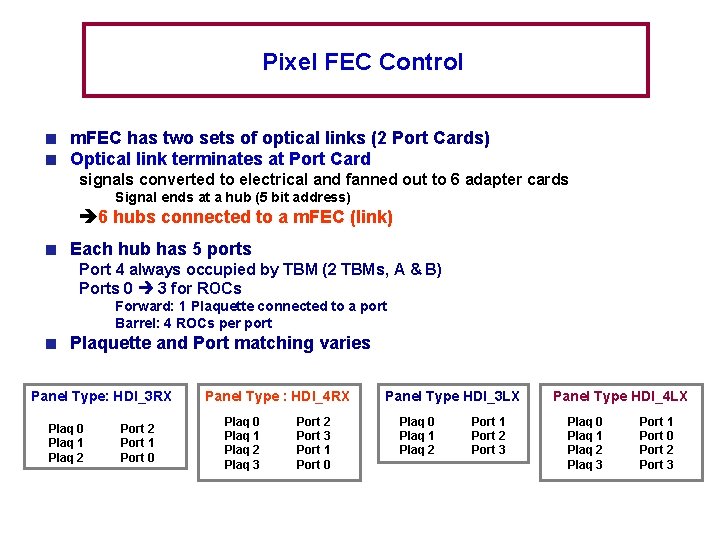

Pixel FEC Control m. FEC has two sets of optical links (2 Port Cards) Optical link terminates at Port Card signals converted to electrical and fanned out to 6 adapter cards Signal ends at a hub (5 bit address) 6 hubs connected to a m. FEC (link) Each hub has 5 ports Port 4 always occupied by TBM (2 TBMs, A & B) Ports 0 3 for ROCs Forward: 1 Plaquette connected to a port Barrel: 4 ROCs per port Plaquette and Port matching varies Panel Type: HDI_3 RX Plaq 0 Plaq 1 Plaq 2 Port 1 Port 0 Panel Type : HDI_4 RX Plaq 0 Plaq 1 Plaq 2 Plaq 3 Port 2 Port 3 Port 1 Port 0 Panel Type HDI_3 LX Plaq 0 Plaq 1 Plaq 2 Port 1 Port 2 Port 3 Panel Type HDI_4 LX Plaq 0 Plaq 1 Plaq 2 Plaq 3 Port 1 Port 0 Port 2 Port 3

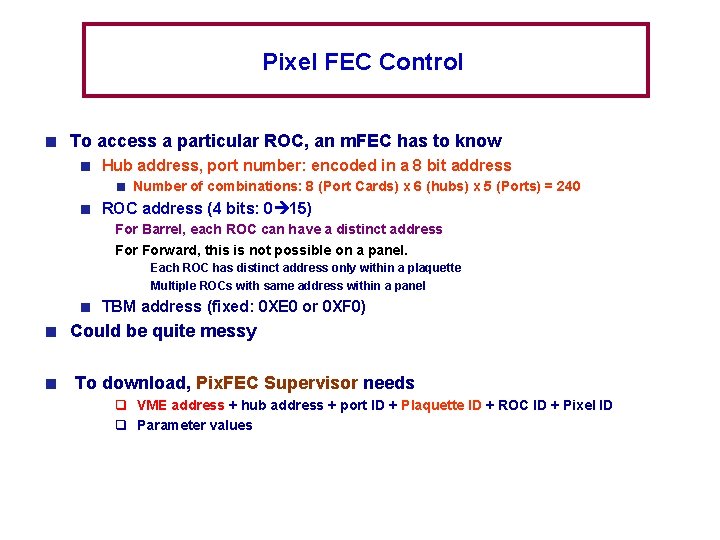

Pixel FEC Control To access a particular ROC, an m. FEC has to know Hub address, port number: encoded in a 8 bit address Number of combinations: 8 (Port Cards) x 6 (hubs) x 5 (Ports) = 240 ROC address (4 bits: 0 15) For Barrel, each ROC can have a distinct address Forward, this is not possible on a panel. Each ROC has distinct address only within a plaquette Multiple ROCs with same address within a panel TBM address (fixed: 0 XE 0 or 0 XF 0) Could be quite messy To download, Pix. FEC Supervisor needs q VME address + hub address + port ID + Plaquette ID + ROC ID + Pixel ID q Parameter values

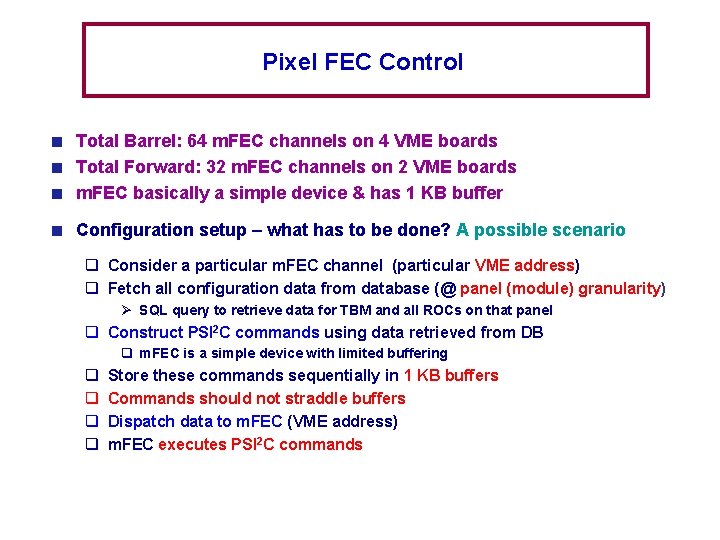

Pixel FEC Control Total Barrel: 64 m. FEC channels on 4 VME boards Total Forward: 32 m. FEC channels on 2 VME boards m. FEC basically a simple device & has 1 KB buffer Configuration setup – what has to be done? A possible scenario q Consider a particular m. FEC channel (particular VME address) q Fetch all configuration data from database (@ panel (module) granularity) Ø SQL query to retrieve data for TBM and all ROCs on that panel q Construct PSI 2 C commands using data retrieved from DB q m. FEC is a simple device with limited buffering q q Store these commands sequentially in 1 KB buffers Commands should not straddle buffers Dispatch data to m. FEC (VME address) m. FEC executes PSI 2 C commands

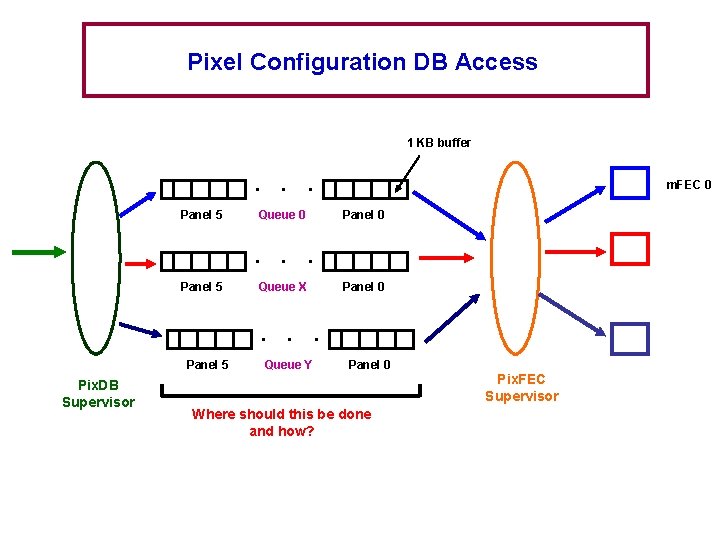

Pixel Configuration DB Access 1 KB buffer . . . Panel 5 Queue 0 m. FEC 0 Panel 0 . . . Panel 5 Queue X Panel 0 . . . Panel 5 Pix. DB Supervisor Queue Y Panel 0 Where should this be done and how? Pix. FEC Supervisor

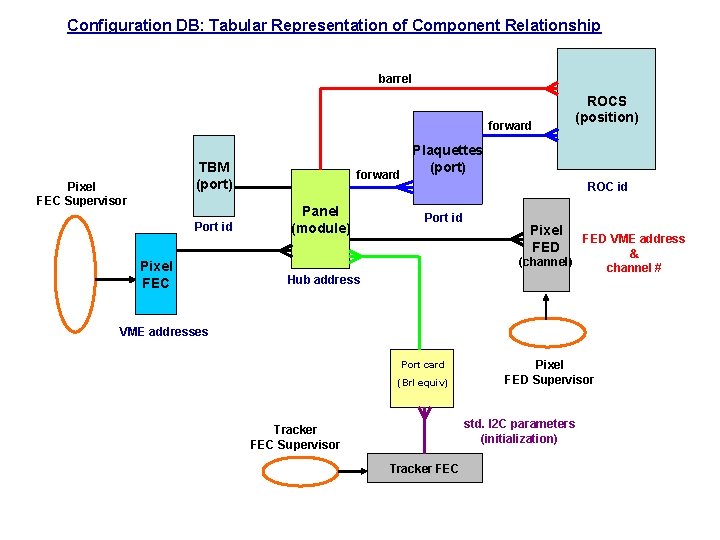

Configuration DB: Tabular Representation of Component Relationship barrel forward TBM (port) Pixel FEC Supervisor Port id Pixel FEC forward Panel (module) ROCS (position) Plaquettes (port) ROC id Port id Pixel FED VME address & (channel) channel # Hub address VME addresses Port card (Brl equiv) Pixel FED Supervisor std. I 2 C parameters (initialization) Tracker FEC Supervisor Tracker FEC

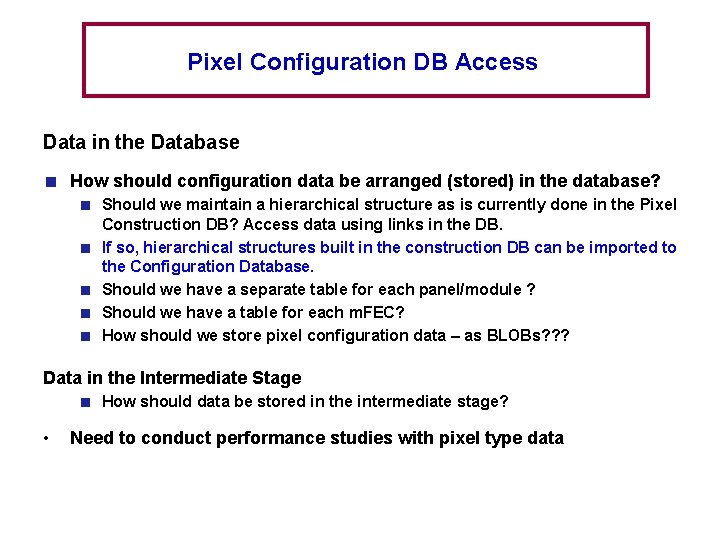

Pixel Configuration DB Access Data in the Database How should configuration data be arranged (stored) in the database? Should we maintain a hierarchical structure as is currently done in the Pixel Construction DB? Access data using links in the DB. If so, hierarchical structures built in the construction DB can be imported to the Configuration Database. Should we have a separate table for each panel/module ? Should we have a table for each m. FEC? How should we store pixel configuration data – as BLOBs? ? ? Data in the Intermediate Stage How should data be stored in the intermediate stage? • Need to conduct performance studies with pixel type data

- Slides: 13