CMOS Monolithic Sensors with Sparsified Readout and Time

- Slides: 14

CMOS Monolithic Sensors with Sparsified Readout and Time Stamping Capabilities for Vertexing Applications at the ILC L. Rattia, c, E. Pozzatia, c, C. Andreolia, c, M. Manghisonib, c, V. Reb, c, V. Spezialia, c, G. Traversib, c a. Università b. Università degli Studi di Pavia degli Studi di Bergamo c. INFN Pavia International Linear Collider Workshop Valencia, 6 -10 November 2006

MAPS for vertexing applications Tracking and vertexing systems in future high luminosity colliders (ILC, SLHC, Super B-Factory) will be operated at high rate with low material budget to optimize position and momentum resolution Monolithic active pixel sensors (MAPS) may provide the required low mass and high granularity An ambitious goal is to design MAPS with similar readout functionalities as in hybrid pixels (sparsification, time stamping, e. g. FPIX) A readout architecture with data sparsification would be a new feature which could give some advantages with respect to existing MAPS implementations flexibility in dealing with possible luminosity and background changes during the experiment lifespan decouple modularity from readout speed reduce digital power dissipation Modern VLSI CMOS processes (130 nm and below) could be exploited to increase the functionality in the elementary cell ILC Workshop 2006 – Valencia, 6 -10 November 2006 2

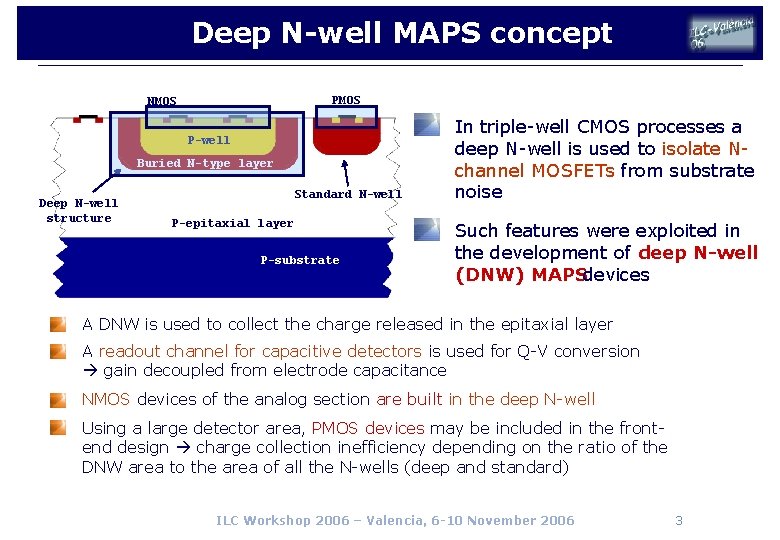

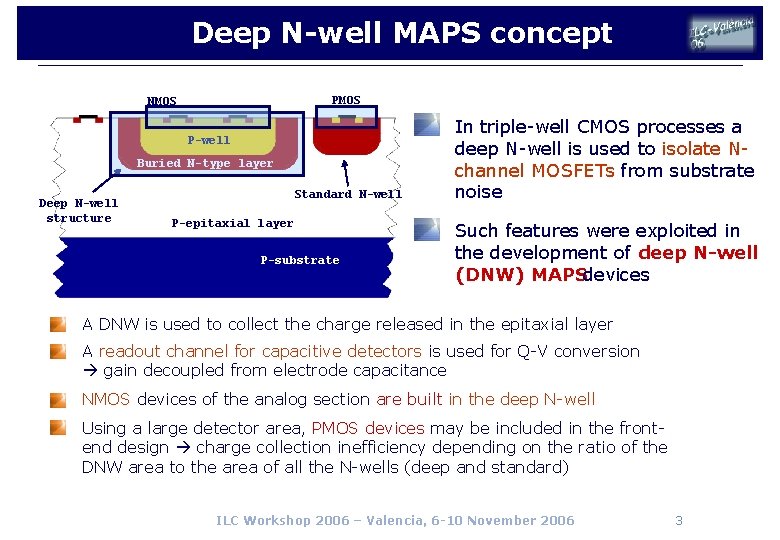

Deep N-well MAPS concept PMOS NMOS P-well Buried N-type layer Deep N-well structure Standard N-well P-epitaxial layer P-substrate In triple-well CMOS processes a deep N-well is used to isolate Nchannel MOSFETs from substrate noise Such features were exploited in the development of deep N-well (DNW) MAPSdevices A DNW is used to collect the charge released in the epitaxial layer A readout channel for capacitive detectors is used for Q-V conversion gain decoupled from electrode capacitance NMOS devices of the analog section are built in the deep N-well Using a large detector area, PMOS devices may be included in the frontend design charge collection inefficiency depending on the ratio of the DNW area to the area of all the N-wells (deep and standard) ILC Workshop 2006 – Valencia, 6 -10 November 2006 3

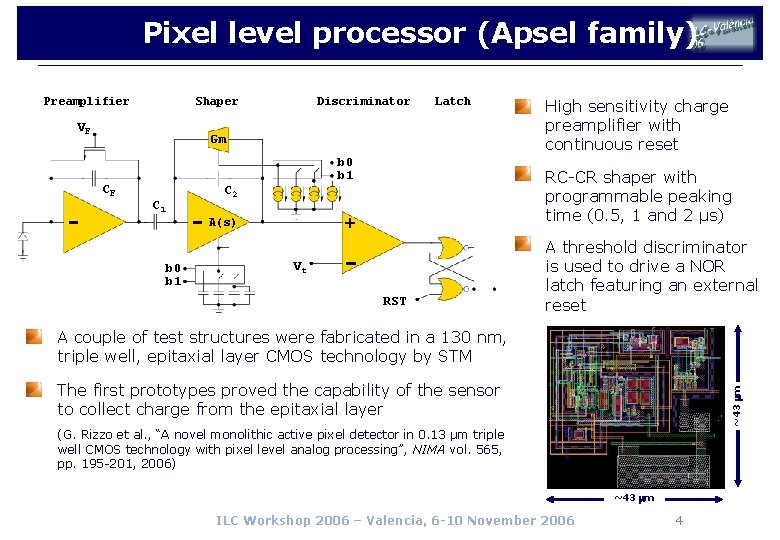

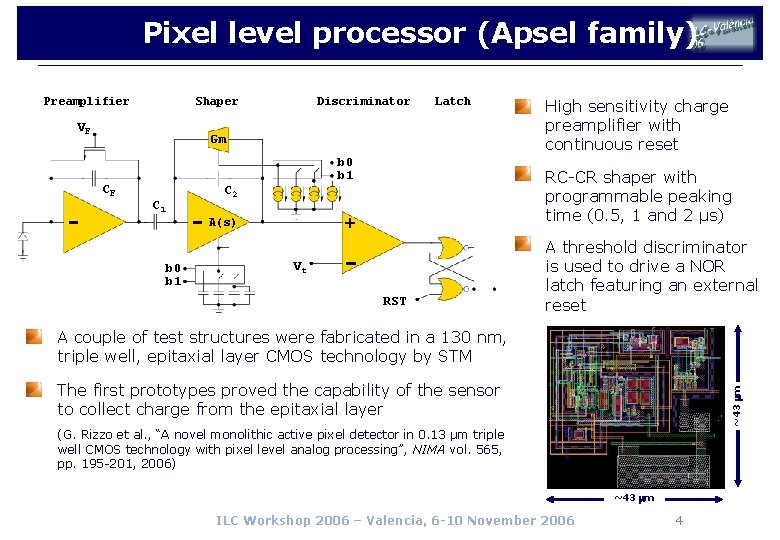

Pixel level processor (Apsel family) Preamplifier Shaper VF Discriminator Latch Gm CF b 0 b 1 C 2 C 1 RC-CR shaper with programmable peaking time (0. 5, 1 and 2 μs) + A(s) Vt b 0 b 1 NMOS P-well High sensitivity charge preamplifier with continuous reset PMOS RST PMOS A threshold discriminator is used to drive a NOR latch featuring an external reset A couple of test structures were fabricated in a 130 nm, triple well, epitaxial layer CMOS technology by STM ~43 mm The first prototypes proved the capability of the sensor to collect charge from the epitaxial layer (G. Rizzo et al. , “A novel monolithic active pixel detector in 0. 13 μm triple well CMOS technology with pixel level analog processing”, NIMA vol. 565, pp. 195 -201, 2006) ~43 mm ILC Workshop 2006 – Valencia, 6 -10 November 2006 4

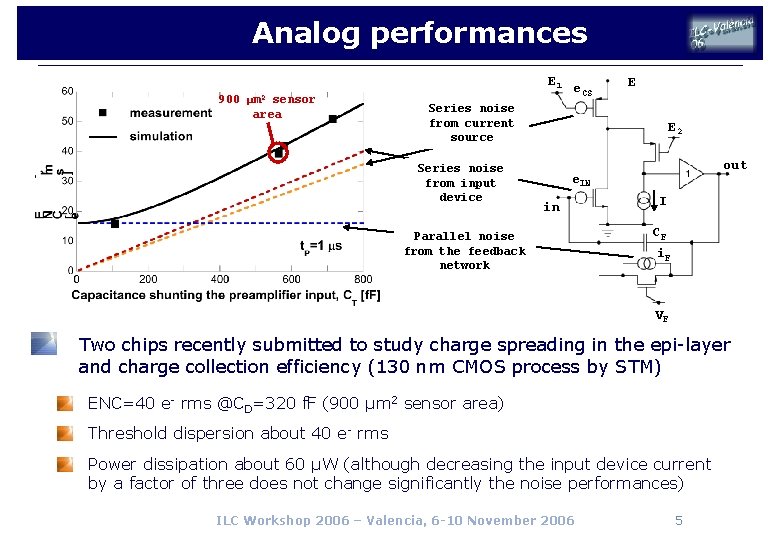

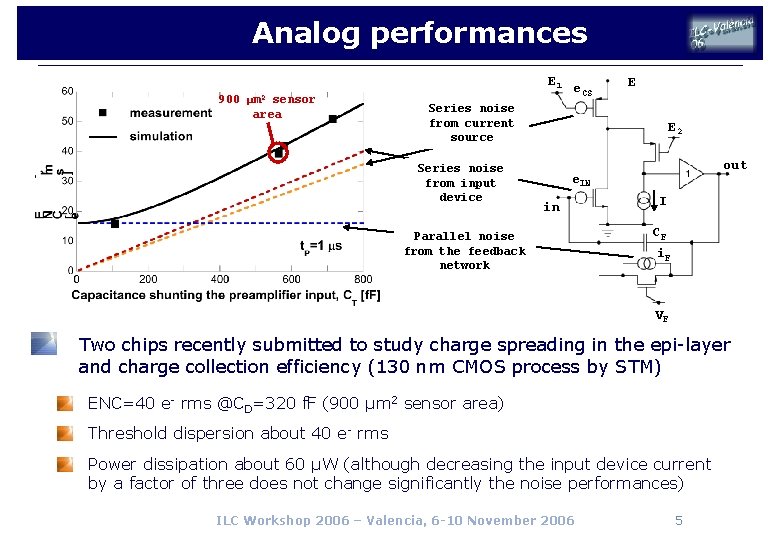

Analog performances E 1 900 μm 2 sensor area e. CS E Series noise from current source Series noise from input device E 2 out e. IN in Parallel noise from the feedback network I CF i. F VF Two chips recently submitted to study charge spreading in the epi-layer and charge collection efficiency (130 nm CMOS process by STM) ENC=40 e- rms @CD=320 f. F (900 μm 2 sensor area) Threshold dispersion about 40 e- rms Power dissipation about 60 μW (although decreasing the input device current by a factor of three does not change significantly the noise performances) ILC Workshop 2006 – Valencia, 6 -10 November 2006 5

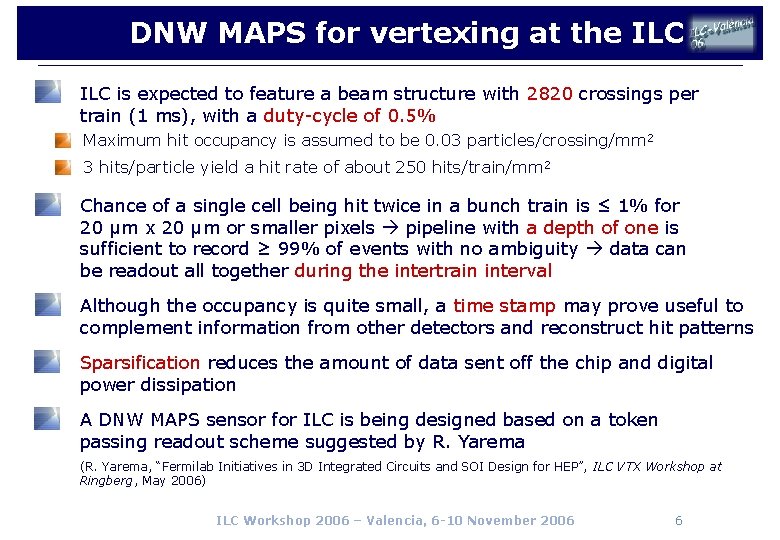

DNW MAPS for vertexing at the ILC is expected to feature a beam structure with 2820 crossings per train (1 ms), with a duty-cycle of 0. 5% Maximum hit occupancy is assumed to be 0. 03 particles/crossing/mm 2 3 hits/particle yield a hit rate of about 250 hits/train/mm 2 Chance of a single cell being hit twice in a bunch train is ≤ 1% for 20 μm x 20 μm or smaller pixels pipeline with a depth of one is sufficient to record ≥ 99% of events with no ambiguity data can be readout all together during the intertrain interval Although the occupancy is quite small, a time stamp may prove useful to complement information from other detectors and reconstruct hit patterns Sparsification reduces the amount of data sent off the chip and digital power dissipation A DNW MAPS sensor for ILC is being designed based on a token passing readout scheme suggested by R. Yarema (R. Yarema, “Fermilab Initiatives in 3 D Integrated Circuits and SOI Design for HEP”, ILC VTX Workshop at Ringberg, May 2006) ILC Workshop 2006 – Valencia, 6 -10 November 2006 6

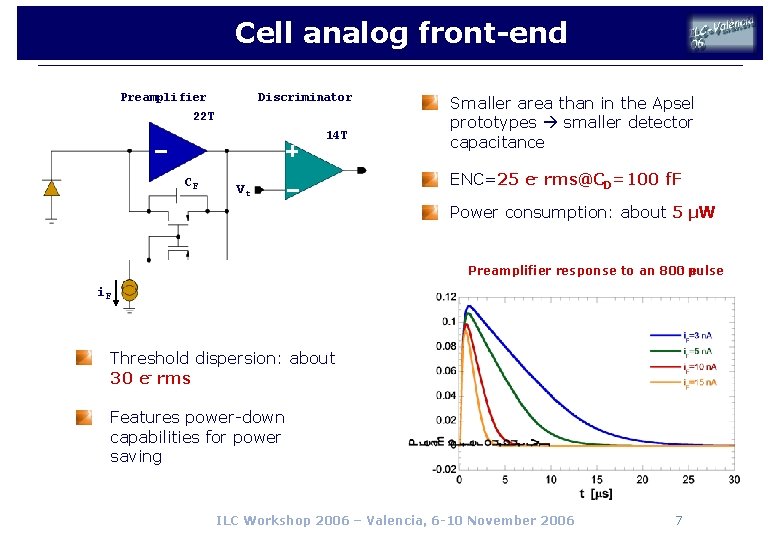

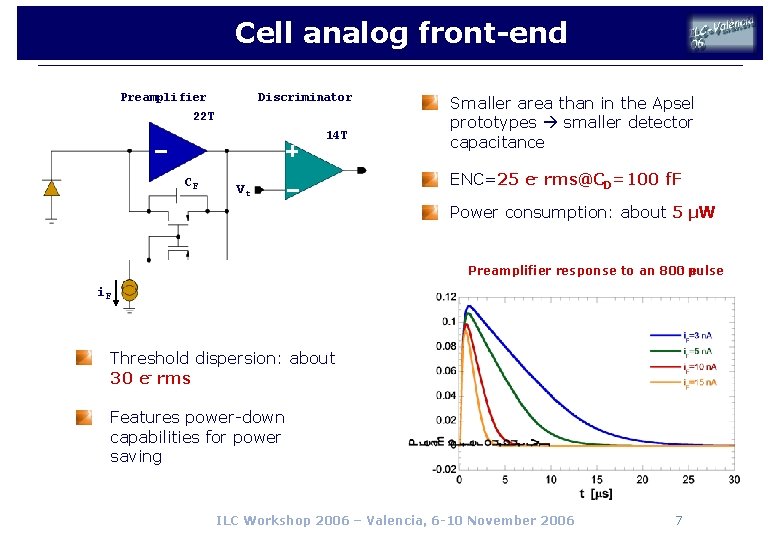

Cell analog front-end Preamplifier Discriminator 22 T 14 T CF Vt Smaller area than in the Apsel prototypes smaller detector capacitance ENC=25 e- rms@CD=100 f. F Power consumption: about 5 μW Preamplifier response to an 800 - pulse e i. F Threshold dispersion: about 30 e- rms Features power-down capabilities for power saving ILC Workshop 2006 – Valencia, 6 -10 November 2006 7

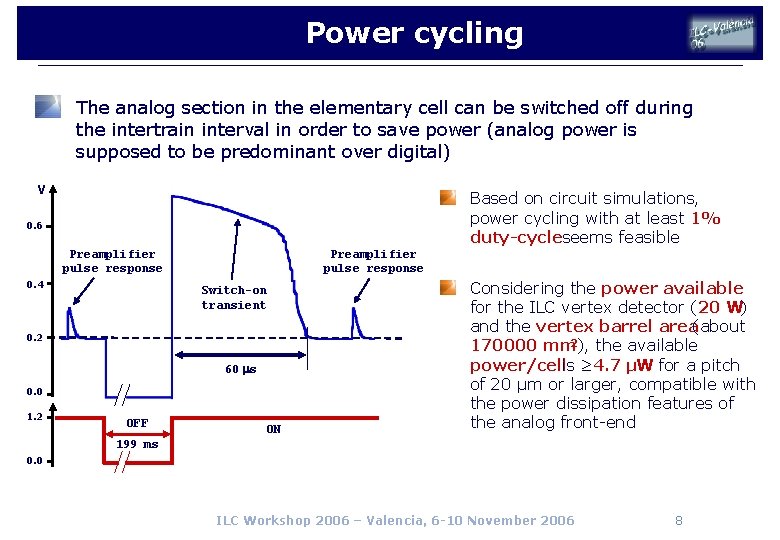

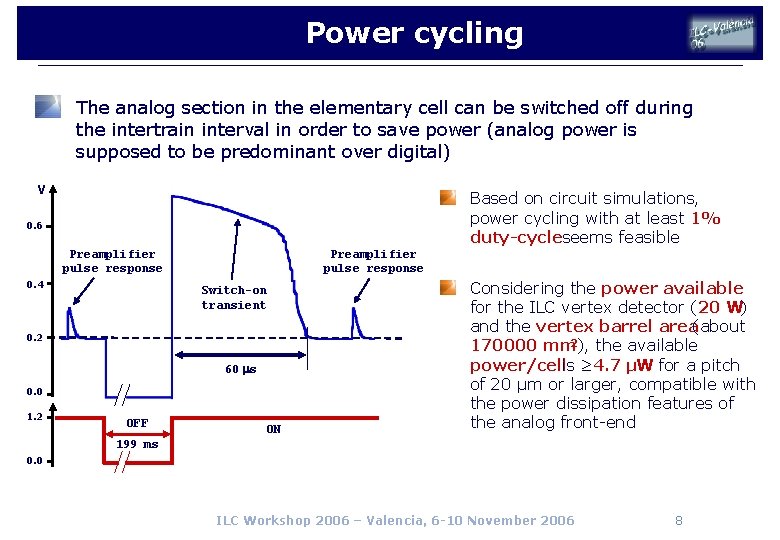

Power cycling The analog section in the elementary cell can be switched off during the intertrain interval in order to save power (analog power is supposed to be predominant over digital) V Based on circuit simulations, power cycling with at least 1% duty-cycleseems feasible 0. 6 Preamplifier pulse response 0. 4 Preamplifier pulse response Switch-on transient 0. 2 60 ms 0. 0 1. 2 OFF ON Considering the power available for the ILC vertex detector (20 W) and the vertex barrel area(about 170000 mm 2), the available power/cellis ≥ 4. 7 μW for a pitch of 20 μm or larger, compatible with the power dissipation features of the analog front-end 199 ms 0. 0 ILC Workshop 2006 – Valencia, 6 -10 November 2006 8

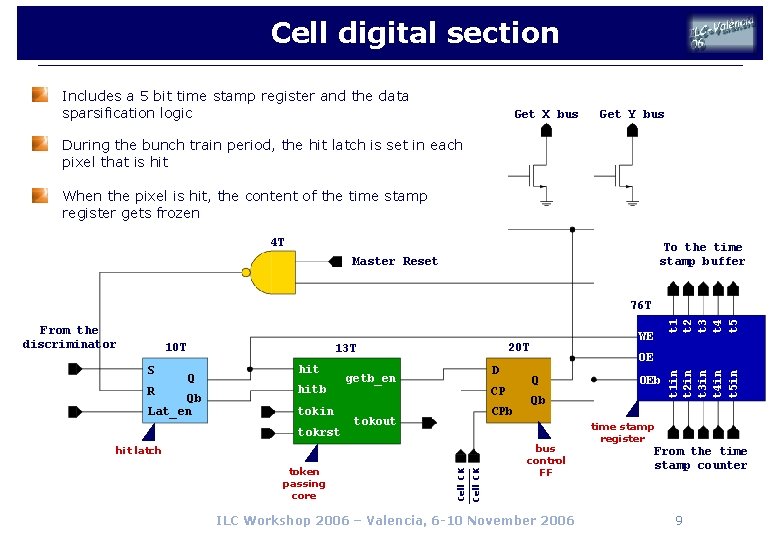

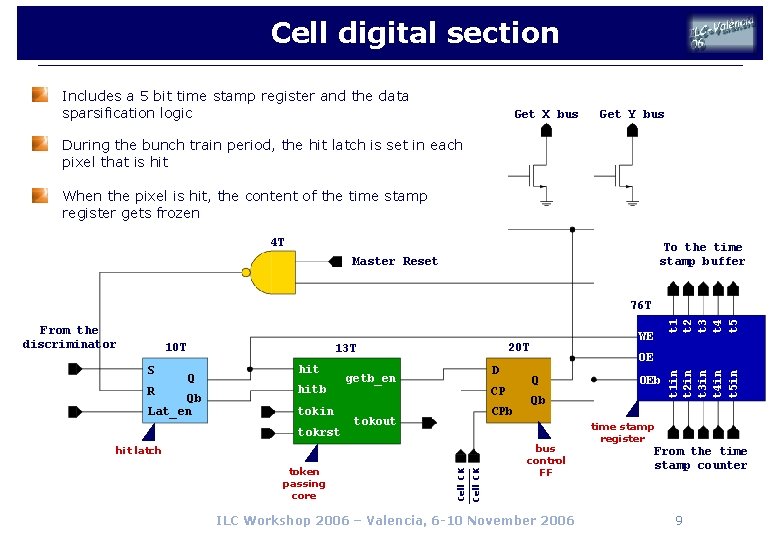

Cell digital section Includes a 5 bit time stamp register and the data sparsification logic Get X bus Get Y bus During the bunch train period, the hit latch is set in each pixel that is hit When the pixel is hit, the content of the time stamp register gets frozen 4 T To the time stamp buffer Master Reset 10 T S R 13 T Q Qb Lat_en hitb tokin tokrst D getb_en CP CPb tokout Cell CK hit latch token passing core WE 20 T OE Q OEb Qb bus control FF ILC Workshop 2006 – Valencia, 6 -10 November 2006 t 1 in t 2 in t 3 in t 4 in t 5 in From the discriminator t 1 t 2 t 3 t 4 t 5 76 T time stamp register From the time stamp counter 9

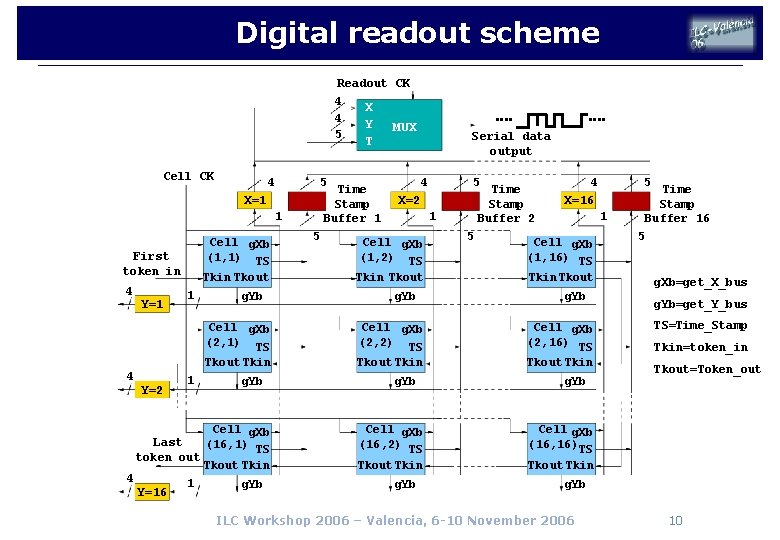

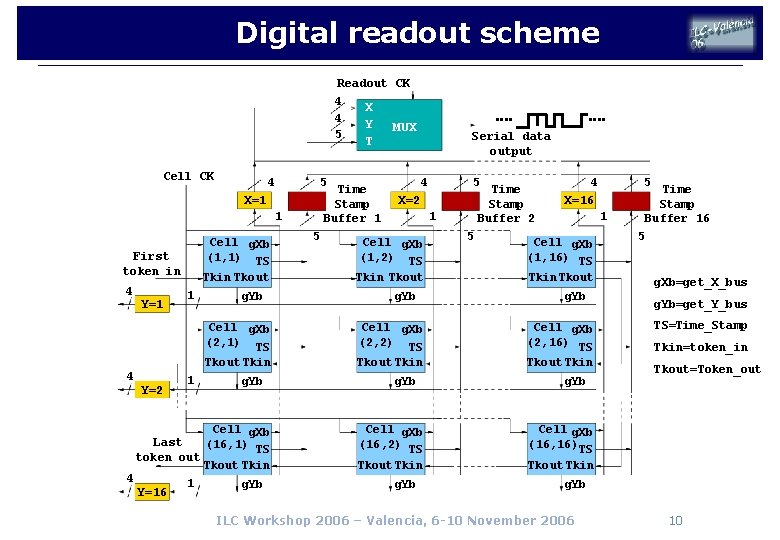

Digital readout scheme Readout CK 4 X 4 Y MUX 5 T Cell CK 4 5 Time Stamp Buffer 1 X=1 1 Cell g. Xb (1, 1) TS Tkin Tkout First token in 4 Y=1 1 g. Yb Cell g. Xb (2, 1) TS Tkout Tkin 4 Y=2 1 g. Yb Cell g. Xb Last (16, 1) TS token out Tkin 4 1 g. Yb Y=16 5 Serial data output 4 5 Time Stamp Buffer 2 X=2 1 Cell g. Xb (1, 2) TS Tkin Tkout g. Yb Cell g. Xb (2, 2) TS Tkout Tkin g. Yb Cell g. Xb (16, 2) TS Tkout. Tkin g. Yb 5 4 X=16 5 Time Stamp Buffer 16 1 Cell g. Xb (1, 16) TS Tkin. Tkout g. Yb Cell g. Xb (2, 16) TS Tkout Tkin g. Yb 5 g. Xb=get_X_bus g. Yb=get_Y_bus TS=Time_Stamp Tkin=token_in Tkout=Token_out Cell g. Xb (16, 16)TS Tkout Tkin g. Yb ILC Workshop 2006 – Valencia, 6 -10 November 2006 10

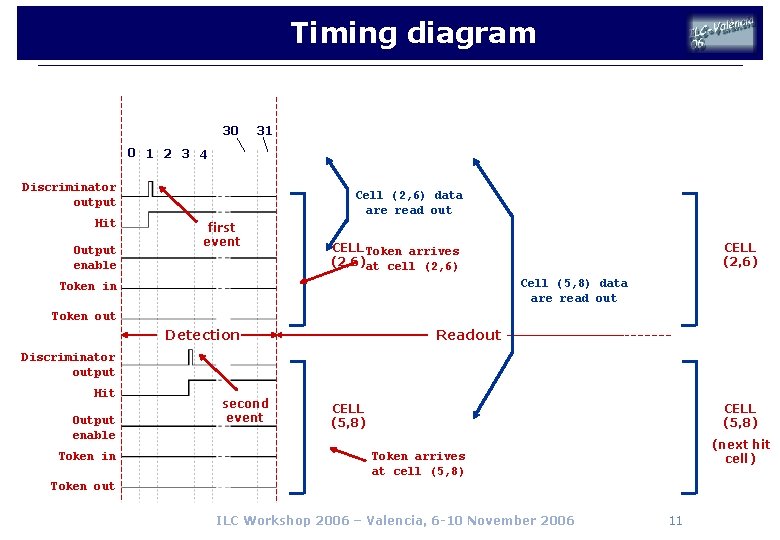

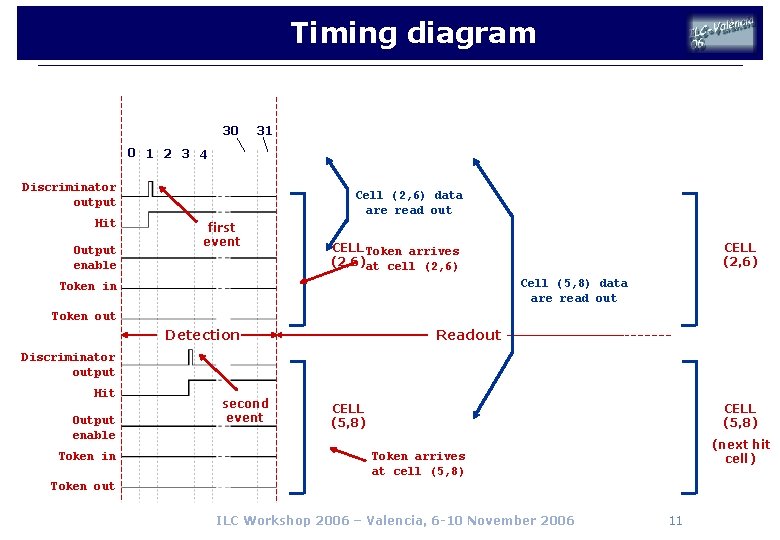

Timing diagram CELL (2, 6) X Y TS 30 CELL (5, 8) X Y TS 31 0 1 2 3 4 Cell CK Discriminator output Hit Output enable Serial Data Output Cell (2, 6) data are read out first event CELL (2, 6) CELL Token arrives Data output (2, 6) at cell (2, 6) Cell (5, 8) data are read out Token in Token out Detection Readout Discriminator output Hit Output enable Token in second event CELL (5, 8) Data output (next hit cell) Token arrives at cell (5, 8) Token out ILC Workshop 2006 – Valencia, 6 -10 November 2006 11

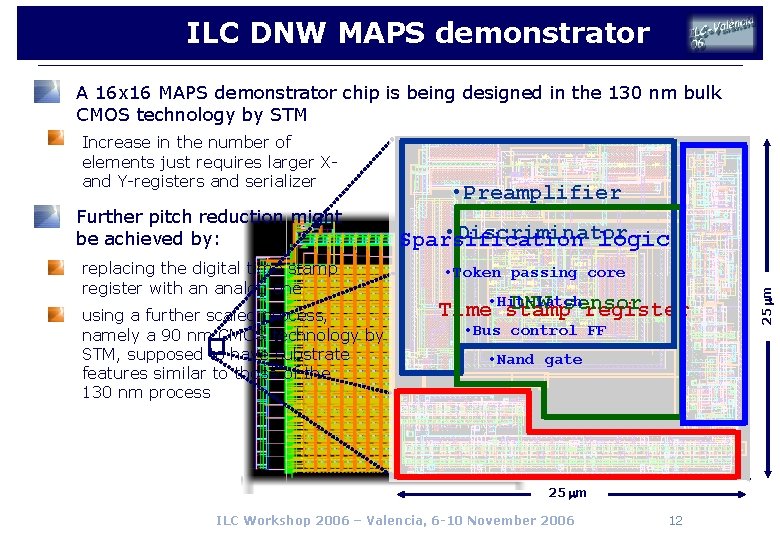

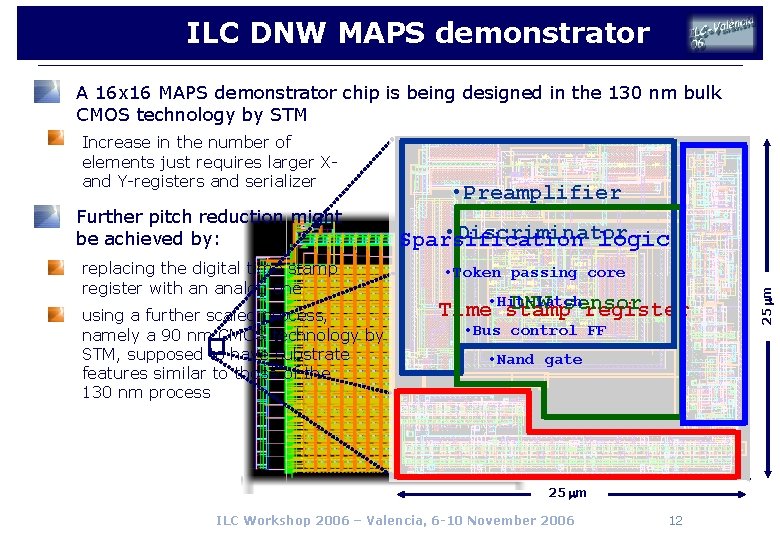

ILC DNW MAPS demonstrator A 16 x 16 MAPS demonstrator chip is being designed in the 130 nm bulk CMOS technology by STM Further pitch reduction might be achieved by: replacing the digital time stamp register with an analog one using a further scaled process, namely a 90 nm CMOS technology by STM, supposed to have substrate features similar to those of the 130 nm process • Preamplifier • Discriminator Sparsification logic • Token passing core DNW sensor Time • Hit-latch stamp register • Bus control FF • Nand gate 25 mm ILC Workshop 2006 – Valencia, 6 -10 November 2006 12 25 mm Increase in the number of elements just requires larger Xand Y-registers and serializer

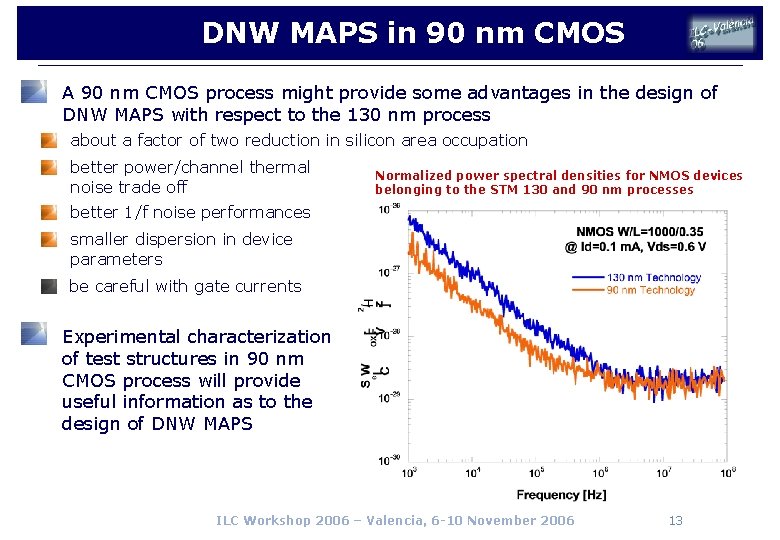

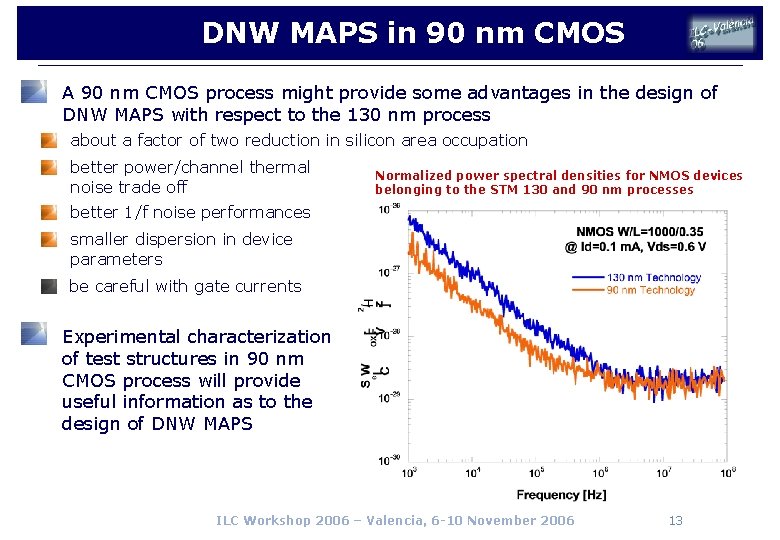

DNW MAPS in 90 nm CMOS A 90 nm CMOS process might provide some advantages in the design of DNW MAPS with respect to the 130 nm process about a factor of two reduction in silicon area occupation better power/channel thermal noise trade off Normalized power spectral densities for NMOS devices belonging to the STM 130 and 90 nm processes better 1/f noise performances smaller dispersion in device parameters be careful with gate currents Experimental characterization of test structures in 90 nm CMOS process will provide useful information as to the design of DNW MAPS ILC Workshop 2006 – Valencia, 6 -10 November 2006 13

Conclusions A DNW MAPS demonstrator aimed at vertexing applications at the ILC is being designed in a 130 nm bulk CMOS technology The chip is capable of sparsified readout, time stamp generation and is compatible with power cycling operation Simulations show good noise and threshold dispersion performances at a power dissipation close to the ILC vertex specifications Further activities are under way to optimize the elementary cell size and geometry, including simplification of the pixel cell logic MAPS development in a 90 nm CMOS technology physical device simulations ILC Workshop 2006 – Valencia, 6 -10 November 2006 14