Assertions in Open Vera Assertions check for the

![Multiple Sequences of Evaluation e 1 #[1. . 3] (ack==0) e 1 #1 (ack==0) Multiple Sequences of Evaluation e 1 #[1. . 3] (ack==0) e 1 #1 (ack==0)](https://slidetodoc.com/presentation_image/60402655fdd0512c65efa511e2509d87/image-9.jpg)

- Slides: 9

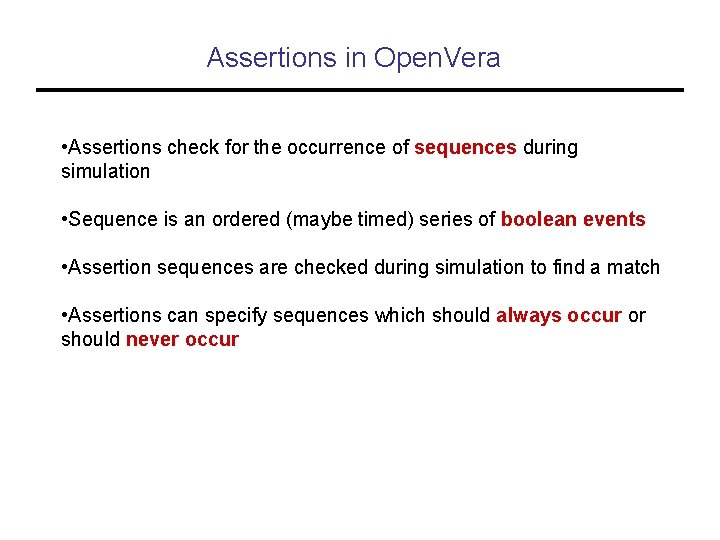

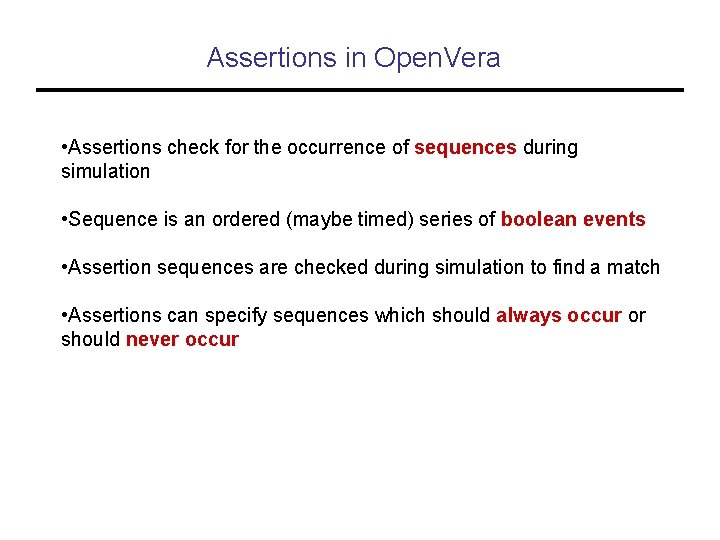

Assertions in Open. Vera • Assertions check for the occurrence of sequences during simulation • Sequence is an ordered (maybe timed) series of boolean events • Assertion sequences are checked during simulation to find a match • Assertions can specify sequences which should always occur or should never occur

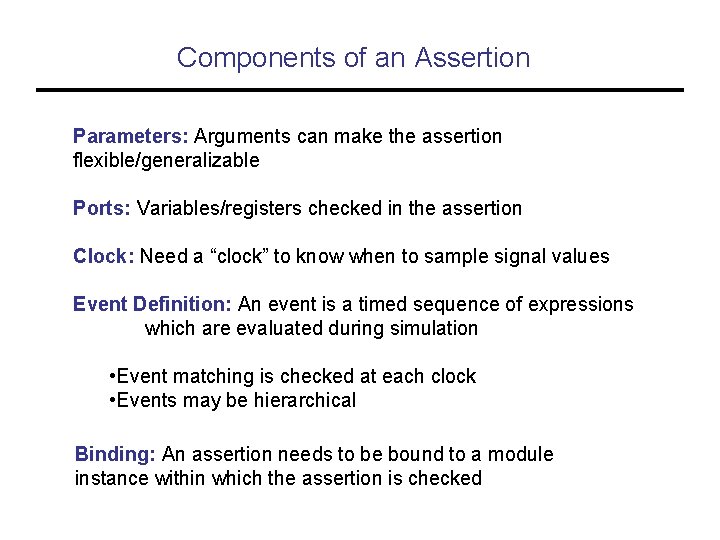

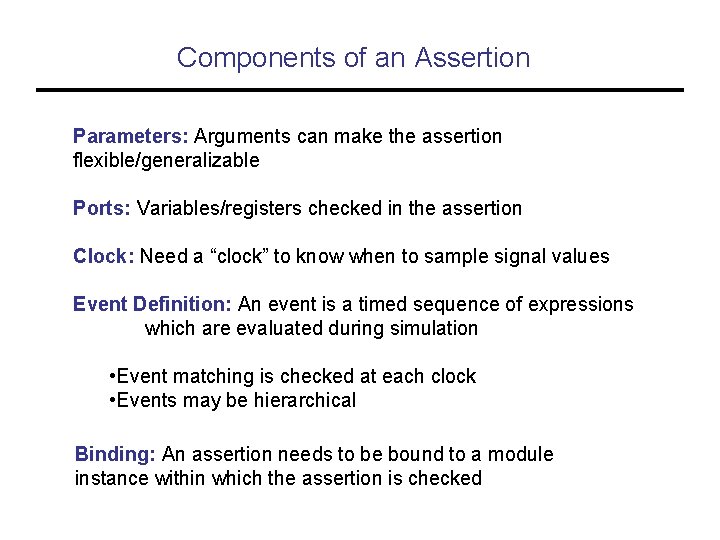

Components of an Assertion Parameters: Arguments can make the assertion flexible/generalizable Ports: Variables/registers checked in the assertion Clock: Need a “clock” to know when to sample signal values Event Definition: An event is a timed sequence of expressions which are evaluated during simulation • Event matching is checked at each clock • Events may be hierarchical Binding: An assertion needs to be bound to a module instance within which the assertion is checked

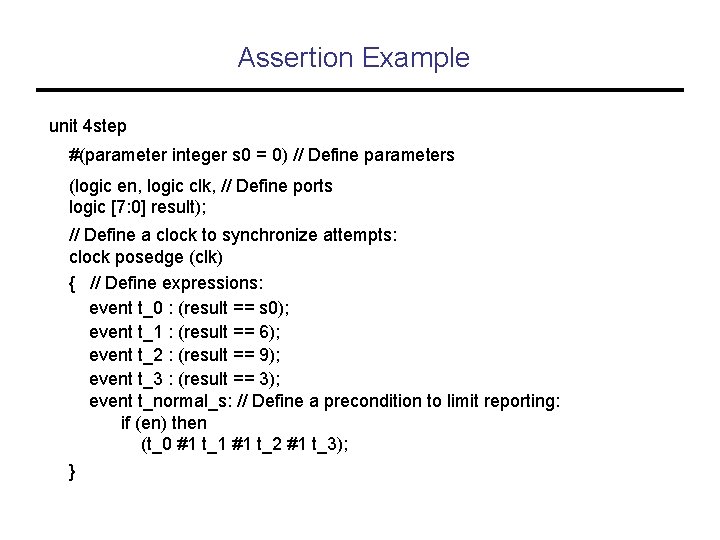

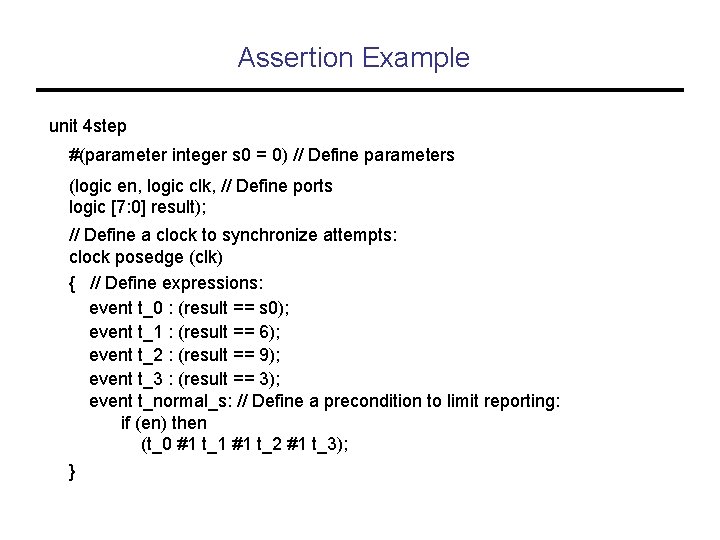

Assertion Example unit 4 step #(parameter integer s 0 = 0) // Define parameters (logic en, logic clk, // Define ports logic [7: 0] result); // Define a clock to synchronize attempts: clock posedge (clk) { // Define expressions: event t_0 : (result == s 0); event t_1 : (result == 6); event t_2 : (result == 9); event t_3 : (result == 3); event t_normal_s: // Define a precondition to limit reporting: if (en) then (t_0 #1 t_1 #1 t_2 #1 t_3); }

Assertion Example Continued // Define an assertion: assert c_normal_s : check(t_normal_s, "Missed a step. "); endunit /* Bind the unit to one or more instances in the design. */ // bind module cnt : // All instances of cnt or bind instances cnt_top. dut : // one instance. 4 step start_4 // Name the unit instance. #(4) // Specify parameters. (!reset, m_clk, outp); // Specify ports.

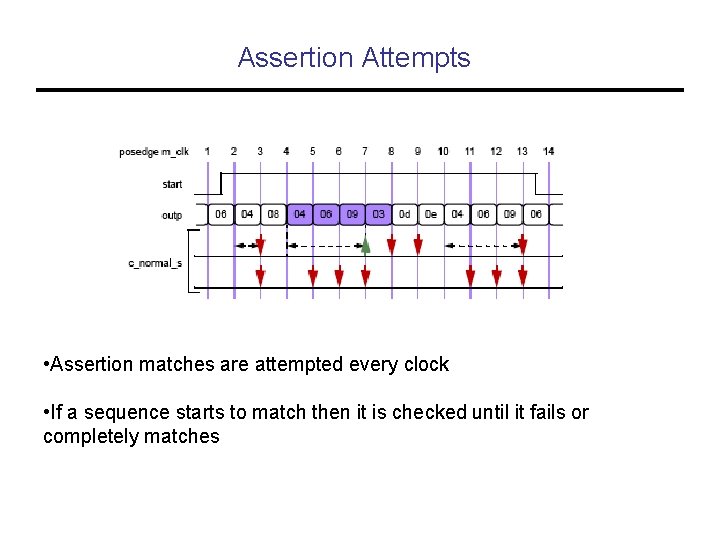

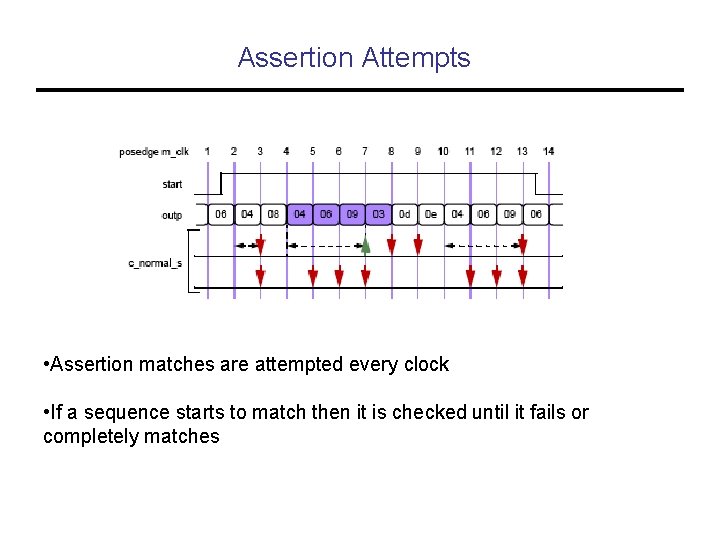

Assertion Attempts • Assertion matches are attempted every clock • If a sequence starts to match then it is checked until it fails or completely matches

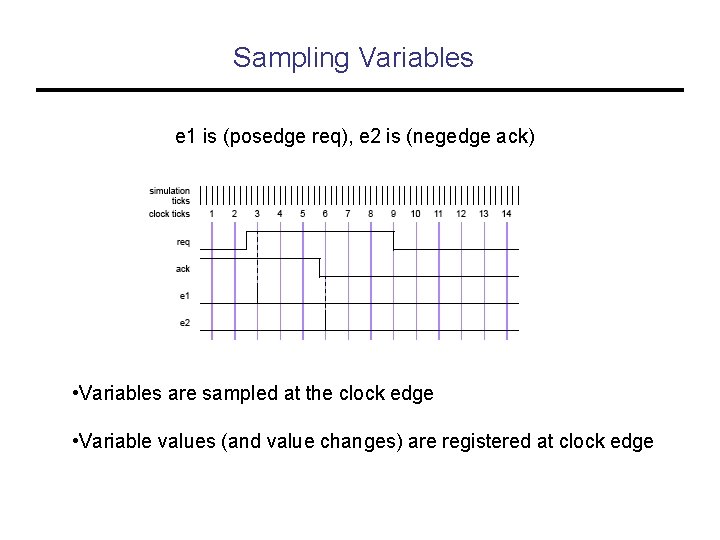

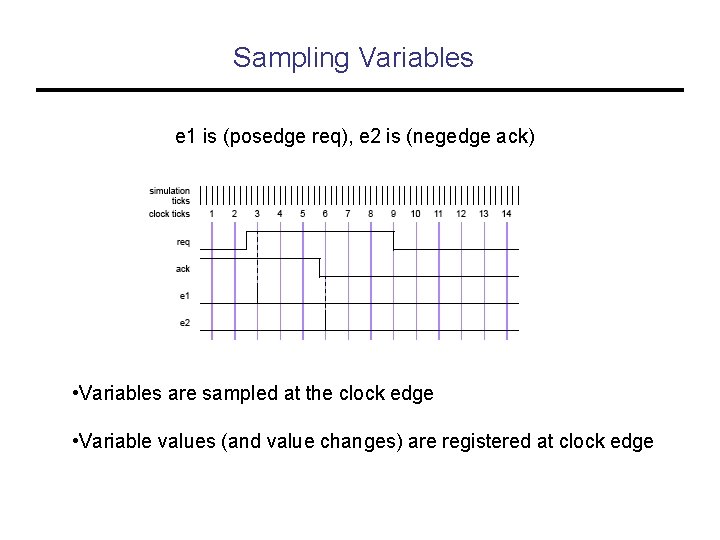

Sampling Variables e 1 is (posedge req), e 2 is (negedge ack) • Variables are sampled at the clock edge • Variable values (and value changes) are registered at clock edge

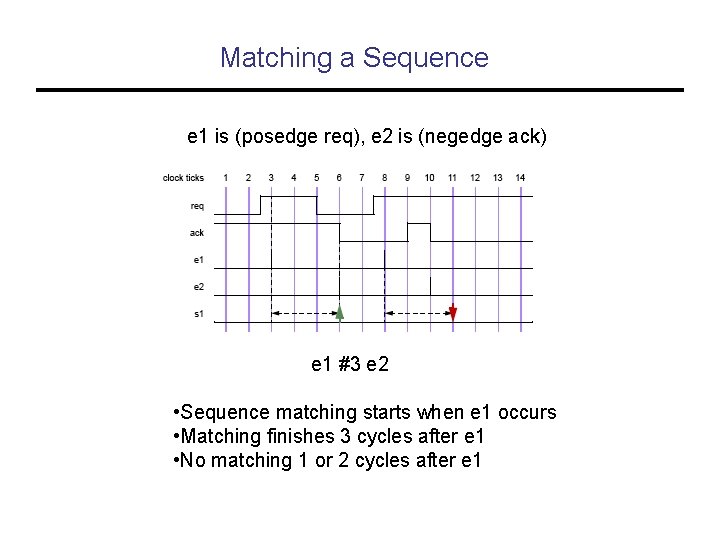

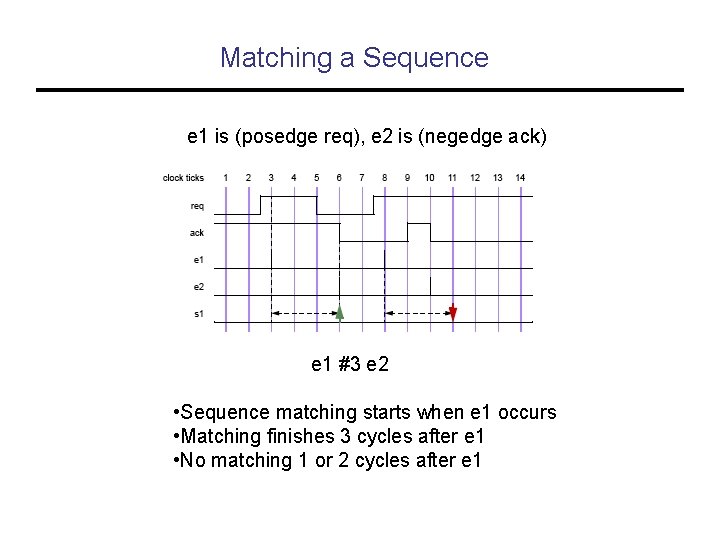

Matching a Sequence e 1 is (posedge req), e 2 is (negedge ack) e 1 #3 e 2 • Sequence matching starts when e 1 occurs • Matching finishes 3 cycles after e 1 • No matching 1 or 2 cycles after e 1

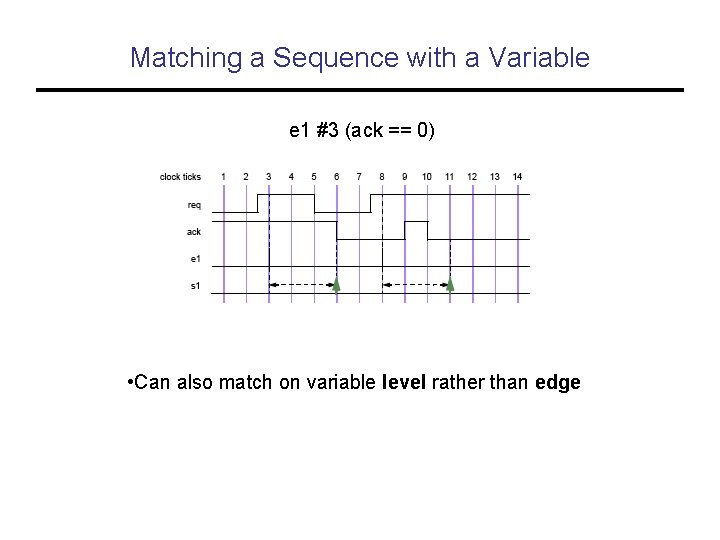

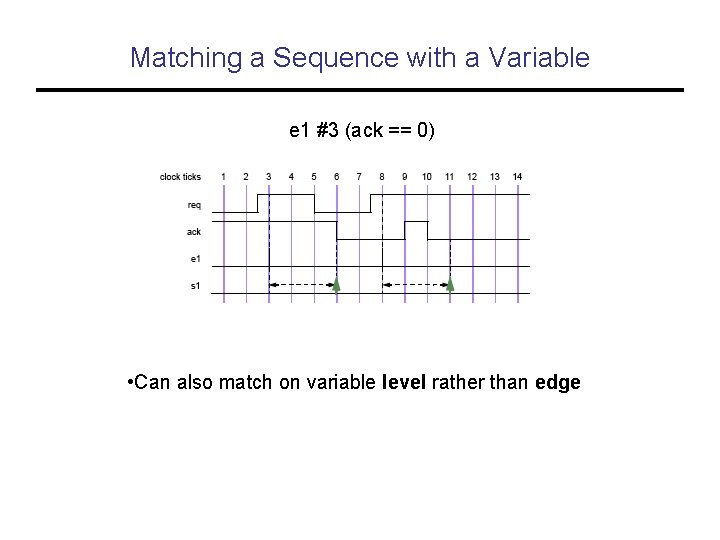

Matching a Sequence with a Variable e 1 #3 (ack == 0) • Can also match on variable level rather than edge

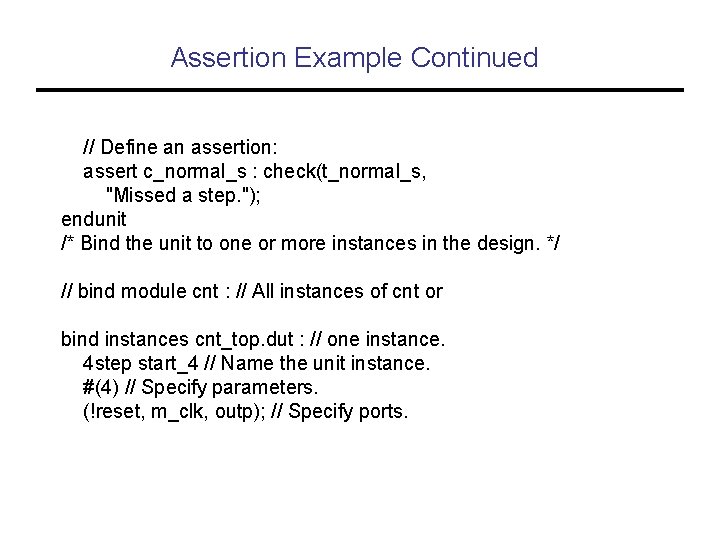

![Multiple Sequences of Evaluation e 1 1 3 ack0 e 1 1 ack0 Multiple Sequences of Evaluation e 1 #[1. . 3] (ack==0) e 1 #1 (ack==0)](https://slidetodoc.com/presentation_image/60402655fdd0512c65efa511e2509d87/image-9.jpg)

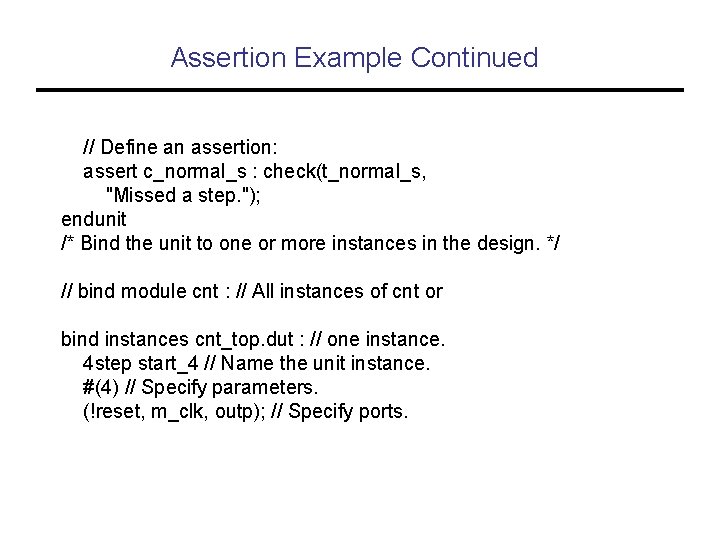

Multiple Sequences of Evaluation e 1 #[1. . 3] (ack==0) e 1 #1 (ack==0) e 1 #2 (ack==0) e 1 #3 (ack==0) • Timing ranges causes matching to branch out to check multiple alternatives