Assembly Language for IntelBased Computers 4 th Edition

Assembly Language for Intel-Based Computers, 4 th Edition Kip R. Irvine Chapter 4: Data Transfers, Addressing, and Arithmetic Lecture 14 Slides prepared by Kip R. Irvine Revision date: 09/26/2002 Modified by Dr. Nikolay Metodiev Sirakov-3/1/2005 • Chapter corrections (Web) Assembly language sources (Web) (c) Pearson Education, 2002. All rights reserved. You may modify and copy this slide show for your personal use, or for use in the classroom, as long as this copyright statement, the author's name, and the title are not changed.

Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

Data Transfer Instructions • • Operand Types Instruction Operand Notation Direct Memory Operands MOV Instruction Zero & Sign Extension LAHF and SAHF Instructions XCHG Instruction Direct-Offset Instructions Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

Operand Types • Three basic types of operands: • Immediate – a constant integer (8, 16, or 32 bits) • value is encoded within the instruction • Register – the name of a register • register name is converted to a number and encoded within the instruction • Memory – reference to a location in memory • memory address is encoded within the instruction, or a register holds the address of a memory location Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

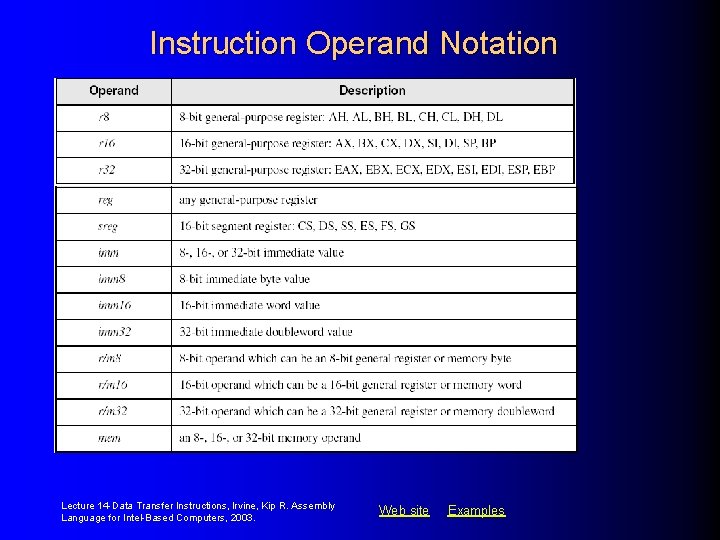

Instruction Operand Notation Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

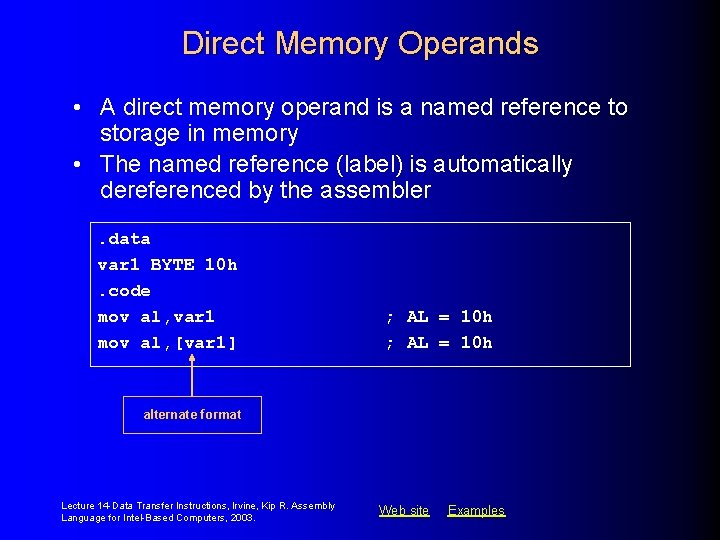

Direct Memory Operands • A direct memory operand is a named reference to storage in memory • The named reference (label) is automatically dereferenced by the assembler. data var 1 BYTE 10 h. code mov al, var 1 mov al, [var 1] ; AL = 10 h alternate format Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

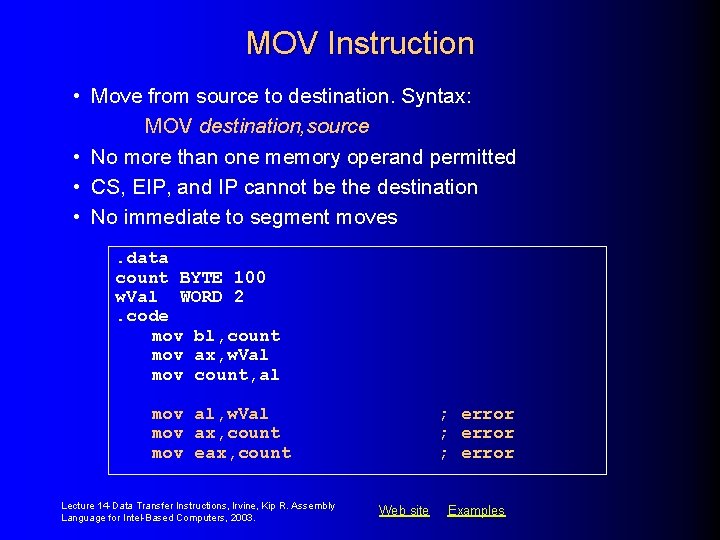

MOV Instruction • Move from source to destination. Syntax: MOV destination, source • No more than one memory operand permitted • CS, EIP, and IP cannot be the destination • No immediate to segment moves. data count BYTE 100 w. Val WORD 2. code mov bl, count mov ax, w. Val mov count, al mov al, w. Val mov ax, count mov eax, count Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. ; error Web site Examples

Your turn. . . Explain why each of the following MOV statements are invalid: . data b. Val BYTE 100 b. Val 2 BYTE ? w. Val WORD 2 d. Val DWORD 5. code mov ds, 45 mov esi, w. Val mov eip, d. Val mov 25, b. Val mov b. Val 2, b. Val Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. ; ; ; Web site a. b. c. d. e. Examples

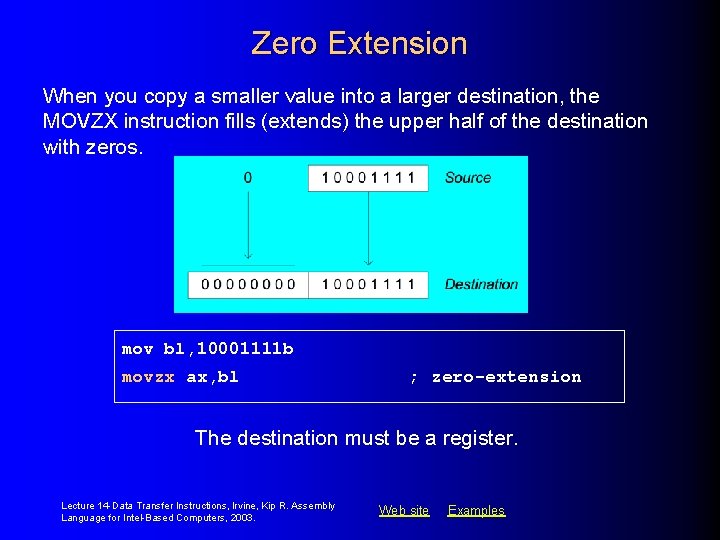

Zero Extension When you copy a smaller value into a larger destination, the MOVZX instruction fills (extends) the upper half of the destination with zeros. mov bl, 10001111 b movzx ax, bl ; zero-extension The destination must be a register. Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

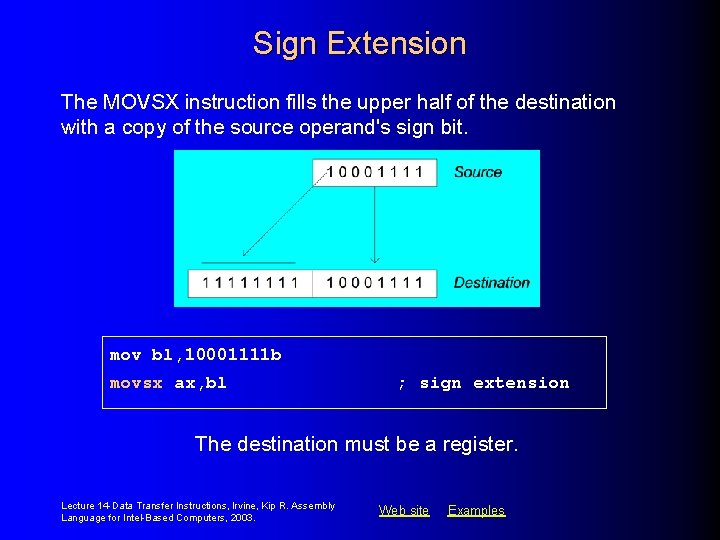

Sign Extension The MOVSX instruction fills the upper half of the destination with a copy of the source operand's sign bit. mov bl, 10001111 b movsx ax, bl ; sign extension The destination must be a register. Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

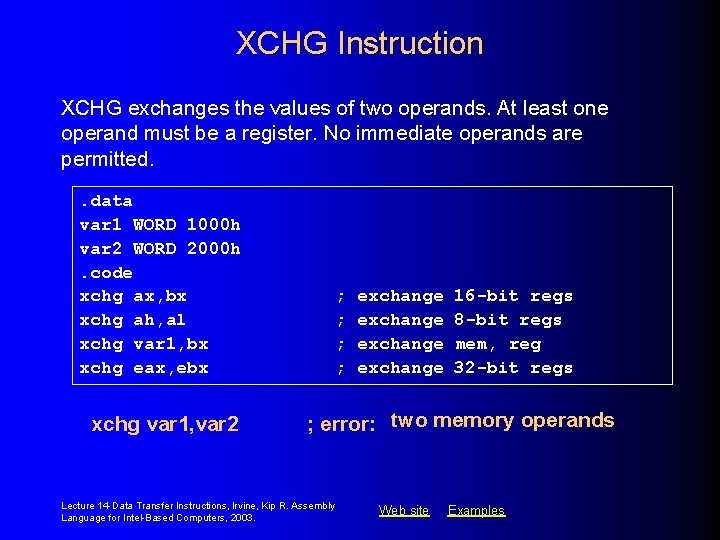

XCHG Instruction XCHG exchanges the values of two operands. At least one operand must be a register. No immediate operands are permitted. . data var 1 WORD 1000 h var 2 WORD 2000 h. code xchg ax, bx xchg ah, al xchg var 1, bx xchg eax, ebx xchg var 1, var 2 ; ; exchange 16 -bit regs 8 -bit regs mem, reg 32 -bit regs ; error: two memory operands Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

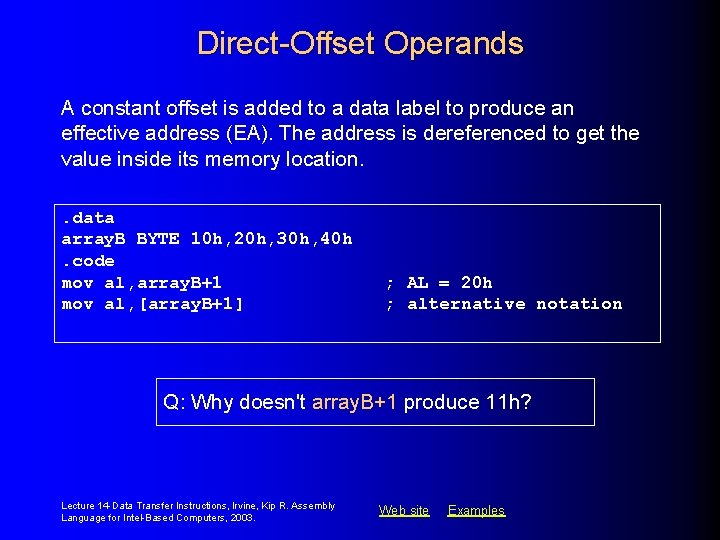

Direct-Offset Operands A constant offset is added to a data label to produce an effective address (EA). The address is dereferenced to get the value inside its memory location. . data array. B BYTE 10 h, 20 h, 30 h, 40 h. code mov al, array. B+1 mov al, [array. B+1] ; AL = 20 h ; alternative notation Q: Why doesn't array. B+1 produce 11 h? Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

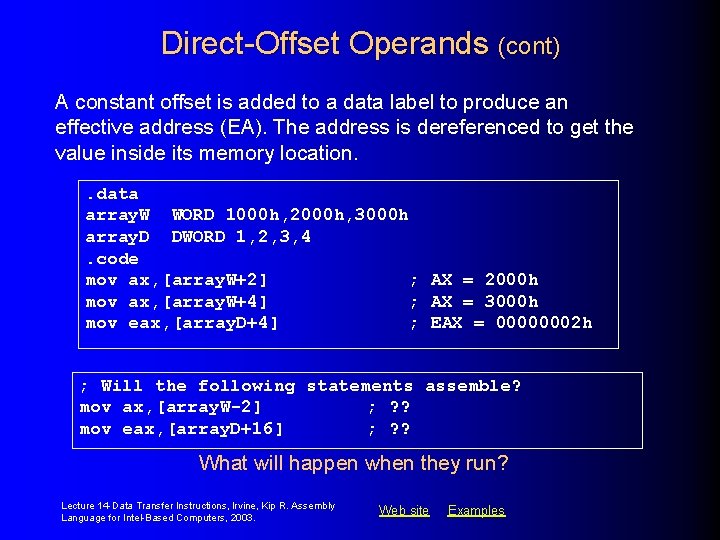

Direct-Offset Operands (cont) A constant offset is added to a data label to produce an effective address (EA). The address is dereferenced to get the value inside its memory location. . data array. W WORD 1000 h, 2000 h, 3000 h array. D DWORD 1, 2, 3, 4. code mov ax, [array. W+2] ; AX = 2000 h mov ax, [array. W+4] ; AX = 3000 h mov eax, [array. D+4] ; EAX = 00000002 h ; Will the following statements assemble? mov ax, [array. W-2] ; ? ? mov eax, [array. D+16] ; ? ? What will happen when they run? Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

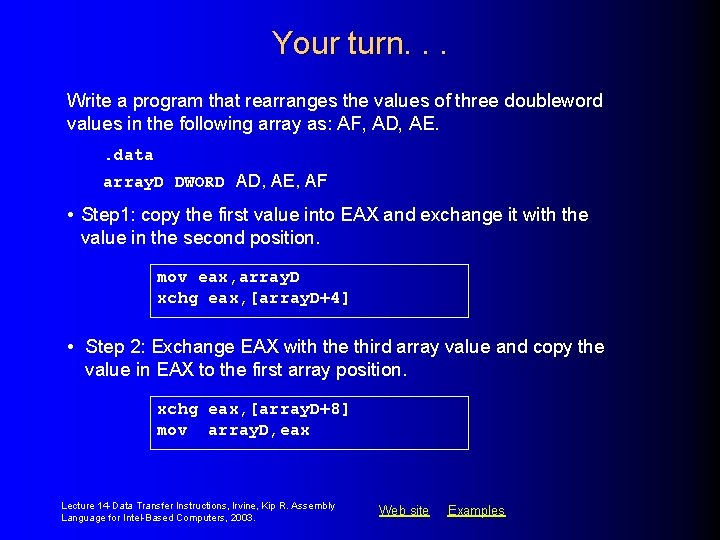

Your turn. . . Write a program that rearranges the values of three doubleword values in the following array as: AF, AD, AE. . data array. D DWORD AD, AE, AF • Step 1: copy the first value into EAX and exchange it with the value in the second position. mov eax, array. D xchg eax, [array. D+4] • Step 2: Exchange EAX with the third array value and copy the value in EAX to the first array position. xchg eax, [array. D+8] mov array. D, eax Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

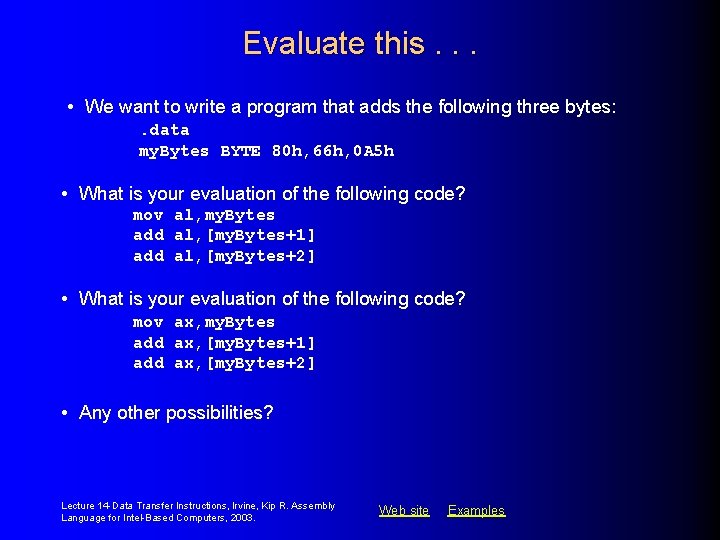

Evaluate this. . . • We want to write a program that adds the following three bytes: . data my. Bytes BYTE 80 h, 66 h, 0 A 5 h • What is your evaluation of the following code? mov al, my. Bytes add al, [my. Bytes+1] add al, [my. Bytes+2] • What is your evaluation of the following code? mov ax, my. Bytes add ax, [my. Bytes+1] add ax, [my. Bytes+2] • Any other possibilities? Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

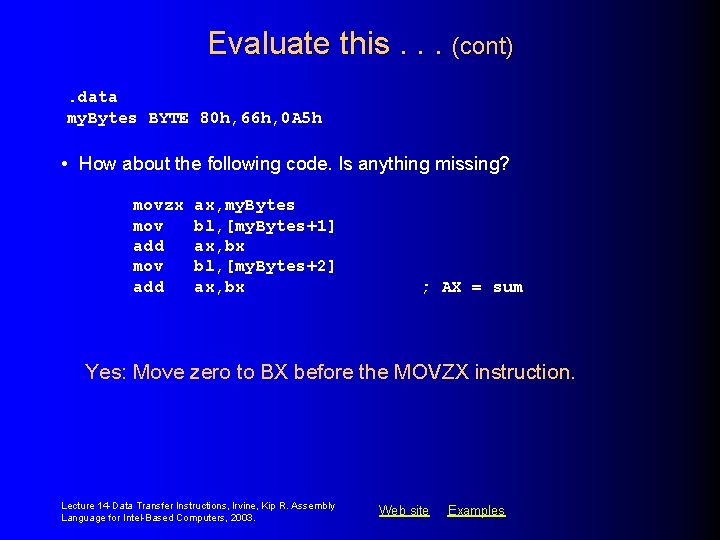

Evaluate this. . . (cont). data my. Bytes BYTE 80 h, 66 h, 0 A 5 h • How about the following code. Is anything missing? movzx mov add ax, my. Bytes bl, [my. Bytes+1] ax, bx bl, [my. Bytes+2] ax, bx ; AX = sum Yes: Move zero to BX before the MOVZX instruction. Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

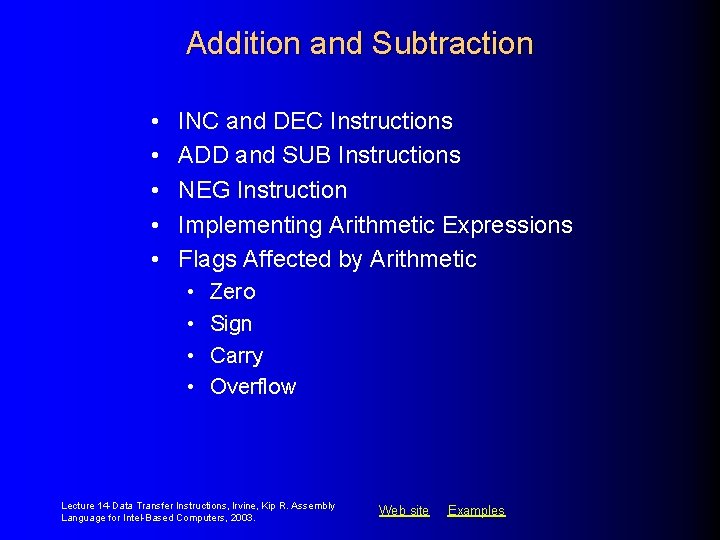

Addition and Subtraction • • • INC and DEC Instructions ADD and SUB Instructions NEG Instruction Implementing Arithmetic Expressions Flags Affected by Arithmetic • • Zero Sign Carry Overflow Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

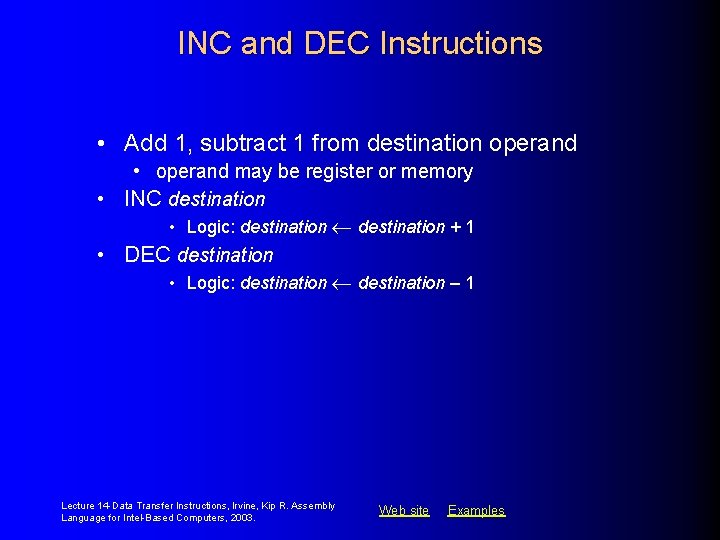

INC and DEC Instructions • Add 1, subtract 1 from destination operand • operand may be register or memory • INC destination • Logic: destination + 1 • DEC destination • Logic: destination – 1 Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. Web site Examples

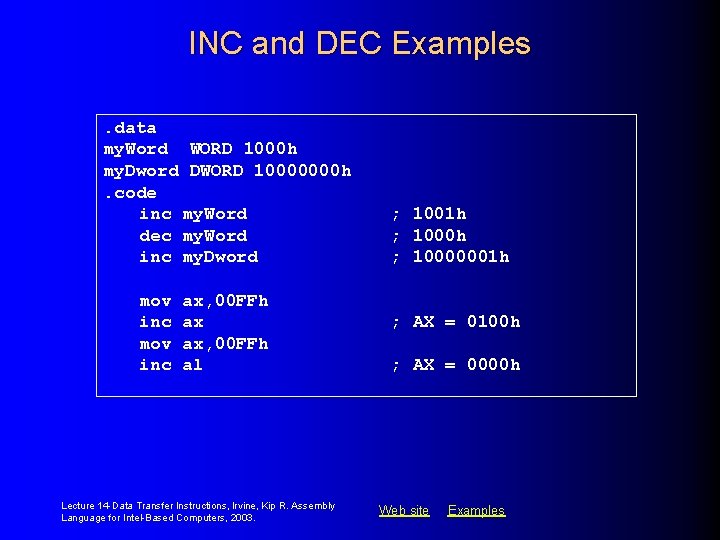

INC and DEC Examples. data my. Word WORD 1000 h my. Dword DWORD 10000000 h. code inc my. Word dec my. Word inc my. Dword mov inc ax, 00 FFh ax ax, 00 FFh al Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. ; 1001 h ; 10000001 h ; AX = 0100 h ; AX = 0000 h Web site Examples

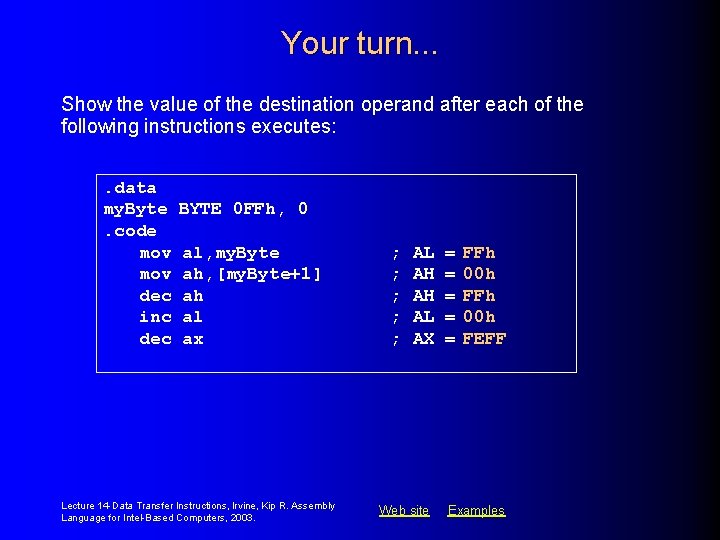

Your turn. . . Show the value of the destination operand after each of the following instructions executes: . data my. Byte. code mov dec inc dec BYTE 0 FFh, 0 al, my. Byte ah, [my. Byte+1] ah al ax Lecture 14 -Data Transfer Instructions, Irvine, Kip R. Assembly Language for Intel-Based Computers, 2003. ; ; ; AL AH AH AL AX Web site = = = FFh 00 h FEFF Examples

- Slides: 20