ARQUITECTURA DE COMPUTADORAS UNIDAD CENTRAL DE PROCESO Prof

- Slides: 44

ARQUITECTURA DE COMPUTADORAS UNIDAD CENTRAL DE PROCESO Prof. Juan Álvarez

CONTENIDO • Aritmética de punto Flotante. • Arquitectura del microprocesador (CPU) genérico. Evolución. Registros de propósito general y específicos. • Unidad de control, fases de ejecución de una instrucción, requisitos funcionales y señales de control. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 3)

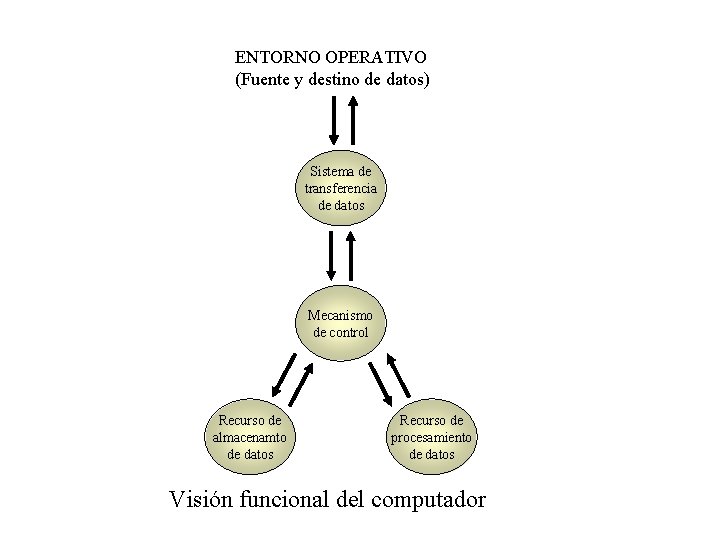

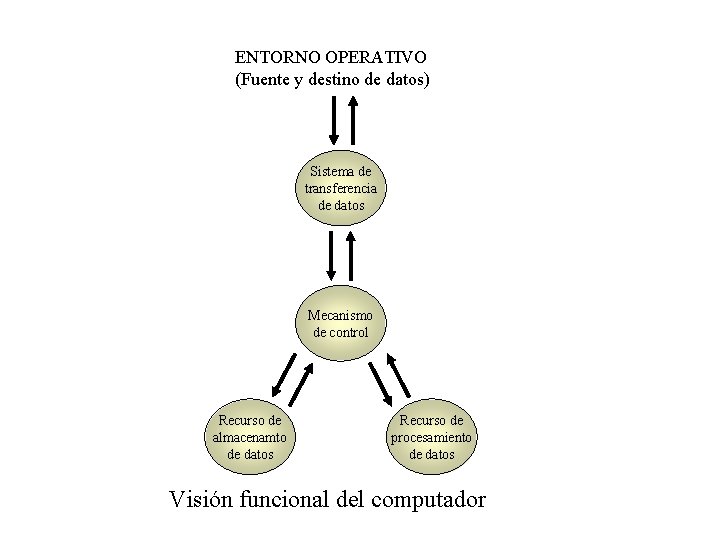

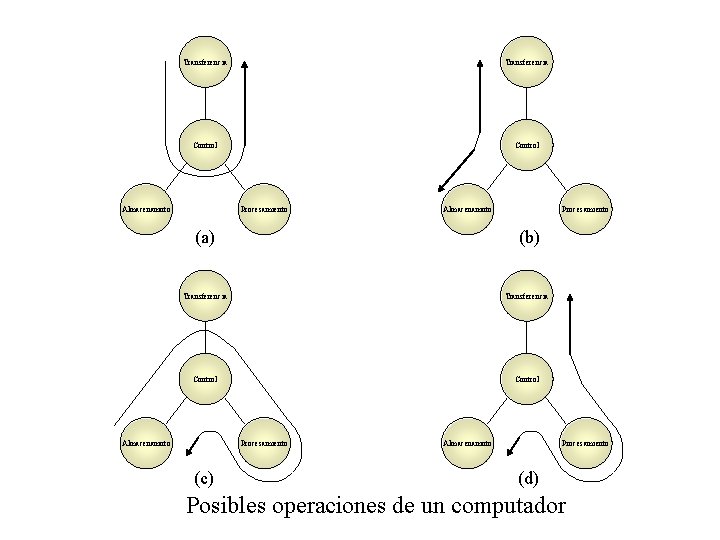

DESCRIPCIÓN FUNCIONAL DE LA CPU Las funciones básicas de un computador son: • Procesamiento de datos • Almacenamiento de datos • Transferencia de datos entre el computador y el mundo exterior • Control de las funciones anteriores En la siguiente figura se ilustran las relaciones que existen entre estas funciones. Obsérvese que el mecanismo de control actúa sobre las otras tres operaciones. La unidad de control gestiona los recursos y conduce las prestaciones de sus partes funcionales.

ENTORNO OPERATIVO (Fuente y destino de datos) Sistema de transferencia de datos Mecanismo de control Recurso de almacenamto de datos Recurso de procesamiento de datos Visión funcional del computador

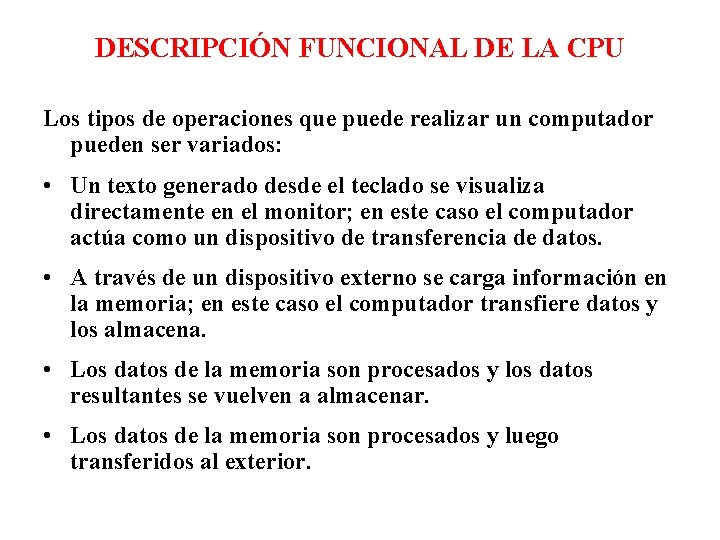

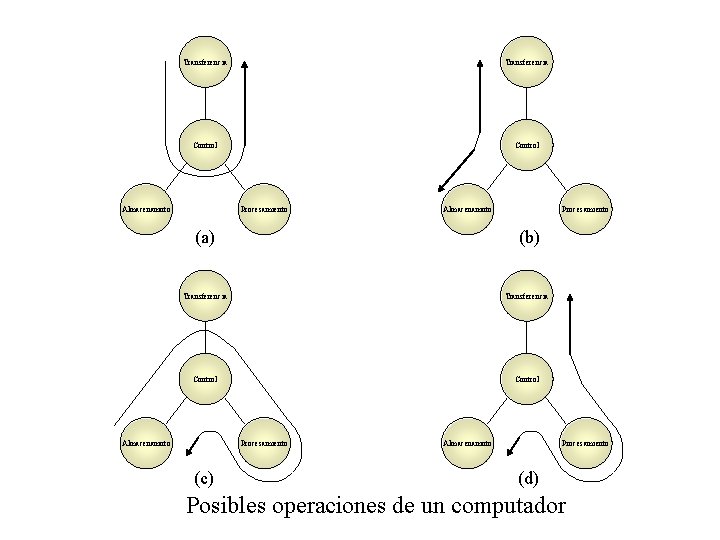

DESCRIPCIÓN FUNCIONAL DE LA CPU Los tipos de operaciones que puede realizar un computador pueden ser variados: • Un texto generado desde el teclado se visualiza directamente en el monitor; en este caso el computador actúa como un dispositivo de transferencia de datos. • A través de un dispositivo externo se carga información en la memoria; en este caso el computador transfiere datos y los almacena. • Los datos de la memoria son procesados y los datos resultantes se vuelven a almacenar. • Los datos de la memoria son procesados y luego transferidos al exterior.

Transferencia Control Almacenamnto Procesamiento (a) (b) Transferencia Control Almacenamnto Procesamiento (c) Almacenamnto Procesamiento (d) Posibles operaciones de un computador

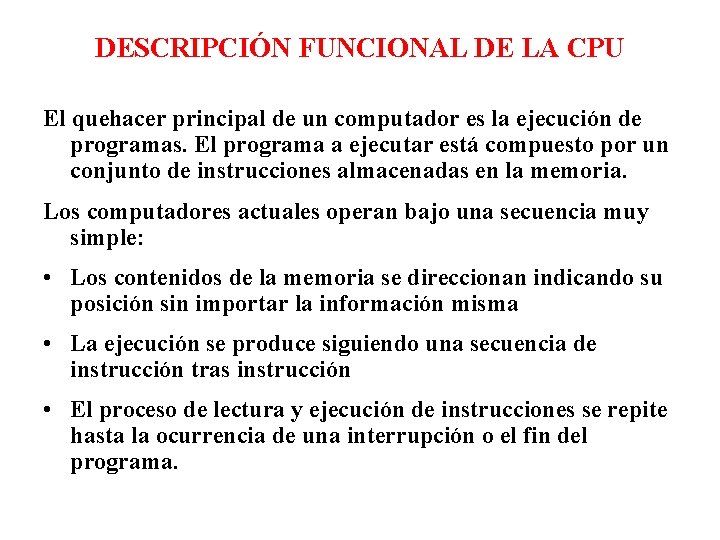

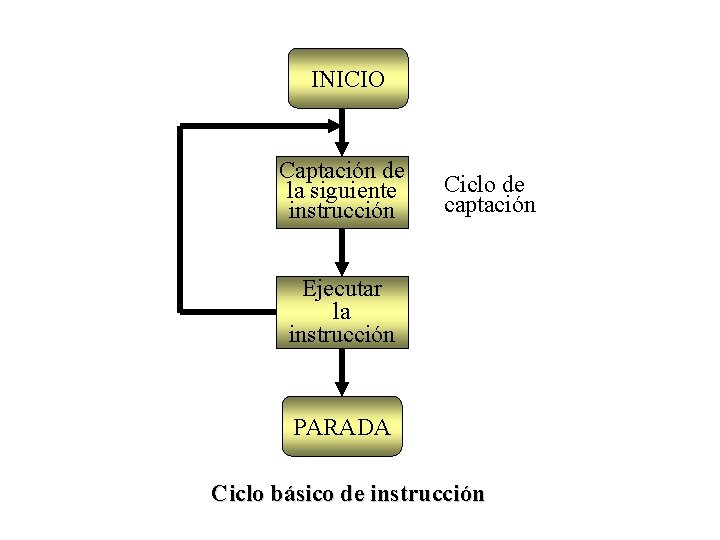

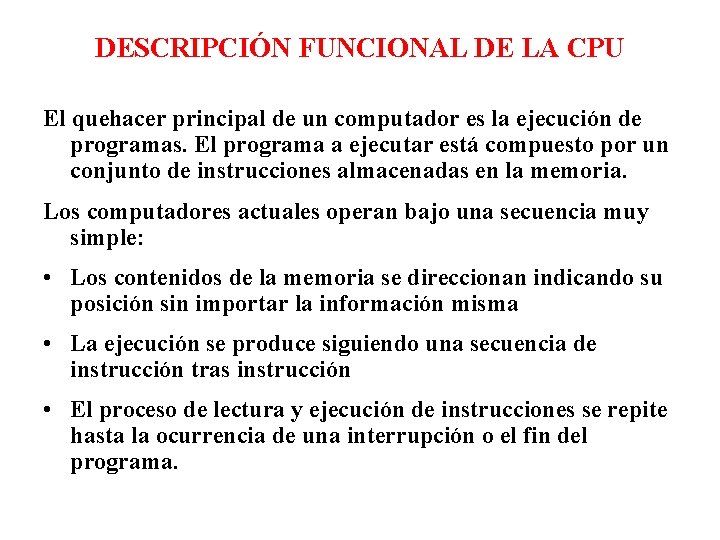

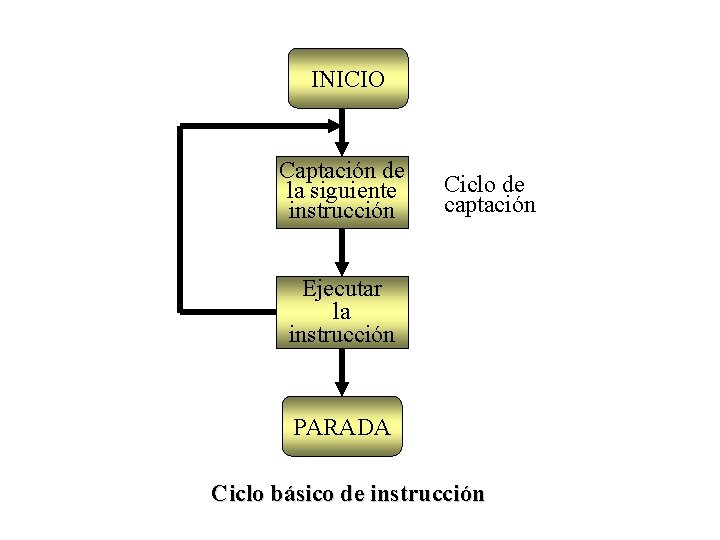

DESCRIPCIÓN FUNCIONAL DE LA CPU El quehacer principal de un computador es la ejecución de programas. El programa a ejecutar está compuesto por un conjunto de instrucciones almacenadas en la memoria. Los computadores actuales operan bajo una secuencia muy simple: • Los contenidos de la memoria se direccionan indicando su posición sin importar la información misma • La ejecución se produce siguiendo una secuencia de instrucción tras instrucción • El proceso de lectura y ejecución de instrucciones se repite hasta la ocurrencia de una interrupción o el fin del programa.

INICIO Captación de la siguiente instrucción Ciclo de captación Ejecutar la instrucción PARADA Ciclo básico de instrucción

ARQUITECTURA DE UNA CPU Una CPU realiza las siguientes funciones: • Leer instrucciones de la memoria • Decodificar instrucciones • Leer datos de la memoria o de los puertos de E/S • Procesar datos • Escribir datos en la memoria o en los puertos de E/S

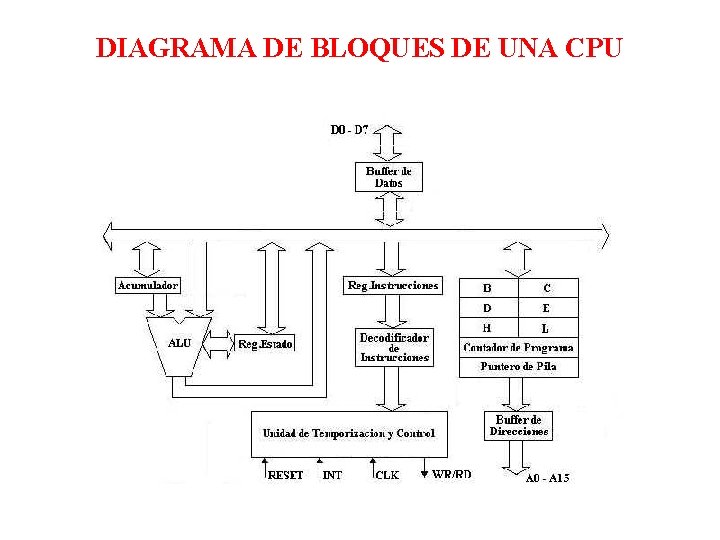

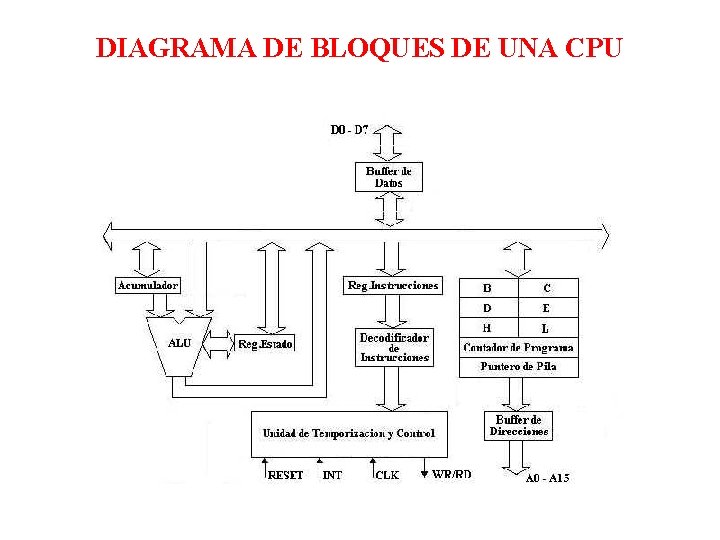

ARQUITECTURA DE UNA CPU Para ello, la CPU debe contar con un mínimo de elementos internos los cuales se observan en todos los computadores: • Una unidad de ejecución de instrucciones • Una unidad de lectura y decodificación de instrucciones • Una unidad de control • Registros de almacenamiento temporal de datos El diagrama siguiente muestra los bloques internos de un microprocesador que tiene 8 bits en el bus de datos y 16 bits en el bus de direcciones. En él se pueden enumerar elementos cuya función aparece en la mayoría de CPUs. En el grupo ejecutivo se distingue a la Unidad Aritmética y Lógica (ALU), el Acumulador y el Registro de Estado.

DIAGRAMA DE BLOQUES DE UNA CPU

ARQUITECTURA DE UNA CPU • La Unidad Aritmética y Lógica realiza las operaciones aritméticas, lógicas y de desplazamiento. Los resultados de las operaciones de la ALU suelen guardarse en el registro Acumulador, datos adicionales acerca de la misma operación se guardan en el Registro de Estado. • El Acumulador es un registro donde se guardan temporalmente datos y suele trabajar frecuentemente con la ALU. • El Registro de Estado, también llamado Registro de Banderas (Flag Register) o Registro de Señalizadores, guarda información adicional acerca de la última operación de la ALU. También suele guardar información del estado de operación de la CPU.

ARQUITECTURA DE UNA CPU En el grupo administrativo se observa al Registro de Instrucciones, al Decodificador de Instrucciones, a la Unidad de Temporización y Control. • En el Registro de Instrucciones se guarda el código de operación de la instrucción que se va a ejecutar. • El Decodificador de Instrucciones interpreta los códigos de operación de las instrucciones, determina la secuencia de micro-operaciones para ejecutar las instrucciones y establece la secuencia de micro-códigos para tal fin.

ARQUITECTURA DE UNA CPU • La Unidad de Temporización y Control recibe las señales del Decodificador de Instrucciones y se encarga de controlar la ejecución de las instrucciones. Esta unidad tiene conexión interna con todos los bloques de la CPU que le permite actuar sobre ellos para habilitar su participación en la ejecución secuencial de las microoperaciones. En particular, la CPU de la figura tiene también a su cargo la comunicación externa a través de las líneas de control.

ARQUITECTURA DE UNA CPU Toda CPU cuenta con un conjunto de Registros de uso general y de uso particular. • Los Registros de Uso General guardan temporalmente datos y suelen tener el mismo tamaño del bus de datos. • En los Registros de Uso Particular se encuentra el Contador de Programa y el Puntero de Pila: • El Contador de Programa (PC) contiene la posición de memoria a la que la CPU acude para leer la instrucción que se va a ejecutar. • El Puntero de Pila (SP = Stack Pointer) contiene la posición de memoria donde se almacenó el último dato introducido en la Pila.

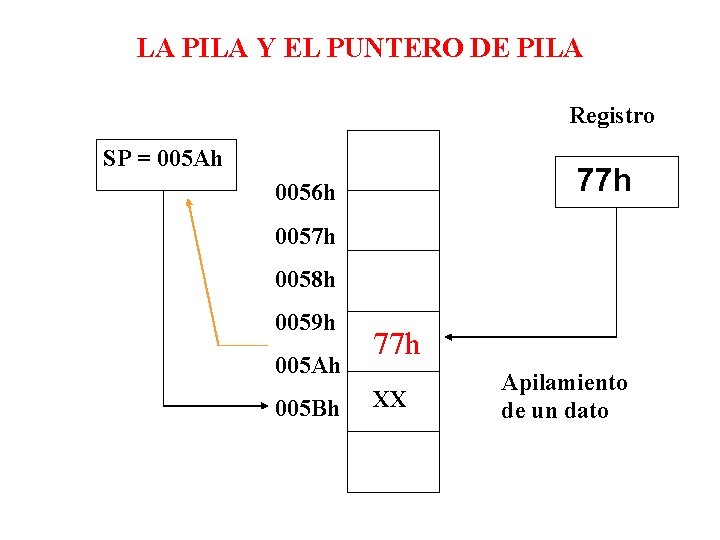

ARQUITECTURA DE UNA CPU • La Pila es una región de la memoria destinada a almacenar datos que previamente estuvieron en los registros de la CPU. Cuando un programa requiere guardar un dato en un registro, el dato precedente en el registro es borrado y se perdería si previamente no se toma la precaución de almacenarlo en la memoria. Este es el fin de la Pila. Su necesidad se justifica por el reducido número de registros en una CPU.

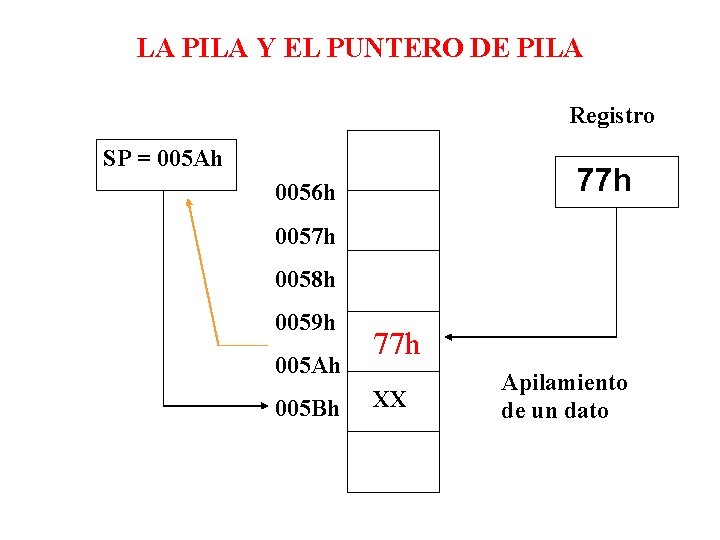

ARQUITECTURA DE UNA CPU La Pila tiene una forma peculiar de introducir los datos en la memoria: estos se apilan. Al igual que una pila de libros o de ladrillos, el nuevo dato se coloca encima del dato anterior. Cuando se quiere sacar un dato de la Pila, siempre se saca el que está encima de todos. Se dice que se usa en la modalidad LIFO: Last In First Out Como el Puntero de Pila apunta siempre al último dato que se introdujo en la Pila, su valor se decrementa con un nuevo dato introducido. Cuando se saca un dato de la Pila, el valor del SP se incrementa.

LA PILA Y EL PUNTERO DE PILA Registro SP = 005 Ah 77 h 0056 h 0057 h 0058 h 0059 h 005 Ah 005 Bh 77 h XX Apilamiento de un dato

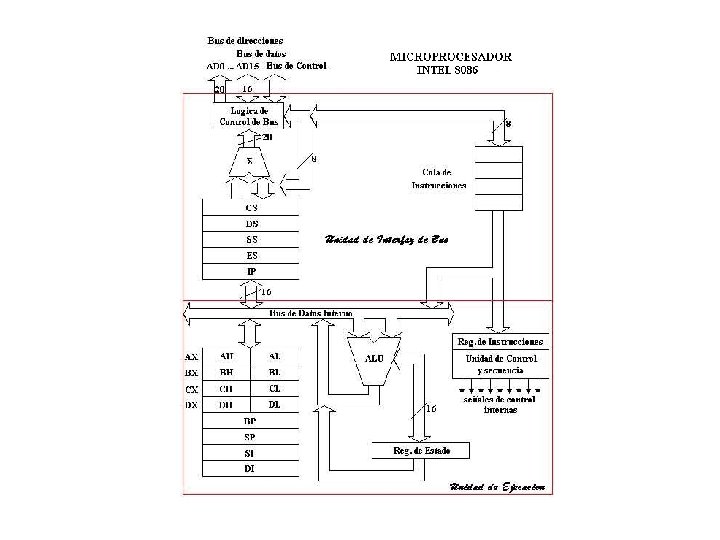

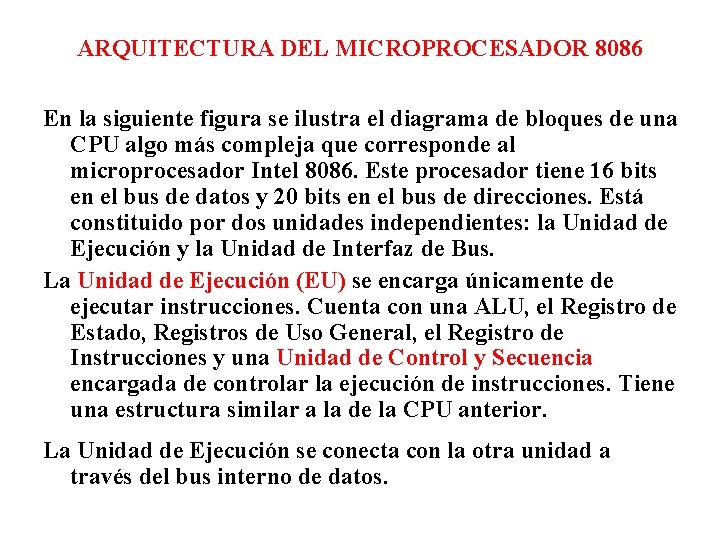

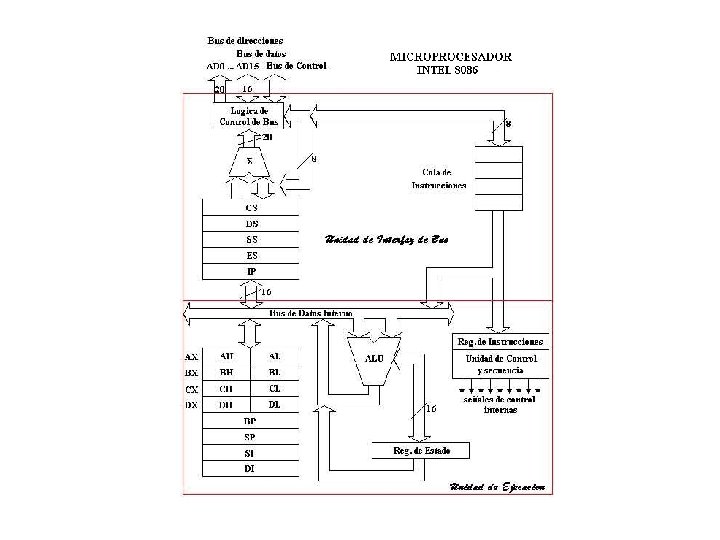

ARQUITECTURA DEL MICROPROCESADOR 8086 En la siguiente figura se ilustra el diagrama de bloques de una CPU algo más compleja que corresponde al microprocesador Intel 8086. Este procesador tiene 16 bits en el bus de datos y 20 bits en el bus de direcciones. Está constituido por dos unidades independientes: la Unidad de Ejecución y la Unidad de Interfaz de Bus. La Unidad de Ejecución (EU) se encarga únicamente de ejecutar instrucciones. Cuenta con una ALU, el Registro de Estado, Registros de Uso General, el Registro de Instrucciones y una Unidad de Control y Secuencia encargada de controlar la ejecución de instrucciones. Tiene una estructura similar a la de la CPU anterior. La Unidad de Ejecución se conecta con la otra unidad a través del bus interno de datos.

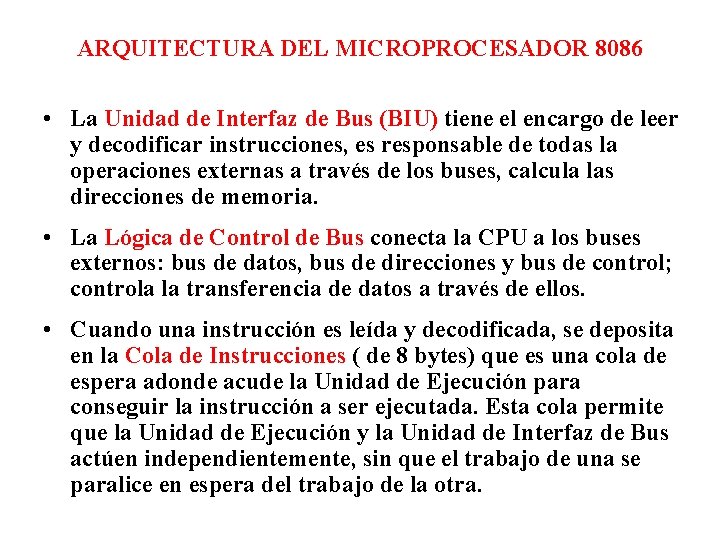

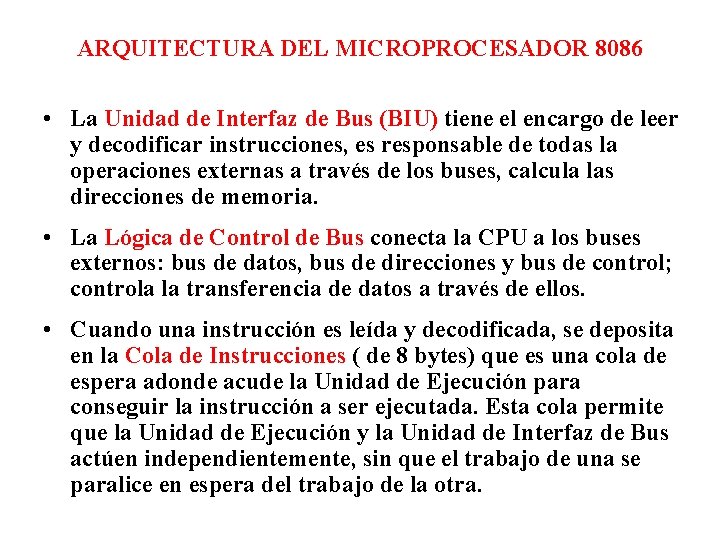

ARQUITECTURA DEL MICROPROCESADOR 8086 • La Unidad de Interfaz de Bus (BIU) tiene el encargo de leer y decodificar instrucciones, es responsable de todas la operaciones externas a través de los buses, calcula las direcciones de memoria. • La Lógica de Control de Bus conecta la CPU a los buses externos: bus de datos, bus de direcciones y bus de control; controla la transferencia de datos a través de ellos. • Cuando una instrucción es leída y decodificada, se deposita en la Cola de Instrucciones ( de 8 bytes) que es una cola de espera adonde acude la Unidad de Ejecución para conseguir la instrucción a ser ejecutada. Esta cola permite que la Unidad de Ejecución y la Unidad de Interfaz de Bus actúen independientemente, sin que el trabajo de una se paralice en espera del trabajo de la otra.

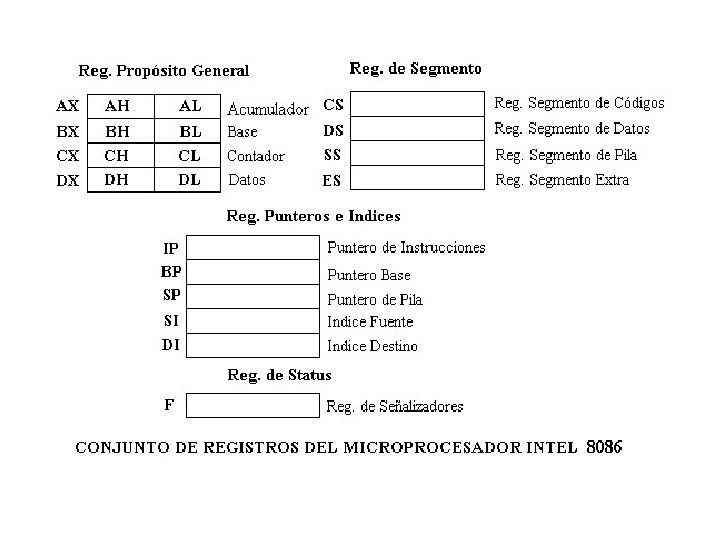

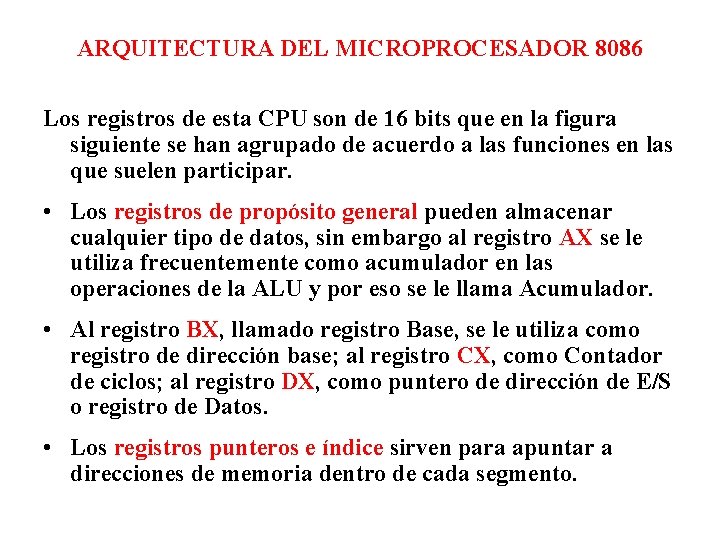

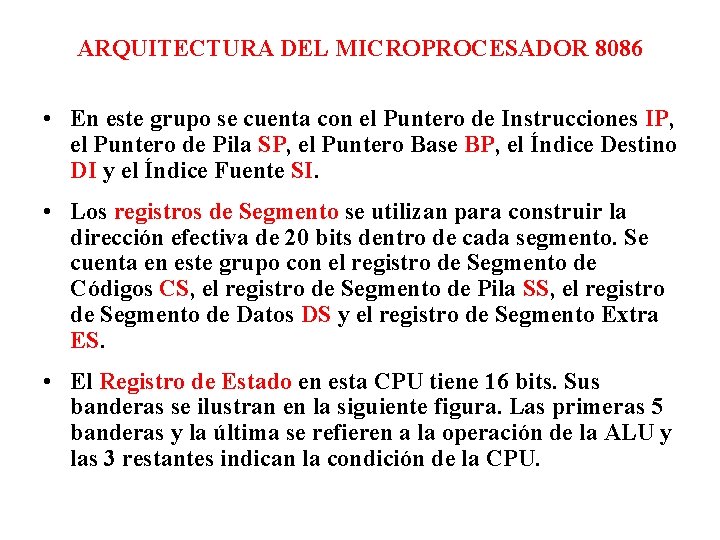

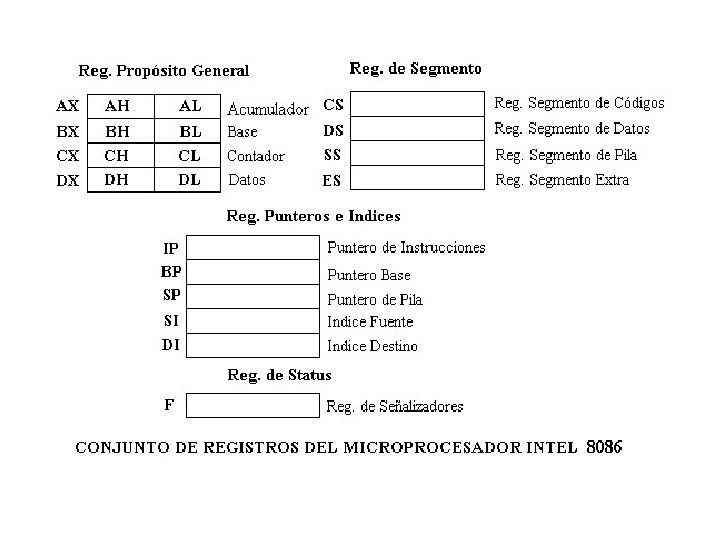

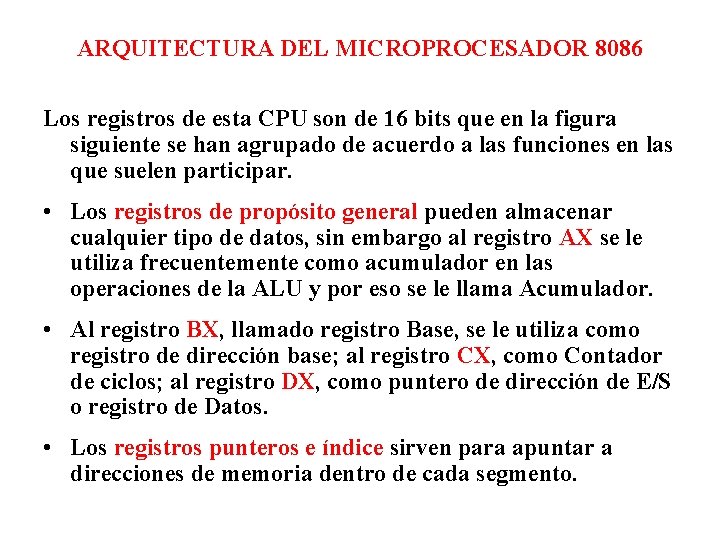

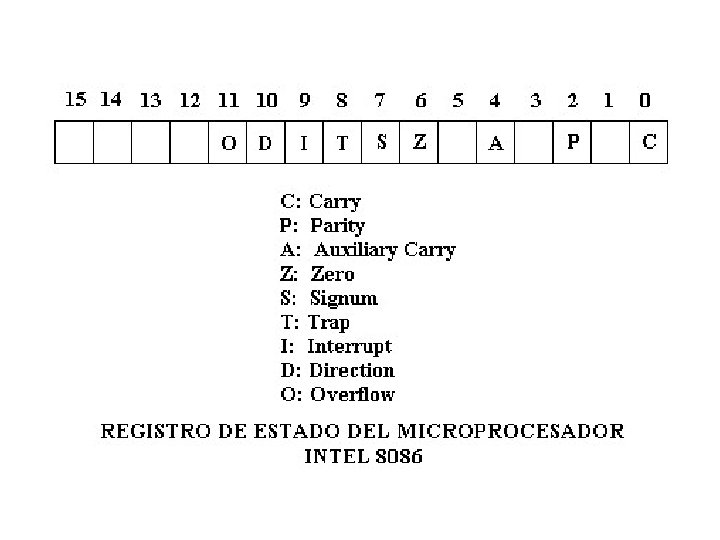

ARQUITECTURA DEL MICROPROCESADOR 8086 Los registros de esta CPU son de 16 bits que en la figura siguiente se han agrupado de acuerdo a las funciones en las que suelen participar. • Los registros de propósito general pueden almacenar cualquier tipo de datos, sin embargo al registro AX se le utiliza frecuentemente como acumulador en las operaciones de la ALU y por eso se le llama Acumulador. • Al registro BX, llamado registro Base, se le utiliza como registro de dirección base; al registro CX, como Contador de ciclos; al registro DX, como puntero de dirección de E/S o registro de Datos. • Los registros punteros e índice sirven para apuntar a direcciones de memoria dentro de cada segmento.

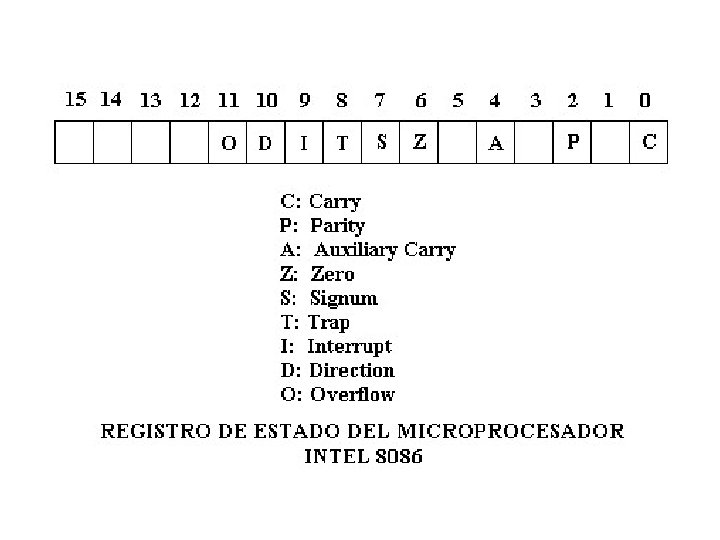

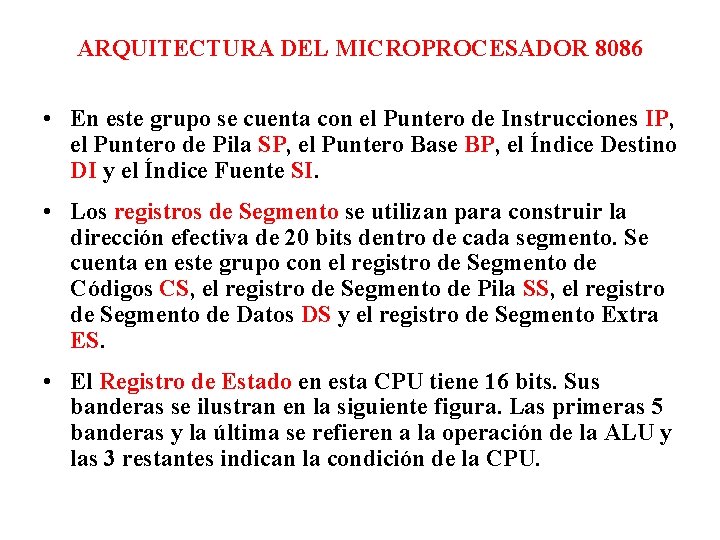

ARQUITECTURA DEL MICROPROCESADOR 8086 • En este grupo se cuenta con el Puntero de Instrucciones IP, el Puntero de Pila SP, el Puntero Base BP, el Índice Destino DI y el Índice Fuente SI. • Los registros de Segmento se utilizan para construir la dirección efectiva de 20 bits dentro de cada segmento. Se cuenta en este grupo con el registro de Segmento de Códigos CS, el registro de Segmento de Pila SS, el registro de Segmento de Datos DS y el registro de Segmento Extra ES. • El Registro de Estado en esta CPU tiene 16 bits. Sus banderas se ilustran en la siguiente figura. Las primeras 5 banderas y la última se refieren a la operación de la ALU y las 3 restantes indican la condición de la CPU.

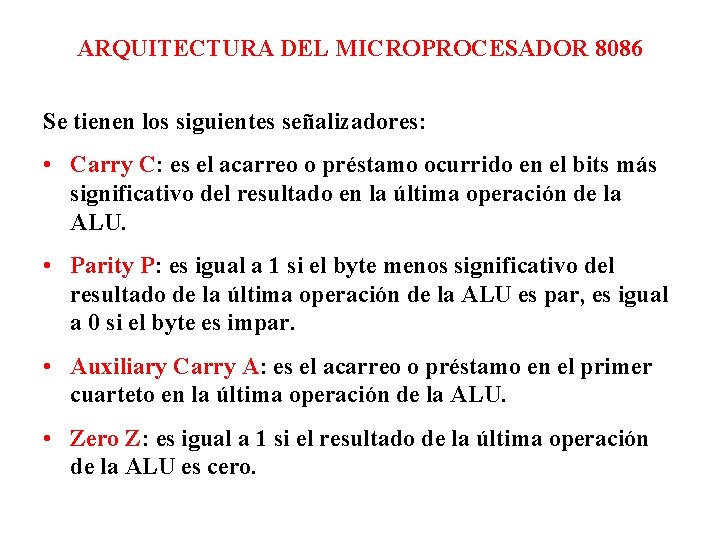

ARQUITECTURA DEL MICROPROCESADOR 8086 Se tienen los siguientes señalizadores: • Carry C: es el acarreo o préstamo ocurrido en el bits más significativo del resultado en la última operación de la ALU. • Parity P: es igual a 1 si el byte menos significativo del resultado de la última operación de la ALU es par, es igual a 0 si el byte es impar. • Auxiliary Carry A: es el acarreo o préstamo en el primer cuarteto en la última operación de la ALU. • Zero Z: es igual a 1 si el resultado de la última operación de la ALU es cero.

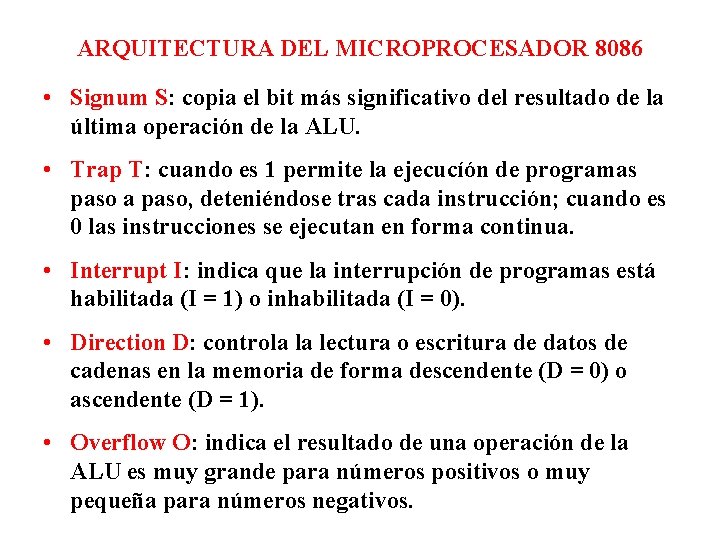

ARQUITECTURA DEL MICROPROCESADOR 8086 • Signum S: copia el bit más significativo del resultado de la última operación de la ALU. • Trap T: cuando es 1 permite la ejecucíón de programas paso a paso, deteniéndose tras cada instrucción; cuando es 0 las instrucciones se ejecutan en forma continua. • Interrupt I: indica que la interrupción de programas está habilitada (I = 1) o inhabilitada (I = 0). • Direction D: controla la lectura o escritura de datos de cadenas en la memoria de forma descendente (D = 0) o ascendente (D = 1). • Overflow O: indica el resultado de una operación de la ALU es muy grande para números positivos o muy pequeña para números negativos.

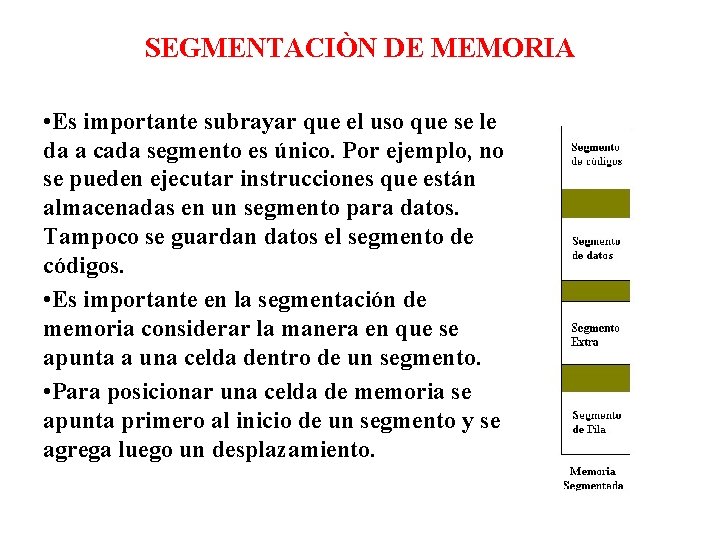

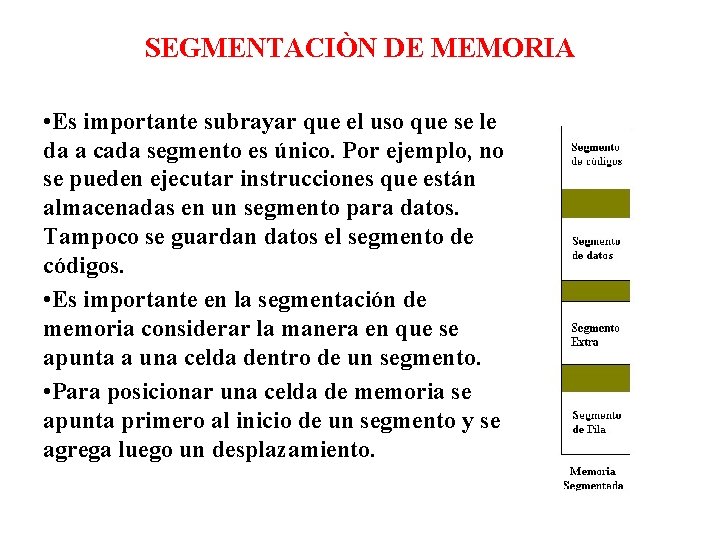

SEGMENTACIÒN DE MEMORIA • La memoria segmentada está formada por cuatro espacios de memoria perfectamente definidos para usos específicos. Cada segmento ocupa un espacio no mayor de 64 KB. Se distinguen: • El segmento de códigos donde sólo se almacenan programas. • El segmento de datos permite almacenar datos en general. • El segmento extra se destina para almacenar datos en general y datos de cadena en particular. • El segmento de pila sirve para almacenar datos de pila, es decir datos que estuvieron previamente en registros internos y que se perderían al ser utilizados los registros, a menos que previamente se metan en la pila.

SEGMENTACIÒN DE MEMORIA • Es importante subrayar que el uso que se le da a cada segmento es único. Por ejemplo, no se pueden ejecutar instrucciones que están almacenadas en un segmento para datos. Tampoco se guardan datos el segmento de códigos. • Es importante en la segmentación de memoria considerar la manera en que se apunta a una celda dentro de un segmento. • Para posicionar una celda de memoria se apunta primero al inicio de un segmento y se agrega luego un desplazamiento.

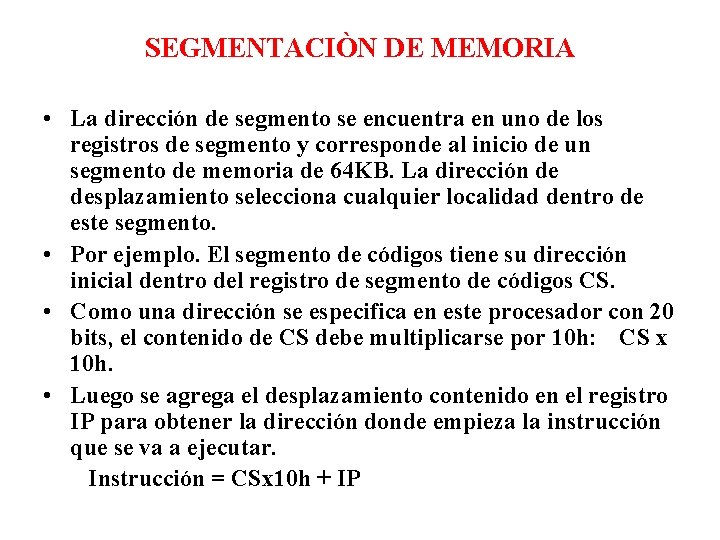

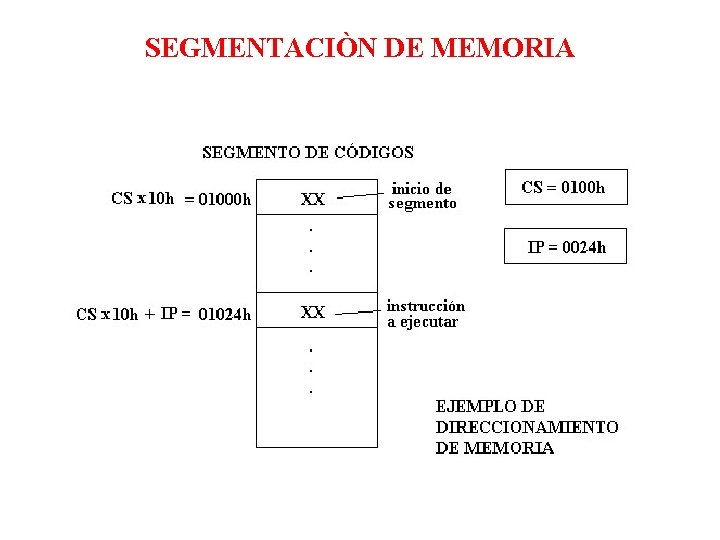

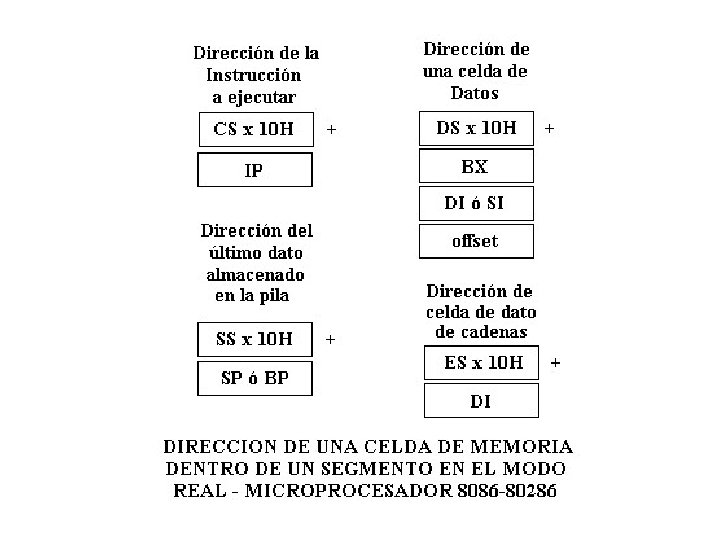

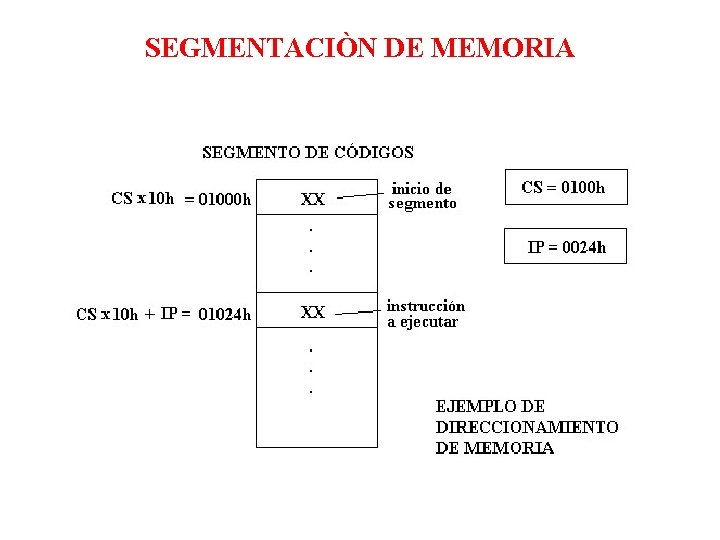

SEGMENTACIÒN DE MEMORIA • La dirección de segmento se encuentra en uno de los registros de segmento y corresponde al inicio de un segmento de memoria de 64 KB. La dirección de desplazamiento selecciona cualquier localidad dentro de este segmento. • Por ejemplo. El segmento de códigos tiene su dirección inicial dentro del registro de segmento de códigos CS. • Como una dirección se especifica en este procesador con 20 bits, el contenido de CS debe multiplicarse por 10 h: CS x 10 h. • Luego se agrega el desplazamiento contenido en el registro IP para obtener la dirección donde empieza la instrucción que se va a ejecutar. Instrucción = CSx 10 h + IP

SEGMENTACIÒN DE MEMORIA

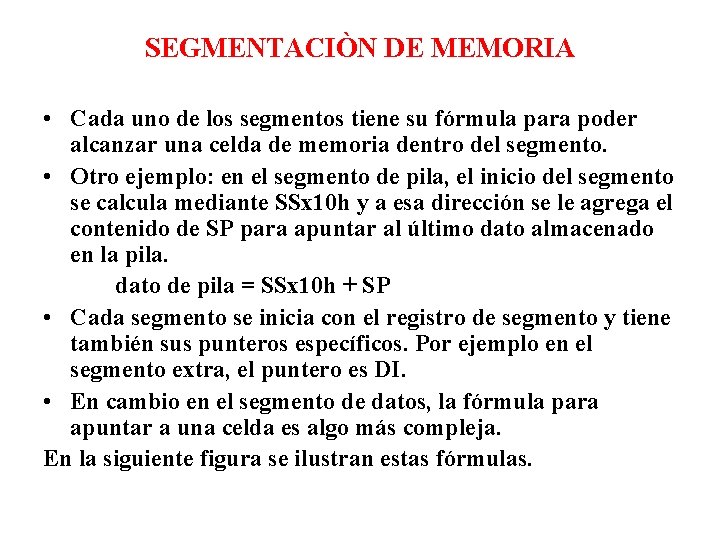

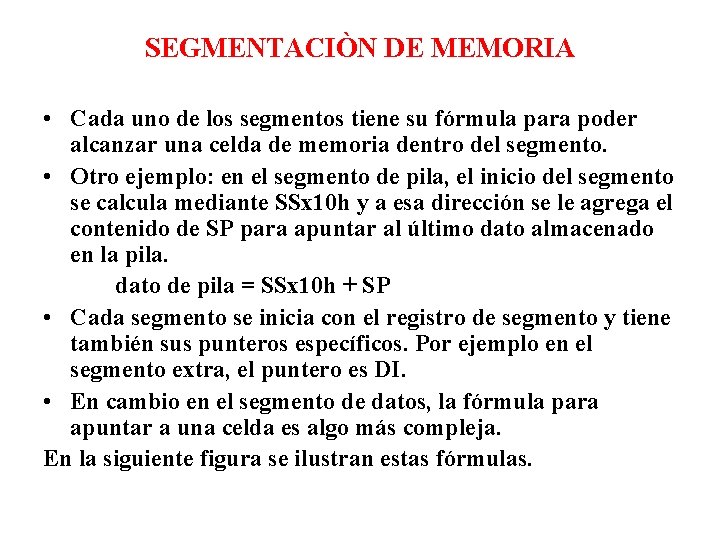

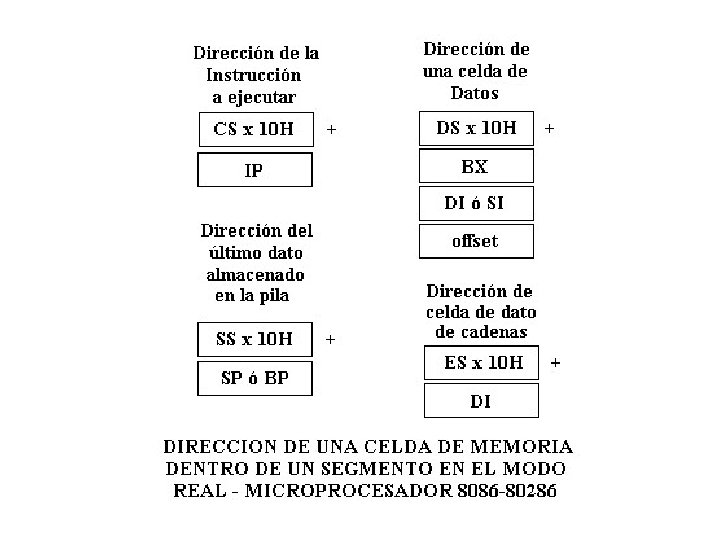

SEGMENTACIÒN DE MEMORIA • Cada uno de los segmentos tiene su fórmula para poder alcanzar una celda de memoria dentro del segmento. • Otro ejemplo: en el segmento de pila, el inicio del segmento se calcula mediante SSx 10 h y a esa dirección se le agrega el contenido de SP para apuntar al último dato almacenado en la pila. dato de pila = SSx 10 h + SP • Cada segmento se inicia con el registro de segmento y tiene también sus punteros específicos. Por ejemplo en el segmento extra, el puntero es DI. • En cambio en el segmento de datos, la fórmula para apuntar a una celda es algo más compleja. En la siguiente figura se ilustran estas fórmulas.

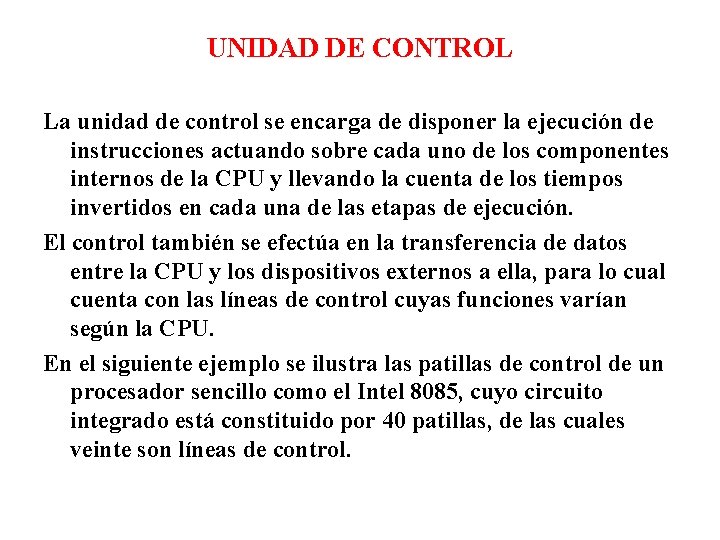

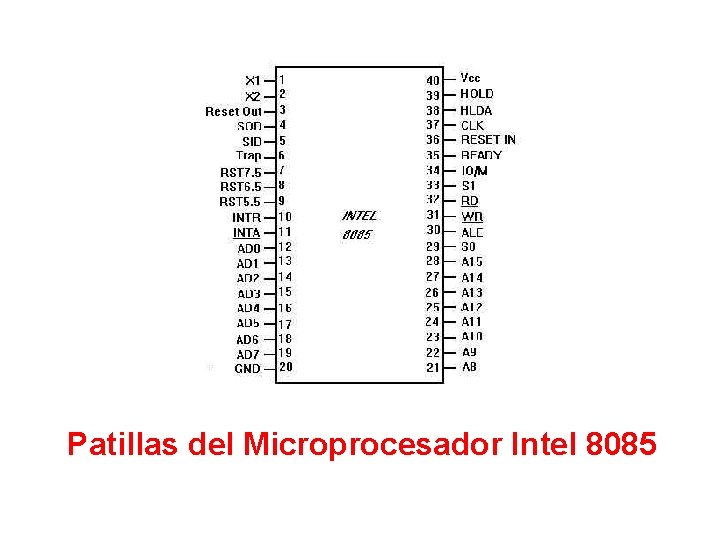

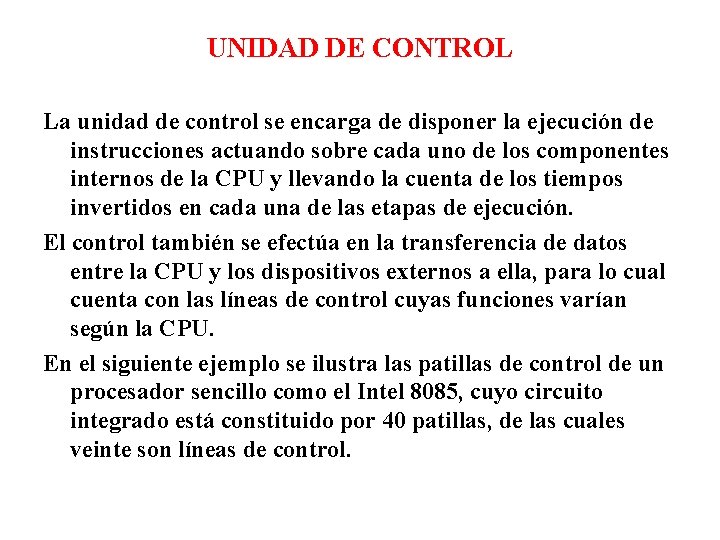

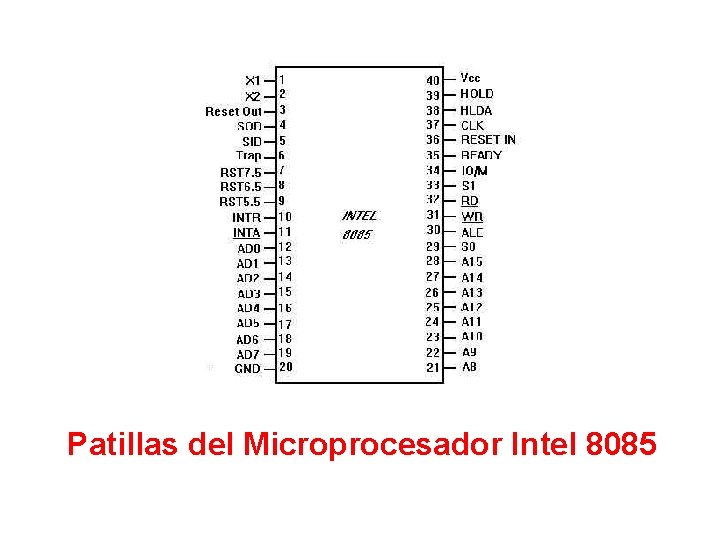

UNIDAD DE CONTROL La unidad de control se encarga de disponer la ejecución de instrucciones actuando sobre cada uno de los componentes internos de la CPU y llevando la cuenta de los tiempos invertidos en cada una de las etapas de ejecución. El control también se efectúa en la transferencia de datos entre la CPU y los dispositivos externos a ella, para lo cual cuenta con las líneas de control cuyas funciones varían según la CPU. En el siguiente ejemplo se ilustra las patillas de control de un procesador sencillo como el Intel 8085, cuyo circuito integrado está constituido por 40 patillas, de las cuales veinte son líneas de control.

Patillas del Microprocesador Intel 8085

MICROPROCESADORES DE 8 BITS • Las 8 patillas de datos se multiplexan con las 8 primeras patillas de direcciones, AD 0, AD 1, AD 2, …, AD 7, por la limitación impuesta por el número de patillas en el chip. • Vcc y GND corresponden a las patillas de alimentación, en tanto que en las patillas X 1 y X 2 se conecta el cristal de cuarzo para fijar la frecuencia de reloj. CLK es una salida de la señal de reloj. • Los 8 bits más significativos del bus de direcciones se encuentran en las patillas A 8, A 9, A 10, A 11, A 12, A 13, A 14 y A 15. • Las patillas INTR, Trap, RST 5. 5, RST 6. 5, RST 7. 5 e INTA, corresponden a los controles de interrupción para la comunicación con las interfaces E/S.

MICROPROCESADORES DE 8 BITS • RESET IN recibe la orden de reinicialización y RESET OUT permite avisar a los demás dispositivos del inicio de aquella orden. • SOD y SID son las patillas para salida e ingreso de datos seriales respectivamente. • HOLD, HLDA, READY y ALE son patillas para controlar el flujo de datos por los buses. • Las patillas S 0, S 1 e IO/M informan sobre el estado operativo del procesador. • Los controles RD y WR permiten avisar a los otros dispositivos de la intención de leer o de escribir datos ya sea en la memoria o en algún puerto.

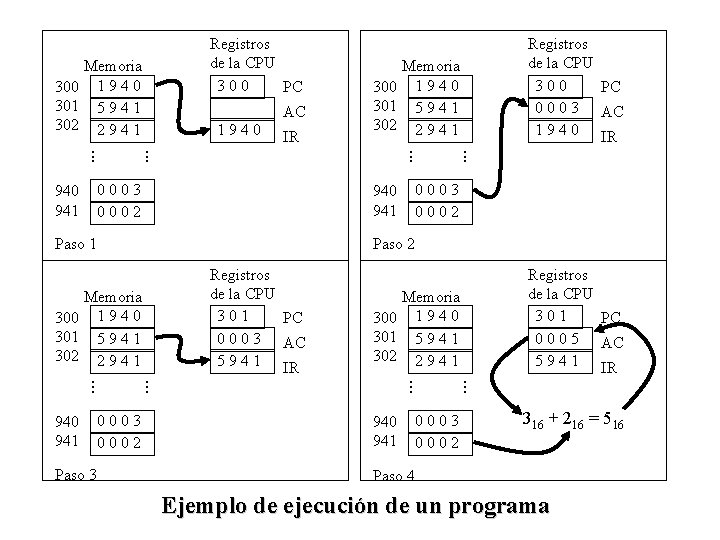

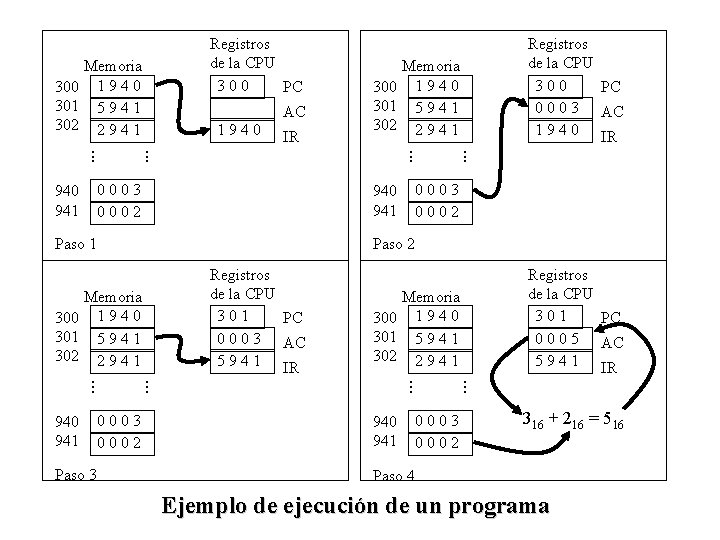

UNIDAD DE CONTROL El computador está diseñado para ejecutar instrucciones. Este proceso considera varias etapas: • La captación de una instrucción que consiste en direccionar la memoria y leer la instrucción de una posición específica. • La decodificación de la instrucción. • La ejecución de la instrucción que supone la realización de una secuencia de micro-operaciones. En el siguiente ejemplo se suma el contenido de la palabra de memoria en la dirección 0940 h con el contenido de la palabra de memoria en la dirección 0941 h y se almacena el resultado en esta ultima posición.

Memoria 300 1 9 4 0 301 5 9 4 1 302 2 9 4 1. . . 940 941 Registros de la CPU 300 PC 1940 AC IR 0003 0002 940 941 Paso 1 Memoria 300 1 9 4 0 301 5 9 4 1 302 2 9 4 1. . . 940 941 0003 0002 Paso 3 Memoria 300 1 9 4 0 301 5 9 4 1 302 2 9 4 1. . . Registros de la CPU 300 PC 0 0 0 3 AC 1 9 4 0 IR 0003 0002 Paso 2 Registros de la CPU 301 PC 0 0 0 3 AC 5 9 4 1 IR Memoria 300 1 9 4 0 301 5 9 4 1 302 2 9 4 1. . . 940 941 0003 0002 Registros de la CPU 301 PC 0 0 0 5 AC 5 9 4 1 IR 316 + 216 = 516 Paso 4 Ejemplo de ejecución de un programa

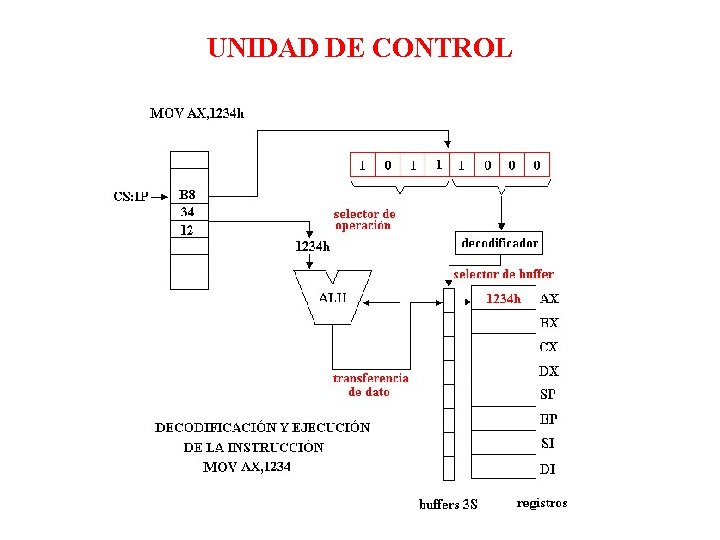

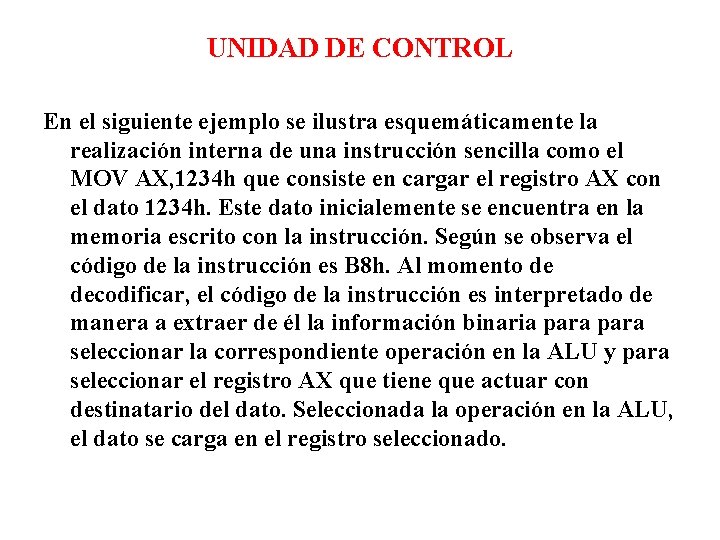

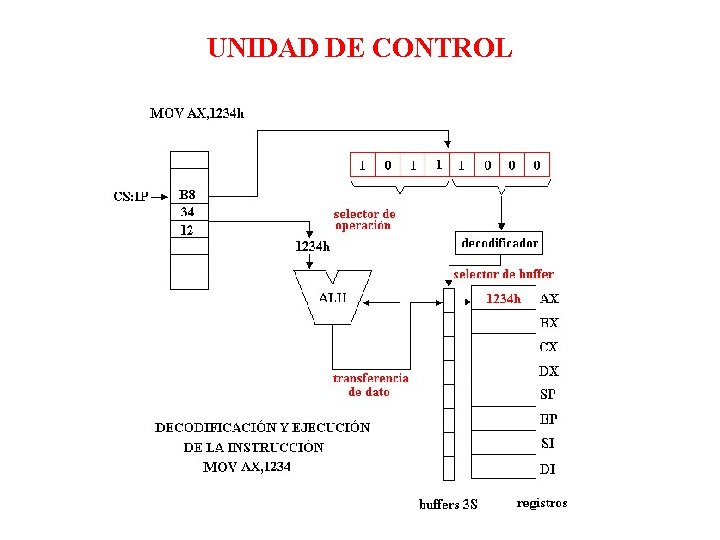

UNIDAD DE CONTROL En el siguiente ejemplo se ilustra esquemáticamente la realización interna de una instrucción sencilla como el MOV AX, 1234 h que consiste en cargar el registro AX con el dato 1234 h. Este dato inicialemente se encuentra en la memoria escrito con la instrucción. Según se observa el código de la instrucción es B 8 h. Al momento de decodificar, el código de la instrucción es interpretado de manera a extraer de él la información binaria para seleccionar la correspondiente operación en la ALU y para seleccionar el registro AX que tiene que actuar con destinatario del dato. Seleccionada la operación en la ALU, el dato se carga en el registro seleccionado.

UNIDAD DE CONTROL

PREGUNTAS PROPUESTAS 1. Describir los siguientes conceptos: 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. Registro de Estado Decodificador de instrucciones Puntero de Pila Memoria segmentada Unidad de interfaz de Bus Contador de Programa Unidad de Control de Bus Co-procesador Buffer de tres estados, indique como opera Fases de ejecución de una instrucción del procesador Intel. Interrupciones Unidad de Control y Secuencia

PREGUNTAS PROPUESTAS 2. Responder a las siguientes preguntas: 1. ¿Cuáles son los elementos básicos de la Unidad Central de Proceso? 2. ¿Cuáles son banderas que cambian con una operación de la ALU? 3. ¿Porqué la cola de instrucciones mejora el rendimiento del 8086? 4. ¿Cuál es la función de la Unidad de Control de Ejecución? 5. ¿Para qué sirve el puntero de instrucciones? 6. ¿Qué espacio de memoria se puede utilizar con el modo real?

PREGUNTAS PROPUESTAS 3. Responder a las siguientes preguntas: 1. 2. 3. 4. ¿Porqué es mejor el 8086 frente al 8085? ¿Cuál es la función de la Unidad de Control de Bus? ¿Cuáles son las funciones básicas de un computador? ¿Qué espacio de memoria se puede utilizar con un procesador de 20 bits en el bus de direcciones? 5. ¿Cuáles son los componentes básicos de una tarjeta madre? 6. ¿Cuáles son banderas que no cambian con una operación de la ALU? 7. ¿Cuál es la función de la Unidad de Temporización y Control?