ARQUITECTURA DE COMPUTADORAS SYLLABUS Prof Juan lvarez INFORMACIN

ARQUITECTURA DE COMPUTADORAS SYLLABUS Prof. Juan Álvarez

INFORMACIÓN GENERAL CURSO: ARQUITECTURA DE COMPUTADORES ÁREA: SISTEMAS DIGITALES, CONECTIVIDAD Y REDES NIVEL: CUARTO CARÁCTER: OBLIGATORIO CRÉDITOS: 3 HORAS: 2 T, 2 P

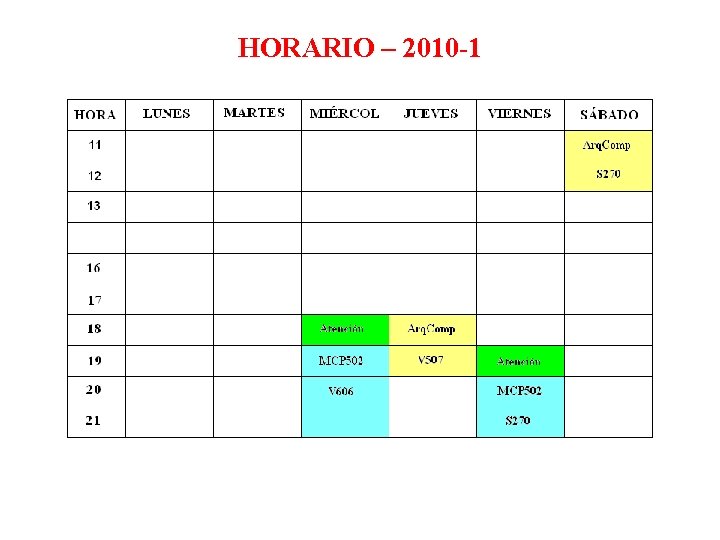

HORARIO – 2010 1

EL INGENIERO DE SISTEMAS El egresado de la carrera de Ingeniería de Sistemas es un profesional preparado para afrontar los retos y las exigencias del entorno de negocios actual y futuro, gracias a su capacidad de proponer, desarrollar, implementar y gestionar soluciones basadas en tecnologías de información que se integran a los procesos de negocio de las organizaciones, permitiéndoles alcanzar sus objetivos estratégicos de una manera oportuna, efectiva y eficiente.

EL INGENIERO DE SISTEMAS El Ingeniero de Sistemas está en condiciones de: • Comprender y analizar los procesos de negocio y su integración con otros procesos para mejorarlos aplicando tecnologías de información. • Conocer, evaluar y aplicar las tecnologías de información asegurando que éstas coadyuven a la formación de ventajas competitivas en los procesos de negocios. • Formular, evaluar, gestionar y desarrollar proyectos de innovación que utilicen en forma intensiva las tecnologías de información para incrementar el valor de los procesos de negocio.

EL INGENIERO DE SISTEMAS • Liderar proyectos de tecnología de información bajo un enfoque basado en equipos. • Emprender proactivamente la generación de nuevos negocios y mejoras de los existentes. • Tener una actitud crítica y de investigación frente a las situaciones problemáticas de negocios para generar soluciones factibles y deseables utilizando tecnologías de información.

EL INGENIERO DE SISTEMAS • Actuar con ética, honestidad y actitud de servicio, con un alto desempeño profesional que fortalezca el sistema organizacional. • Promover las buenas prácticas de la ingeniería de acuerdo a los requerimientos locales e internacionales de gestión de tecnologías de información y de responsabilidad social. • Ser proactivo en su desempeño profesional para alcanzar objetivos personales y organizacionales.

AREAS OCUPACIONALES • El Ingeniero de Sistemas graduado por la Universidad de Lima puede desempeñarse profesionalmente, tanto en entidades públicas como privadas, en las siguientes áreas: • Formulación, administración y ejecución de proyectos basados en las tecnologías de información. • Consultoría y/o asesoría aplicando tecnologías de información a los procesos de negocio. • Autogestión empresarial aplicando tecnologías de información. • Gestión de las áreas de tecnologías de información.

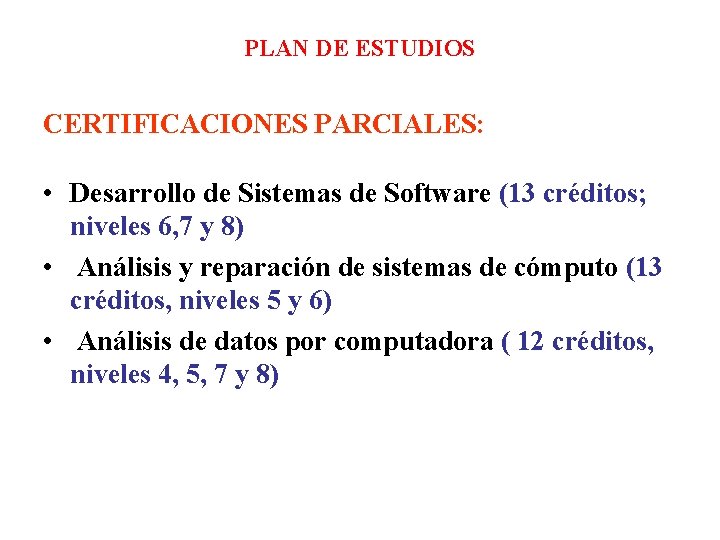

PLAN DE ESTUDIOS CERTIFICACIONES PARCIALES: • Desarrollo de Sistemas de Software (13 créditos; niveles 6, 7 y 8) • Análisis y reparación de sistemas de cómputo (13 créditos, niveles 5 y 6) • Análisis de datos por computadora ( 12 créditos, niveles 4, 5, 7 y 8)

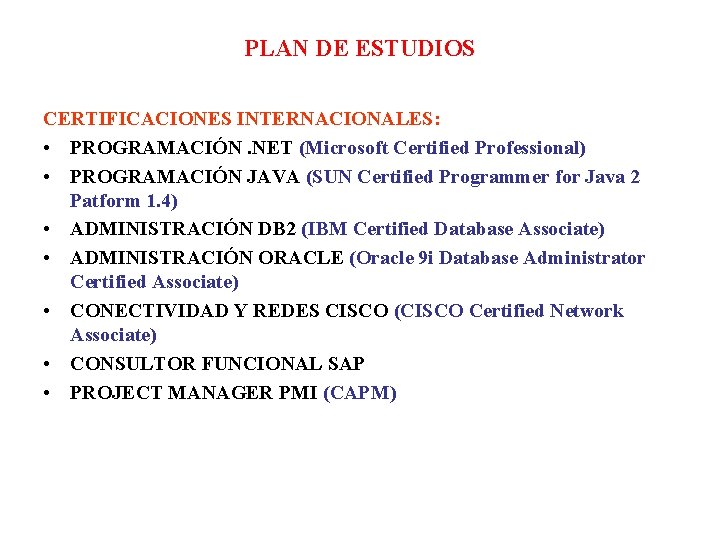

PLAN DE ESTUDIOS CERTIFICACIONES INTERNACIONALES: • PROGRAMACIÓN. NET (Microsoft Certified Professional) • PROGRAMACIÓN JAVA (SUN Certified Programmer for Java 2 Patform 1. 4) • ADMINISTRACIÓN DB 2 (IBM Certified Database Associate) • ADMINISTRACIÓN ORACLE (Oracle 9 i Database Administrator Certified Associate) • CONECTIVIDAD Y REDES CISCO (CISCO Certified Network Associate) • CONSULTOR FUNCIONAL SAP • PROJECT MANAGER PMI (CAPM)

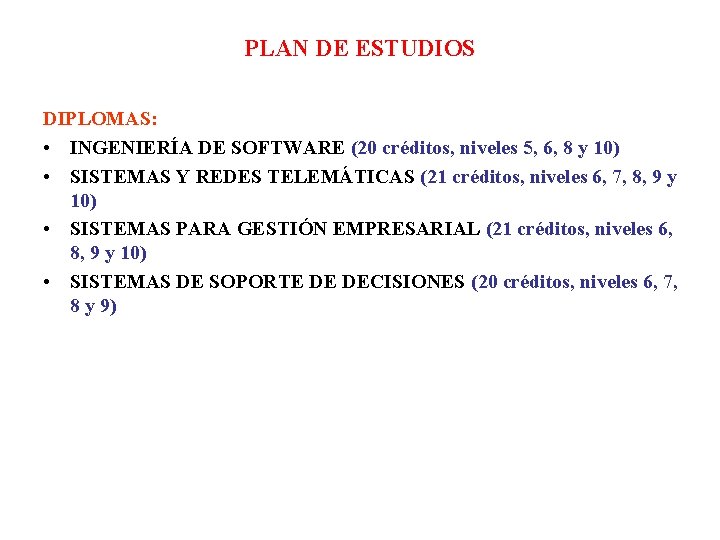

PLAN DE ESTUDIOS DIPLOMAS: • INGENIERÍA DE SOFTWARE (20 créditos, niveles 5, 6, 8 y 10) • SISTEMAS Y REDES TELEMÁTICAS (21 créditos, niveles 6, 7, 8, 9 y 10) • SISTEMAS PARA GESTIÓN EMPRESARIAL (21 créditos, niveles 6, 8, 9 y 10) • SISTEMAS DE SOPORTE DE DECISIONES (20 créditos, niveles 6, 7, 8 y 9)

PLAN DE ESTUDIOS

ARQUITECTURA DE COMPUTADORES SYLLABUS

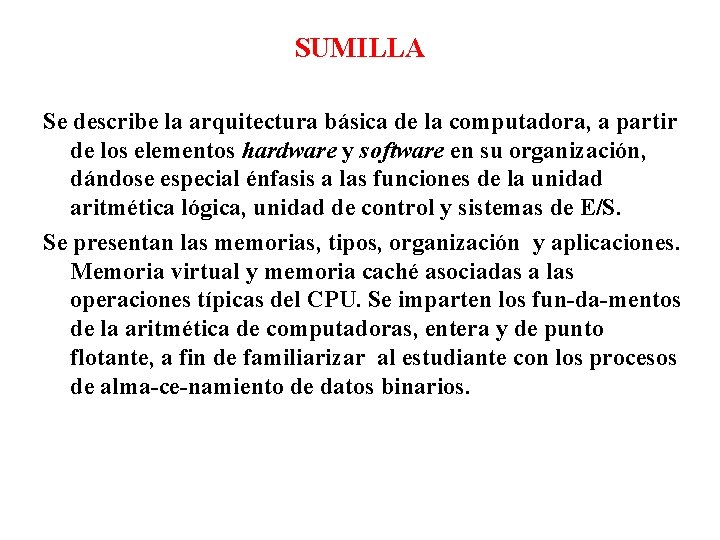

SUMILLA Se describe la arquitectura básica de la computadora, a partir de los elementos hardware y software en su organización, dándose especial énfasis a las funciones de la unidad aritmética lógica, unidad de control y sistemas de E/S. Se presentan las memorias, tipos, organización y aplicaciones. Memoria virtual y memoria caché asociadas a las operaciones típicas del CPU. Se imparten los fun da mentos de la aritmética de computadoras, entera y de punto flotante, a fin de familiarizar al estudiante con los procesos de alma ce namiento de datos binarios.

SUMILLA Se revisan las instrucciones básicas de un microprocesador genérico. Se estudian las diversas tecnologías de construcción de arquitecturas CISC, RISC, MIMD y SIMD, desde un punto de vista de análisis y comparación de desempeño. Se analizan los sistemas de cómputo considerando tres niveles de jerarquía: el nivel de lógica digital, el nivel de componentes y el nivel de sistema, a fin de utilizar los conceptos de rendimiento y costo como índices para la gestión de recursos informáticos.

OBJETIVOS Identificar los componentes de un computador digital, explicar su funcionamiento y los métodos para estimar su capacidad a partir del reconocimiento de las diversas arquitecturas. • Identificar y definir los niveles de organización de un computador • Identificar y comprender los principios de jerarquía de memoria • Analizar la operación del microprocesador con los otros componentes • Comprender las instrucciones de un microprocesador • Explicar el funcionamiento de las interfaces básicas de entrada/salida

CONTENIDO PRIMERA SEMANA Arquitectura y organización de computadoras. Conceptos generales. Evolución de las computadoras. El estado actual de la tecnología. Estructura de la Máquina de von Neumann. Unidad Central de Procesamiento (CPU), Memoria, Unidad de Interfaz de Entrada/Salida, Buses y Periféricos. Principios de operación. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78( Capítulo 2)

CONTENIDO SEGUNDA SEMANA Representación de tipos de datos. Aritmética computacional con enteros. Suma, resta, multiplicación y división de enteros. Estándar IEEE para aritmética punto flotante. Aritmética de punto flotante. Algoritmos de operaciones aritméticas. Laboratorio 1: Registros Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 8)

CONTENIDO TERCERA SEMANA Aritmética de punto Flotante. Arquitectura del microprocesador (CPU) genérico. Evolución. Registros de propósito general y específicos. Unidad de control, fases de ejecución de una instrucción, requisitos funcionales y señales de control. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 3)

CONTENIDO CUARTA SEMANA Transferencia de datos y microoperaciones. Unidad aritmética lógica (ALU). Diseño de una ALU. Laboratorio 2: Reconocimiento del Hardware de la Tarjeta madre. 1. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 8)

CONTENIDO QUINTA SEMANA Direccionamiento de la memoria en modo real. Segmento y desplazamiento. Modos de direccionamiento de datos. Direccionamiento de memoria de pila. Primera Práctica Brey, Barry. Los Microprocesadores Intel. 3 ra. Edición. Editorial Prentice Hall. 1995. Código de biblioteca: 004. 165/B 82 M (Capítulo 3)

CONTENIDO SEXTA SEMANA Debug. Descripción, uso y aplicaciones. Descripción de instrucciones del microprocesador genérico. Lenguaje de máquina y estructura del lenguaje ensamblador. Instrucciones: MOV, ADD, SUB, AND, OR, XOR, CMP. Laboratorio 3: Proceso de lectura y lectura de una memoria SRAM. Peter, Abel. Lenguaje Ensamblador y Programación para IBM PC Compatibles. 3 ra. Edición. Editorial Prentice Hall. Hispanoamericana. (Capítulo 3)

CONTENIDO SÉTIMA SEMANA Aplicaciones utilizando el Debug. Instrucciones: PUSH y POP. Memoria, características y jerarquía. Memorias semiconductoras. Tipos de memoria. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 4)

CONTENIDO NOVENA SEMANA Memoria caché. Tipos de memoria caché. Proceso de lectura/escritura en memoria SRAM. Arreglos de memorias. Laboratorio 4: Proceso de lectura en memorias ROM Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 4) Brey, Barry. Los Microprocesadores Intel. 3 ra. Edición. Editorial Prentice Hall. 1995. Código de biblioteca: 004. 165/B 82 M (Capítulo 10)

CONTENIDO DÉCIMA SEMANA Periféricos: Memoria externa o auxiliar. Discos magnéticos. Conjunto redundante de discos independientes (RAID). Memoria óptica. Cinta magnética La gestión de la memoria. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 5) Brey, Barry. Los Microprocesadores Intel. 3 ra. Edición. Editorial Prentice Hall. 1995. Código de biblioteca: 004. 165/B 82 M (Capítulo 10)

CONTENIDO DÉCIMO PRIMERA SEMANA Estructuras de interconexión en una computadora. Buffer de tres estados. Estructura del bus del sistema. Jerarquía de buses múltiples. Elementos de diseño de un bus. Buses estándares. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 6)

CONTENIDO DÉCIMO SEGUNDA SEMANA Interfaz de entrada salida. Transferencia síncrona y asíncrona de datos. Modos de transferencia: E/S programada, E/S por interrupción y acceso directo a memoria (DMA). Controlador DMA. Procesador de entrada – salida (IOP). Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 6)

CONTENIDO DÉCIMO TERCERA SEMANA Periféricos de una computadora. Dispositivos de entrada salida. Soporte del Sistema Operativo. Segunda Práctica. Buckel, Herbert. Ampliar y Reparar su PC. 4 ta. Edición. Editorial Alfaomega, 1999. Código biblioteca: 621. 3916/B 86 (Capítulo 9)

CONTENIDO DÉCIMO CUARTA SEMANA Medición del Rendimiento del Computador. Programas para evaluar el rendimiento. Computadoras de conjunto reducido de instrucciones (RISC). Arquitecturas RISC, y CISC. Laboratorio 5: Desmontaje y ensamblaje de PCs Buckel, Herbert. Ampliar y Reparar su PC. 4 ta. Edición. Editorial Alfaomega, 1999. Código biblioteca: 621. 3916/B 86 (Capítulo 2)

CONTENIDO DÉCIMO QUINTA SEMANA Arquitectura Paralela: Conceptos generales. Red de conexión: estrella, anillo, malla; red de conmutación. Tipos de arquitecturas paralelas: SISD, SIMD, MIMD memoria compartida, MIMD memoria distribuida. Laboratorio 6: Medición del rendimiento de una PC. Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 (Capítulo 16)

METODOLOGÍA El profesor desarrollará los temas de manera teórico – práctica propiciando que los alumnos empleen estos conocimientos en la solución de problemas y casos. Asimismo se desarrollaran experiencias de laboratorio con la participación activa de los alumnos y se brindará asesoría para el desarrollo de una monografía que profundiza el contenido de un tema del curso.

EVALUACIÓN La nota final será obtenida según el siguiente criterio: Examen parcial (30%) Examen final (40%) Tarea académica (30%) Comprende dos prácticas calificadas (50%), monografía y exposición final (25%) e informes de laboratorio (25%) Los contenidos de las prácticas y examen parcial no son cancelatorios. El alumno que tenga más del 20% de inasistencias está impedido de rendir examen final y examen complementario (Art. 39 Reglamento General de Estudios).

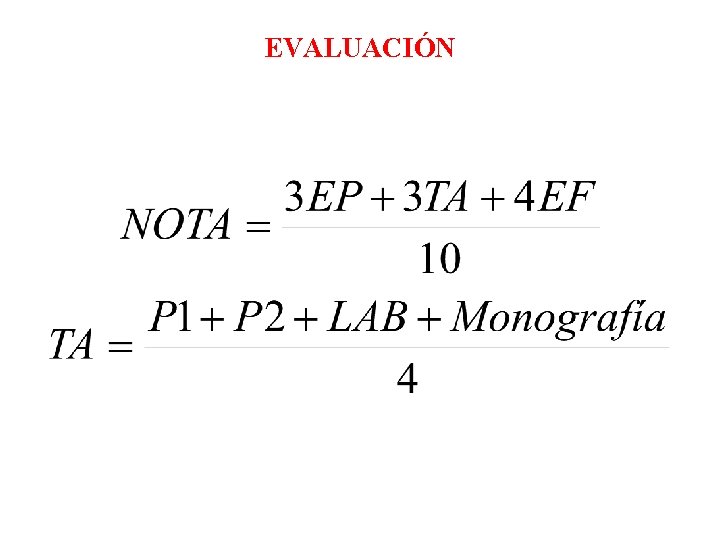

EVALUACIÓN

BIBLIOGRAFÍA • Stallings, William. Organización y Arquitectura de Computadores. 5 ta. Edición. Editorial Prentice Hall, 2000. Código biblioteca: 004. 22/S 78 • Patterson, David; Hennessy, Jhon. Organización y Diseño de Computadoras La Interfaz Hardware/Software. Mc Graw Hill. 1995. Cod. Biblioteca: 004/H 39 • Tanenbaum, Andrew. Organización de Computadores. Un Enfoque Estructurado. 3 ra. Edición. Prentice Hall 1992. Cod. Biblioteca: 044. 22/T 19/1992 • Mano, Morris, Arquitectura de Computadoras. 3 ra. Edición. Editorial Prentice Hall. 1994. Código biblioteca: 004. 22/M 226

BIBLIOGRAFÍA COMPLEMENTARIA • Mueller, Scott Manual de Actualización y Reparación de PCs. Prentice Hall. 1998. Código biblioteca: 621. 3916/M 86. • Brey, Barry. Los Microprocesadores Intel. 3 ra. Edición. Editorial Prentice Hall. 1995. Código de biblioteca: 004. 165/B 82 M • Angulo, José Ma. Estructura Del Computador. Paraninfo. 1996. Código Biblioteca: 004. 22/A 58 • Mano, Morris Ingeniería computacional Diseño del Hardware. Editoiral Prentice Hall. 1991. • Pedro De Miguel; José Ma. Angulo. Arquitectura de Computadores. Paraninfo 1987.

BIBLIOGRAFÍA COMPLEMENTARIA • Hennessy J Y Patterson D. Arquitectura de Computadoras. Un enfoque Cuantitativo. Mc. Graw Hill 1995. Cod. Biblioteca: 004. 22/H 39 • Long, Larry Y Long, Nancy. Introducción a las Computadoras y a los Sistemas de Información. Prentice Hall. 1999. Cod. Biblioteca: 004/L 82/1999. • www. pctechguide. com http: //arith. stanford. edu/

- Slides: 36