Useroriented Power Management for ManyCore Mobile Architectures Energy

User-oriented Power Management for Many-Core Mobile Architectures Energy Aware Computing - 18743 Nupur Kulkarni & Chandirasekarendiran Anandan

Outline: • Motivation • Problem • Proposed Solution • Milestones • References • Questions

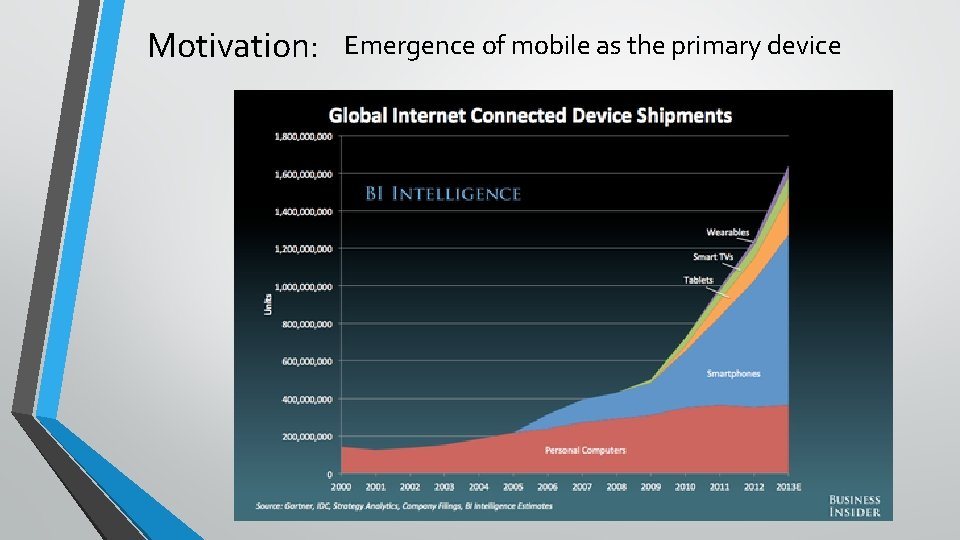

Motivation: Emergence of mobile as the primary device

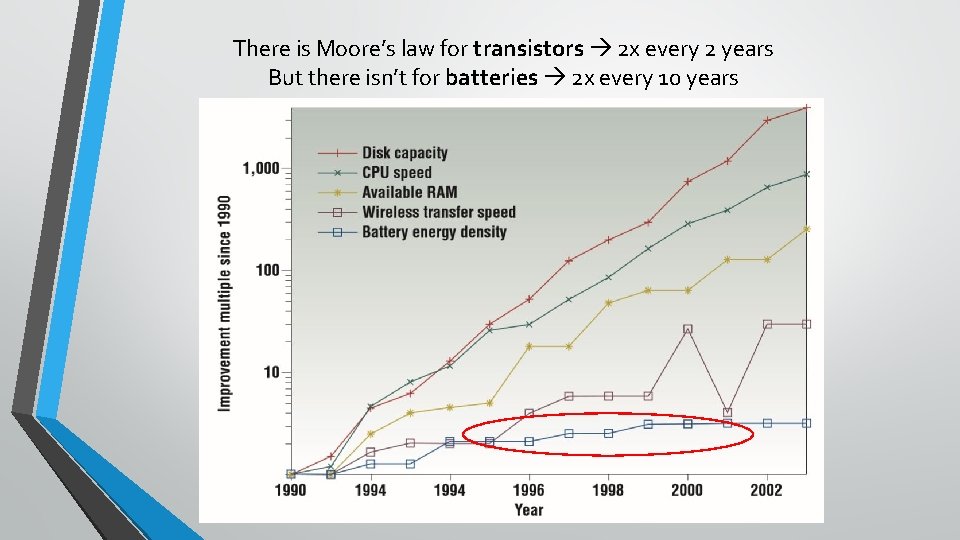

There is Moore’s law for transistors 2 x every 2 years But there isn’t for batteries 2 x every 10 years

Problem: • Dynamic voltage and frequency scaling (DVFS) is widely used to reduce active power, but its effectiveness and cost depends on the granularity at which it is applied. • Per-core DVFS allows the greatest flexibility in controlling power, but incurs the expense of an unrealistically large number of on-chip voltage regulators. • Per-chip DVFS, where all cores are controlled by a single regulator overcomes this problem at the expense of greatly reduced flexibility. • Therefore, we need an intermediate solution.

Proposed Solution: The solution is to propose a per-cluster scheme, where we cluster cores based on the instructions per cycle(IPC) of the applications which are scheduled on those cores at run-time. The following steps are executed to do the above: • Perform Greedy Algorithm [4] for application scheduling : Ranks applications based on IPC & ranks the cores according to inherent frequency (before DVFS) and then matches applications and cores by rank. • Cluster the cores based on applications with closer IPC.

Milestones: 1. Research related work and understand practical implementation of the proposed solution. 2. Familiarise with the simulation software Sniper. 3. Implement the proposed Greedy algorithm 4. Implement steepest drop algorithm. 5. Test on various workbenches and obtain results.

References: 1. Paradiso et al. , “Energy Scavenging for Mobile and Wireless Electronics”, Pervasive Computing, IEEE CS, 2005, pp. 18 -26 2. Khaled et al. , “Dynamic power management techniques in multi-core architectures : A survey study”, Ain Shams Engineering Journal, Elsevier, 2015 3. Kolpe Tejaswini, Zhai Antonia, Sapatnekar Sachin S, “Enabling improved power management in multicore processors through clustered DVFS”, Design, automation & test in Europe conference & exhibition (DATE), IEEE, 2011 4. Jonathan A. Winter et al. , “Scalable Thread Scheduling and Global Power Management for Heterogeneous Many-Core Architectures”, PACT, 2010

QUESTIONS ?

- Slides: 10