Universitt Dortmund Specifications P Marwedel Univ Dortmund Informatik

![Universität Dortmund Models of computation - Definition Models of computation define [Lee, UCB, 1999]: Universität Dortmund Models of computation - Definition Models of computation define [Lee, UCB, 1999]:](https://slidetodoc.com/presentation_image_h/14c59b32ffd50c4b645be134a8387bf8/image-7.jpg)

![Universität Dortmund General form of edge labels event [condition] / reaction Events: • Exist Universität Dortmund General form of edge labels event [condition] / reaction Events: • Exist](https://slidetodoc.com/presentation_image_h/14c59b32ffd50c4b645be134a8387bf8/image-23.jpg)

- Slides: 32

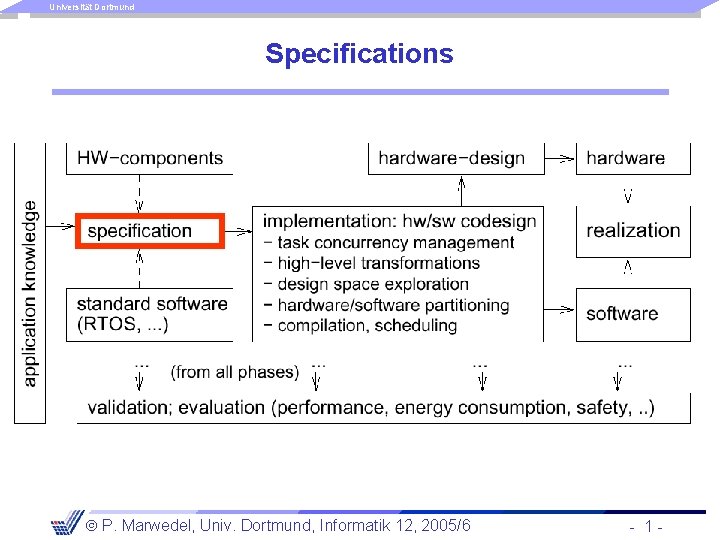

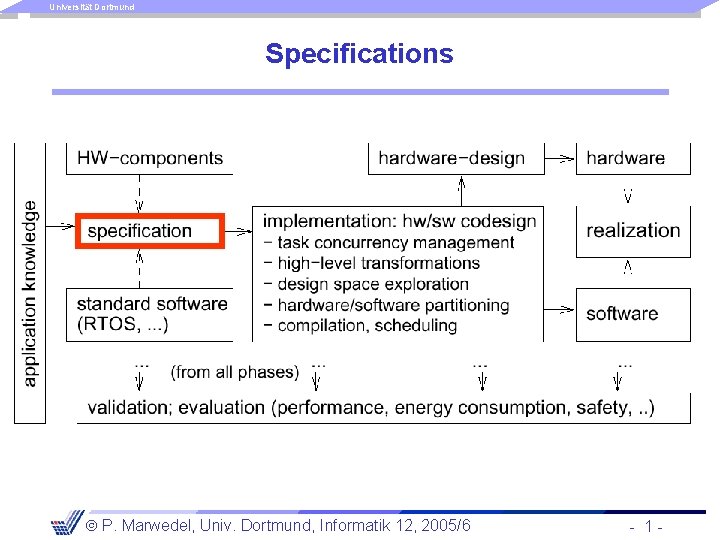

Universität Dortmund Specifications P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 1 -

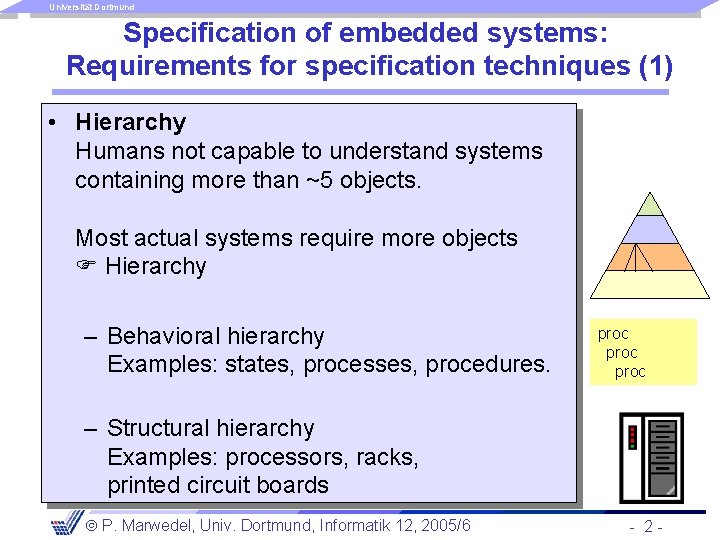

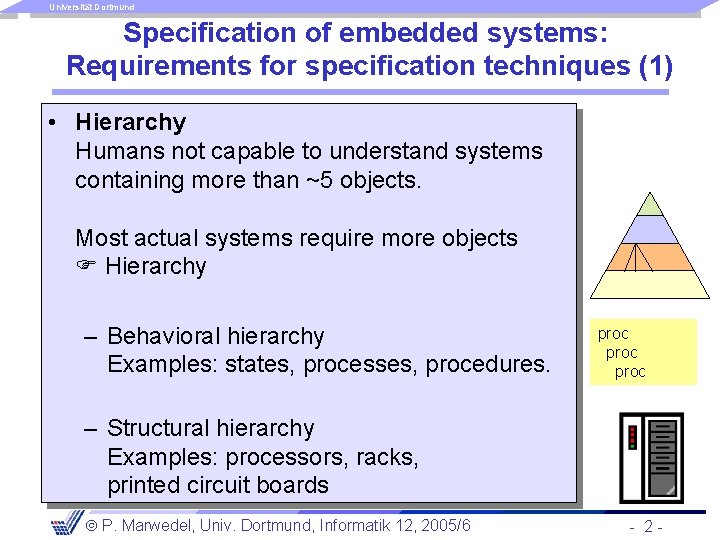

Universität Dortmund Specification of embedded systems: Requirements for specification techniques (1) • Hierarchy Humans not capable to understand systems containing more than ~5 objects. Most actual systems require more objects Hierarchy – Behavioral hierarchy Examples: states, processes, procedures. proc – Structural hierarchy Examples: processors, racks, printed circuit boards P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 2 -

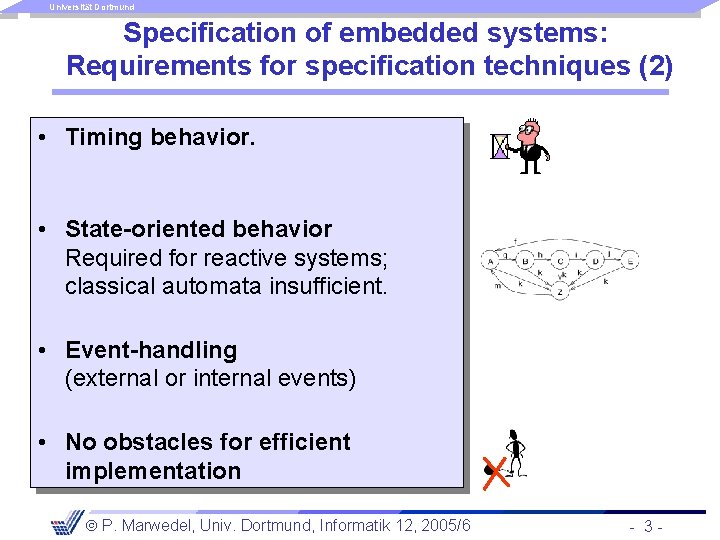

Universität Dortmund Specification of embedded systems: Requirements for specification techniques (2) • Timing behavior. • State-oriented behavior Required for reactive systems; classical automata insufficient. • Event-handling (external or internal events) • No obstacles for efficient implementation P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 3 -

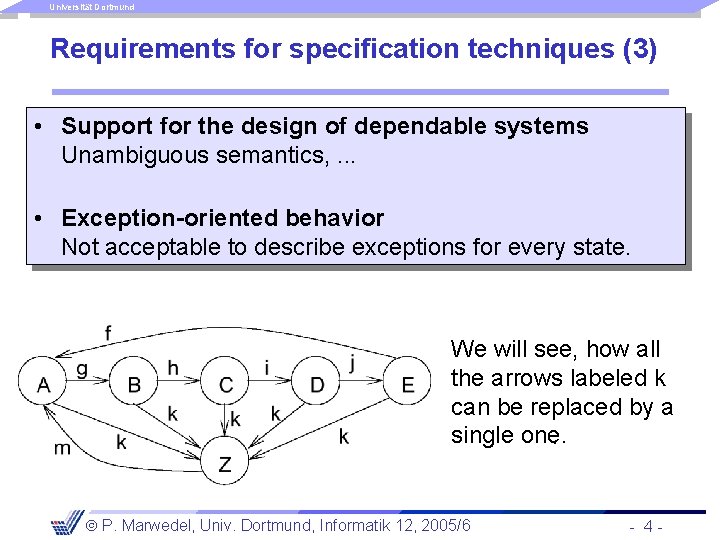

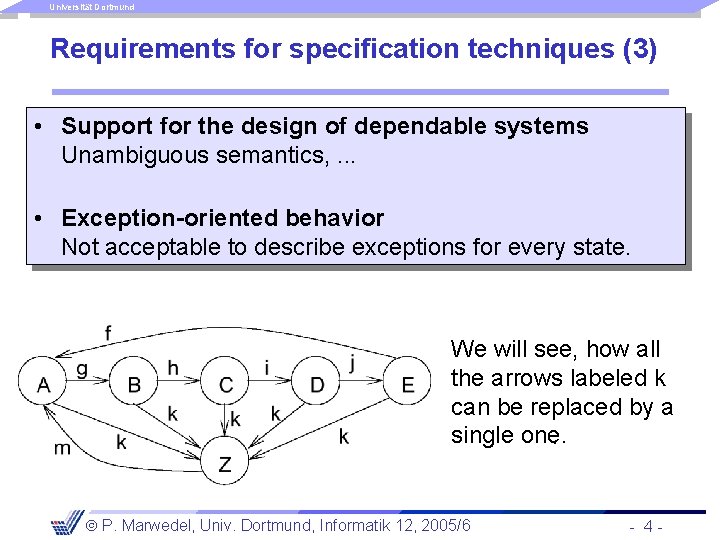

Universität Dortmund Requirements for specification techniques (3) • Support for the design of dependable systems Unambiguous semantics, . . . • Exception-oriented behavior Not acceptable to describe exceptions for every state. We will see, how all the arrows labeled k can be replaced by a single one. . P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 4 -

Universität Dortmund Requirements for specification techniques (4) • Concurrency Real-life systems are concurrent • Synchronization and communication Components have to communicate! • Presence of programming elements For example, arithmetic operations, loops, and function calls should be available • Executability (no algebraic specification) • Support for the design of large systems ( OO) • Domain-specific support P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 5 -

Universität Dortmund Requirements for specification techniques (5) • Readability • Portability and flexibility • Termination It should be clear, at which time all computations are completed • Support for non-standard I/O devices Direct access to switches, displays, . . . • Non-functional properties fault-tolerance, disposability, EMC-properties, weight, size, user friendliness, extendibility, expected life time, power consumption. . . • Adequate model of computation P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 6 -

![Universität Dortmund Models of computation Definition Models of computation define Lee UCB 1999 Universität Dortmund Models of computation - Definition Models of computation define [Lee, UCB, 1999]:](https://slidetodoc.com/presentation_image_h/14c59b32ffd50c4b645be134a8387bf8/image-7.jpg)

Universität Dortmund Models of computation - Definition Models of computation define [Lee, UCB, 1999]: • What it means to be a component: Subroutine? Process? Thread? • The mechanisms by which components interact: Message passing? Rendez-vous? • Possibly also: What components know about each other (global variables? Implicit behavior of other components) • Certainly not: vocabulary P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 7 -

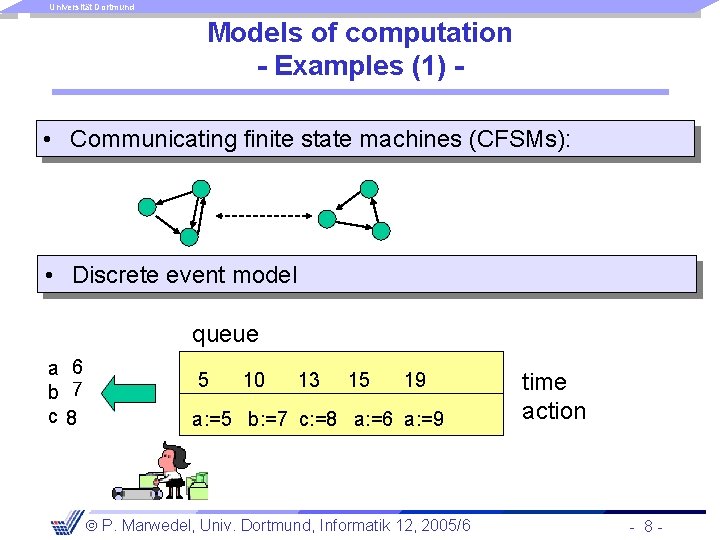

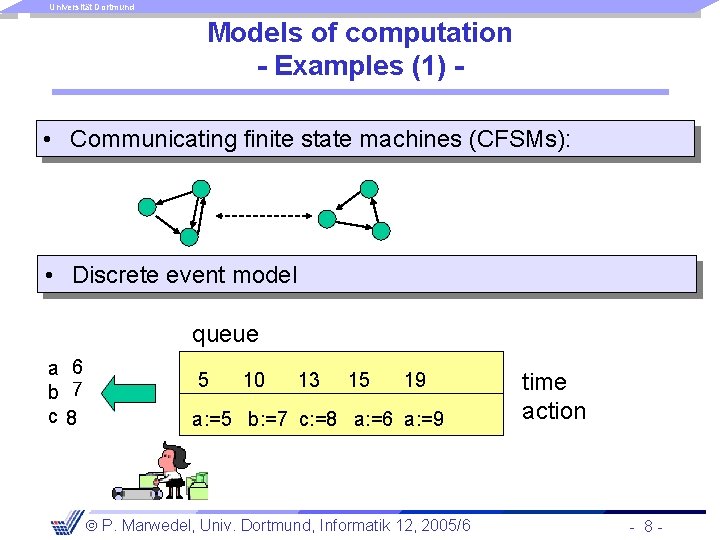

Universität Dortmund Models of computation - Examples (1) • Communicating finite state machines (CFSMs): • Discrete event model queue 6 a 5 b 7 c 8 5 10 13 15 19 a: =5 b: =7 c: =8 a: =6 a: =9 P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 time action - 8 -

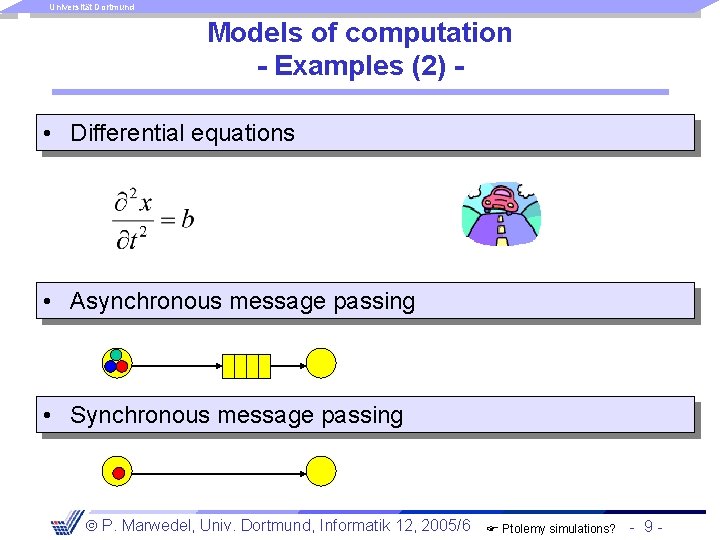

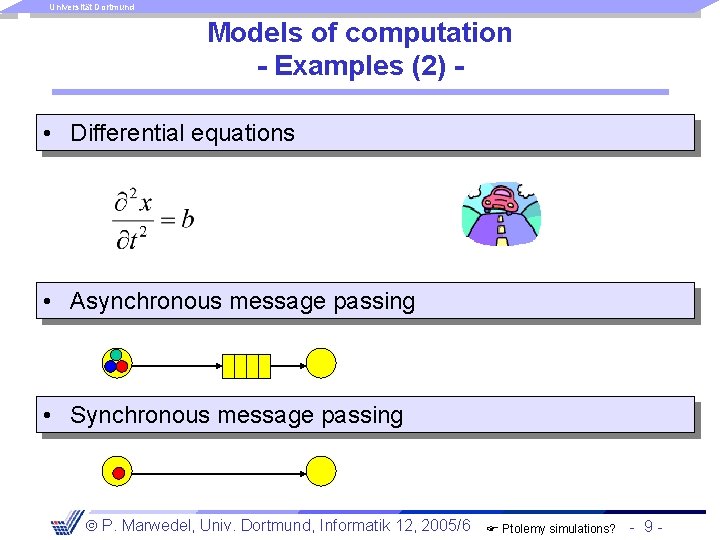

Universität Dortmund Models of computation - Examples (2) • Differential equations • Asynchronous message passing • Synchronous message passing P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 Ptolemy simulations? - 9 -

Universität Dortmund Facing reality No language that meets all language requirements using compromises P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 10 -

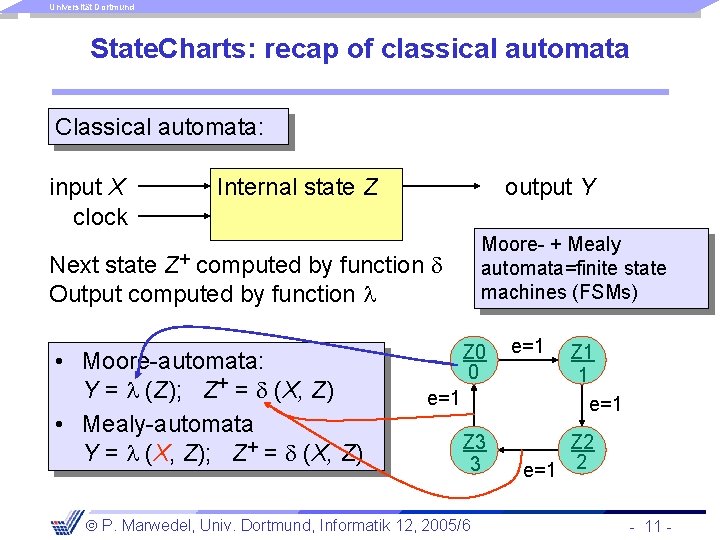

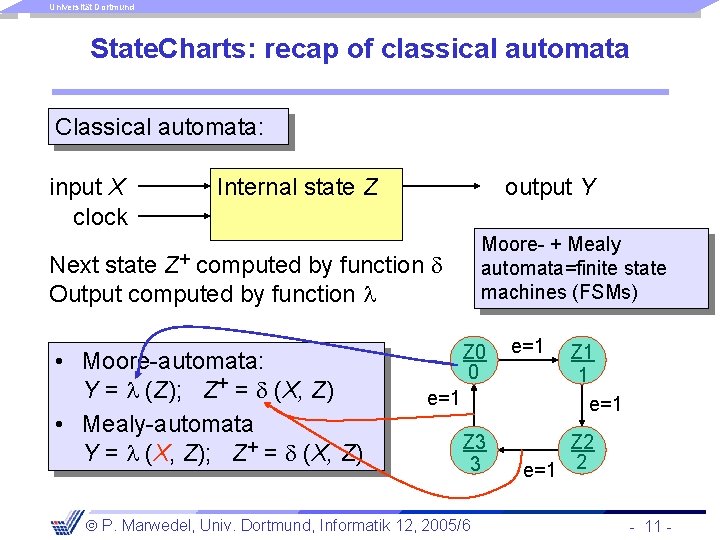

Universität Dortmund State. Charts: recap of classical automata Classical automata: input X clock Internal state Z output Y Moore- + Mealy automata=finite state machines (FSMs) Next state Z+ computed by function Output computed by function • Moore-automata: Y = (Z); Z+ = (X, Z) • Mealy-automata Y = (X, Z); Z+ = (X, Z) Z 0 0 e=1 Z 3 3 P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 e=1 Z 1 1 e=1 Z 2 e=1 2 - 11 -

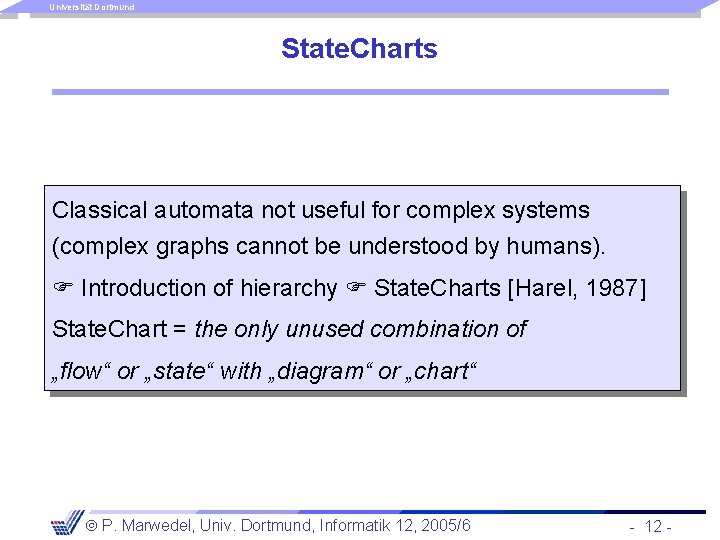

Universität Dortmund State. Charts Classical automata not useful for complex systems (complex graphs cannot be understood by humans). Introduction of hierarchy State. Charts [Harel, 1987] State. Chart = the only unused combination of „flow“ or „state“ with „diagram“ or „chart“ P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 12 -

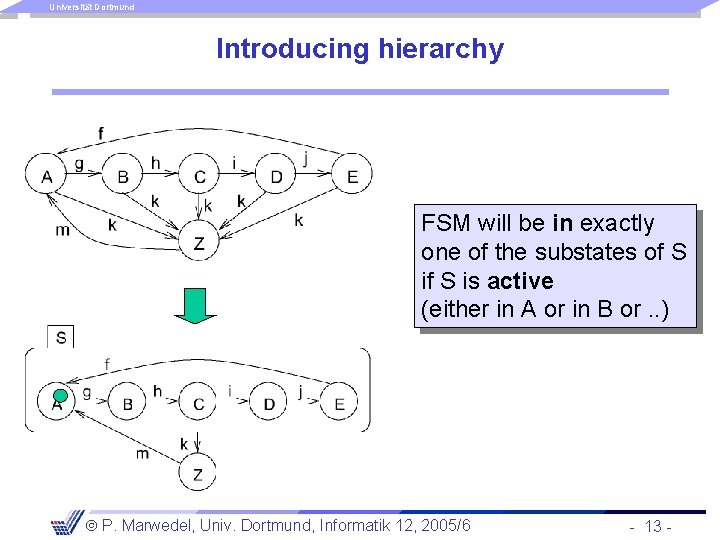

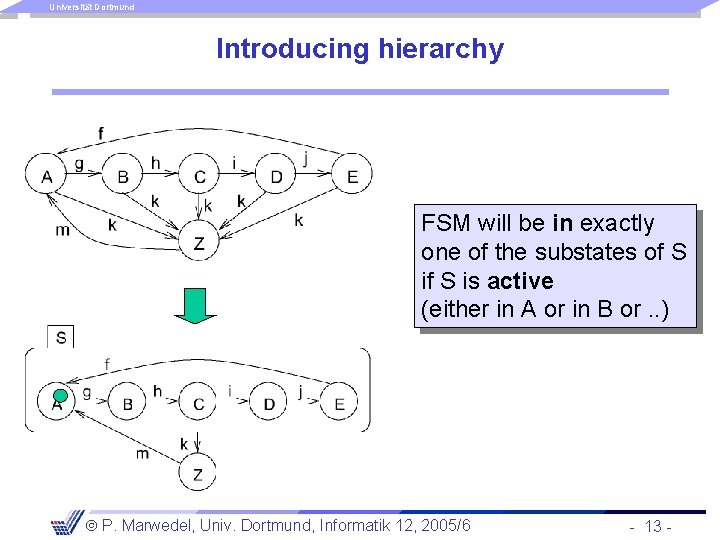

Universität Dortmund Introducing hierarchy FSM will be in exactly one of the substates of S is active (either in A or in B or. . ) P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 13 -

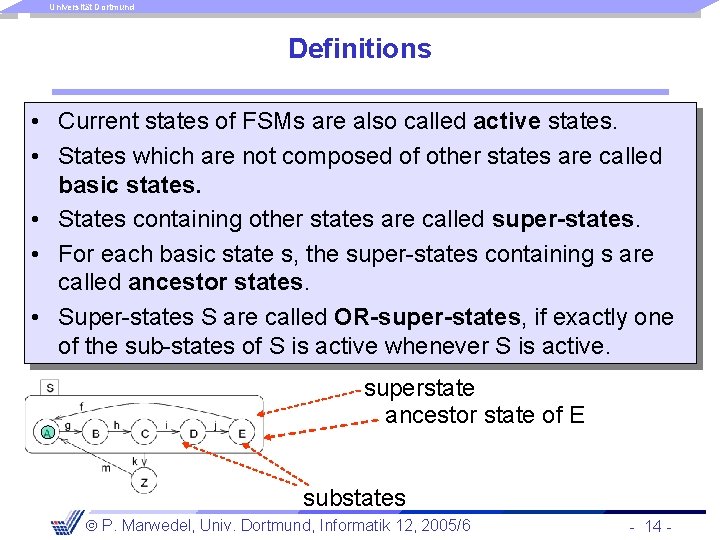

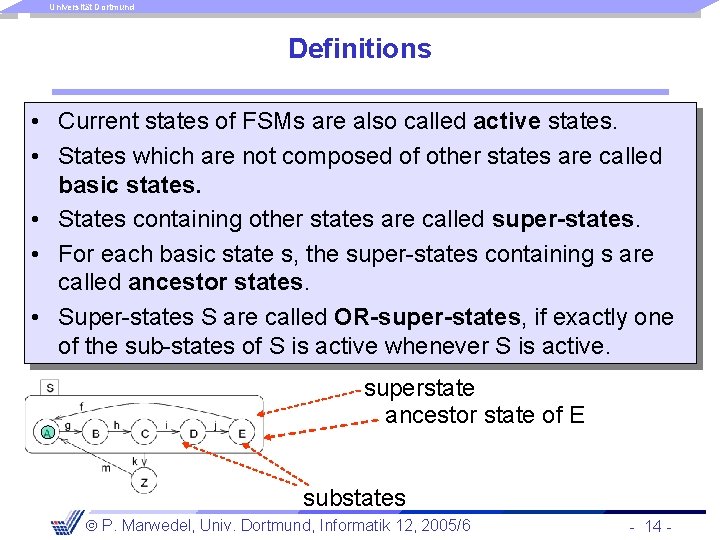

Universität Dortmund Definitions • Current states of FSMs are also called active states. • States which are not composed of other states are called basic states. • States containing other states are called super-states. • For each basic state s, the super-states containing s are called ancestor states. • Super-states S are called OR-super-states, if exactly one of the sub-states of S is active whenever S is active. superstate ancestor state of E substates P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 14 -

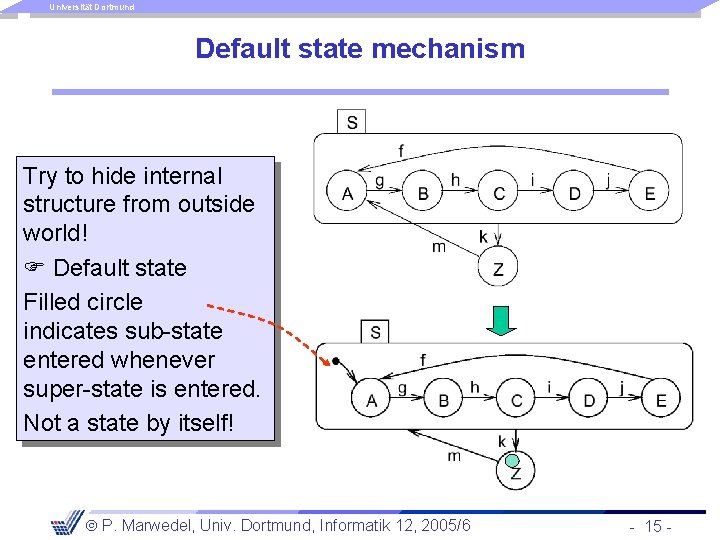

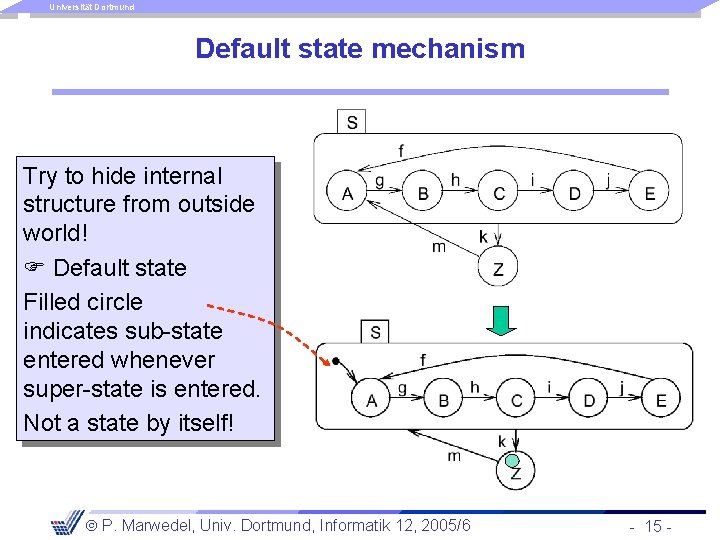

Universität Dortmund Default state mechanism Try to hide internal structure from outside world! Default state Filled circle indicates sub-state entered whenever super-state is entered. Not a state by itself! P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 15 -

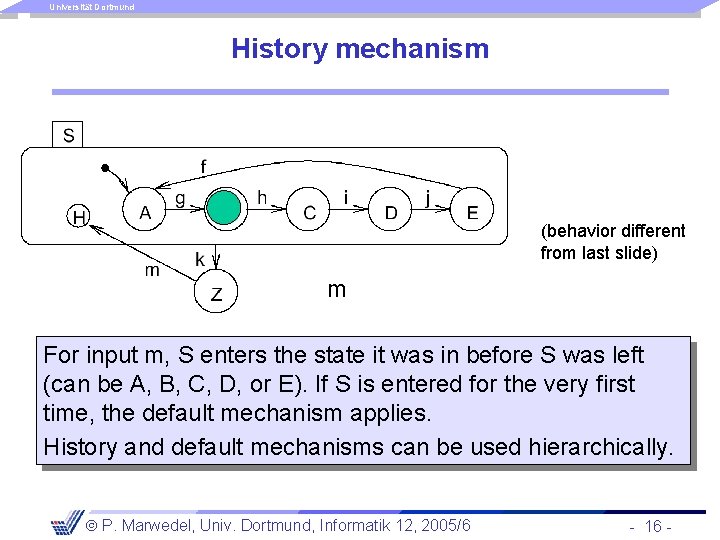

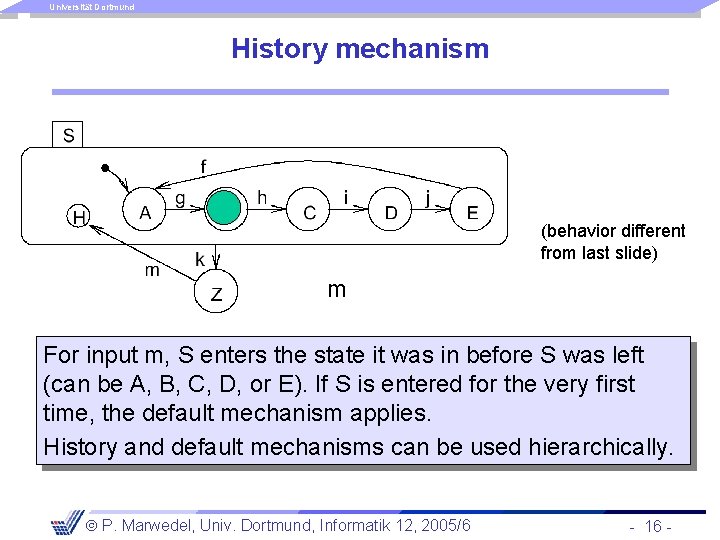

Universität Dortmund History mechanism (behavior different from last slide) km For input m, S enters the state it was in before S was left (can be A, B, C, D, or E). If S is entered for the very first time, the default mechanism applies. History and default mechanisms can be used hierarchically. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 16 -

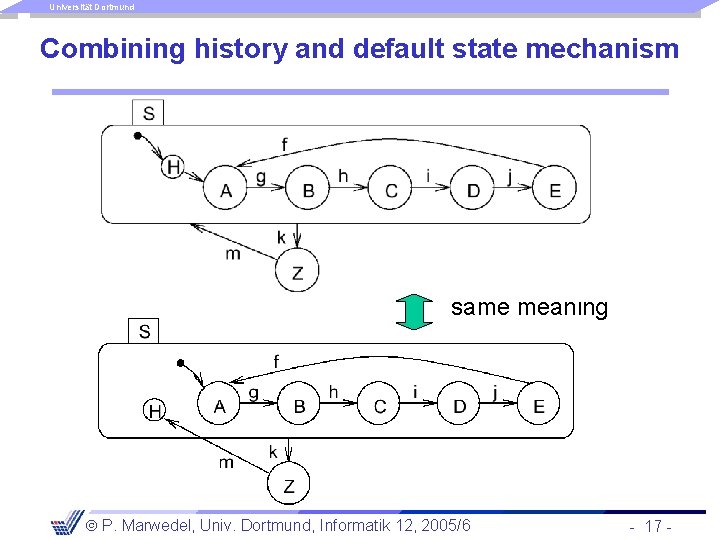

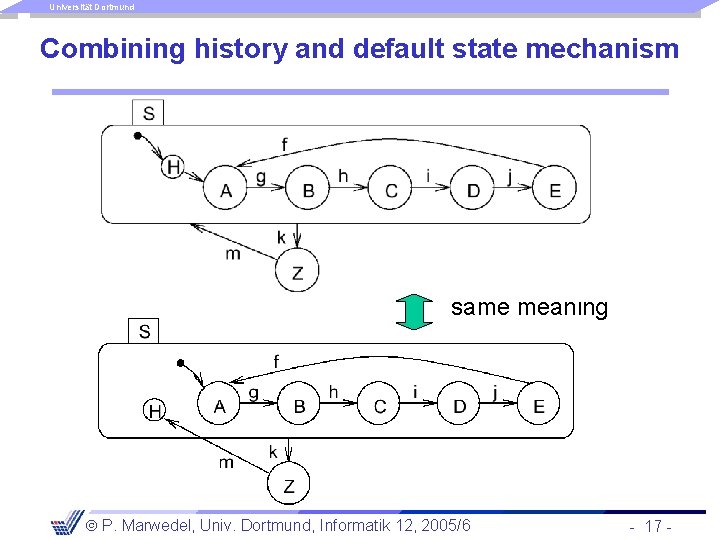

Universität Dortmund Combining history and default state mechanism same meaning P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 17 -

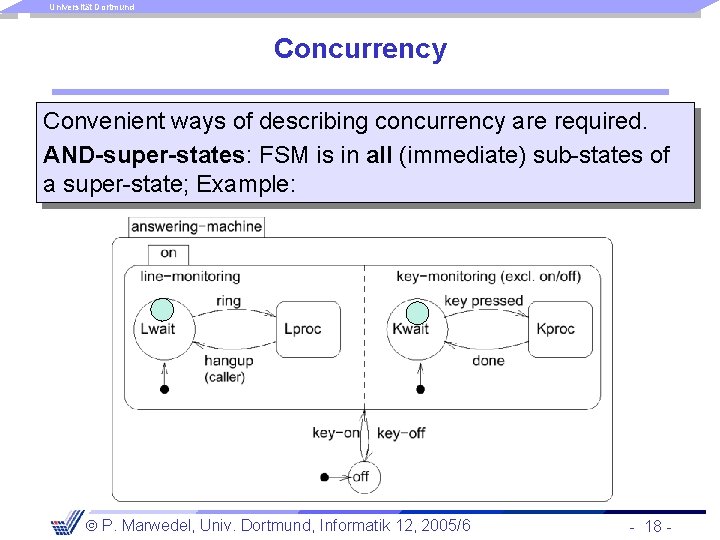

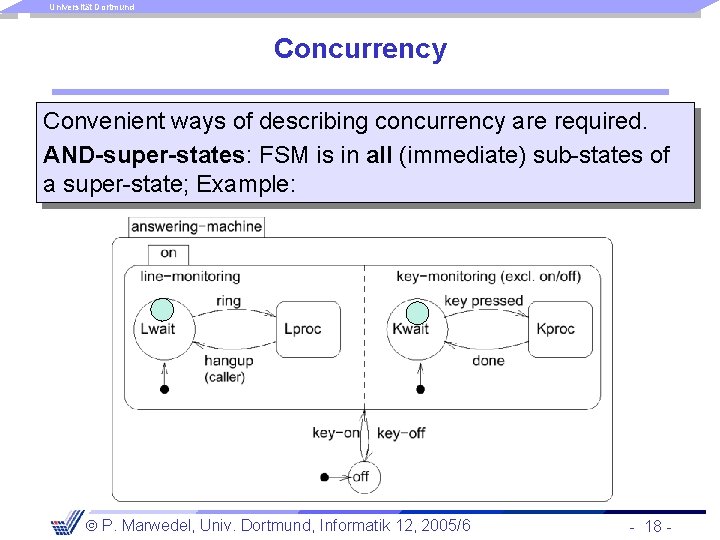

Universität Dortmund Concurrency Convenient ways of describing concurrency are required. AND-super-states: FSM is in all (immediate) sub-states of a super-state; Example: P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 18 -

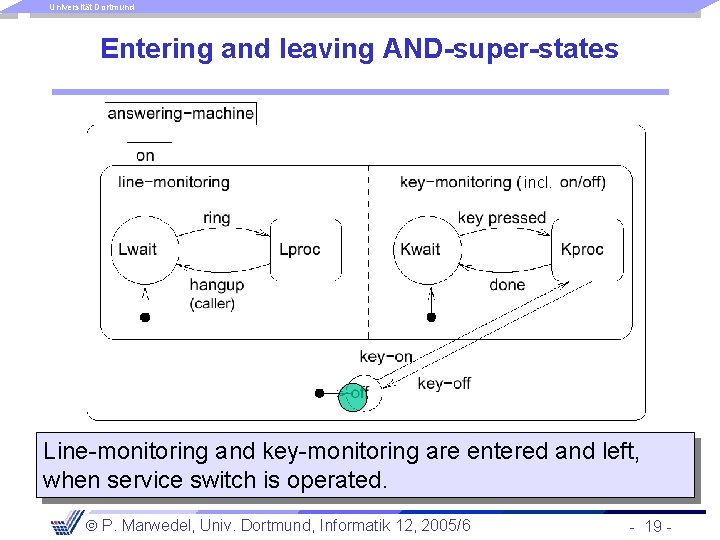

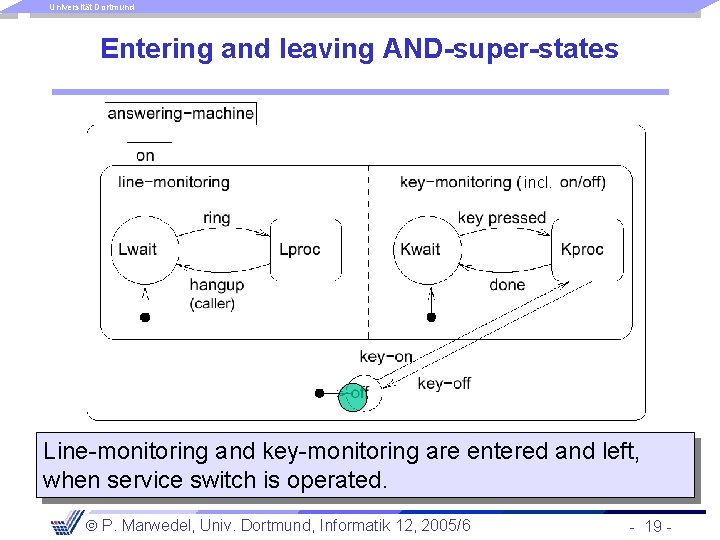

Universität Dortmund Entering and leaving AND-super-states incl. Line-monitoring and key-monitoring are entered and left, when service switch is operated. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 19 -

Universität Dortmund Types of states In State. Charts, states are either • basic states, or • AND-super-states, or • OR-super-states. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 20 -

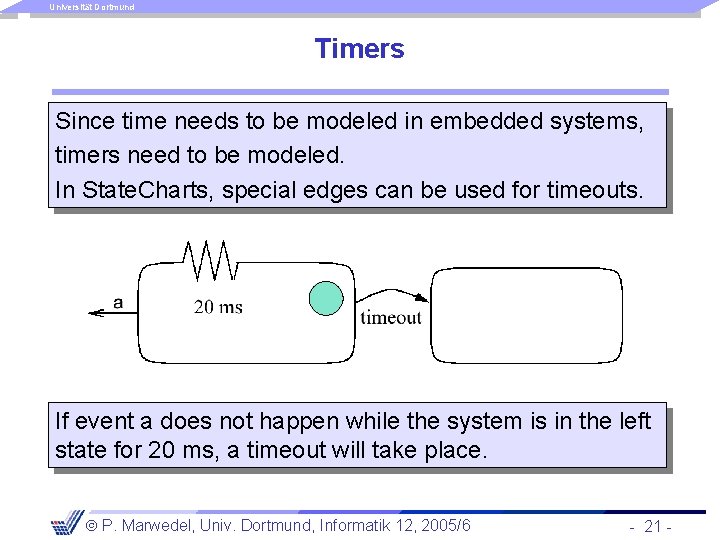

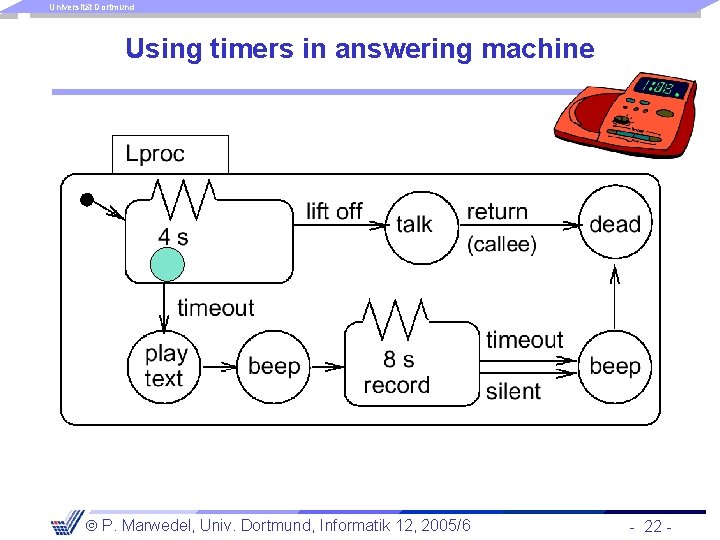

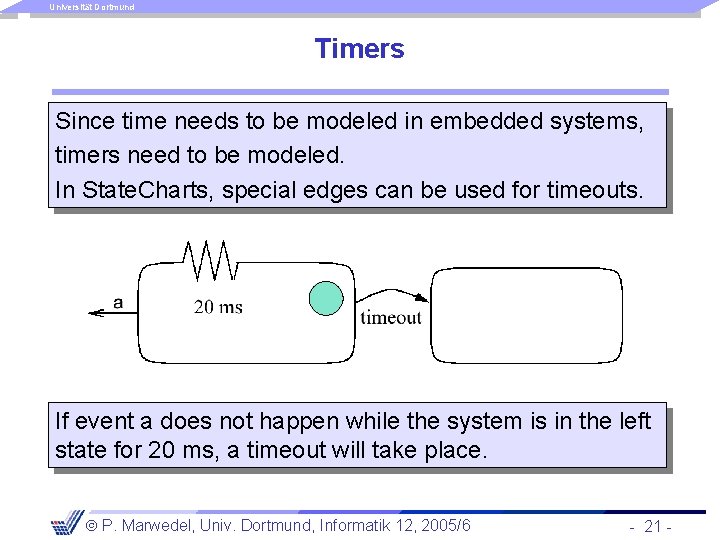

Universität Dortmund Timers Since time needs to be modeled in embedded systems, timers need to be modeled. In State. Charts, special edges can be used for timeouts. If event a does not happen while the system is in the left state for 20 ms, a timeout will take place. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 21 -

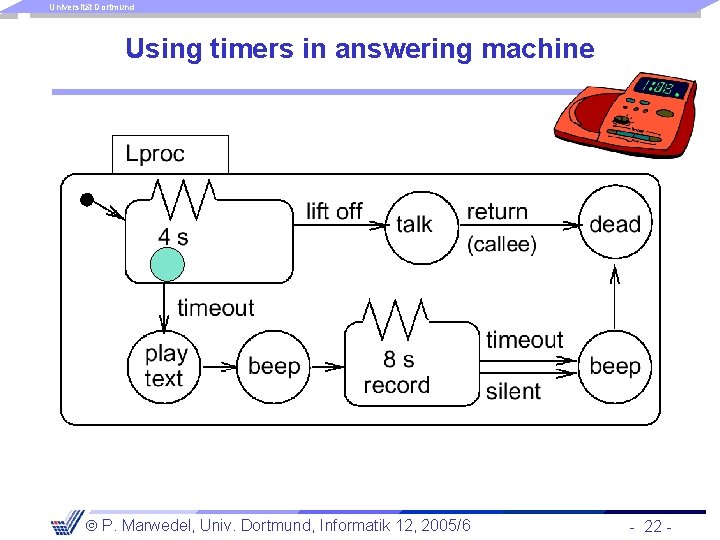

Universität Dortmund Using timers in answering machine P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 22 -

![Universität Dortmund General form of edge labels event condition reaction Events Exist Universität Dortmund General form of edge labels event [condition] / reaction Events: • Exist](https://slidetodoc.com/presentation_image_h/14c59b32ffd50c4b645be134a8387bf8/image-23.jpg)

Universität Dortmund General form of edge labels event [condition] / reaction Events: • Exist only until the next evaluation of the model • Can be either internally or externally generated Conditions: • Refer to values of variables that keep their value until they are reassigned Reactions: • Can either be assignments for variables or creation of events Example: • service-off [not in Lproc] / service: =0 P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 23 -

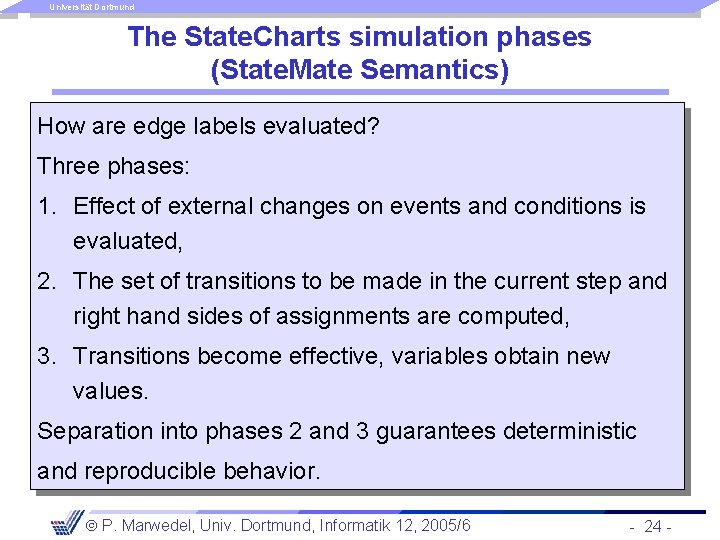

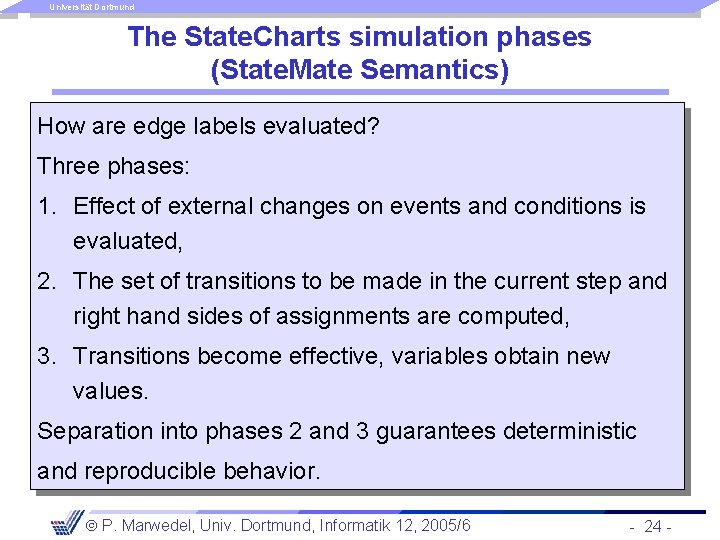

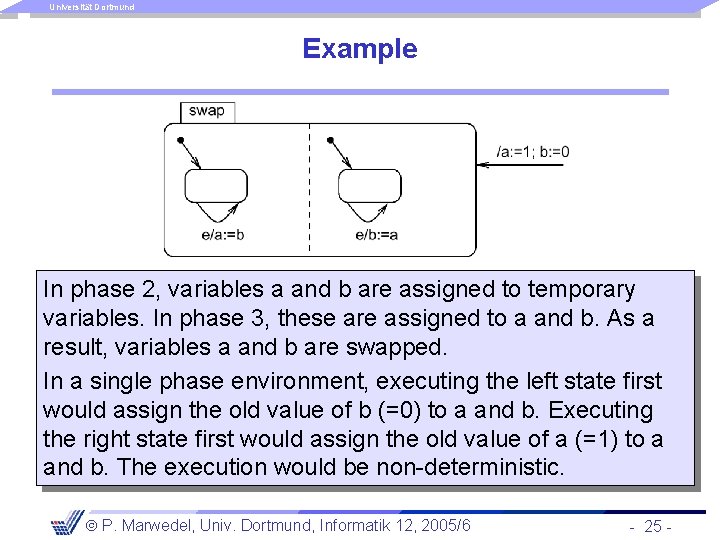

Universität Dortmund The State. Charts simulation phases (State. Mate Semantics) How are edge labels evaluated? Three phases: 1. Effect of external changes on events and conditions is evaluated, 2. The set of transitions to be made in the current step and right hand sides of assignments are computed, 3. Transitions become effective, variables obtain new values. Separation into phases 2 and 3 guarantees deterministic and reproducible behavior. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 24 -

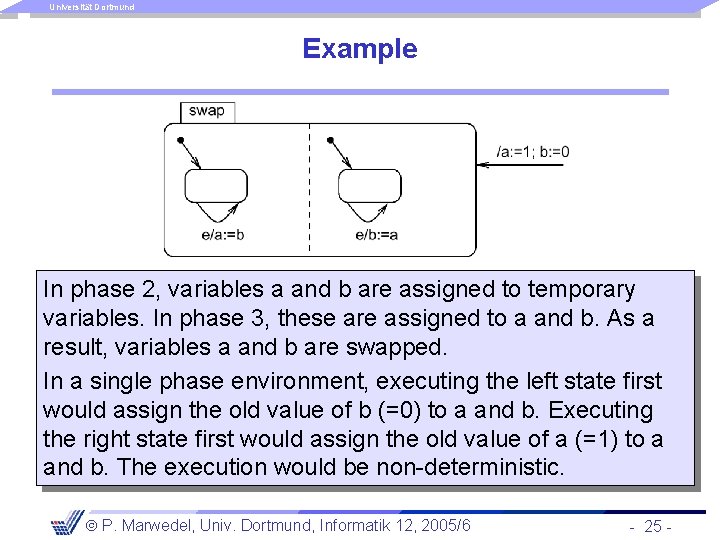

Universität Dortmund Example In phase 2, variables a and b are assigned to temporary variables. In phase 3, these are assigned to a and b. As a result, variables a and b are swapped. In a single phase environment, executing the left state first would assign the old value of b (=0) to a and b. Executing the right state first would assign the old value of a (=1) to a and b. The execution would be non-deterministic. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 25 -

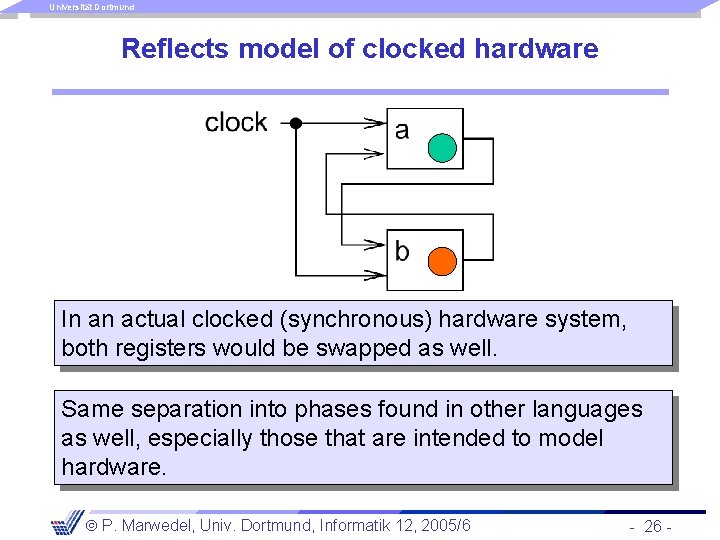

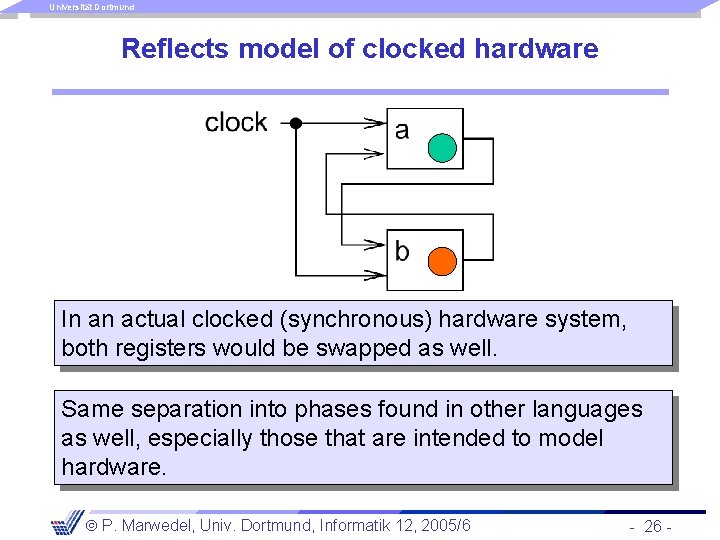

Universität Dortmund Reflects model of clocked hardware In an actual clocked (synchronous) hardware system, both registers would be swapped as well. Same separation into phases found in other languages as well, especially those that are intended to model hardware. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 26 -

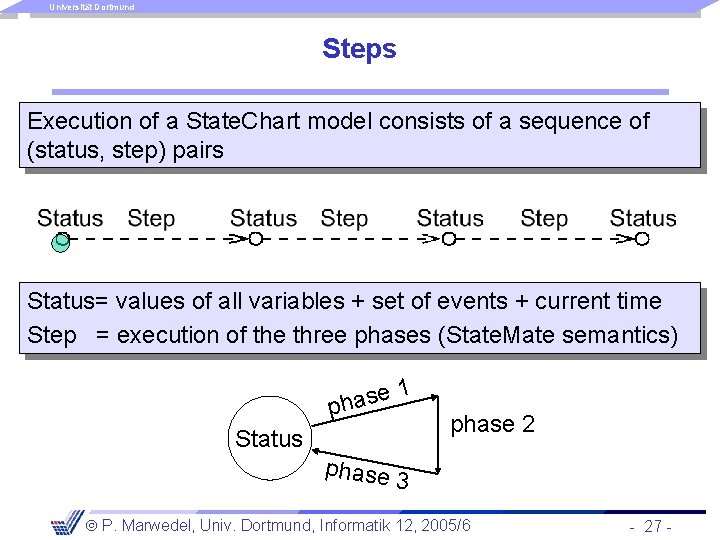

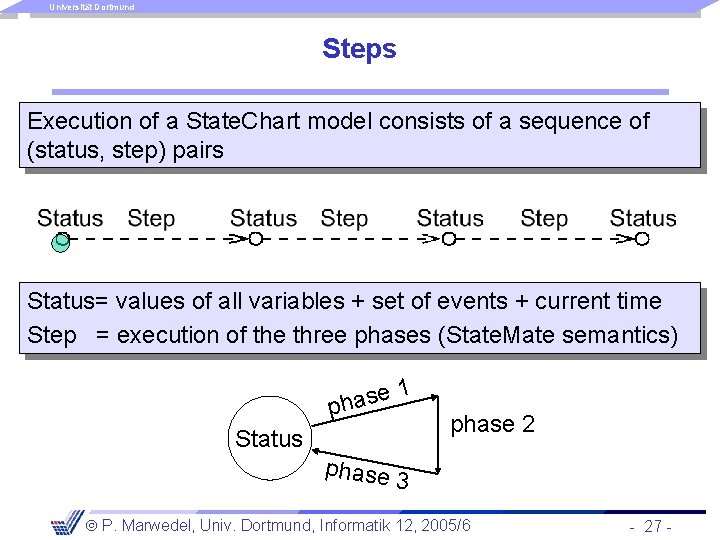

Universität Dortmund Steps Execution of a State. Chart model consists of a sequence of (status, step) pairs Status= values of all variables + set of events + current time Step = execution of the three phases (State. Mate semantics) 1 e s a ph Status phase 2 3 P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 27 -

Universität Dortmund Broadcast mechanism Values of variables are visible to all parts of the State. Chart model. New values become effective in phase 3 of the current step and are obtained by all parts of the model in the following step. State. Charts implicitly assumes a broadcast mechanism for variables. State. Charts is appropriate for local control systems ( ), but not for distributed applications for which updating variables might take some time ( ). P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 28 -

Universität Dortmund Lifetime of events Events live until the step following the one in which they are generated („one shot-events“). P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 29 -

Universität Dortmund Evaluation of State. Charts (1) Pros: • Hierarchy allows arbitrary nesting of AND- and OR-super states. • (State. Mate-) Semantics defined in a follow-up paper to original paper. • Large number of commercial simulation tools available (State. Mate, State. Flow, Better. State, . . . ) • Available „back-ends“ translate State. Charts into C or VHDL, thus enabling software or hardware implementations. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 30 -

Universität Dortmund Evaluation of State. Charts (2) Cons: • Generated C programs frequently inefficient, • Not useful for distributed applications, • No program constructs, • No description of non-functional behavior, • No object-orientation, • No description of structural hierarchy. Extensions: • Module charts for description of structural hierarchy. P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 31 -

Universität Dortmund Summary Requirements for specification languages – Hierarchy – Timing behavior – State-oriented behavior – Concurrency – Synchronization & communication, … Models of computation State. Charts – AND-states – OR-states – Timer – Broadcast – Semantics –… P. Marwedel, Univ. Dortmund, Informatik 12, 2005/6 - 32 -