Thumb Mode Chapter 8 Sepehr Naimi www Nicer

Thumb Mode Chapter 8 Sepehr Naimi www. Nicer. Land. com

Thumb Mode • Instructions are 16 -bit 2

Registers • Two registers instead of 3 registers • Only the low 8 registers (R 0 to R 7) 3

Instructions affect the flags • Just ADDS (No ADD) 4

No Barrel shifter • add r 1, r 2, lsl #6 5

Only branches can be conditional • subne r 1, r 2 6

Limited immediate values • 8 bits in the mov instruction without any rotations (values 0 to 255) • 3 bits in data processing instructions (values 0 to 7): – adds r 1, r 2, #126 – Instead: • mov r 2, #126 • adds r 1, r 2 7

Branch range • 11 -bit offset in the Branch • 8 -bit offset in the conditional branches 8

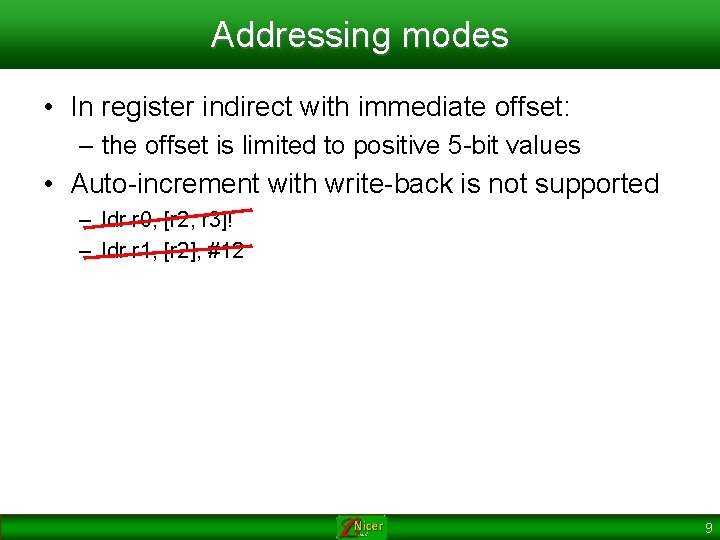

Addressing modes • In register indirect with immediate offset: – the offset is limited to positive 5 -bit values • Auto-increment with write-back is not supported – ldr r 0, [r 2, r 3]! – ldr r 1, [r 2], #12 9

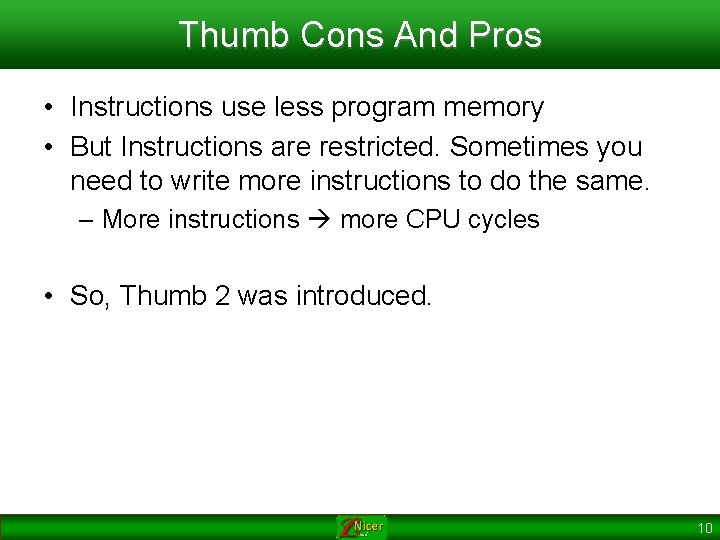

Thumb Cons And Pros • Instructions use less program memory • But Instructions are restricted. Sometimes you need to write more instructions to do the same. – More instructions more CPU cycles • So, Thumb 2 was introduced. 10

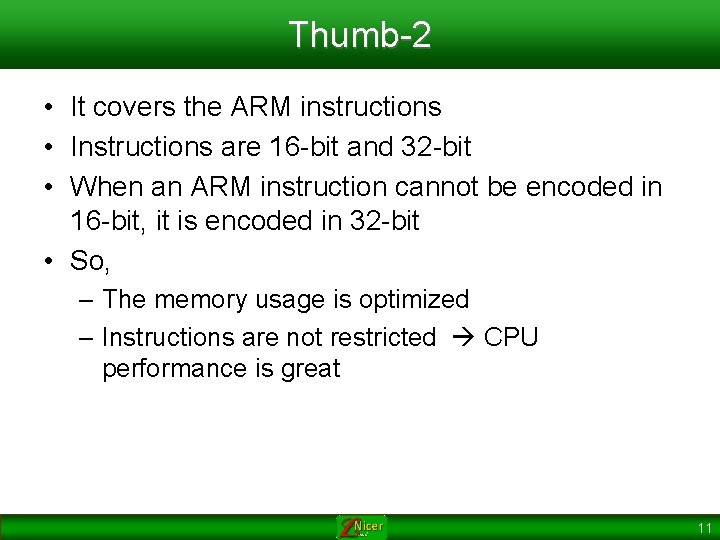

Thumb-2 • It covers the ARM instructions • Instructions are 16 -bit and 32 -bit • When an ARM instruction cannot be encoded in 16 -bit, it is encoded in 32 -bit • So, – The memory usage is optimized – Instructions are not restricted CPU performance is great 11

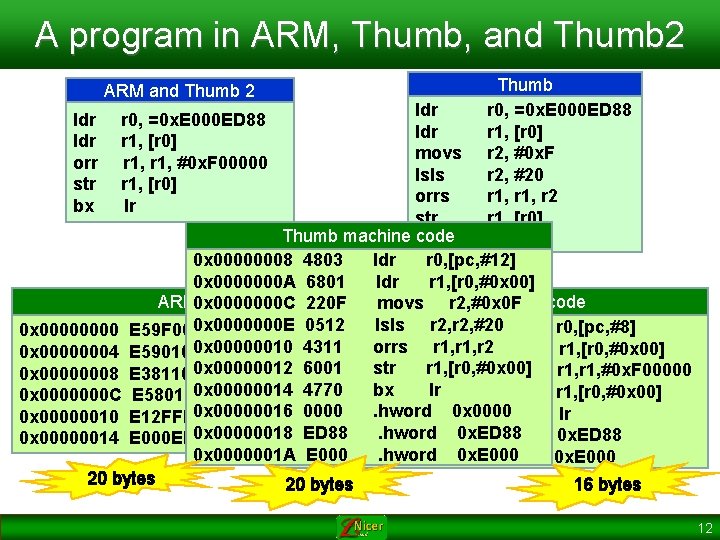

A program in ARM, Thumb, and Thumb 2 Thumb ldr r 0, =0 x. E 000 ED 88 ldr r 1, [r 0] movs r 2, #0 x. F orr r 1, #0 x. F 00000 lsls r 2, #20 str r 1, [r 0] orrs r 1, r 2 bx lr str r 1, [r 0] Thumb machine bx code lr 0 x 00000008 4803 ldr r 0, [pc, #12] 0 x 0000000 A 6801 ldr r 1, [r 0, #0 x 00] ARM 0 x 0000000 C 220 F movs r 2, #0 x 0 F machine code Thumb-2 machine code 0 x 0000000 E 0512 lsls r 2, #20 0 x 00000008 4802 ldr r 0, [pc, #8] 0 x 0000 E 59 F 000 C ldr r 0, [pc, #0 x 000 C] 0 x 00000010 4311 orrs r 1, r 2 0 x 0000000 A 6801 ldr r 1, [r 0, #0 x 00] 0 x 00000004 E 5901000 ldr r 1, [r 0] 0 x 00000012 6001 str r 1, [r 0, #0 x 00] 0 x 0000000 C F 4410170 orr r 1, #0 x. F 00000 0 x 00000008 E 381160 F orr r 1, #0 x 00 F 00000 0 x 00000014 4770 bx lr 0 x 00000010 6001 str r 1, [r 0, #0 x 00] 0 x 0000000 C E 5801000 str r 1, [r 0] 0 x 00000016 0000 . hword 0 x 00000012 4770 bx lr 0 x 00000010 E 12 FFF 1 E bx r 14 0 x 00000018 ED 88 . hword 0 x. ED 88 0 x 00000014 ED 88 . hword 0 x. ED 88 0 x 00000014 E 000 ED 88 . word 0 x. E 000 ED 88 0 x 0000001 A E 000 . hword 0 x. E 000 0 x 00000016 E 000 . hword 0 x. E 000 20 bytes 16 bytes ARM and Thumb 2 12

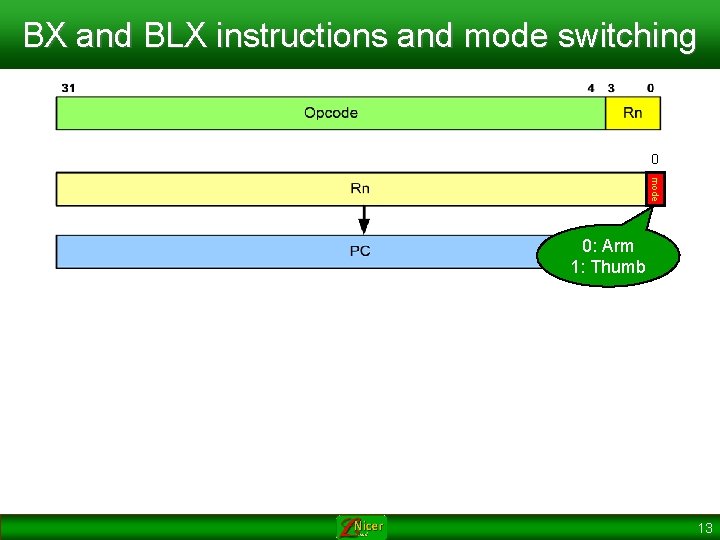

BX and BLX instructions and mode switching 0 mode 0: Arm 1: Thumb 13

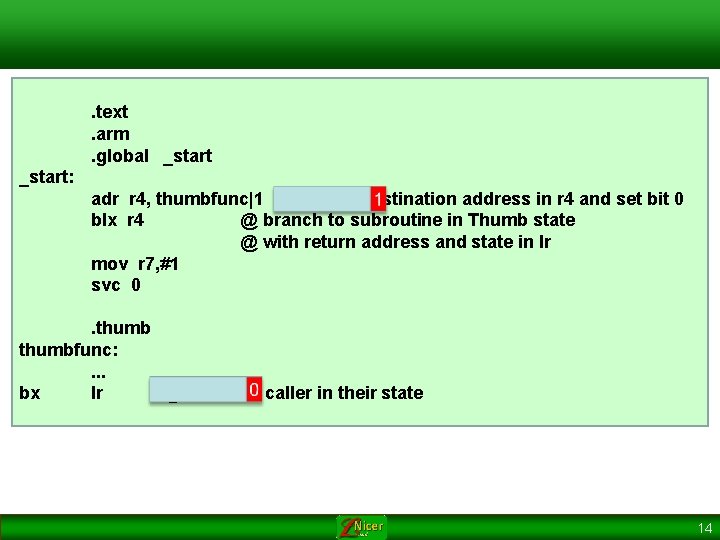

. text. arm. global _start: adr r 4, thumbfunc|1 @ put the destination address in r 4 and set bit 0 blx r 4 @ branch to subroutine in Thumb state @ with return address and state in lr mov r 7, #1 svc 0 . thumbfunc: . . . bx lr @ return to caller in their state 14

- Slides: 14