The von Neumann Machine X 86 64 Overview

- Slides: 17

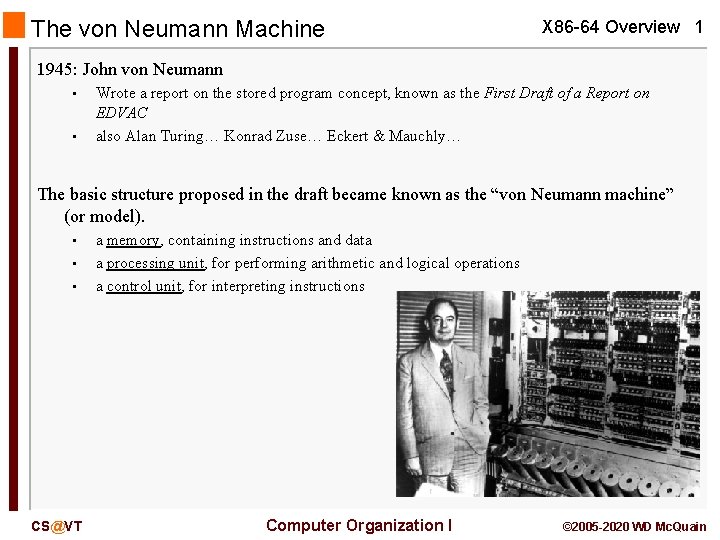

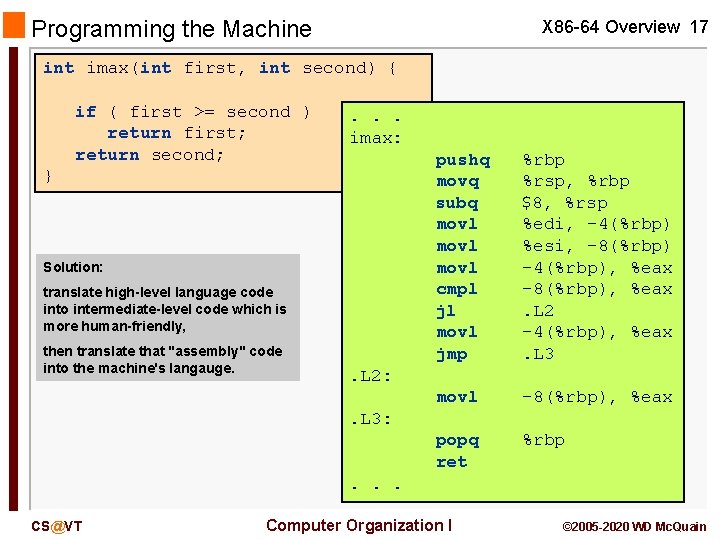

The von Neumann Machine X 86 -64 Overview 1 1945: John von Neumann • • Wrote a report on the stored program concept, known as the First Draft of a Report on EDVAC also Alan Turing… Konrad Zuse… Eckert & Mauchly… The basic structure proposed in the draft became known as the “von Neumann machine” (or model). • • • CS@VT a memory, containing instructions and data a processing unit, for performing arithmetic and logical operations a control unit, for interpreting instructions Computer Organization I © 2005 -2020 WD Mc. Quain

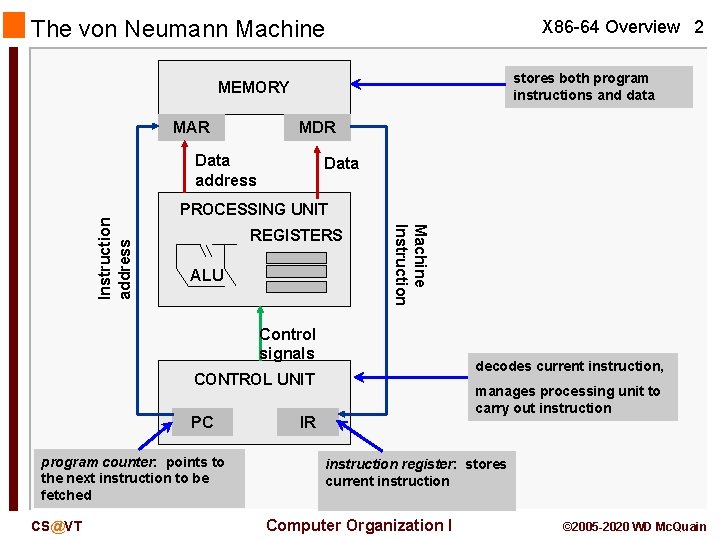

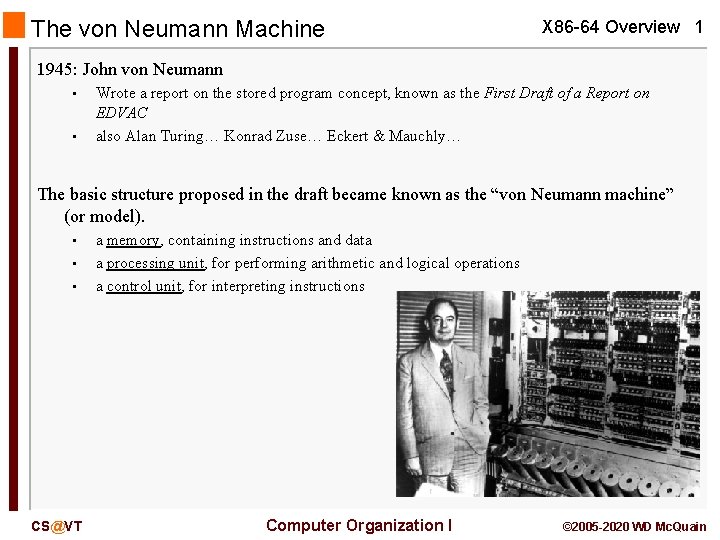

The von Neumann Machine X 86 -64 Overview 2 stores both program instructions and data MEMORY MAR MDR Data PROCESSING UNIT REGISTERS ALU Machine Instruction address Data address Control signals decodes current instruction, CONTROL UNIT PC program counter: points to the next instruction to be fetched CS@VT manages processing unit to carry out instruction IR instruction register: stores current instruction Computer Organization I © 2005 -2020 WD Mc. Quain

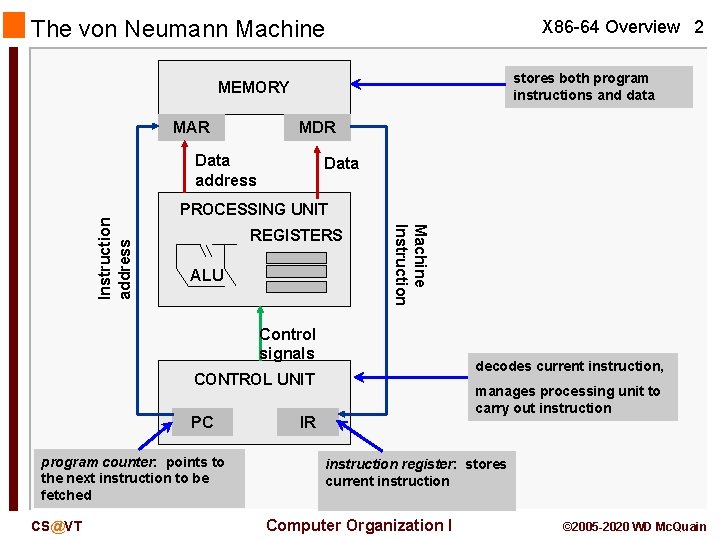

Intel x 86 Family X 86 -64 Overview 3 Totally dominate laptop/desktop/server market Evolutionary design • • • Backwards compatible to the 8086, introduced in 1978 Open architecture: 3 rd party suppliers for all sorts of external hardware and software Added more features as time went on Complex instruction set computer architecture (CISC) • Many different instructions with many different formats • • • Hard to match performance of Reduced Instruction Set Architectures (RISC) But, Intel has done just that! • CS@VT But, only small subset encountered with Linux programs In terms of speed. Less so for low power. Computer Organization I © 2005 -2020 WD Mc. Quain

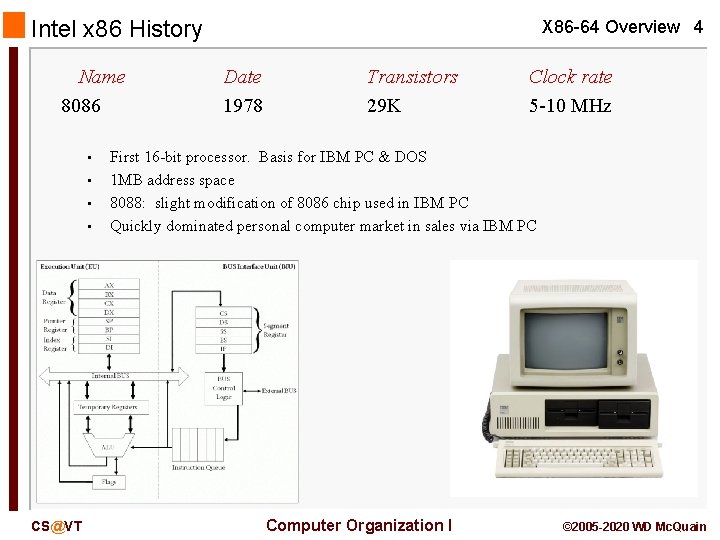

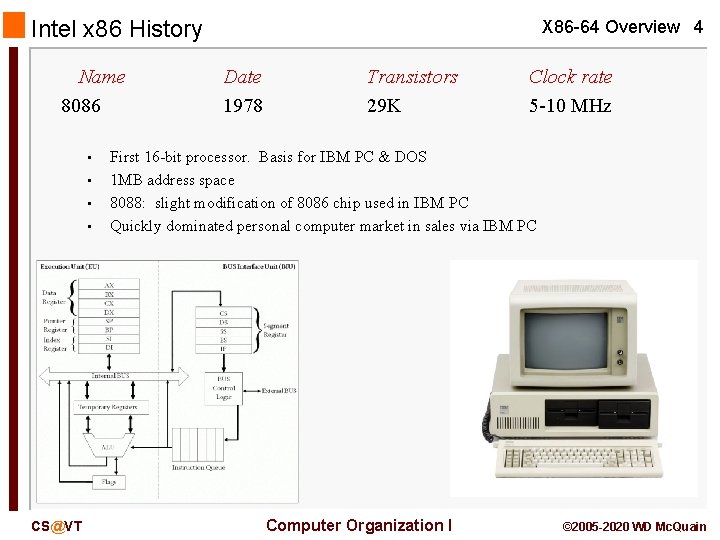

Intel x 86 History Name 8086 • • CS@VT X 86 -64 Overview 4 Date 1978 Transistors 29 K Clock rate 5 -10 MHz First 16 -bit processor. Basis for IBM PC & DOS 1 MB address space 8088: slight modification of 8086 chip used in IBM PC Quickly dominated personal computer market in sales via IBM PC Computer Organization I © 2005 -2020 WD Mc. Quain

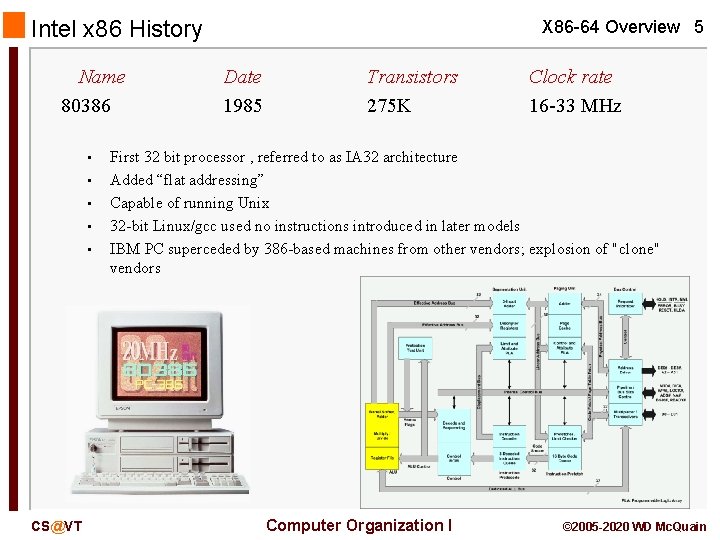

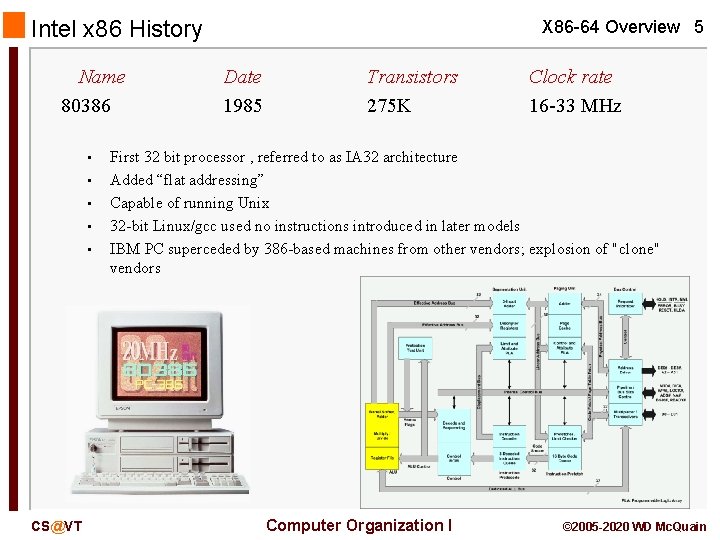

Intel x 86 History Name 80386 • • • CS@VT X 86 -64 Overview 5 Date 1985 Transistors 275 K Clock rate 16 -33 MHz First 32 bit processor , referred to as IA 32 architecture Added “flat addressing” Capable of running Unix 32 -bit Linux/gcc used no instructions introduced in later models IBM PC superceded by 386 -based machines from other vendors; explosion of "clone" vendors Computer Organization I © 2005 -2020 WD Mc. Quain

Intel x 86 History X 86 -64 Overview 6 Intel Attempted Radical Shift from IA 32 to IA 64 • • • Totally different architecture (Itanium) Executes IA 32 code only as legacy Performance disappointing AMD Stepped in with Evolutionary Solution • x 86 -64 (now called “AMD 64”) Intel Felt Obligated to Focus on IA 64 • Hard to admit mistake or that AMD's approach is better 2004: Intel Announces EM 64 T extension to IA 32 • • Extended Memory 64 -bit Technology Almost identical to x 86 -64! (Earlier Intel-AMD licensing agreement gives rights. ) All but low-end x 86 processors support x 86 -64 • CS@VT But, lots of code still runs in 32 -bit mode Computer Organization I © 2005 -2020 WD Mc. Quain

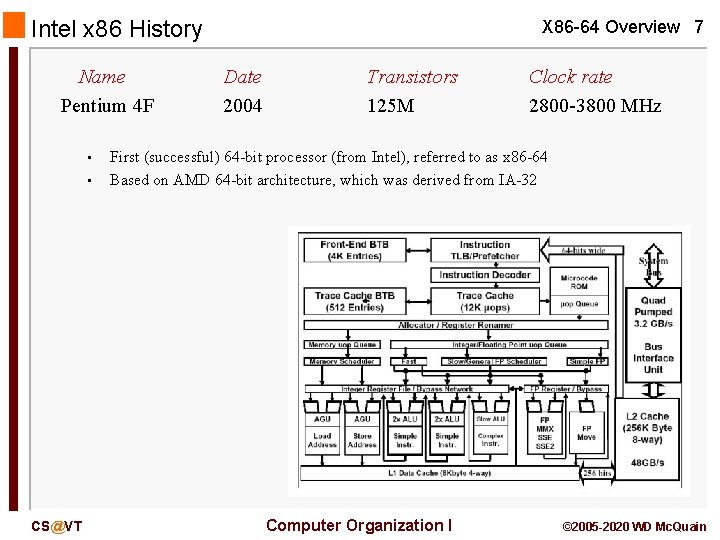

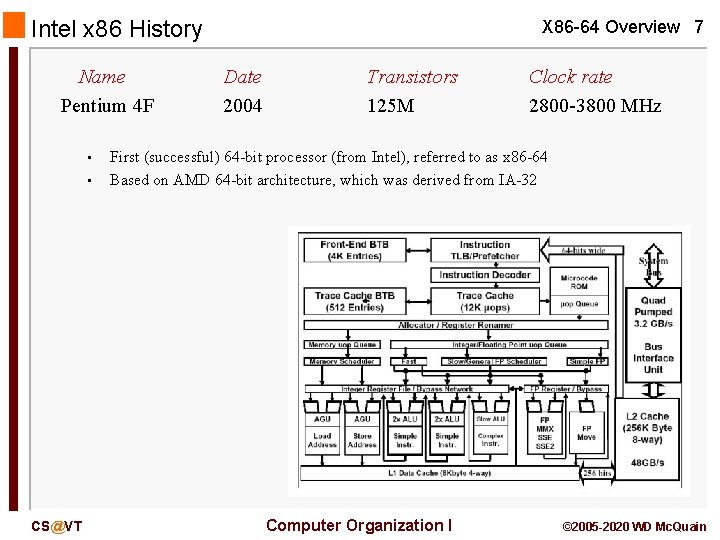

Intel x 86 History Name Pentium 4 F • • CS@VT X 86 -64 Overview 7 Date 2004 Transistors 125 M Clock rate 2800 -3800 MHz First (successful) 64 -bit processor (from Intel), referred to as x 86 -64 Based on AMD 64 -bit architecture, which was derived from IA-32 Computer Organization I © 2005 -2020 WD Mc. Quain

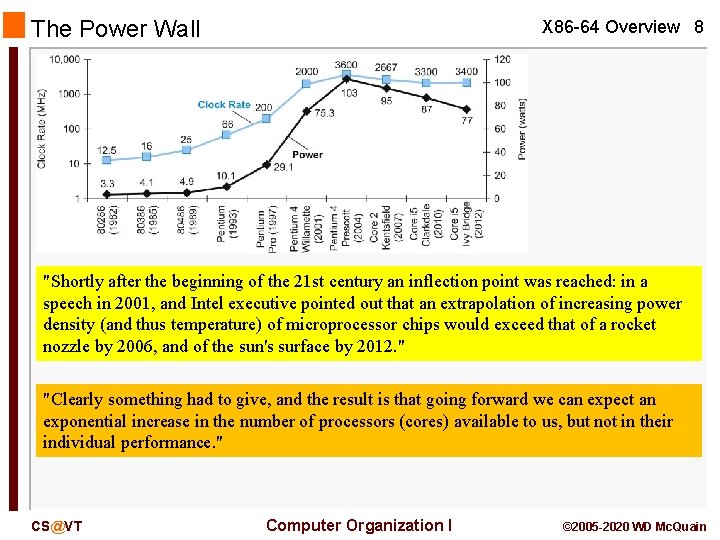

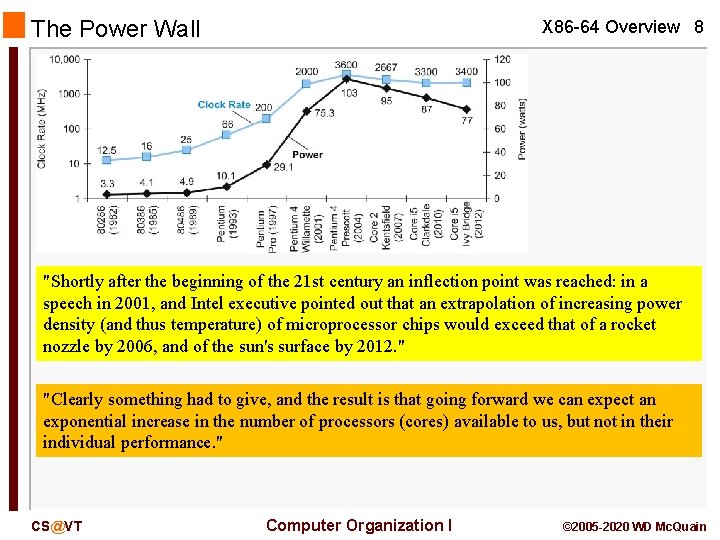

The Power Wall X 86 -64 Overview 8 "Shortly after the beginning of the 21 st century an inflection point was reached: in a speech in 2001, and Intel executive pointed out that an extrapolation of increasing power density (and thus temperature) of microprocessor chips would exceed that of a rocket nozzle by 2006, and of the sun's surface by 2012. " "Clearly something had to give, and the result is that going forward we can expect an exponential increase in the number of processors (cores) available to us, but not in their individual performance. " CS@VT Computer Organization I © 2005 -2020 WD Mc. Quain

Core I 7: the multicore revolution X 86 -64 Overview 9 Response to the Power Wall • • • CS@VT package multiple cores on a single processor die compensate for stagnant clock rates with parallel computation 2, 4, 6, 8 cores and beyond Computer Organization I © 2005 -2020 WD Mc. Quain

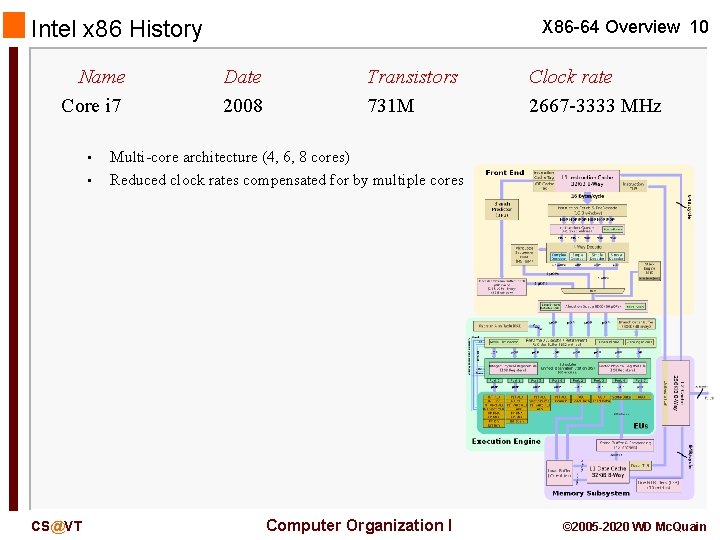

Intel x 86 History Name Core i 7 • • CS@VT X 86 -64 Overview 10 Date 2008 Transistors 731 M Clock rate 2667 -3333 MHz Multi-core architecture (4, 6, 8 cores) Reduced clock rates compensated for by multiple cores Computer Organization I © 2005 -2020 WD Mc. Quain

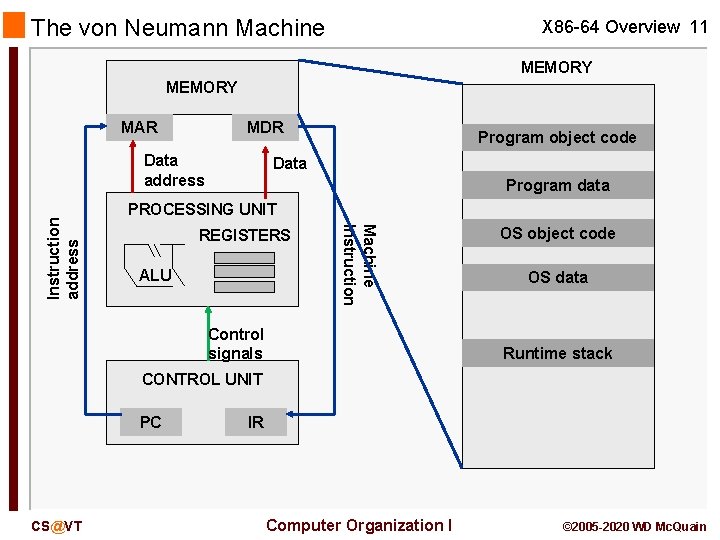

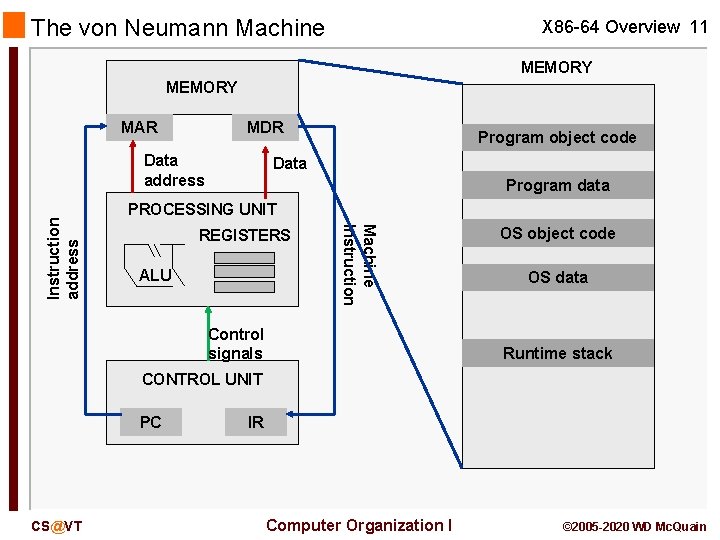

The von Neumann Machine X 86 -64 Overview 11 MEMORY MAR MDR Data Program data PROCESSING UNIT REGISTERS ALU Machine Instruction address Data address Program object code Control signals OS object code OS data Runtime stack CONTROL UNIT PC CS@VT IR Computer Organization I © 2005 -2020 WD Mc. Quain

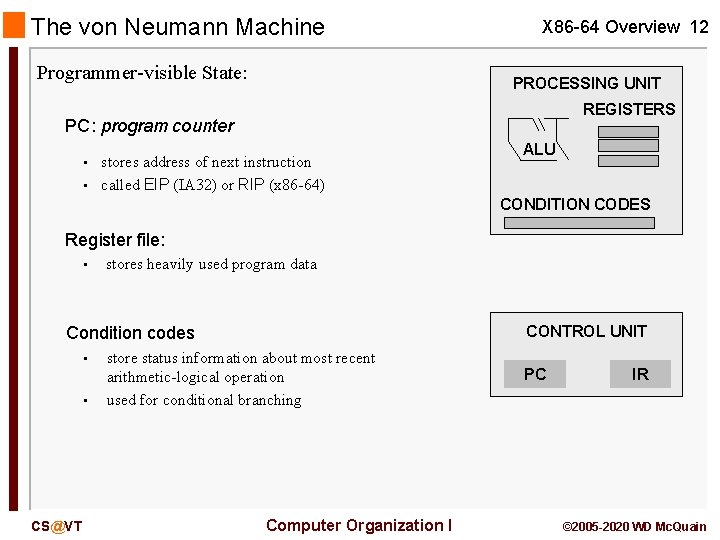

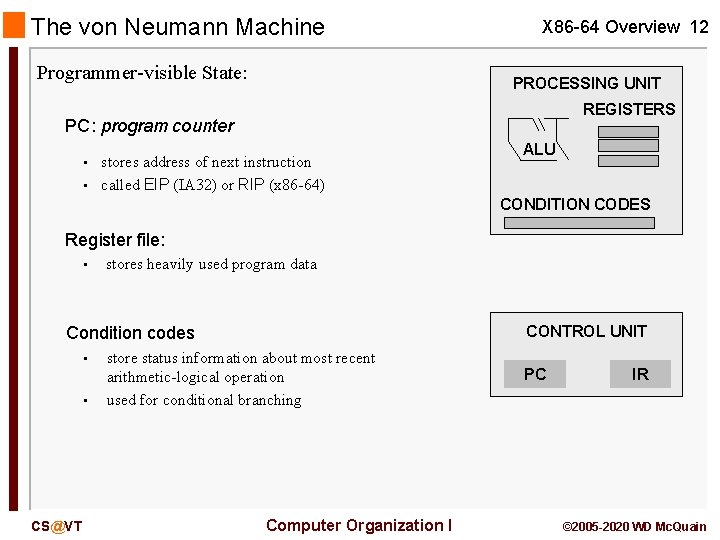

The von Neumann Machine Programmer-visible State: X 86 -64 Overview 12 PROCESSING UNIT REGISTERS PC: program counter • • stores address of next instruction called EIP (IA 32) or RIP (x 86 -64) ALU CONDITION CODES Register file: • stores heavily used program data CONTROL UNIT Condition codes • • CS@VT store status information about most recent arithmetic-logical operation used for conditional branching Computer Organization I PC IR © 2005 -2020 WD Mc. Quain

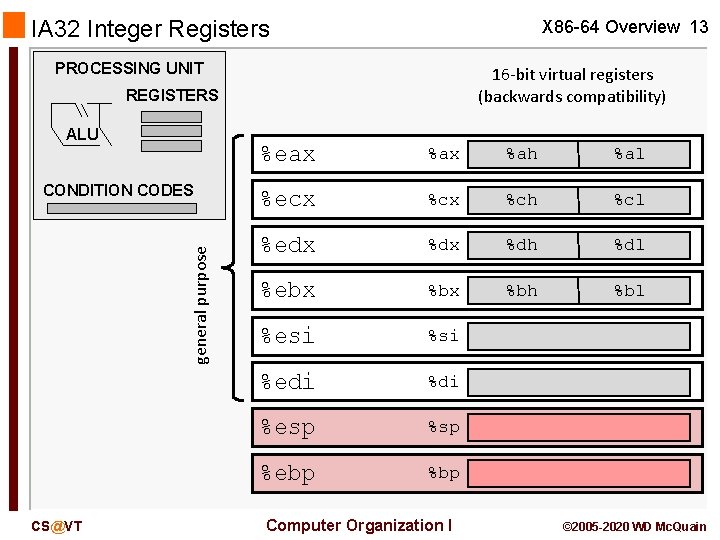

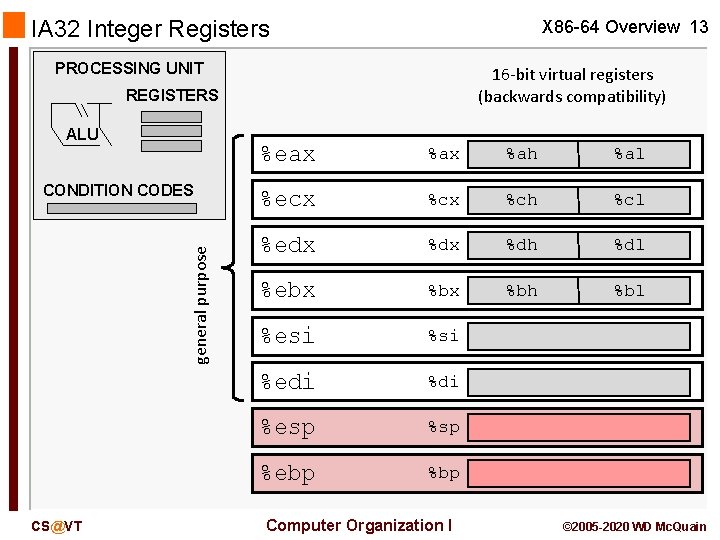

IA 32 Integer Registers X 86 -64 Overview 13 PROCESSING UNIT 16 -bit virtual registers (backwards compatibility) REGISTERS ALU general purpose CONDITION CODES CS@VT %eax %ah %al %ecx %ch %cl %edx %dh %dl %ebx %bh %bl %esi %edi %esp %ebp %bp Computer Organization I © 2005 -2020 WD Mc. Quain

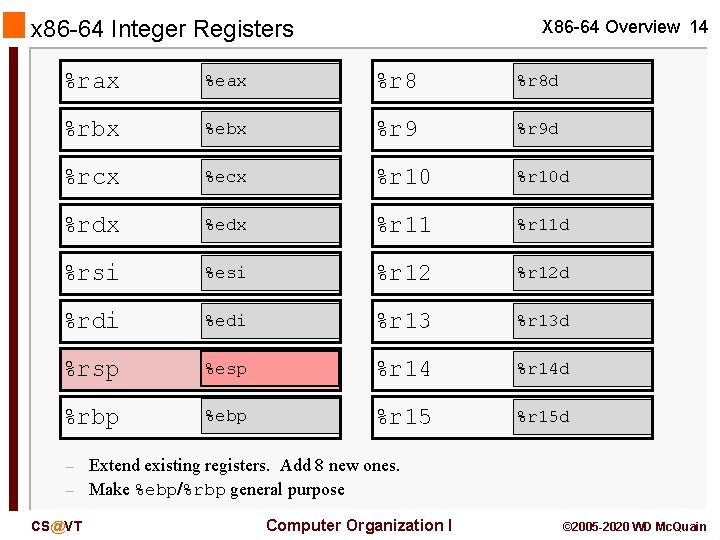

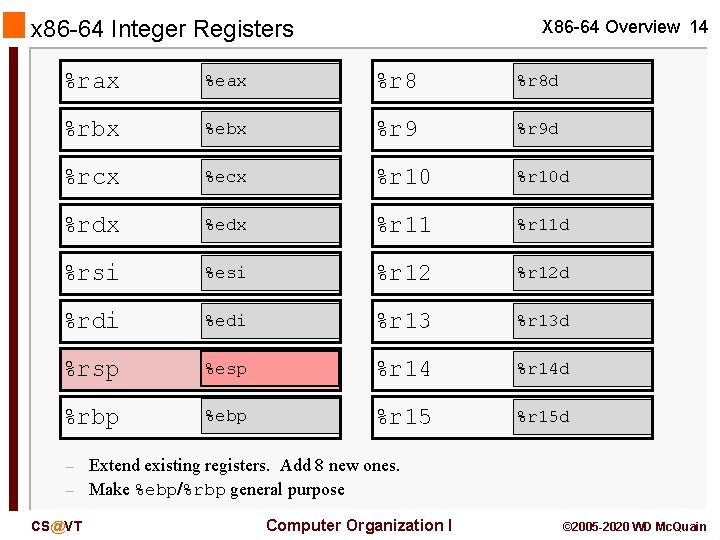

x 86 -64 Integer Registers X 86 -64 Overview 14 %rax %eax %r 8 d %rbx %ebx %r 9 d %rcx %ecx %r 10 d %rdx %edx %r 11 d %rsi %esi %r 12 d %rdi %edi %r 13 d %rsp %esp %r 14 d %rbp %ebp %r 15 d – – CS@VT Extend existing registers. Add 8 new ones. Make %ebp/%rbp general purpose Computer Organization I © 2005 -2020 WD Mc. Quain

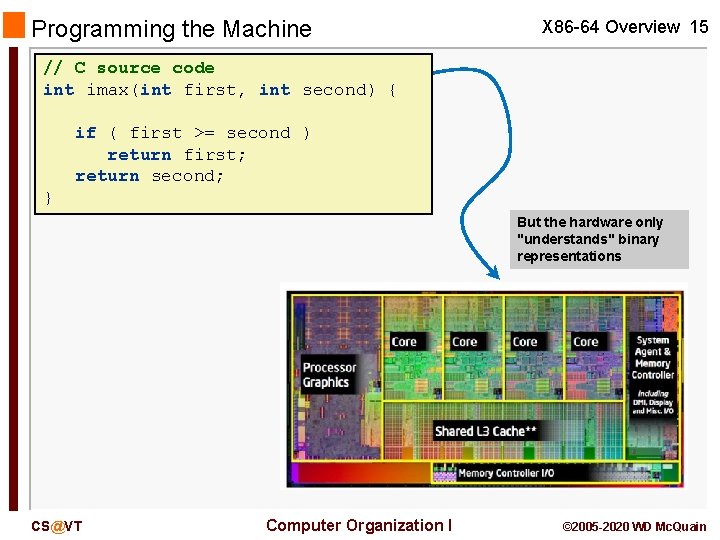

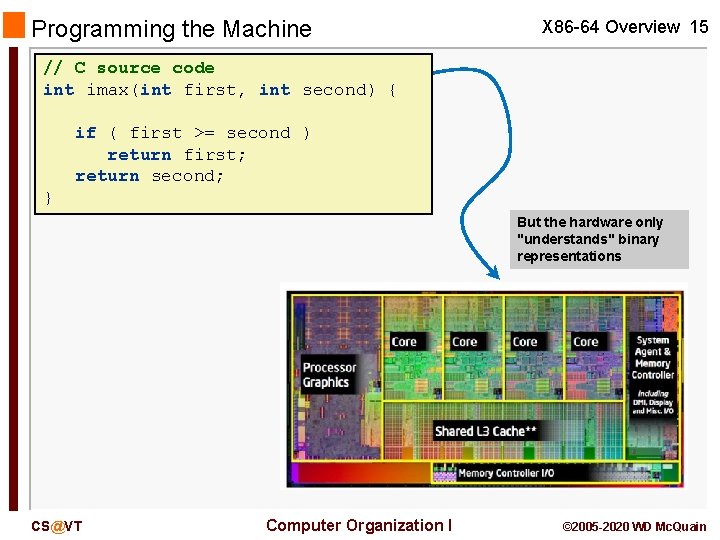

Programming the Machine X 86 -64 Overview 15 // C source code int imax(int first, int second) { if ( first >= second ) return first; return second; } But the hardware only "understands" binary representations CS@VT Computer Organization I © 2005 -2020 WD Mc. Quain

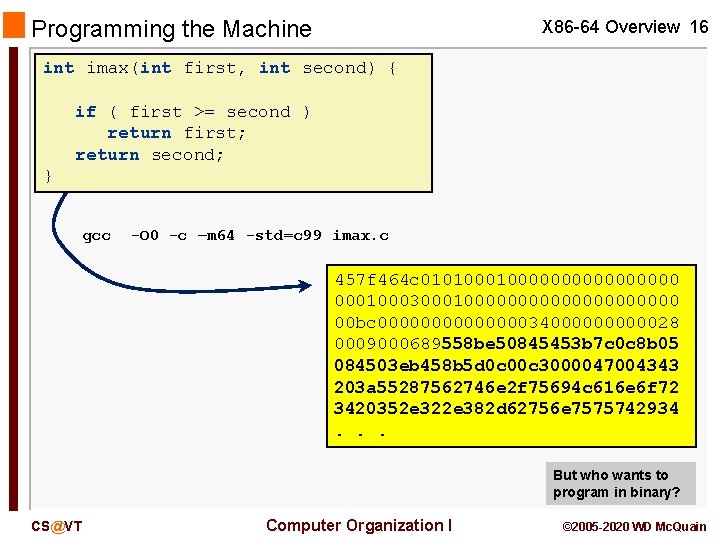

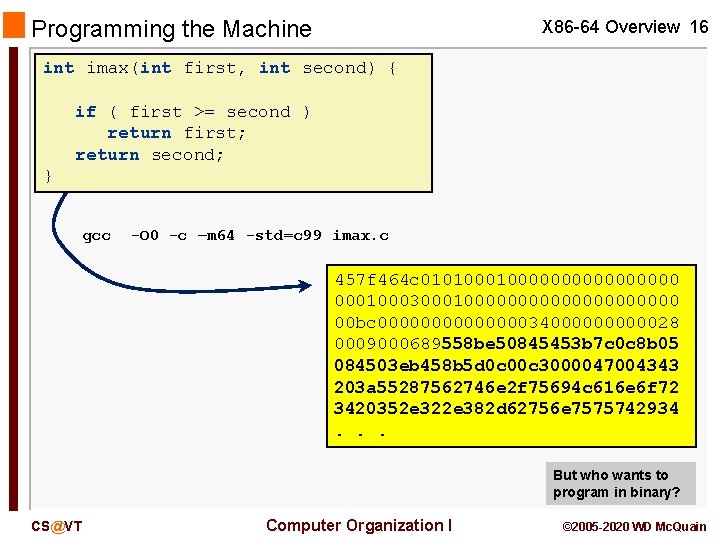

Programming the Machine X 86 -64 Overview 16 int imax(int first, int second) { if ( first >= second ) return first; return second; } gcc -O 0 -c –m 64 -std=c 99 imax. c 457 f 464 c 0101000000000 0001000300010000000000 00 bc 0000000340000028 0009000689558 be 50845453 b 7 c 0 c 8 b 05 084503 eb 458 b 5 d 0 c 00 c 3000047004343 203 a 55287562746 e 2 f 75694 c 616 e 6 f 72 3420352 e 322 e 382 d 62756 e 7575742934. . . But who wants to program in binary? CS@VT Computer Organization I © 2005 -2020 WD Mc. Quain

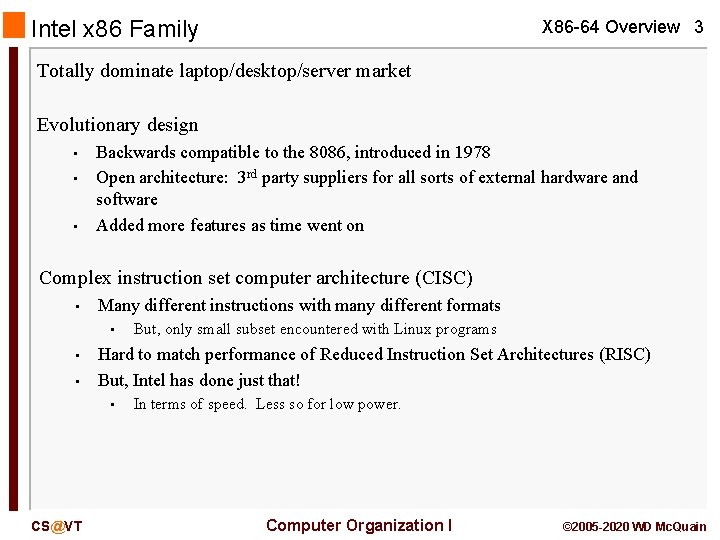

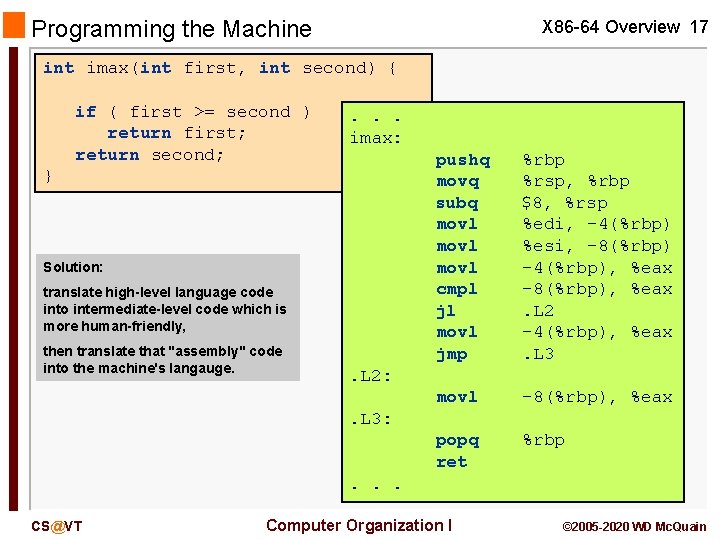

Programming the Machine X 86 -64 Overview 17 int imax(int first, int second) { if ( first >= second ) return first; return second; . . . imax: } Solution: translate high-level language code into intermediate-level code which is more human-friendly, then translate that "assembly" code into the machine's langauge. pushq movq subq movl cmpl jl movl jmp %rbp %rsp, %rbp $8, %rsp %edi, -4(%rbp) %esi, -8(%rbp) -4(%rbp), %eax -8(%rbp), %eax. L 2 -4(%rbp), %eax. L 3 movl -8(%rbp), %eax popq ret %rbp . L 2: . L 3: . . . CS@VT Computer Organization I © 2005 -2020 WD Mc. Quain