BLOC 3 de SPECIALITE NSI Architectures matrielles systmes

BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée - Circuits séquentiels et automates - Architecture de Von Neumann - Jeux d’instructions et langage machine

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Avant propos Le découpage temporel du bloc 3 tel qu’il a été défini implique ce cours sur les architectures matérielles (des processeurs) ne se veut (et ne pourrait l’être) ni magistral ni complet. Il existe sur le net pléthore de supports sur le sujet. Dans la part temporelle du bloc 3 (5 h) qui m’est allouée il n’est qu’un support aux TD et TPs que vous allez réaliser dans le cadre de cette formation académique. J’espère toutefois qu’il vous donnera l’envie d’aller plus loin sur cet aspect « bas niveau » de informatique sont les architectures matérielles des processeurs.

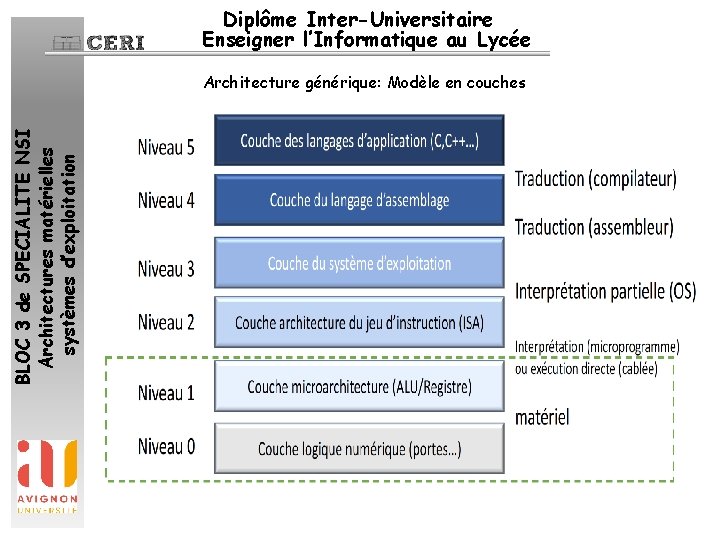

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Architecture générique: Modèle en couches

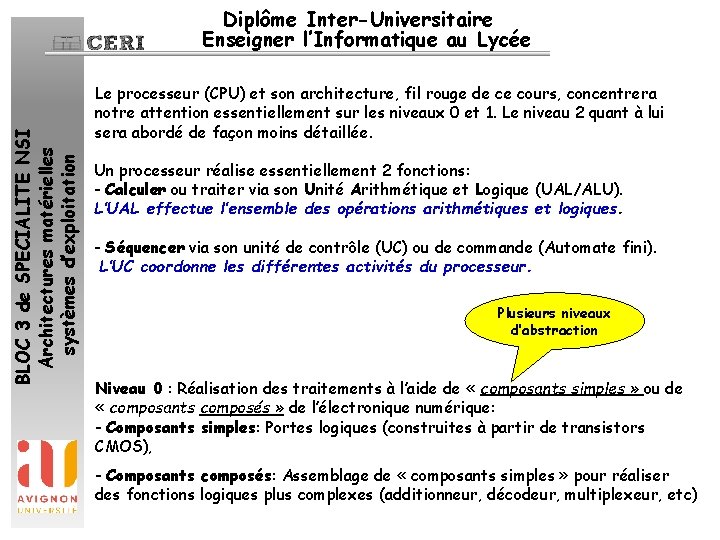

BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée Le processeur (CPU) et son architecture, fil rouge de ce cours, concentrera notre attention essentiellement sur les niveaux 0 et 1. Le niveau 2 quant à lui sera abordé de façon moins détaillée. Un processeur réalise essentiellement 2 fonctions: - Calculer ou traiter via son Unité Arithmétique et Logique (UAL/ALU). L’UAL effectue l’ensemble des opérations arithmétiques et logiques. - Séquencer via son unité de contrôle (UC) ou de commande (Automate fini). L’UC coordonne les différentes activités du processeur. Plusieurs niveaux d’abstraction Niveau 0 : Réalisation des traitements à l’aide de « composants simples » ou de « composants composés » de l’électronique numérique: - Composants simples: Portes logiques (construites à partir de transistors CMOS), - Composants composés: Assemblage de « composants simples » pour réaliser des fonctions logiques plus complexes (additionneur, décodeur, multiplexeur, etc)

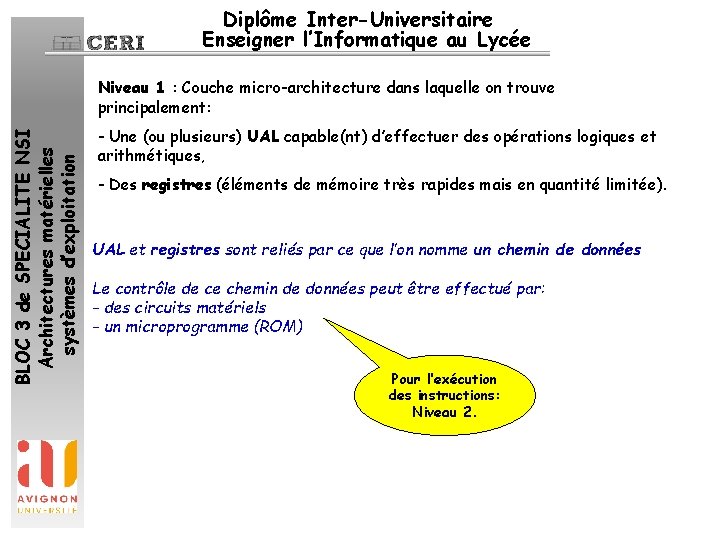

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Niveau 1 : Couche micro-architecture dans laquelle on trouve principalement: - Une (ou plusieurs) UAL capable(nt) d’effectuer des opérations logiques et arithmétiques, - Des registres (éléments de mémoire très rapides mais en quantité limitée). UAL et registres sont reliés par ce que l’on nomme un chemin de données Le contrôle de ce chemin de données peut être effectué par: - des circuits matériels - un microprogramme (ROM) Pour l’exécution des instructions: Niveau 2.

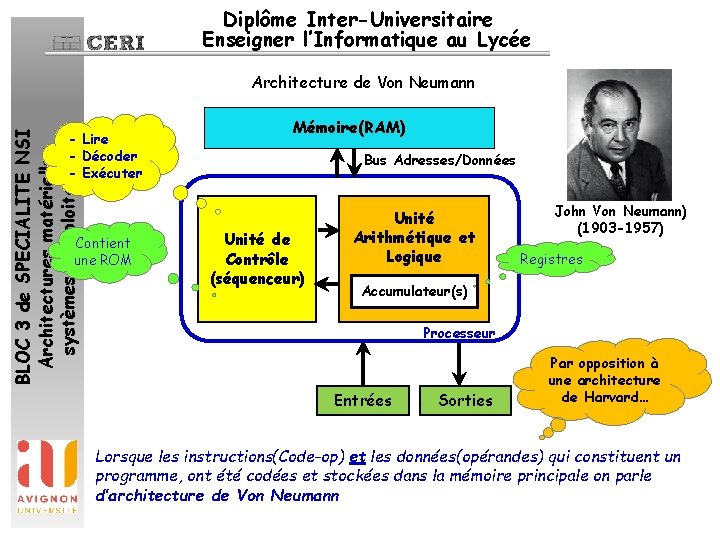

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Architecture de Von Neumann - Lire - Décoder - Exécuter Contient une ROM Mémoire(RAM) Bus Adresses/Données Unité de Contrôle (séquenceur) Unité Arithmétique et Logique John Von Neumann) (1903 -1957) Registres Accumulateur(s) Processeur Entrées Sorties Par opposition à une architecture de Harvard… Lorsque les instructions(Code-op) et les données(opérandes) qui constituent un programme, ont été codées et stockées dans la mémoire principale on parle d’architecture de Von Neumann

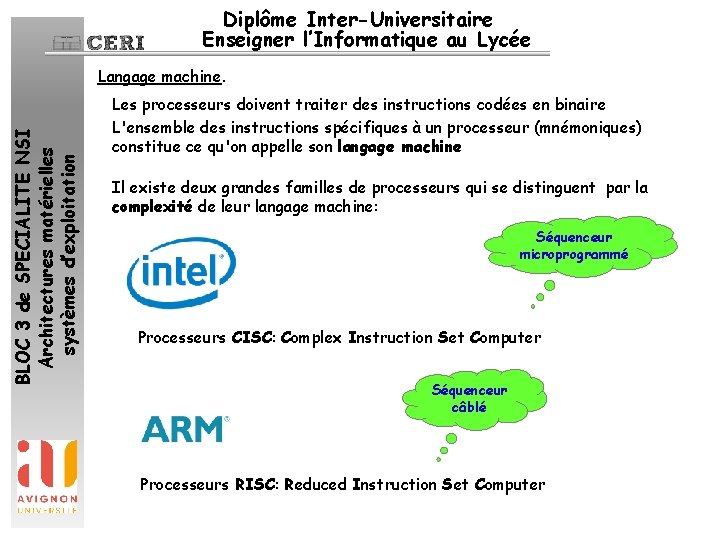

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Langage machine. Les processeurs doivent traiter des instructions codées en binaire L'ensemble des instructions spécifiques à un processeur (mnémoniques) constitue ce qu'on appelle son langage machine Il existe deux grandes familles de processeurs qui se distinguent par la complexité de leur langage machine: Séquenceur microprogrammé Processeurs CISC: Complex Instruction Set Computer Séquenceur câblé Processeurs RISC: Reduced Instruction Set Computer

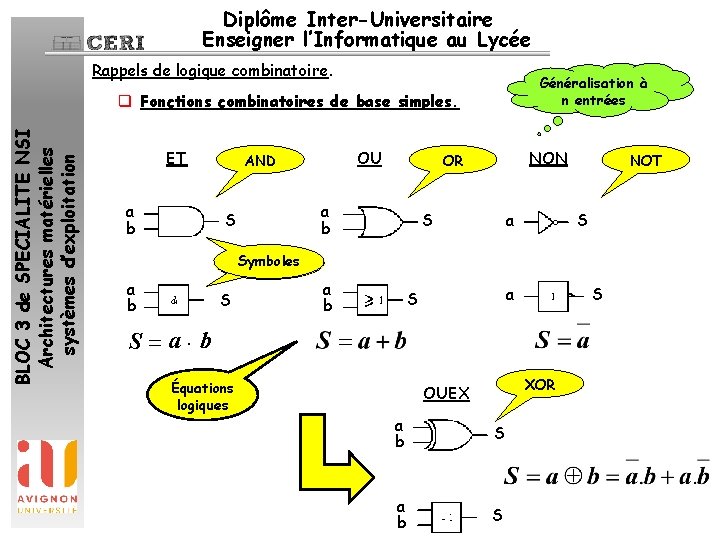

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée Rappels de logique combinatoire. Généralisation à n entrées BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation q Fonctions combinatoires de base simples. ET a b OU AND a b S NON OR S NOT S a Symboles a b S a b a S S S = a. b Équations logiques XOR OUEX a b S

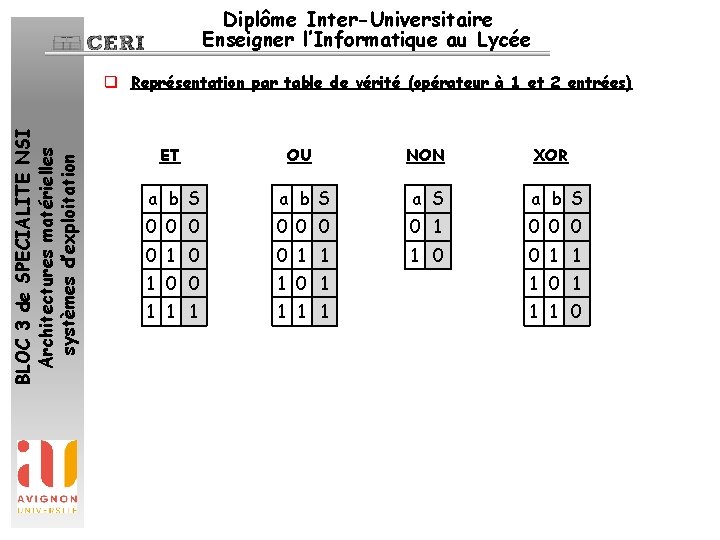

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation q Représentation par table de vérité (opérateur à 1 et 2 entrées) ET OU NON XOR a b S a S a b S 0 0 0 0 1 0 0 1 1 1 0 0 1 1 1 1 1 0

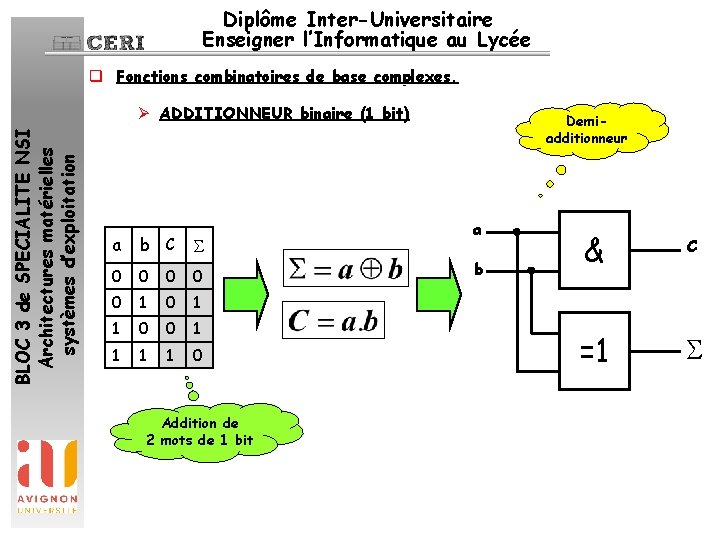

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée q Fonctions combinatoires de base complexes. BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Ø ADDITIONNEUR binaire (1 bit) a b C S 0 0 0 1 1 0 Addition de 2 mots de 1 bit Demiadditionneur a b & C =1 S

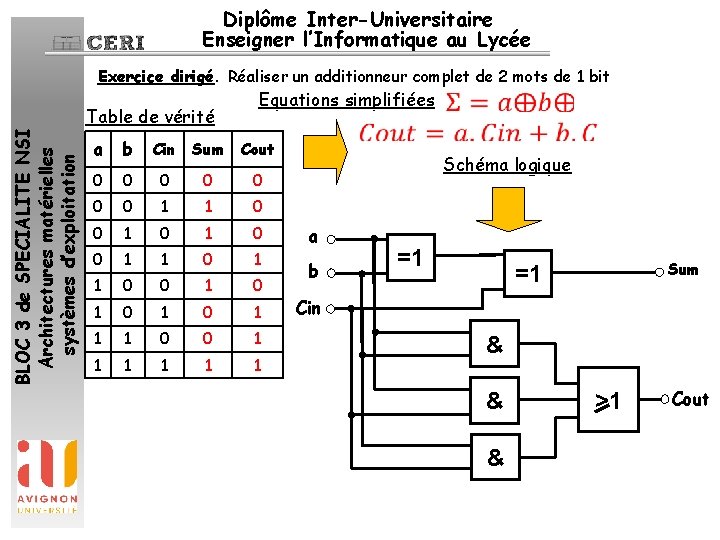

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Exercice dirigé. Réaliser un additionneur complet de 2 mots de 1 bit Table de vérité Equations simplifiées a b Cin Sum Cout 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1 a b Schéma logique =1 Sum =1 Cin & & & >1 Cout

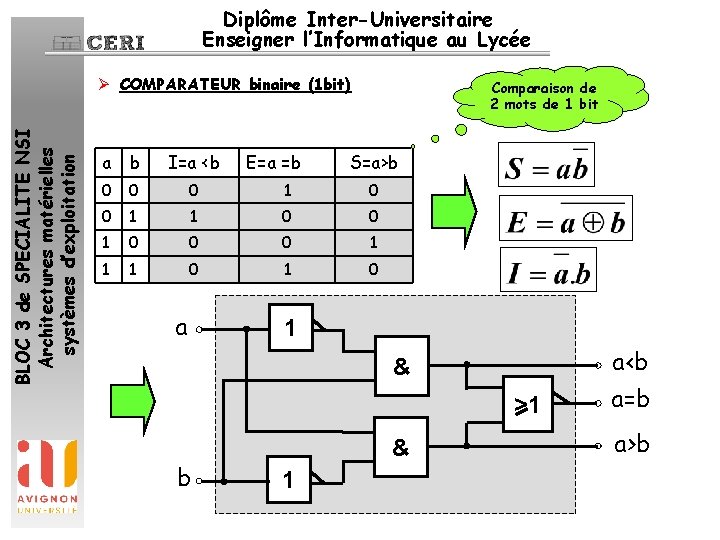

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Ø COMPARATEUR binaire (1 bit) a b I=a <b E=a =b Comparaison de 2 mots de 1 bit S=a>b 0 0 0 1 1 1 0 a 1 a<b & >1 b & 1 a=b a>b

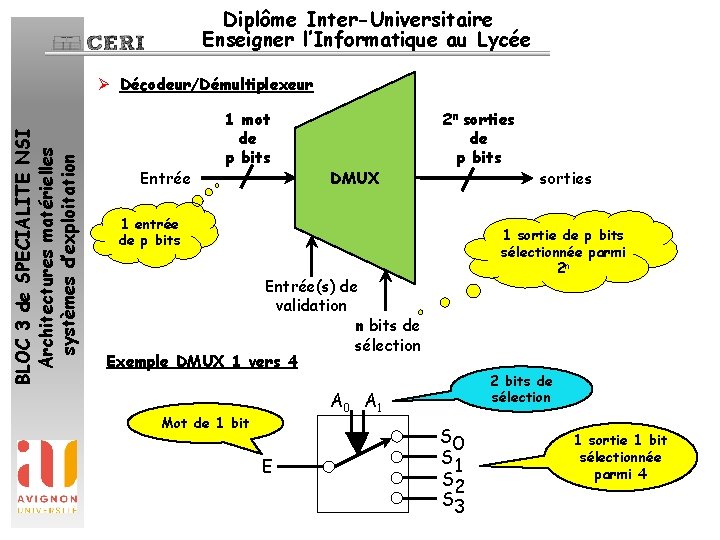

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Ø Décodeur/Démultiplexeur Entrée 1 mot de p bits DMUX 2 n sorties de p bits 1 entrée de p bits 1 sortie de p bits sélectionnée parmi 2 n Entrée(s) de validation n bits de sélection Exemple DMUX 1 vers 4 2 bits de sélection A 0 A 1 Mot de 1 bit E sorties S 0 S 1 S 2 S 3 1 sortie 1 bit sélectionnée parmi 4

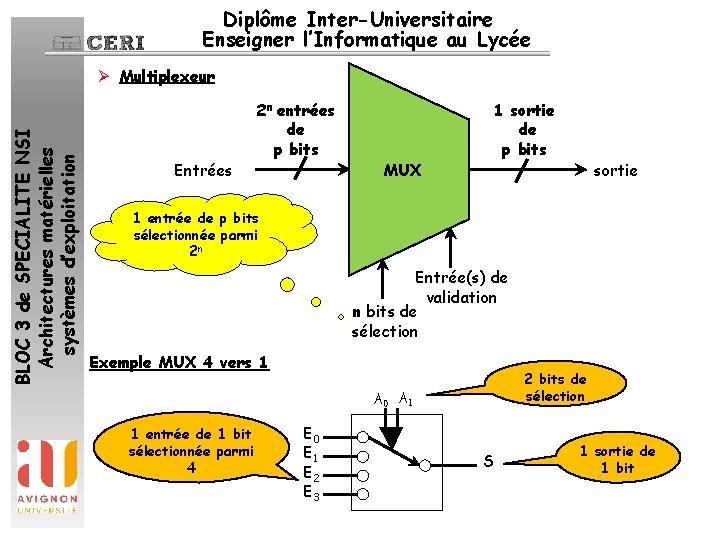

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Ø Multiplexeur Entrées 2 n entrées de p bits MUX 1 sortie de p bits sortie 1 entrée de p bits sélectionnée parmi 2 n Entrée(s) de validation n bits de sélection Exemple MUX 4 vers 1 2 bits de sélection A 0 A 1 1 entrée de 1 bit sélectionnée parmi 4 E 0 E 1 E 2 E 3 S 1 sortie de 1 bit

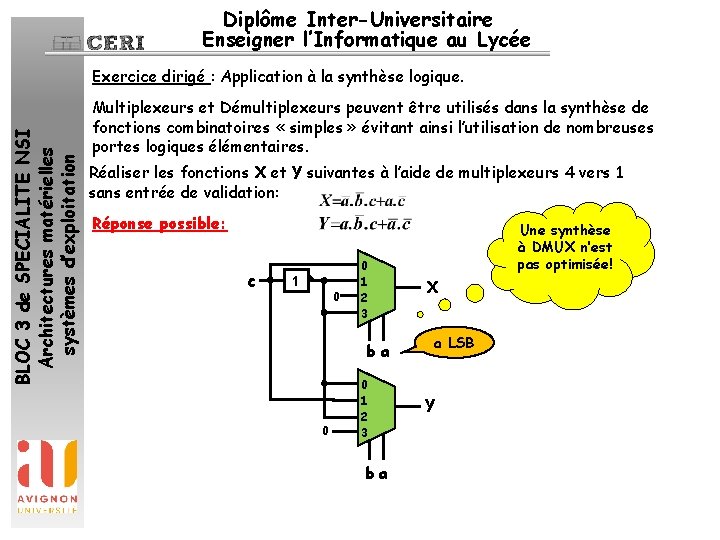

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Exercice dirigé : Application à la synthèse logique. Multiplexeurs et Démultiplexeurs peuvent être utilisés dans la synthèse de fonctions combinatoires « simples » évitant ainsi l’utilisation de nombreuses portes logiques élémentaires. Réaliser les fonctions X et Y suivantes à l’aide de multiplexeurs 4 vers 1 sans entrée de validation: Réponse possible: c 1 0 0 1 2 3 ba Une synthèse à DMUX n’est pas optimisée! X a LSB Y

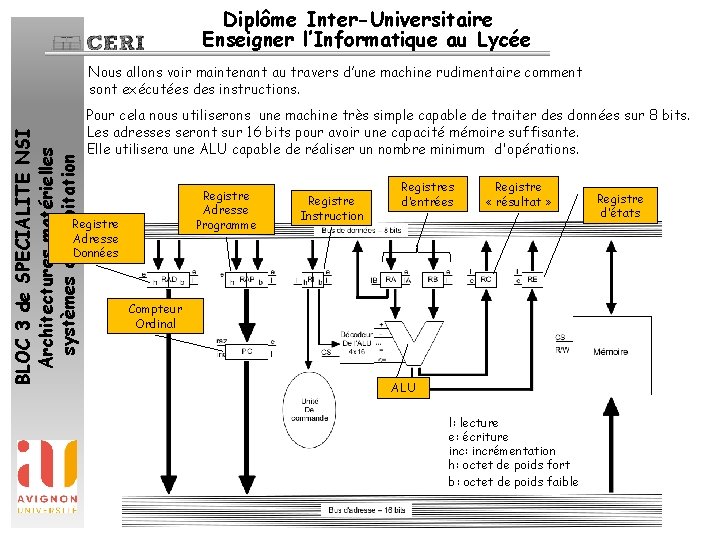

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Nous allons voir maintenant au travers d’une machine rudimentaire comment sont exécutées des instructions. Pour cela nous utiliserons une machine très simple capable de traiter des données sur 8 bits. Les adresses seront sur 16 bits pour avoir une capacité mémoire suffisante. Elle utilisera une ALU capable de réaliser un nombre minimum d'opérations. Registre Adresse Programme Registre Adresse Données Registre Instruction Registres d’entrées Registre « résultat » Compteur Ordinal ALU l: lecture e: écriture inc: incrémentation h: octet de poids fort b: octet de poids faible Registre d’états

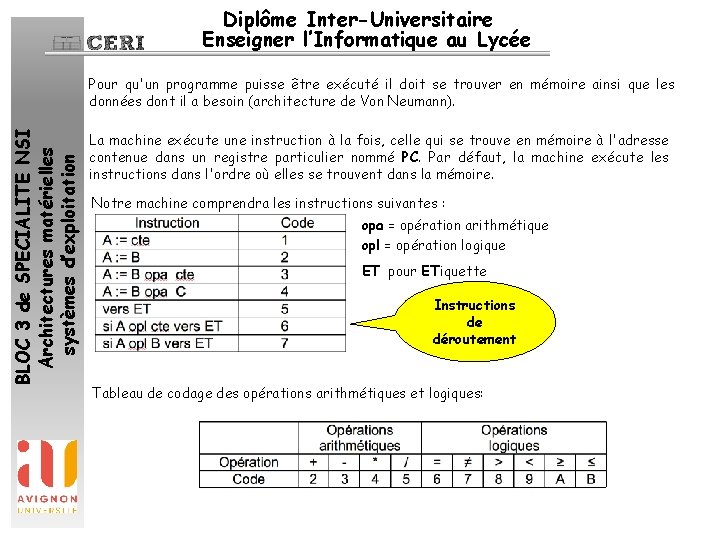

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Pour qu'un programme puisse être exécuté il doit se trouver en mémoire ainsi que les données dont il a besoin (architecture de Von Neumann). La machine exécute une instruction à la fois, celle qui se trouve en mémoire à l'adresse contenue dans un registre particulier nommé PC. Par défaut, la machine exécute les instructions dans l'ordre où elles se trouvent dans la mémoire. Notre machine comprendra les instructions suivantes : opa = opération arithmétique opl = opération logique ET pour ETiquette Instructions de déroutement Tableau de codage des opérations arithmétiques et logiques:

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée Codage des instructions BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Pour qu’un programme s’exécute, il doit se trouver en mémoire. La mémoire est composée de mots de 8 bits, le programme se décompose donc en une série de valeurs entières sur 8 bits. Notre machine possède : – 7 instructions, 3 bits suffisent à les coder, – 10 opérations, 4 bits suffisent à les coder. Au final nous utiliserons 1 octet pour coder l'instruction et l'opération associée: - 4 bits de poids forts coderont l’instruction - 4 bits de poids faibles coderont l’opération Exemple: A: =B opa cte * A : = B * cte sera codée 34 Codage des opérandes Les opérandes possibles pour les instructions de la machine sont de deux types : - des valeurs constantes sur 8 bits (occupent 1 octet), - des adresses (de variables ou de programme) sur 16 bits (occupent 2 octets). A noter: Une étiquette (ET) occupe donc 2 octets.

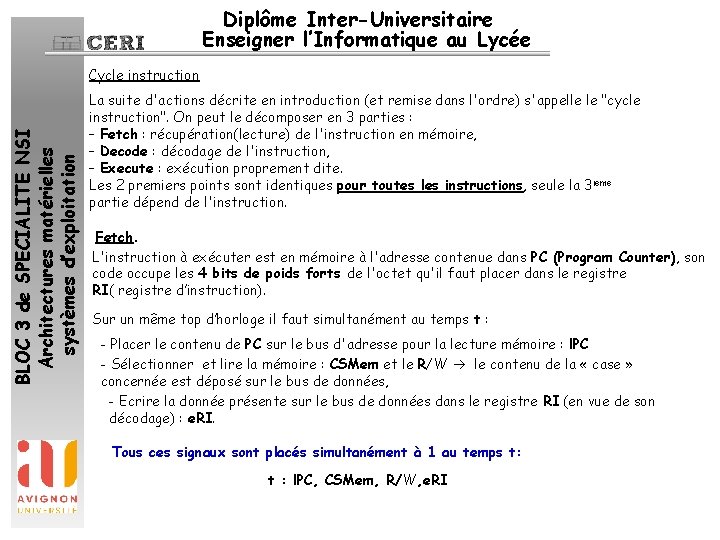

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Cycle instruction La suite d'actions décrite en introduction (et remise dans l'ordre) s'appelle le "cycle instruction". On peut le décomposer en 3 parties : – Fetch : récupération(lecture) de l'instruction en mémoire, – Decode : décodage de l'instruction, – Execute : exécution proprement dite. Les 2 premiers points sont identiques pour toutes les instructions, seule la 3 ieme partie dépend de l'instruction. Fetch. L'instruction à exécuter est en mémoire à l'adresse contenue dans PC (Program Counter), son code occupe les 4 bits de poids forts de l'octet qu'il faut placer dans le registre RI( registre d’instruction). Sur un même top d’horloge il faut simultanément au temps t : - Placer le contenu de PC sur le bus d'adresse pour la lecture mémoire : l. PC - Sélectionner et lire la mémoire : CSMem et le R/W le contenu de la « case » concernée est déposé sur le bus de données, - Ecrire la donnée présente sur le bus de données dans le registre RI (en vue de son décodage) : e. RI. Tous ces signaux sont placés simultanément à 1 au temps t: t : l. PC, CSMem, R/W, e. RI

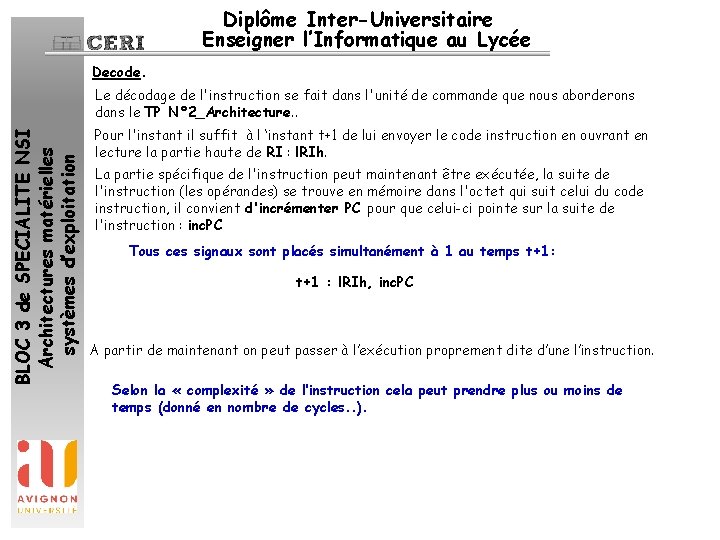

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée Decode. BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Le décodage de l'instruction se fait dans l'unité de commande que nous aborderons dans le TP N° 2_Architecture. . Pour l'instant il suffit à l ‘instant t+1 de lui envoyer le code instruction en ouvrant en lecture la partie haute de RI : l. RIh. La partie spécifique de l'instruction peut maintenant être exécutée, la suite de l'instruction (les opérandes) se trouve en mémoire dans l'octet qui suit celui du code instruction, il convient d'incrémenter PC pour que celui-ci pointe sur la suite de l'instruction : inc. PC Tous ces signaux sont placés simultanément à 1 au temps t+1: t+1 : l. RIh, inc. PC A partir de maintenant on peut passer à l’exécution proprement dite d’une l’instruction. Selon la « complexité » de l’instruction cela peut prendre plus ou moins de temps (donné en nombre de cycles. . ).

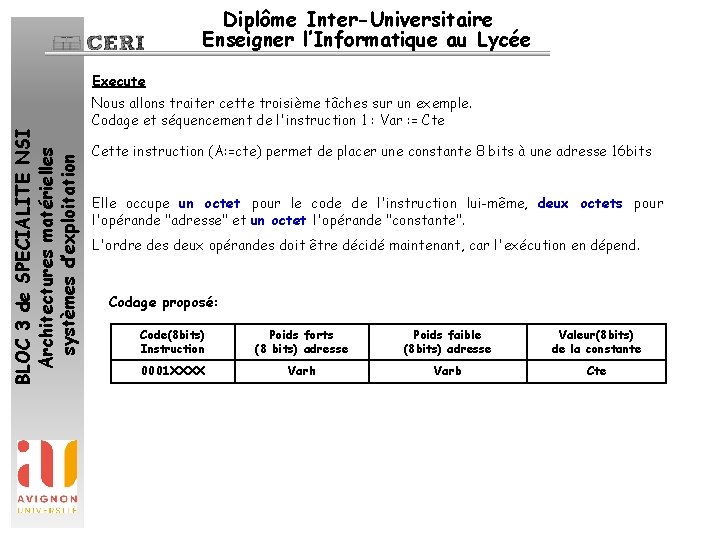

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Execute Nous allons traiter cette troisième tâches sur un exemple. Codage et séquencement de l'instruction 1 : Var : = Cte Cette instruction (A: =cte) permet de placer une constante 8 bits à une adresse 16 bits Elle occupe un octet pour le code de l'instruction lui-même, deux octets pour l'opérande "adresse" et un octet l'opérande "constante". L'ordre des deux opérandes doit être décidé maintenant, car l'exécution en dépend. Codage proposé: Code(8 bits) Instruction Poids forts (8 bits) adresse Poids faible (8 bits) adresse Valeur(8 bits) de la constante 0001 XXXX Varh Varb Cte

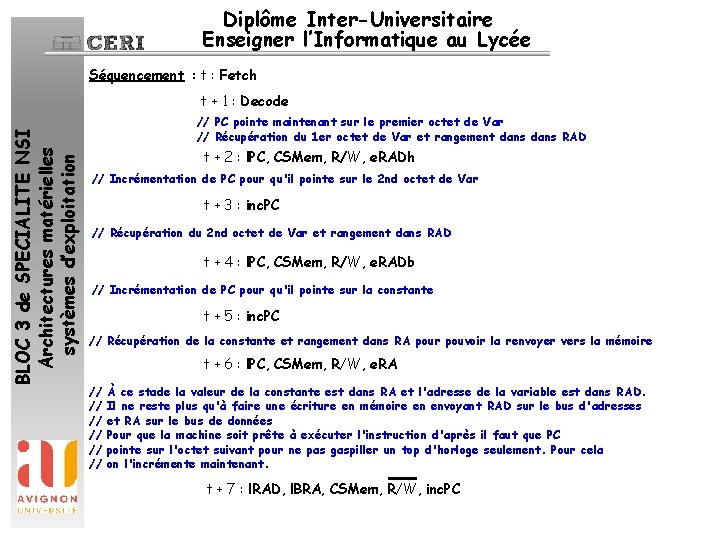

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée Séquencement : Fetch BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation t + 1 : Decode // PC pointe maintenant sur le premier octet de Var // Récupération du 1 er octet de Var et rangement dans RAD t + 2 : l. PC, CSMem, R/W, e. RADh // Incrémentation de PC pour qu'il pointe sur le 2 nd octet de Var t + 3 : inc. PC // Récupération du 2 nd octet de Var et rangement dans RAD t + 4 : l. PC, CSMem, R/W, e. RADb // Incrémentation de PC pour qu'il pointe sur la constante t + 5 : inc. PC // Récupération de la constante et rangement dans RA pour pouvoir la renvoyer vers la mémoire t + 6 : l. PC, CSMem, R/W, e. RA // // // À ce stade la valeur de la constante est dans RA et l'adresse de la variable est dans RAD. Il ne reste plus qu'à faire une écriture en mémoire en envoyant RAD sur le bus d'adresses et RA sur le bus de données Pour que la machine soit prête à exécuter l'instruction d'après il faut que PC pointe sur l'octet suivant pour ne pas gaspiller un top d'horloge seulement. Pour cela on l'incrémente maintenant. t + 7 : l. RAD, l. BRA, CSMem, R/W, inc. PC

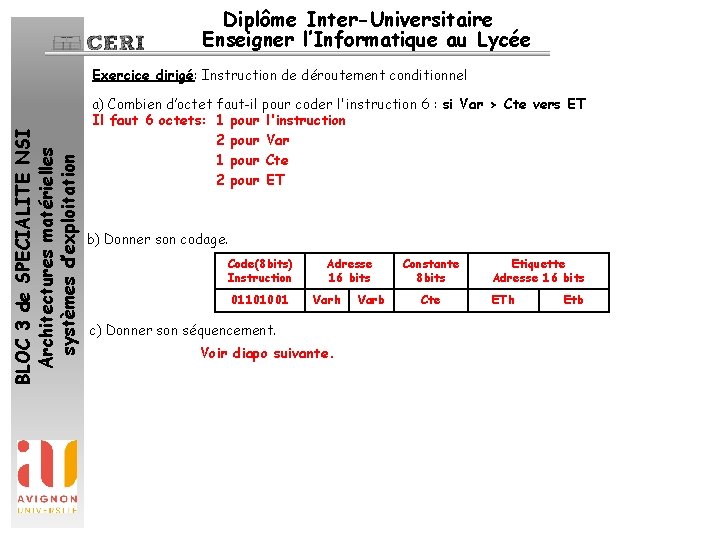

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Exercice dirigé: Instruction de déroutement conditionnel a) Combien d’octet faut-il pour coder l'instruction 6 : si Var > Cte vers ET Il faut 6 octets: 1 pour l'instruction 2 pour Var 1 pour Cte 2 pour ET b) Donner son codage. Code(8 bits) Instruction 01101001 Adresse 16 bits Varh c) Donner son séquencement. Voir diapo suivante. Varb Constante 8 bits Cte Etiquette Adresse 16 bits ETh Etb

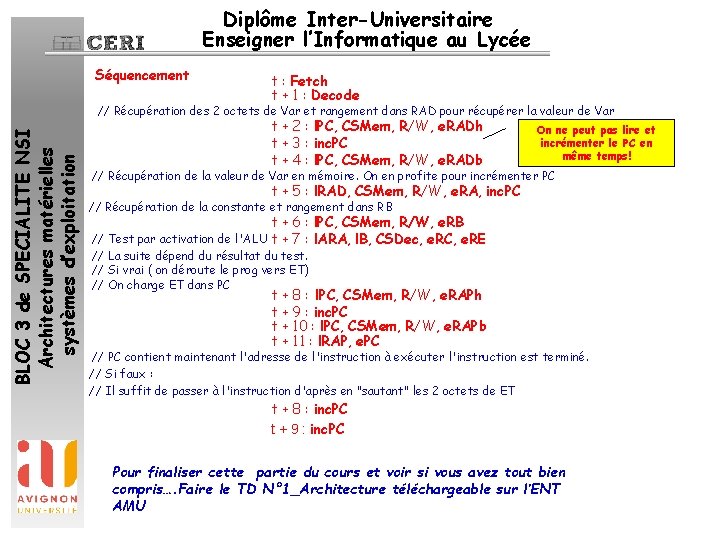

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée Séquencement t : Fetch t + 1 : Decode BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation // Récupération des 2 octets de Var et rangement dans RAD pour récupérer la valeur de Var t + 2 : l. PC, CSMem, R/W, e. RADh t + 3 : inc. PC t + 4 : l. PC, CSMem, R/W, e. RADb On ne peut pas lire et incrémenter le PC en même temps! // Récupération de la valeur de Var en mémoire. On en profite pour incrémenter PC t + 5 : l. RAD, CSMem, R/W, e. RA, inc. PC // Récupération de la constante et rangement dans RB t + 6 : l. PC, CSMem, R/W, e. RB // Test par activation de l'ALU t + 7 : l. ARA, l. B, CSDec, e. RC, e. RE // La suite dépend du résultat du test. // Si vrai ( on déroute le prog vers ET) // On charge ET dans PC t + 8 : l. PC, CSMem, R/W, e. RAPh t + 9 : inc. PC t + 10 : l. PC, CSMem, R/W, e. RAPb t + 11 : l. RAP, e. PC // PC contient maintenant l'adresse de l'instruction à exécuter l'instruction est terminé. // Si faux : // Il suffit de passer à l'instruction d'après en "sautant" les 2 octets de ET t + 8 : inc. PC t + 9 : inc. PC Pour finaliser cette partie du cours et voir si vous avez tout bien compris…. Faire le TD N° 1_Architecture téléchargeable sur l’ENT AMU

Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Mise œuvre Je vous propose 2 TPs pour bien comprendre le fonctionnement d’un processeur. Ces TPs seront réalisés sous Logisim version 2. 7. 2 ou 2. 7. 1 Attention il existe quelques différences mais sans trop de conséquence pour les TPs. Il existe une 3 ième version Logisim-Evolution qui va beaucoup plus loin ( FPGA, Chronogramme, etc), mais ça c’est pour une autre aventure dans le monde des simulateurs numériques… Le TP N° 1_Architecture vous permettra de prendre en mains assez rapidement ce logiciel de simulation multiplateformes et gratuit. Vous concevrez Une petite ALU 8 bits. Le TP N° 2_Architecture vous permettra d’associer à notre ALU 8 bits tous les opérateurs de la logique combinatoire (Multiplexeur, Décodeur, ROM) et séquentielle(Registres, Compteur) pour réaliser un petit processeur 8 bits.

BLOC 3 de SPECIALITE NSI Architectures matérielles systèmes d’exploitation Diplôme Inter-Universitaire Enseigner l’Informatique au Lycée

- Slides: 26