Teised riistvara kirjelduskeeled z L 11 L 12

![Verilog y Andmetüübid integer i, j; real f, d; wire [7: 0] bus; // Verilog y Andmetüübid integer i, j; real f, d; wire [7: 0] bus; //](https://slidetodoc.com/presentation_image_h/1ee5548a2e6a467f9ebe62b705a7fba0/image-10.jpg)

- Slides: 30

Teised riistvara kirjelduskeeled z L 11, L 12. Riistvara kirjelduskeel VHDL z L 13. Mäluga süsteemid VHDL-s z L 14. VHDL-i paketid ja teegid Sünteesitav VHDL z L 15. Teised riistvara kirjelduskeeled © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 1

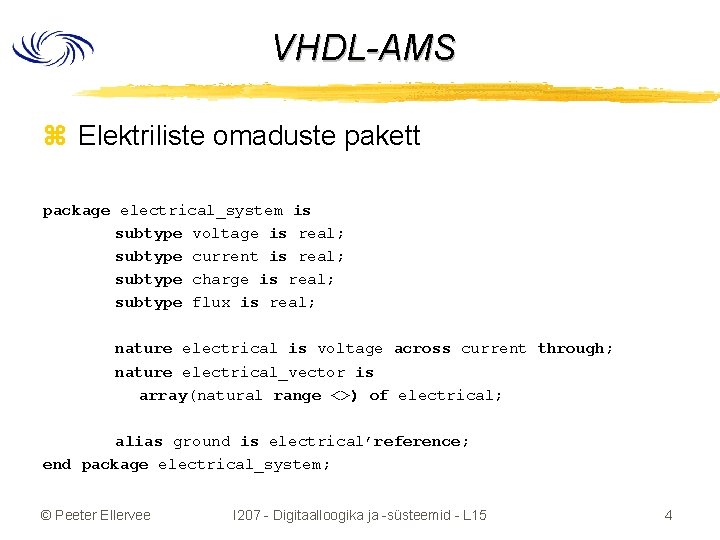

VHDL-AMS z VHDL-AMS - Analog & Mixed Signal extensions z IEEE Standard 1076. 1 z VHDL (IEEE Standard 1076 -1993) laiendus z Matemaatiline alus y Analoogi (pidevalt muutuv osa) kirjeldavad algebralised differentsiaalvõrrandid (differential algebraic equations – DAEs) y Võrrandisüsteemi F(x, dx/dt)=0 lahendamine numbriliselt x x – tundmatute vektor x F – avaldiste vektor © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 2

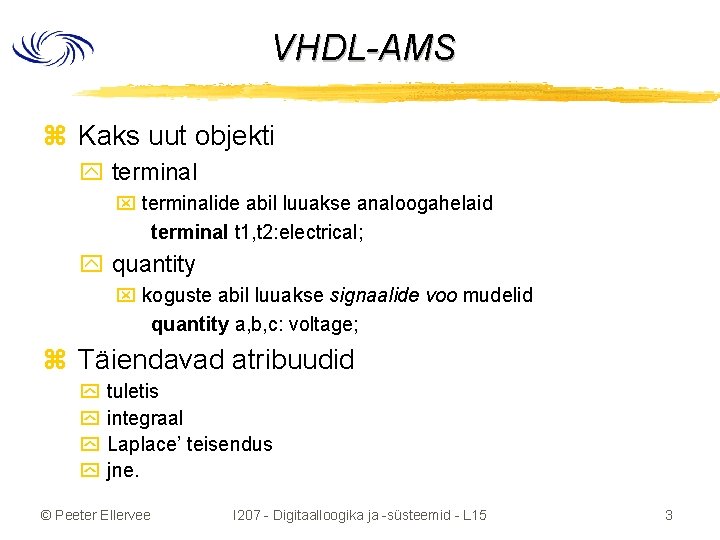

VHDL-AMS z Kaks uut objekti y terminal x terminalide abil luuakse analoogahelaid terminal t 1, t 2: electrical; y quantity x koguste abil luuakse signaalide voo mudelid quantity a, b, c: voltage; z Täiendavad atribuudid y tuletis y integraal y Laplace’ teisendus y jne. © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 3

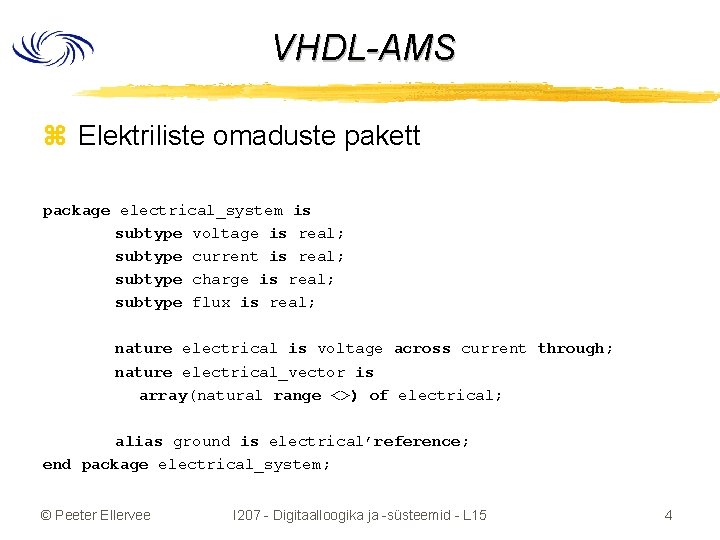

VHDL-AMS z Elektriliste omaduste pakett package electrical_system is subtype voltage is real; subtype current is real; subtype charge is real; subtype flux is real; nature electrical is voltage across current through; nature electrical_vector is array(natural range <>) of electrical; alias ground is electrical’reference; end package electrical_system; © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 4

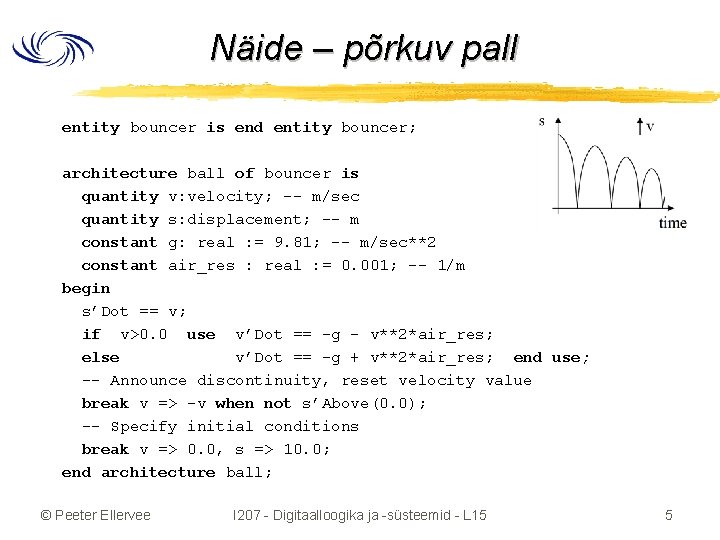

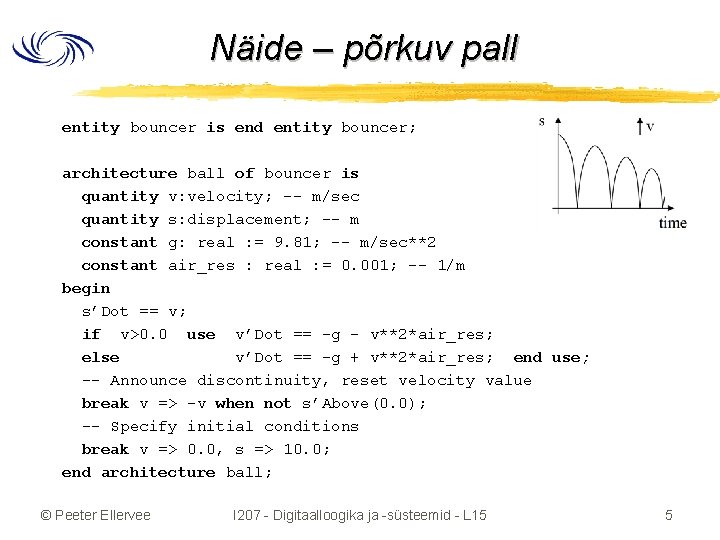

Näide – põrkuv pall entity bouncer is end entity bouncer; architecture ball of bouncer is quantity v: velocity; -- m/sec quantity s: displacement; -- m constant g: real : = 9. 81; -- m/sec**2 constant air_res : real : = 0. 001; -- 1/m begin s’Dot == v; if v>0. 0 use v’Dot == -g - v**2*air_res; else v’Dot == -g + v**2*air_res; end use; -- Announce discontinuity, reset velocity value break v => -v when not s’Above(0. 0); -- Specify initial conditions break v => 0. 0, s => 10. 0; end architecture ball; © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 5

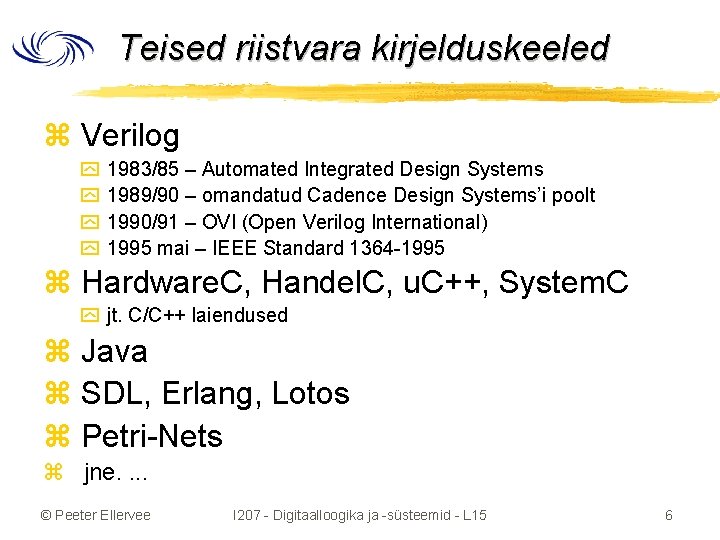

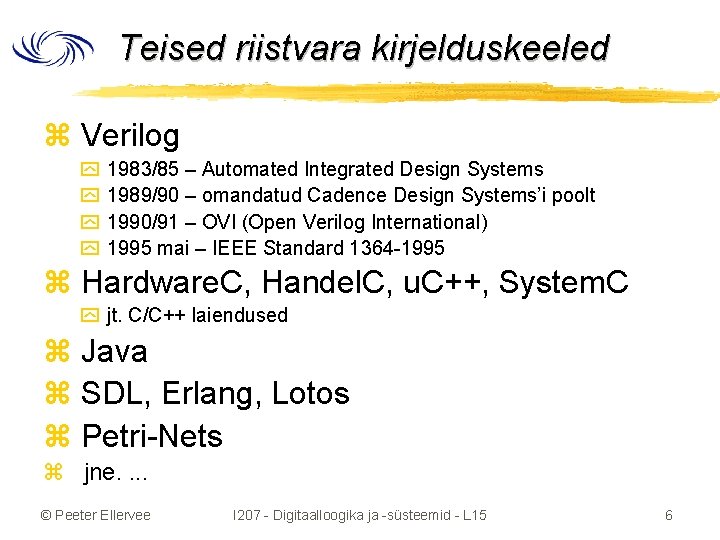

Teised riistvara kirjelduskeeled z Verilog y 1983/85 – Automated Integrated Design Systems y 1989/90 – omandatud Cadence Design Systems’i poolt y 1990/91 – OVI (Open Verilog International) y 1995 mai – IEEE Standard 1364 -1995 z Hardware. C, Handel. C, u. C++, System. C y jt. C/C++ laiendused z Java z SDL, Erlang, Lotos z Petri-Nets z jne. . © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 6

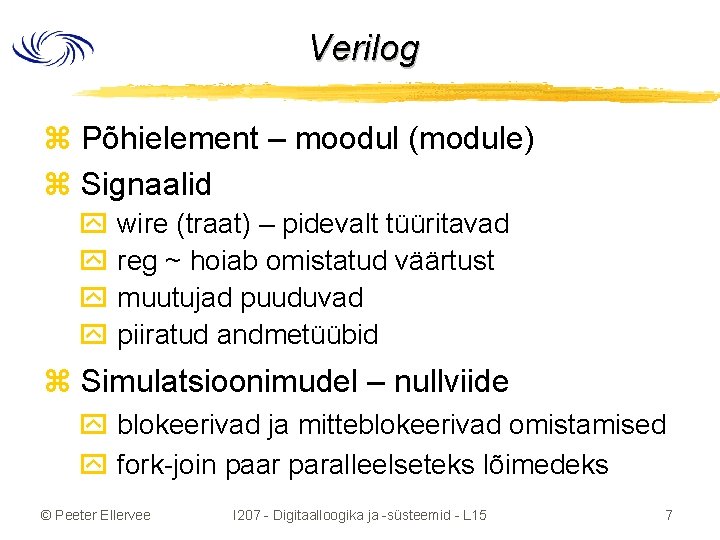

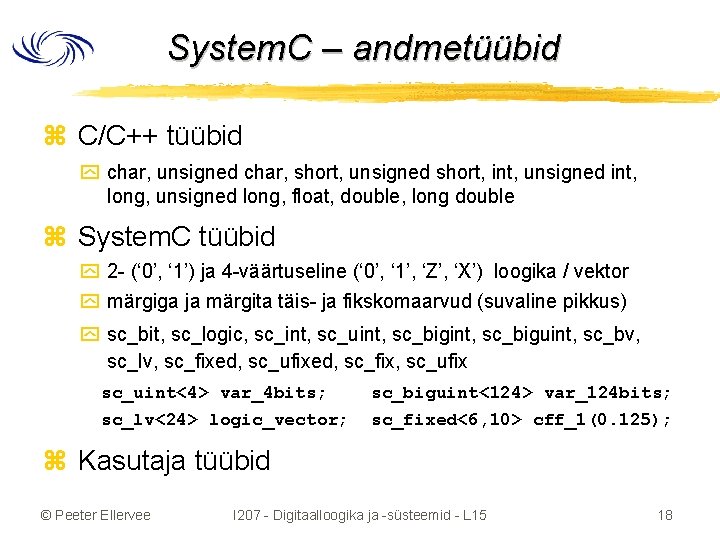

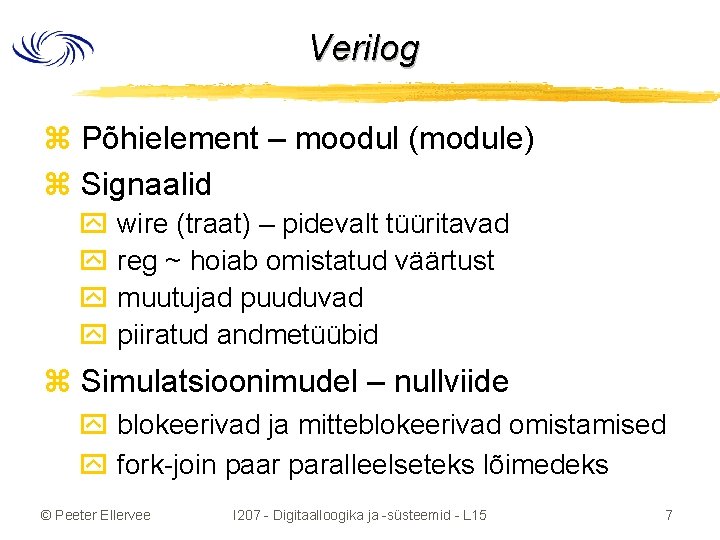

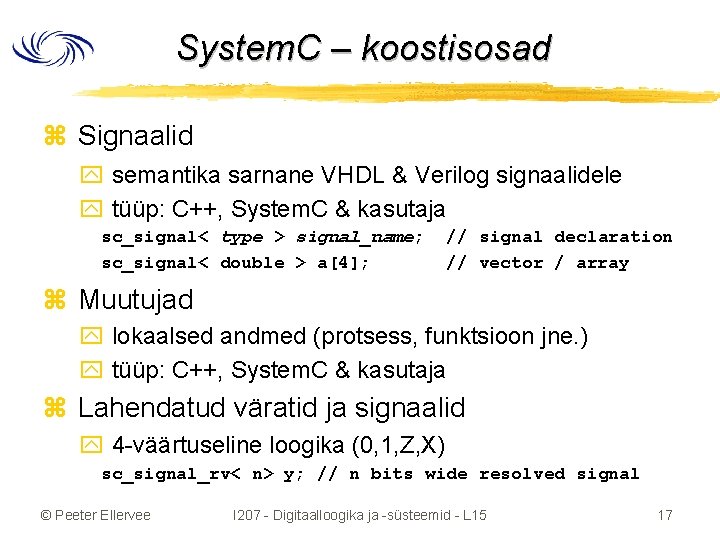

Verilog z Põhielement – moodul (module) z Signaalid y wire (traat) – pidevalt tüüritavad y reg ~ hoiab omistatud väärtust y muutujad puuduvad y piiratud andmetüübid z Simulatsioonimudel – nullviide y blokeerivad ja mitteblokeerivad omistamised y fork-join paar paralleelseteks lõimedeks © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 7

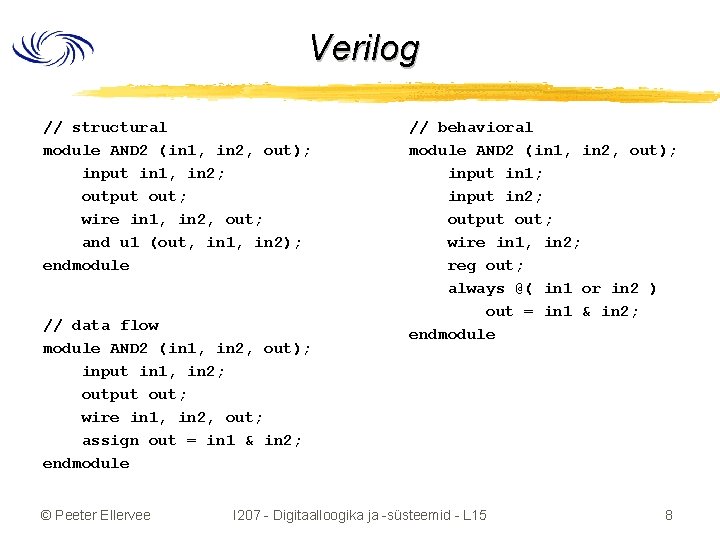

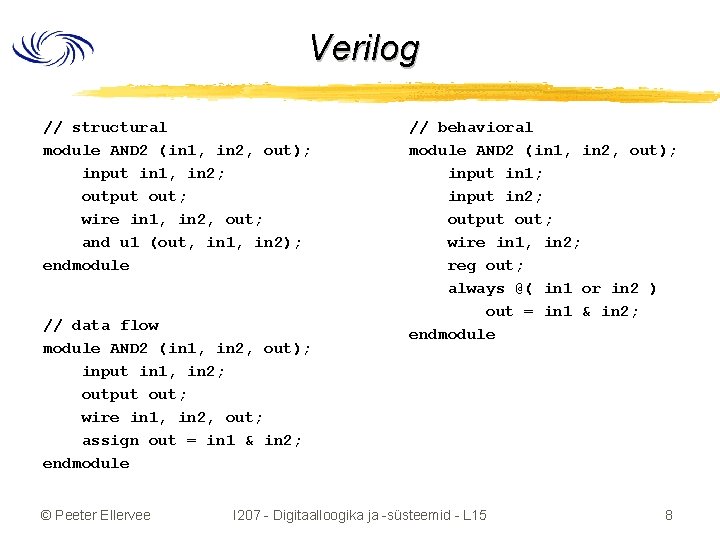

Verilog // structural module AND 2 (in 1, in 2, out); input in 1, in 2; output out; wire in 1, in 2, out; and u 1 (out, in 1, in 2); endmodule // data flow module AND 2 (in 1, in 2, out); input in 1, in 2; output out; wire in 1, in 2, out; assign out = in 1 & in 2; endmodule © Peeter Ellervee // behavioral module AND 2 (in 1, in 2, out); input in 1; input in 2; output out; wire in 1, in 2; reg out; always @( in 1 or in 2 ) out = in 1 & in 2; endmodule I 207 - Digitaalloogika ja -süsteemid - L 15 8

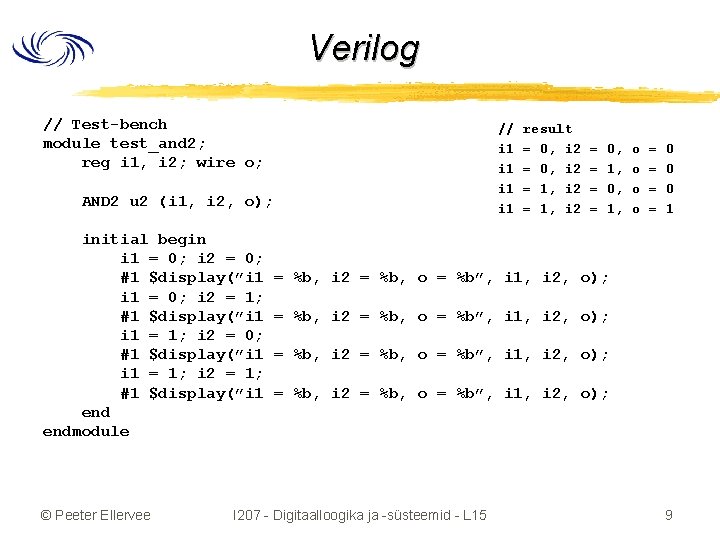

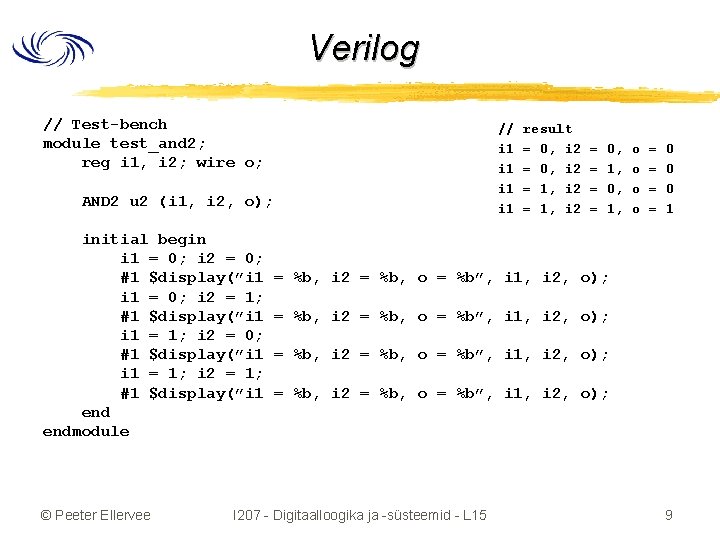

Verilog // Test-bench module test_and 2; reg i 1, i 2; wire o; AND 2 u 2 (i 1, i 2, o); // result i 1 = 0, i 2 = 0, o = 0 i 1 = 0, i 2 = 1, o = 0 i 1 = 1, i 2 = 0, o = 0 i 1 = 1, i 2 = 1, o = 1 initial begin i 1 = 0; i 2 = 0; #1 $display(”i 1 = %b, i 2 = %b, o = %b”, i 1, i 2, o); i 1 = 0; i 2 = 1; #1 $display(”i 1 = %b, i 2 = %b, o = %b”, i 1, i 2, o); i 1 = 1; i 2 = 0; #1 $display(”i 1 = %b, i 2 = %b, o = %b”, i 1, i 2, o); i 1 = 1; i 2 = 1; #1 $display(”i 1 = %b, i 2 = %b, o = %b”, i 1, i 2, o); endmodule © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 9

![Verilog y Andmetüübid integer i j real f d wire 7 0 bus Verilog y Andmetüübid integer i, j; real f, d; wire [7: 0] bus; //](https://slidetodoc.com/presentation_image_h/1ee5548a2e6a467f9ebe62b705a7fba0/image-10.jpg)

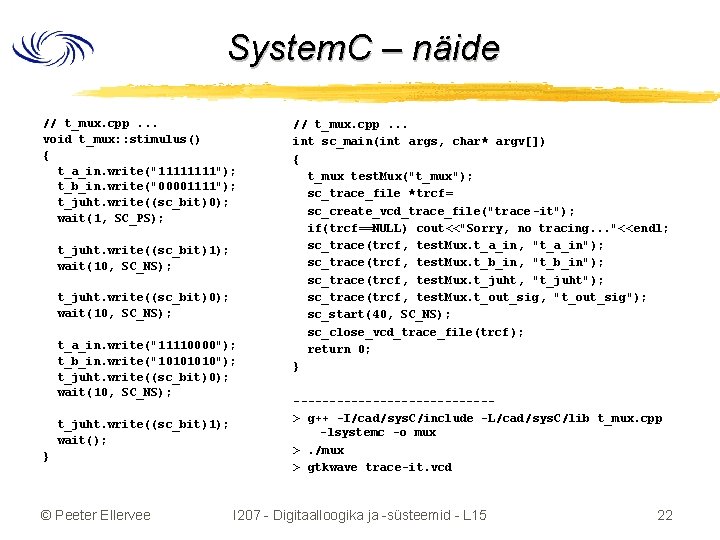

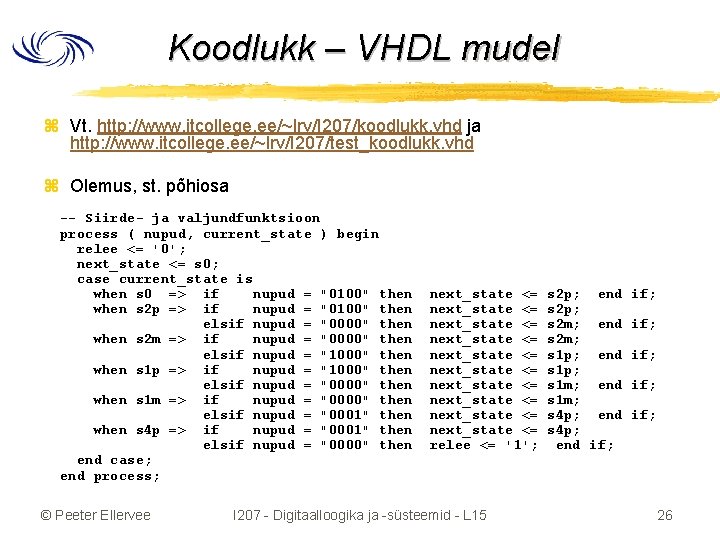

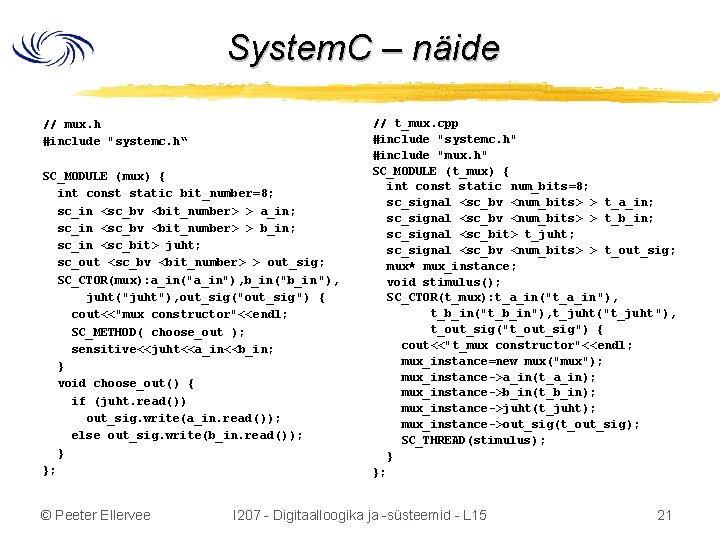

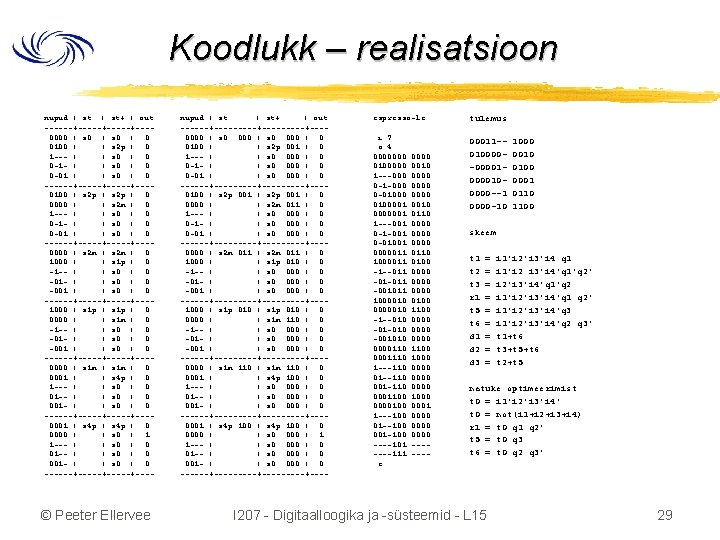

Verilog y Andmetüübid integer i, j; real f, d; wire [7: 0] bus; // 1 x 8 bits reg [0: 15] word; // 1 x 16 bits reg arr[0: 15]; // 16 x 1 bits reg [7: 0] mem[0: 127]; // 128 x 8 bits event trigger, clock_high; time t_setup, t_hold; parameter width=8; parameter width 2=width*2; wire [width-1: 0] ww; // The following are illegal wire w[0: 15]; // No arrays wire [3: 0] a, [7: 0] b; // Only one width per decl. © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 10

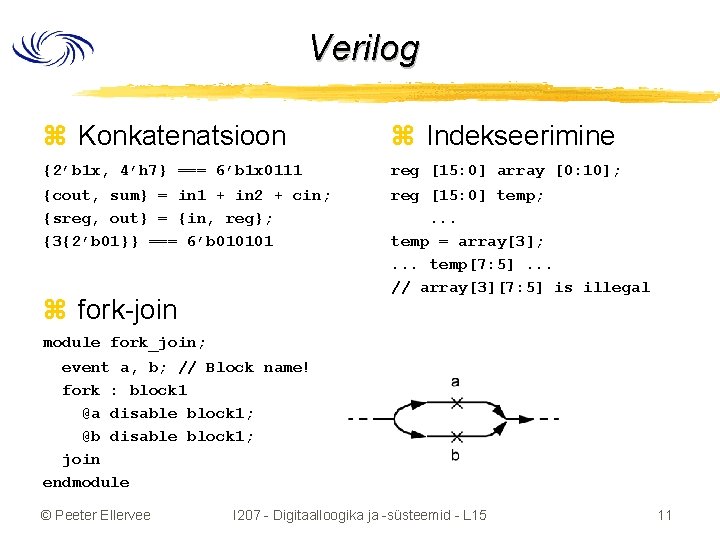

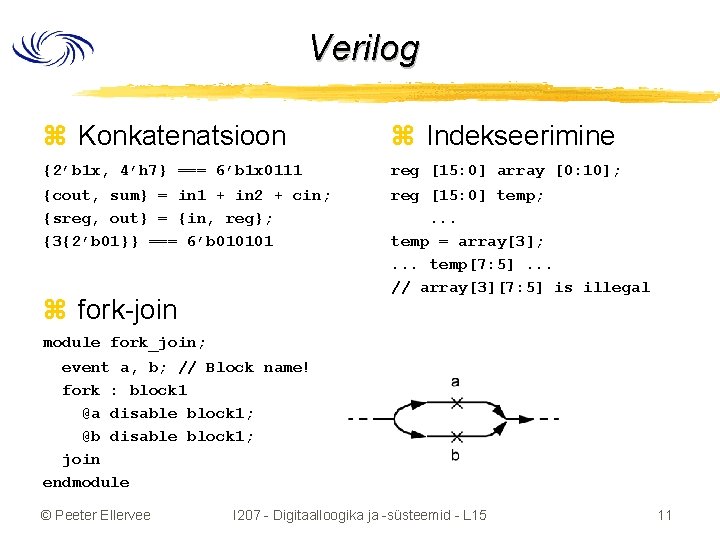

Verilog z Konkatenatsioon z Indekseerimine {2’b 1 x, 4’h 7} === 6’b 1 x 0111 reg [15: 0] array [0: 10]; {cout, sum} = in 1 + in 2 + cin; {sreg, out} = {in, reg}; {3{2’b 01}} === 6’b 010101 reg [15: 0] temp; . . . temp = array[3]; . . . temp[7: 5]. . . // array[3][7: 5] is illegal z fork-join module fork_join; event a, b; // Block name! fork : block 1 @a disable block 1; @b disable block 1; join endmodule © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 11

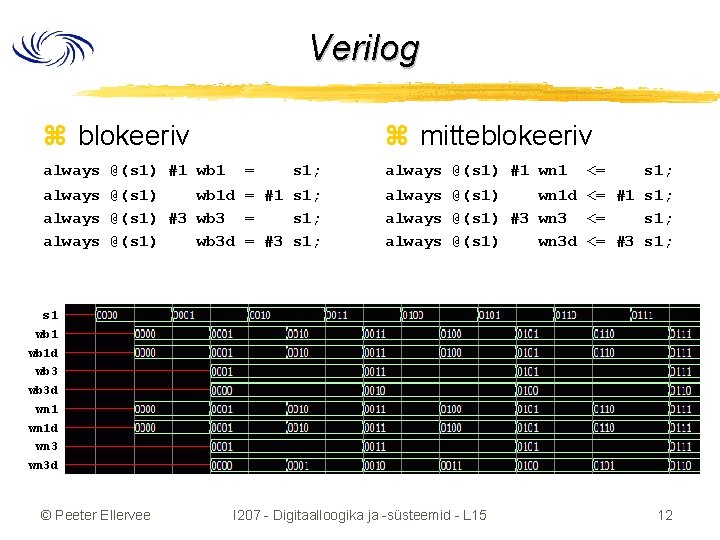

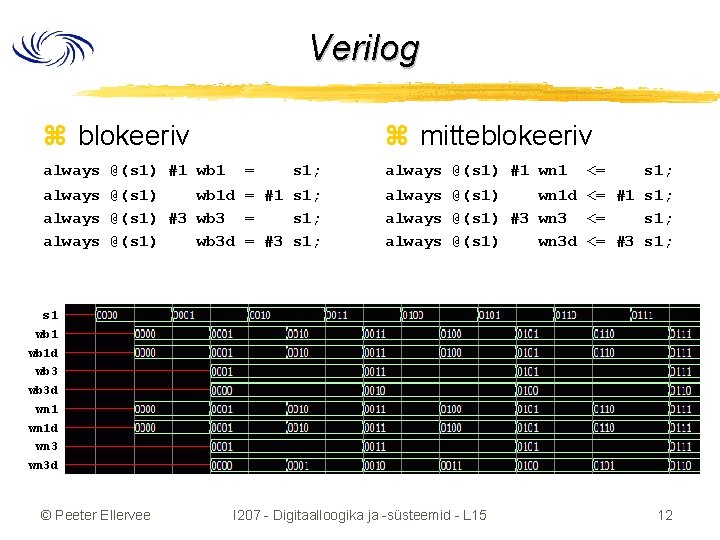

Verilog z blokeeriv z mitteblokeeriv always @(s 1) #1 wb 1 = s 1; always @(s 1) #1 wn 1 <= s 1; always @(s 1) wb 1 d = #1 s 1; always @(s 1) #3 wb 3 = s 1; always @(s 1) wb 3 d = #3 s 1; always @(s 1) wn 1 d <= #1 s 1; always @(s 1) #3 wn 3 <= s 1; always @(s 1) wn 3 d <= #3 s 1; s 1 wb 1 d wb 3 d wn 1 d wn 3 d © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 12

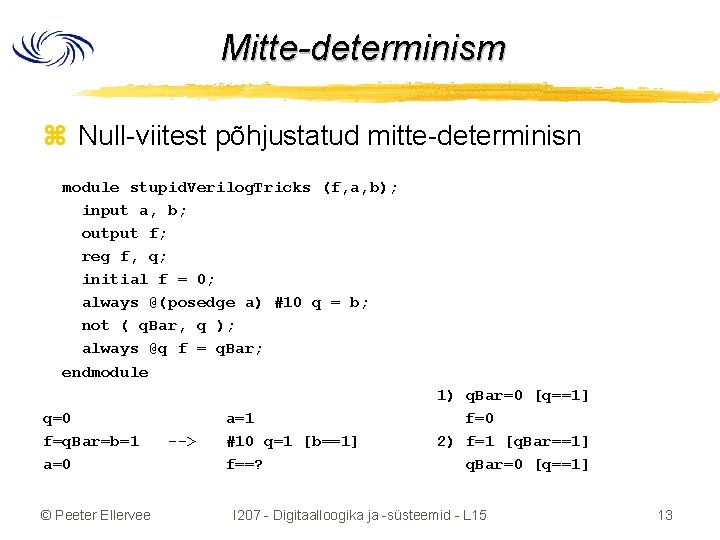

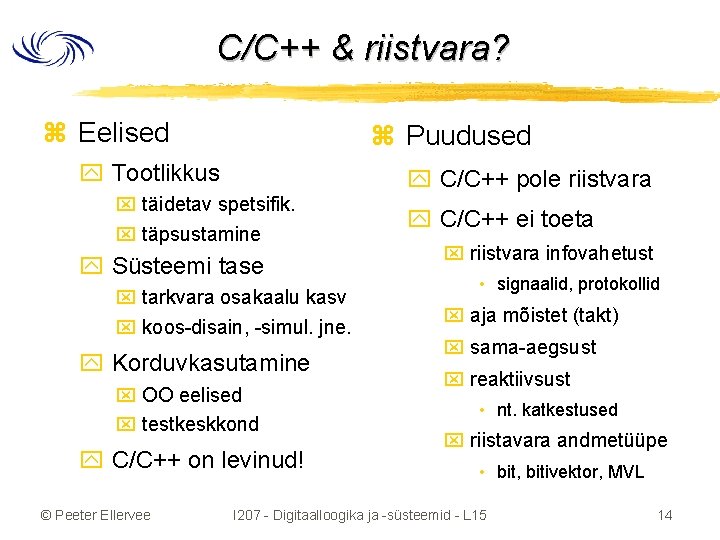

Mitte-determinism z Null-viitest põhjustatud mitte-determinisn module stupid. Verilog. Tricks (f, a, b); input a, b; output f; reg f, q; initial f = 0; always @(posedge a) #10 q = b; not ( q. Bar, q ); always @q f = q. Bar; endmodule 1) q. Bar=0 [q==1] q=0 a=1 f=0 f=q. Bar=b=1 --> #10 q=1 [b==1] 2) f=1 [q. Bar==1] a=0 f==? q. Bar=0 [q==1] © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 13

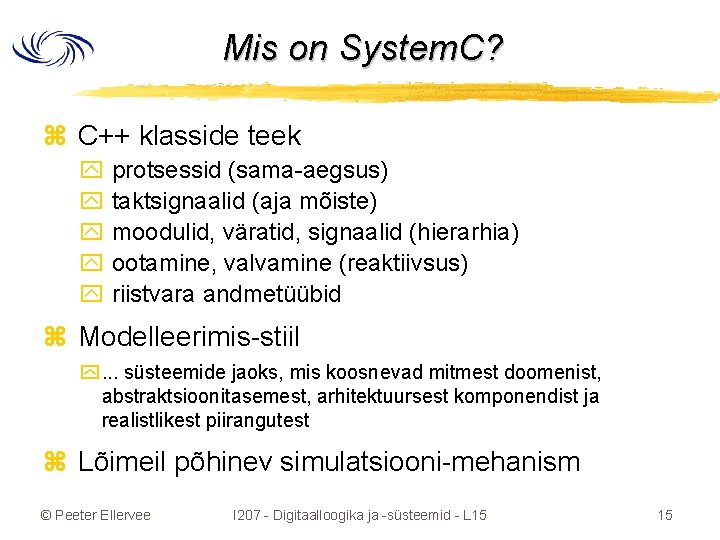

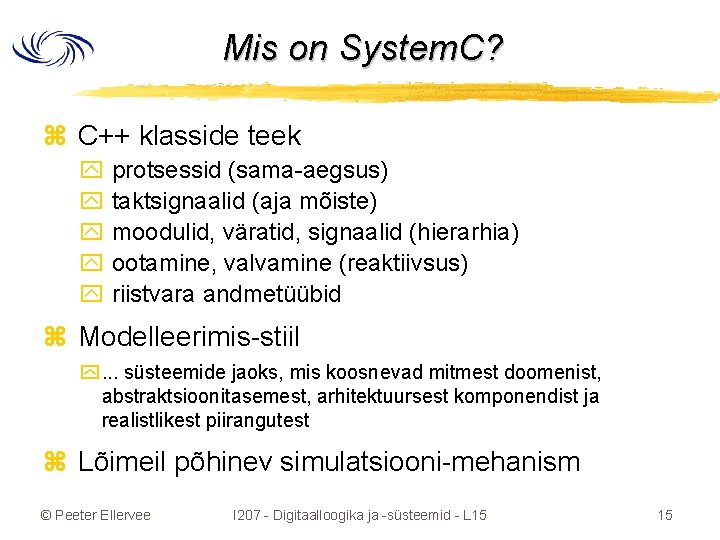

C/C++ & riistvara? z Eelised z Puudused y Tootlikkus y C/C++ pole riistvara x täidetav spetsifik. x täpsustamine y Süsteemi tase x tarkvara osakaalu kasv x koos-disain, -simul. jne. y Korduvkasutamine x OO eelised x testkeskkond y C/C++ on levinud! © Peeter Ellervee y C/C++ ei toeta x riistvara infovahetust • signaalid, protokollid x aja mõistet (takt) x sama-aegsust x reaktiivsust • nt. katkestused x riistavara andmetüüpe • bit, bitivektor, MVL I 207 - Digitaalloogika ja -süsteemid - L 15 14

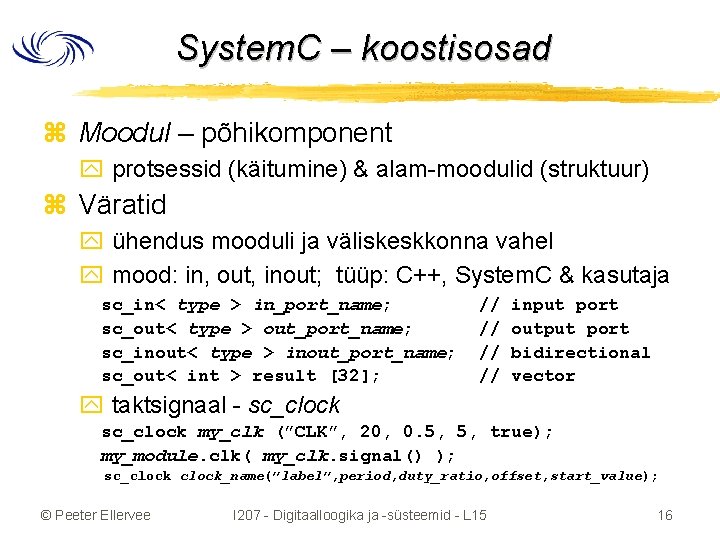

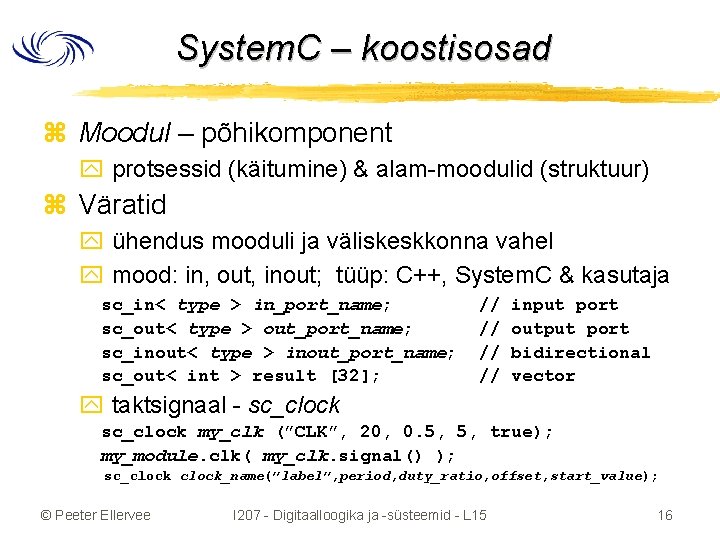

Mis on System. C? z C++ klasside teek y protsessid (sama-aegsus) y taktsignaalid (aja mõiste) y moodulid, väratid, signaalid (hierarhia) y ootamine, valvamine (reaktiivsus) y riistvara andmetüübid z Modelleerimis-stiil y. . . süsteemide jaoks, mis koosnevad mitmest doomenist, abstraktsioonitasemest, arhitektuursest komponendist ja realistlikest piirangutest z Lõimeil põhinev simulatsiooni-mehanism © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 15

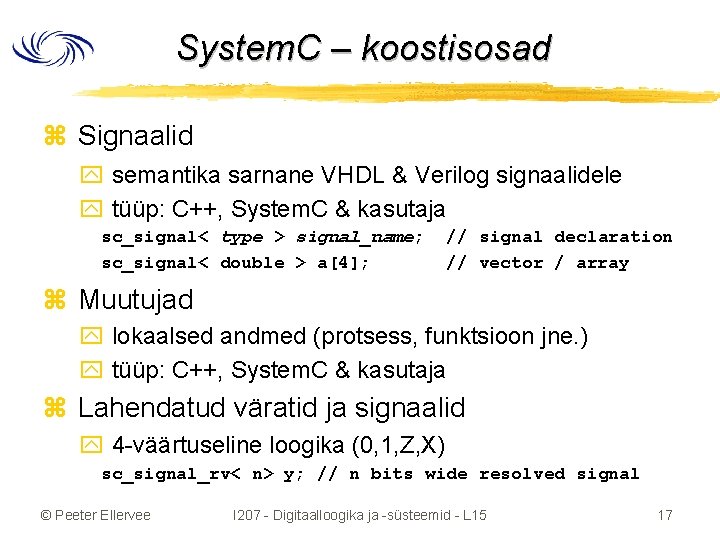

System. C – koostisosad z Moodul – põhikomponent y protsessid (käitumine) & alam-moodulid (struktuur) z Väratid y ühendus mooduli ja väliskeskkonna vahel y mood: in, out, inout; tüüp: C++, System. C & kasutaja sc_in< type > in_port_name; // input port sc_out< type > out_port_name; // output port sc_inout< type > inout_port_name; // bidirectional sc_out< int > result [32]; // vector y taktsignaal - sc_clock my_clk (”CLK”, 20, 0. 5, 5, true); my_module. clk( my_clk. signal() ); sc_clock_name(”label”, period, duty_ratio, offset, start_value); © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 16

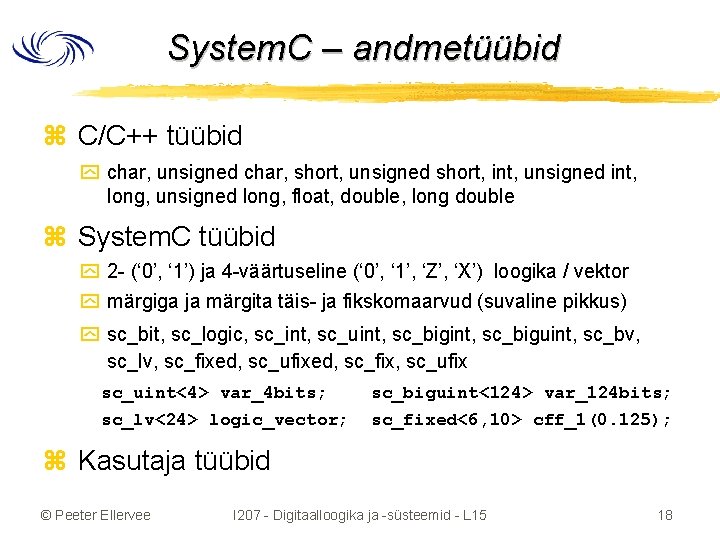

System. C – koostisosad z Signaalid y semantika sarnane VHDL & Verilog signaalidele y tüüp: C++, System. C & kasutaja sc_signal< type > signal_name; // signal declaration sc_signal< double > a[4]; // vector / array z Muutujad y lokaalsed andmed (protsess, funktsioon jne. ) y tüüp: C++, System. C & kasutaja z Lahendatud väratid ja signaalid y 4 -väärtuseline loogika (0, 1, Z, X) sc_signal_rv< n> y; // n bits wide resolved signal © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 17

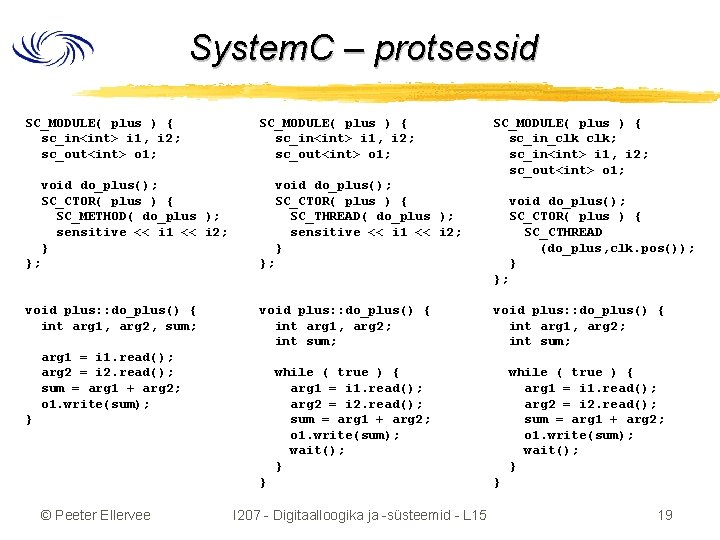

System. C – andmetüübid z C/C++ tüübid y char, unsigned char, short, unsigned short, int, unsigned int, long, unsigned long, float, double, long double z System. C tüübid y 2 - (‘ 0’, ‘ 1’) ja 4 -väärtuseline (‘ 0’, ‘ 1’, ‘Z’, ‘X’) loogika / vektor y märgiga ja märgita täis- ja fikskomaarvud (suvaline pikkus) y sc_bit, sc_logic, sc_int, sc_uint, sc_biguint, sc_bv, sc_lv, sc_fixed, sc_ufixed, sc_fix, sc_ufix sc_uint<4> var_4 bits; sc_biguint<124> var_124 bits; sc_lv<24> logic_vector; sc_fixed<6, 10> cff_1(0. 125); z Kasutaja tüübid © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 18

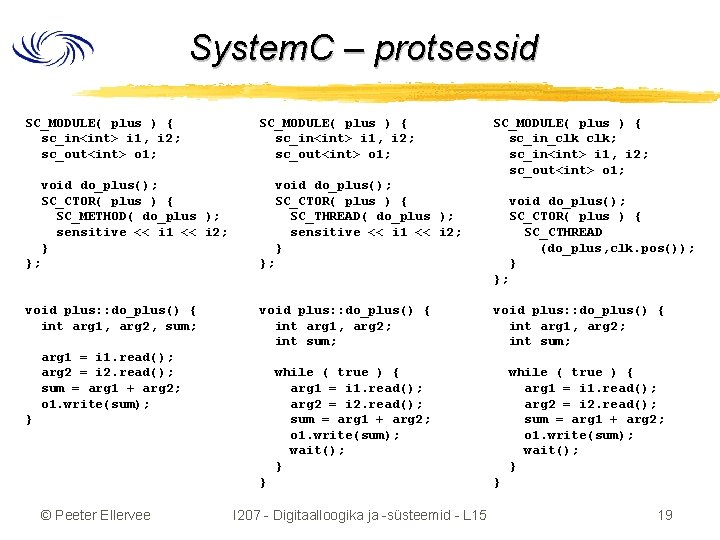

System. C – protsessid SC_MODULE( plus ) { sc_in<int> i 1, i 2; sc_out<int> o 1; void do_plus(); SC_CTOR( plus ) { SC_METHOD( do_plus ); sensitive << i 1 << i 2; } }; void do_plus(); SC_CTOR( plus ) { SC_THREAD( do_plus ); sensitive << i 1 << i 2; } }; void plus: : do_plus() { int arg 1, arg 2, sum; void plus: : do_plus() { int arg 1, arg 2; int sum; while ( true ) { arg 1 = i 1. read(); arg 2 = i 2. read(); sum = arg 1 + arg 2; o 1. write(sum); wait(); } } arg 1 = i 1. read(); arg 2 = i 2. read(); sum = arg 1 + arg 2; o 1. write(sum); } © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 SC_MODULE( plus ) { sc_in_clk clk; sc_in<int> i 1, i 2; sc_out<int> o 1; void do_plus(); SC_CTOR( plus ) { SC_CTHREAD (do_plus, clk. pos()); } }; 19

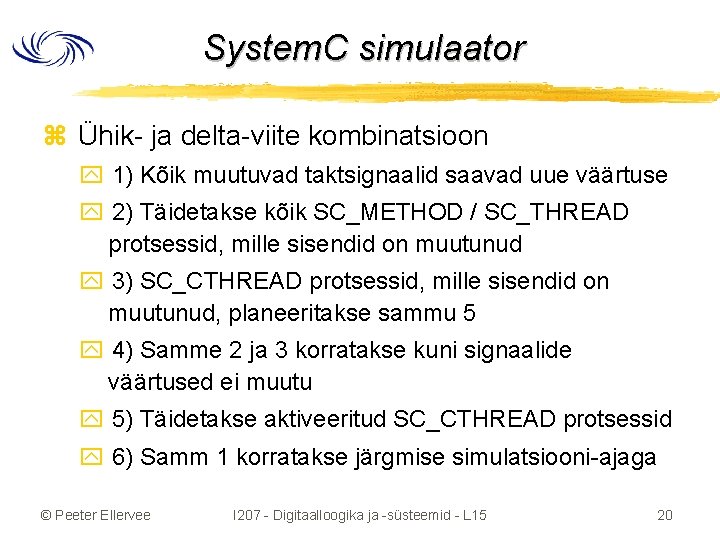

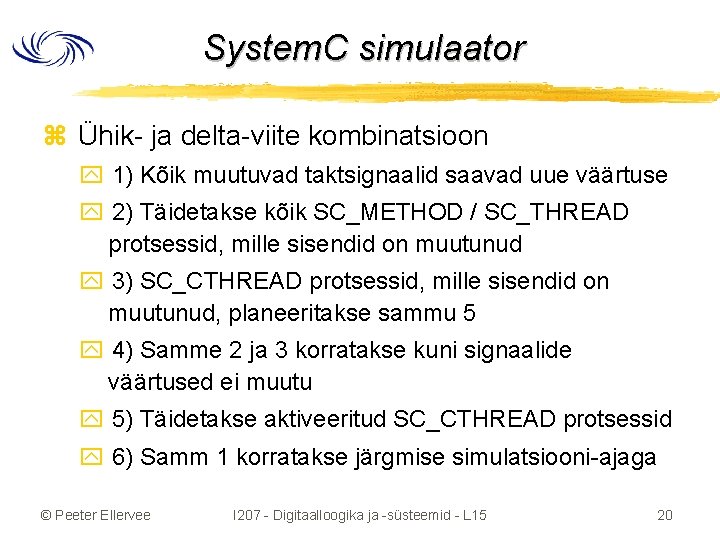

System. C simulaator z Ühik- ja delta-viite kombinatsioon y 1) Kõik muutuvad taktsignaalid saavad uue väärtuse y 2) Täidetakse kõik SC_METHOD / SC_THREAD protsessid, mille sisendid on muutunud y 3) SC_CTHREAD protsessid, mille sisendid on muutunud, planeeritakse sammu 5 y 4) Samme 2 ja 3 korratakse kuni signaalide väärtused ei muutu y 5) Täidetakse aktiveeritud SC_CTHREAD protsessid y 6) Samm 1 korratakse järgmise simulatsiooni-ajaga © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 20

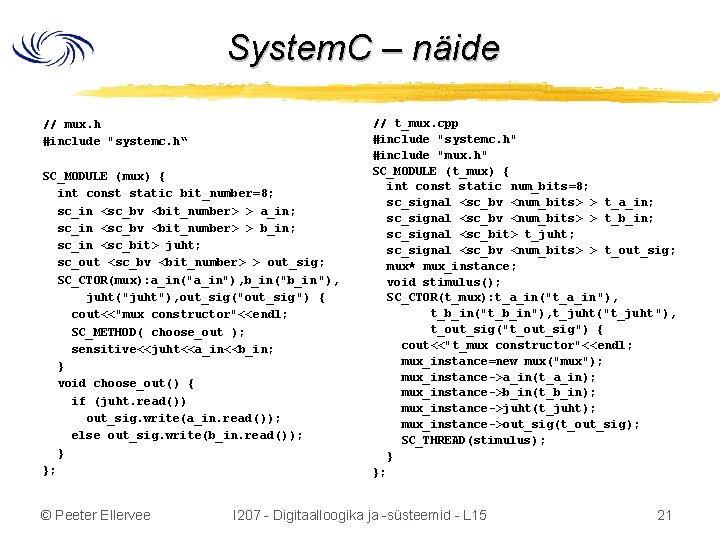

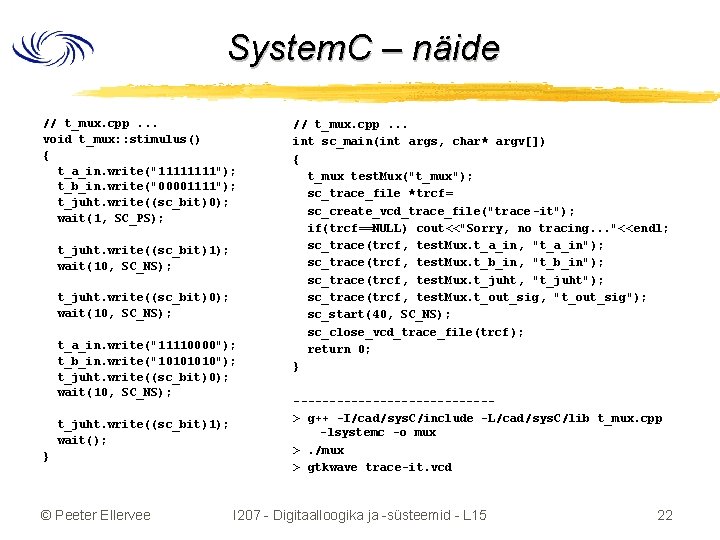

System. C – näide // mux. h #include "systemc. h“ SC_MODULE (mux) { int const static bit_number=8; sc_in <sc_bv <bit_number> > a_in; sc_in <sc_bv <bit_number> > b_in; sc_in <sc_bit> juht; sc_out <sc_bv <bit_number> > out_sig; SC_CTOR(mux): a_in("a_in"), b_in("b_in "), juht("juht"), out_sig("out_sig ") { cout<<"mux constructor"<<endl; SC_METHOD( choose_out ); sensitive<<juht<<a_in<<b_in; } void choose_out() { if (juht. read()) out_sig. write(a_in. read()); else out_sig. write(b_in. read()); } }; © Peeter Ellervee // t_mux. cpp #include "systemc. h" #include "mux. h" SC_MODULE (t_mux) { int const static num_bits=8; sc_signal <sc_bv <num_bits> > t_a_in; sc_signal <sc_bv <num_bits> > t_b_in; sc_signal <sc_bit> t_juht; sc_signal <sc_bv <num_bits> > t_out_sig; mux* mux_instance; void stimulus(); SC_CTOR(t_mux): t_a_in("t_a_in "), t_b_in("t_b_in"), t_juht("t_juht "), t_out_sig("t_out_sig") { cout<<"t_mux constructor"<<endl; mux_instance=new mux("mux"); mux_instance->a_in(t_a_in); mux_instance->b_in(t_b_in); mux_instance->juht(t_juht); mux_instance->out_sig(t_out_sig); SC_THREAD(stimulus); } }; I 207 - Digitaalloogika ja -süsteemid - L 15 21

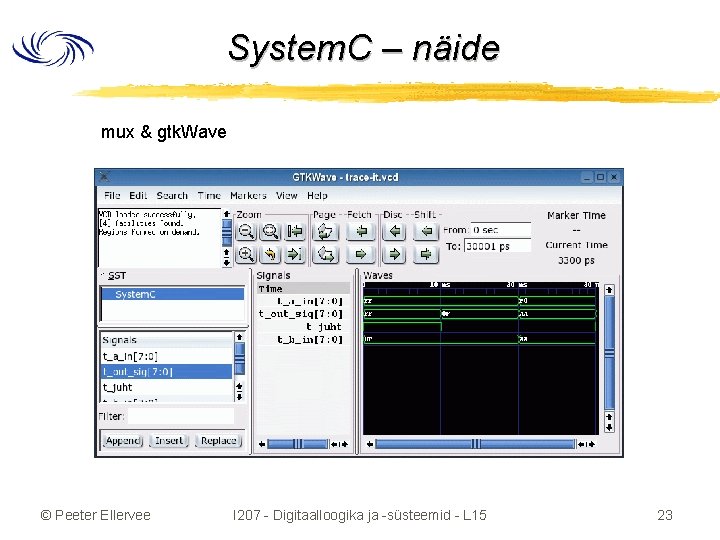

System. C – näide // t_mux. cpp. . . void t_mux: : stimulus() { t_a_in. write("1111"); t_b_in. write("00001111"); t_juht. write((sc_bit)0); wait(1, SC_PS); t_juht. write((sc_bit)1); wait(10, SC_NS); t_juht. write((sc_bit)0); wait(10, SC_NS); t_a_in. write("11110000"); t_b_in. write("1010"); t_juht. write((sc_bit)0); wait(10, SC_NS); t_juht. write((sc_bit)1); wait(); } © Peeter Ellervee // t_mux. cpp. . . int sc_main(int args, char* argv[]) { t_mux test. Mux("t_mux"); sc_trace_file *trcf= sc_create_vcd_trace_file("trace -it"); if(trcf==NULL) cout<<"Sorry, no tracing. . . "<< endl; sc_trace(trcf, test. Mux. t_a_in, "t_a_in"); sc_trace(trcf, test. Mux. t_b_in, "t_b_in"); sc_trace(trcf, test. Mux. t_juht, "t_juht"); sc_trace(trcf, test. Mux. t_out_sig, "t_out_sig"); sc_start(40, SC_NS); sc_close_vcd_trace_file(trcf ); return 0; } --------------> g++ -I/cad/sys. C/include -L/cad/sys. C/lib t_mux. cpp -lsystemc -o mux >. /mux > gtkwave trace-it. vcd I 207 - Digitaalloogika ja -süsteemid - L 15 22

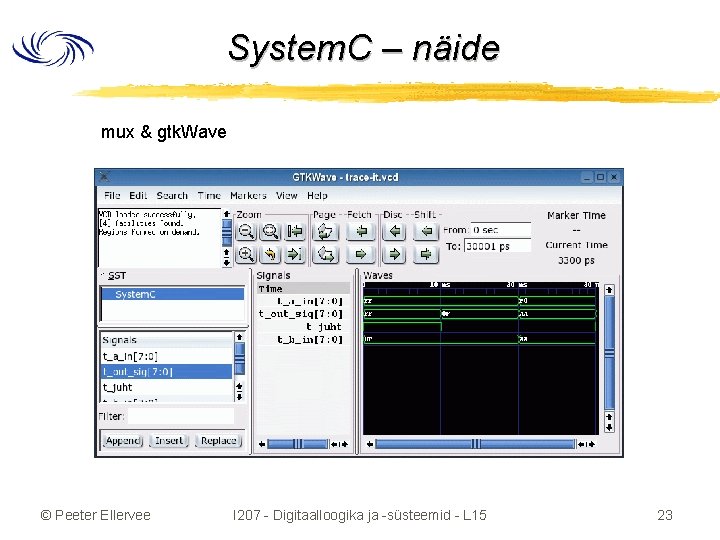

System. C – näide mux & gtk. Wave © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 23

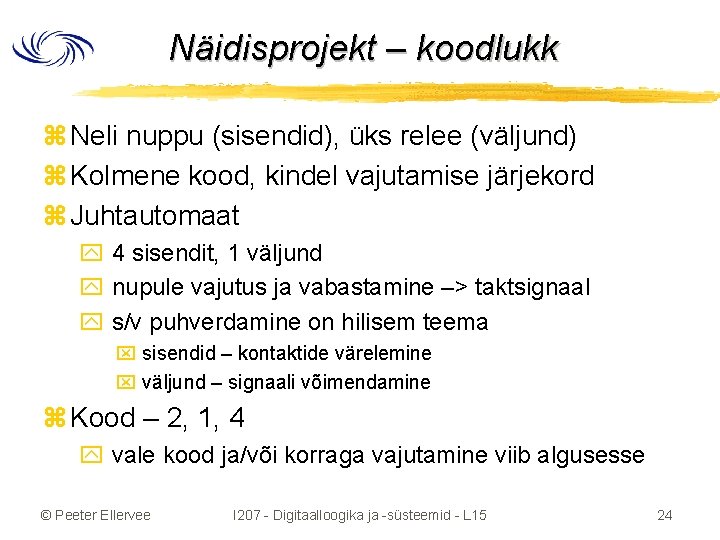

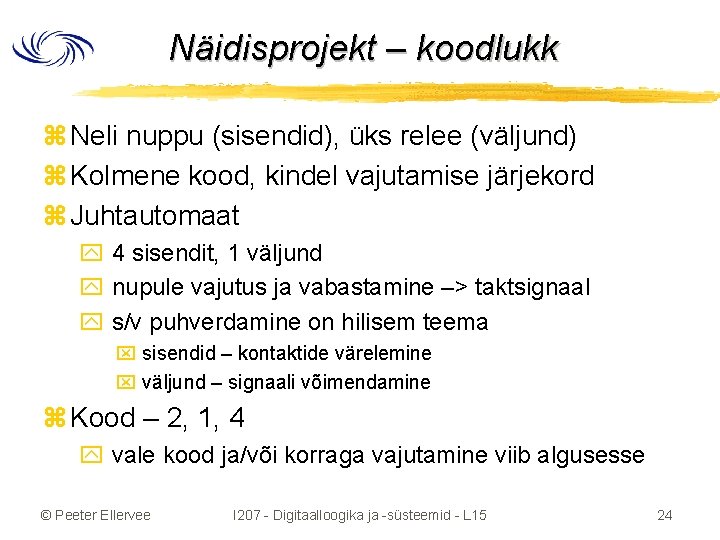

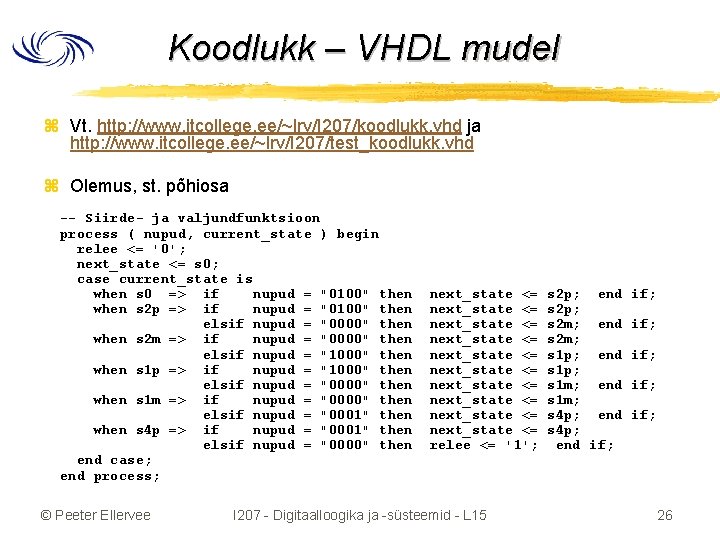

Näidisprojekt – koodlukk z Neli nuppu (sisendid), üks relee (väljund) z Kolmene kood, kindel vajutamise järjekord z Juhtautomaat y 4 sisendit, 1 väljund y nupule vajutus ja vabastamine –> taktsignaal y s/v puhverdamine on hilisem teema x sisendid – kontaktide värelemine x väljund – signaali võimendamine z Kood – 2, 1, 4 y vale kood ja/või korraga vajutamine viib algusesse © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 24

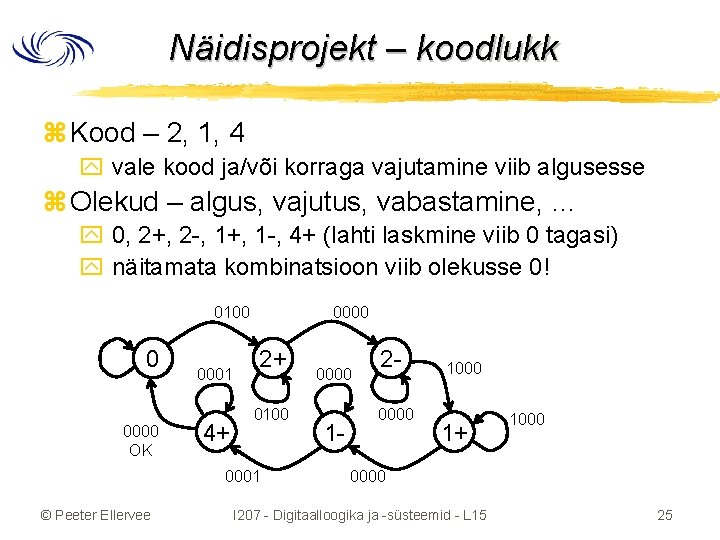

Näidisprojekt – koodlukk z Kood – 2, 1, 4 y vale kood ja/või korraga vajutamine viib algusesse z Olekud – algus, vajutus, vabastamine, … y 0, 2+, 2 -, 1+, 1 -, 4+ (lahti laskmine viib 0 tagasi) y näitamata kombinatsioon viib olekusse 0! 0100 0 0000 OK 0001 4+ 0000 2+ 0100 0001 © Peeter Ellervee 0000 1 - 20000 1+ 1000 0000 I 207 - Digitaalloogika ja -süsteemid - L 15 25

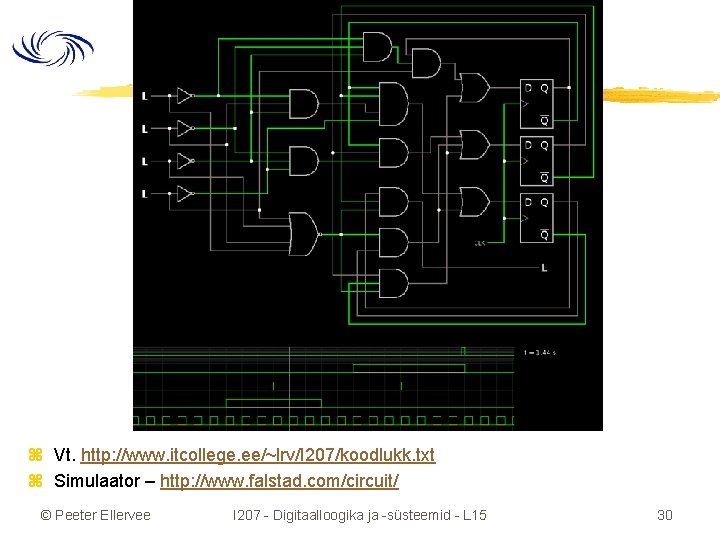

Koodlukk – VHDL mudel z Vt. http: //www. itcollege. ee/~lrv/I 207/koodlukk. vhd ja http: //www. itcollege. ee/~lrv/I 207/test_koodlukk. vhd z Olemus, st. põhiosa -- Siirde- ja valjundfunktsioon process ( nupud, current_state ) begin relee <= '0'; next_state <= s 0; case current_state is when s 0 => if nupud = "0100" then next_state <= s 2 p; end if; when s 2 p => if nupud = "0100" then next_state <= s 2 p; elsif nupud = "0000" then next_state <= s 2 m; end if; when s 2 m => if nupud = "0000" then next_state <= s 2 m; elsif nupud = "1000" then next_state <= s 1 p; end if; when s 1 p => if nupud = "1000" then next_state <= s 1 p; elsif nupud = "0000" then next_state <= s 1 m; end if; when s 1 m => if nupud = "0000" then next_state <= s 1 m; elsif nupud = "0001" then next_state <= s 4 p; end if; when s 4 p => if nupud = "0001" then next_state <= s 4 p; elsif nupud = "0000" then relee <= '1'; end if; end case; end process; © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 26

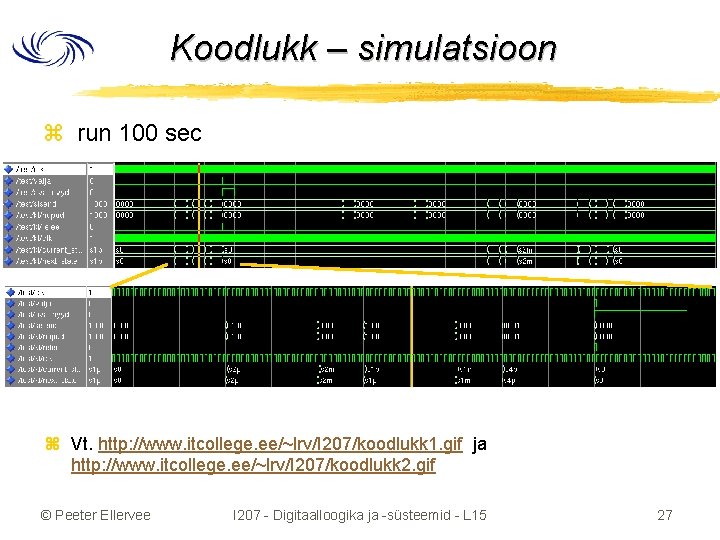

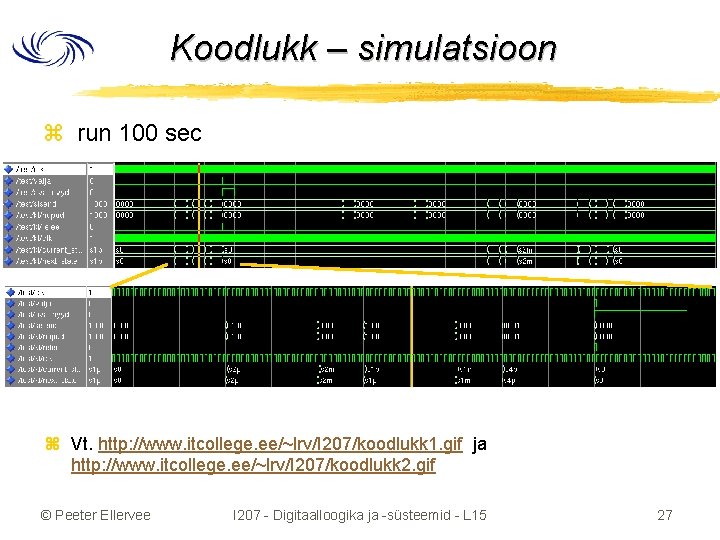

Koodlukk – simulatsioon z run 100 sec z Vt. http: //www. itcollege. ee/~lrv/I 207/koodlukk 1. gif ja http: //www. itcollege. ee/~lrv/I 207/koodlukk 2. gif © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 27

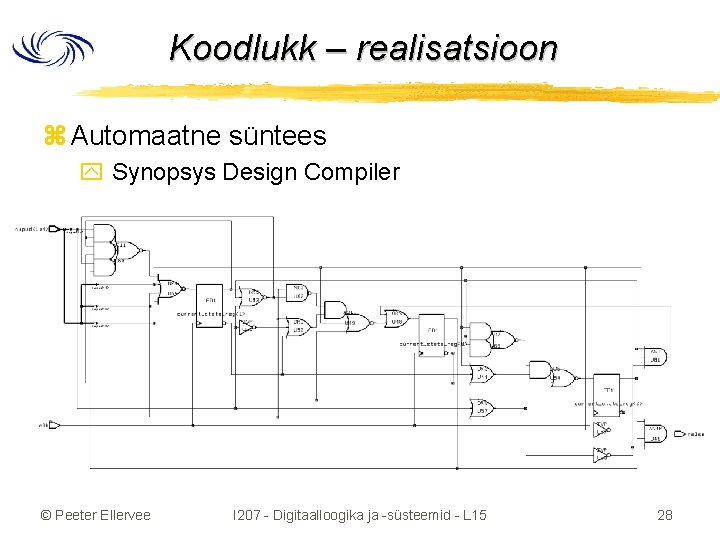

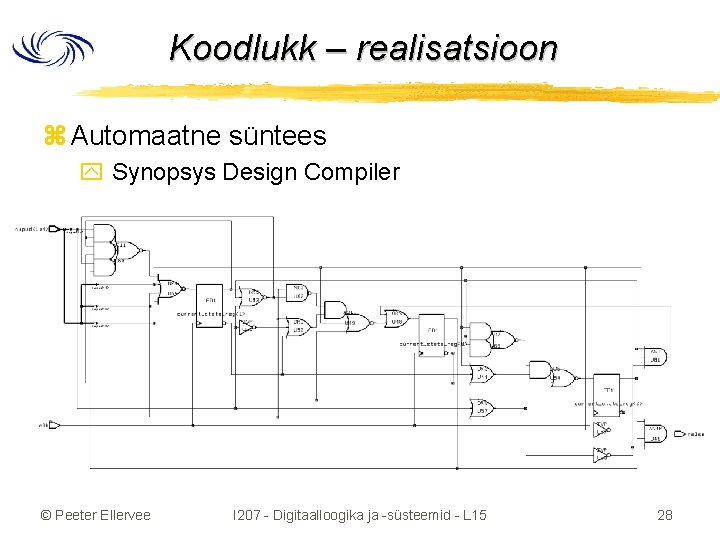

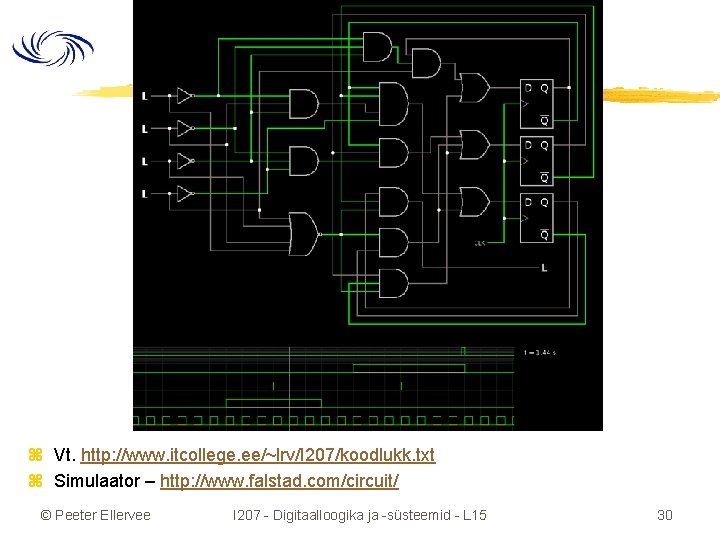

Koodlukk – realisatsioon z Automaatne süntees y Synopsys Design Compiler © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 28

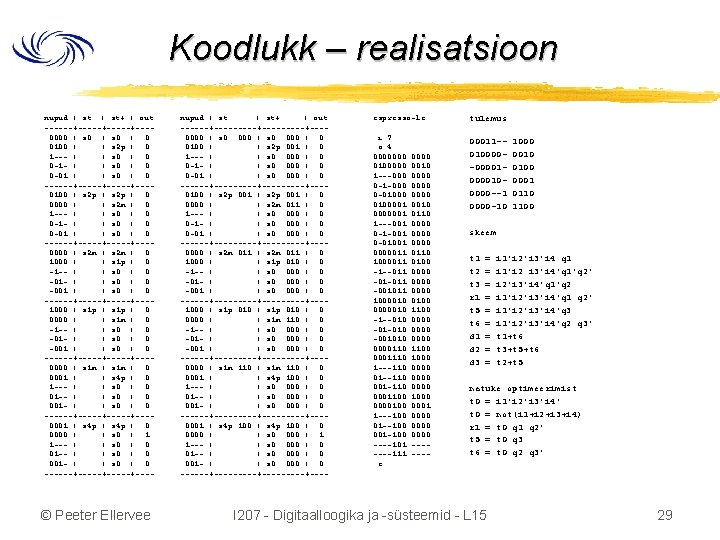

Koodlukk – realisatsioon nupud | st+ | out ------+-----+--- 0000 | s 0 | 0 0100 | | s 2 p | 0 1 --- | | s 0 | 0 0 -1 - | | s 0 | 0 0 -01 | | s 0 | 0 ------+-----+--- 0100 | s 2 p | 0 0000 | | s 2 m | 0 1 --- | | s 0 | 0 0 -1 - | | s 0 | 0 0 -01 | | s 0 | 0 ------+-----+--- 0000 | s 2 m | 0 1000 | | s 1 p | 0 -1 -- | | s 0 | 0 -01 - | | s 0 | 0 -001 | | s 0 | 0 ------+-----+--- 1000 | s 1 p | 0 0000 | | s 1 m | 0 -1 -- | | s 0 | 0 -01 - | | s 0 | 0 -001 | | s 0 | 0 ------+-----+--- 0000 | s 1 m | 0 0001 | | s 4 p | 0 1 --- | | s 0 | 0 01 -- | | s 0 | 0 001 - | | s 0 | 0 ------+-----+--- 0001 | s 4 p | 0 0000 | | s 0 | 1 1 --- | | s 0 | 0 01 -- | | s 0 | 0 001 - | | s 0 | 0 ------+-----+---- © Peeter Ellervee nupud | st+ | out ------+---------+--- 0000 | s 0 000 | 0 0100 | | s 2 p 001 | 0 1 --- | | s 0 000 | 0 0 -1 - | | s 0 000 | 0 0 -01 | | s 0 000 | 0 ------+---------+--- 0100 | s 2 p 001 | 0 0000 | | s 2 m 011 | 0 1 --- | | s 0 000 | 0 0 -1 - | | s 0 000 | 0 0 -01 | | s 0 000 | 0 ------+---------+--- 0000 | s 2 m 011 | 0 1000 | | s 1 p 010 | 0 -1 -- | | s 0 000 | 0 -01 - | | s 0 000 | 0 -001 | | s 0 000 | 0 ------+---------+--- 1000 | s 1 p 010 | 0 0000 | | s 1 m 110 | 0 -1 -- | | s 0 000 | 0 -01 - | | s 0 000 | 0 -001 | | s 0 000 | 0 ------+---------+--- 0000 | s 1 m 110 | 0 0001 | | s 4 p 100 | 0 1 --- | | s 0 000 | 0 01 -- | | s 0 000 | 0 001 - | | s 0 000 | 0 ------+---------+--- 0001 | s 4 p 100 | 0 0000 | | s 0 000 | 1 1 --- | | s 0 000 | 0 01 -- | | s 0 000 | 0 001 - | | s 0 000 | 0 ------+---------+---- espresso-le tulemus . i 7. o 4 0000000 0100000 0010 1 ---000 0 -1 -000 0 -0100001 0010 0000001 0110 1 ---001 0000 0 -1 -001 0000 0 -01001 0000011 0110 1000011 0100 -1 --011 0000 -01 -011 0000 -001011 0000 1000010 0100 0000010 1100 -1 --010 0000 -01 -010 0000 -001010 0000110 1100 0001110 1000 1 ---110 0000 01 --110 0000 001 -110 0001100 1000 0000100 0001 1 ---100 0000 01 --100 001 -100 0000 ----101 -------111 ---. e 00011 -- 1000 010000 - 0010 -00001 - 0100 000010 - 0001 0000 --1 0110 0000 -10 1100 skeem t 1 = i 1'i 2'i 3'i 4 q 1 t 2 = i 1'i 2 i 3'i 4'q 1'q 2' t 3 = i 2'i 3'i 4'q 1'q 2 rl = i 1'i 2'i 3'i 4'q 1 q 2' t 5 = i 1'i 2'i 3'i 4'q 3 t 6 = i 1'i 2'i 3'i 4'q 2 q 3' d 1 = t 1+t 6 d 2 = t 3+t 5+t 6 d 3 = t 2+t 5 natuke optimeerimist t 0 = i 1'i 2'i 3'i 4' t 0 = not(i 1+i 2+i 3+i 4) rl = t 0 q 1 q 2' t 5 = t 0 q 3 t 6 = t 0 q 2 q 3' I 207 - Digitaalloogika ja -süsteemid - L 15 29

z Vt. http: //www. itcollege. ee/~lrv/I 207/koodlukk. txt z Simulaator – http: //www. falstad. com/circuit/ © Peeter Ellervee I 207 - Digitaalloogika ja -süsteemid - L 15 30