Software Defined Radio SDR The Future of Wireless

- Slides: 22

Software Defined Radio – SDR The Future of Wireless Paul Tindall Head of Software SDR - "Radio in which some or all of the physical layer functions are software defined“ - Wireless Innovation Forum

Future of Wireless § Complexity: § “I need to support 10 Radio bands a 8 standards/modes to make a phone that works anywhere on the Vodafone network” - Trevor Gill, Chief Scientist Vodafone § Post Production Flexibility § “I wish I could change the radio filter in the Heathrow ATC RADAR so I can use the adjacent spectrum” § “I’d prefer totally dynamic spectrum assignment” – Graham Louth – Ofcom : UK regulator § Dynamic Behaviour § Cognitive radio is required to manage licensed and unlicensed spectrum § Terminals will sense and reconfigure themselves according to location/environment –Jussi Kahtava 2

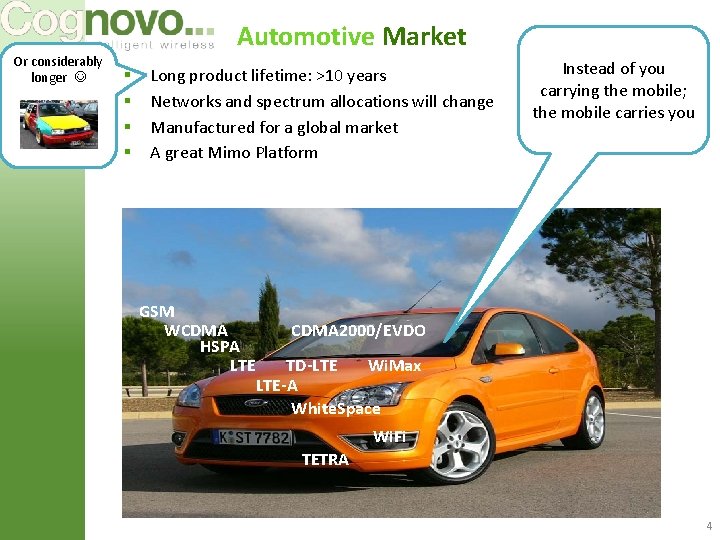

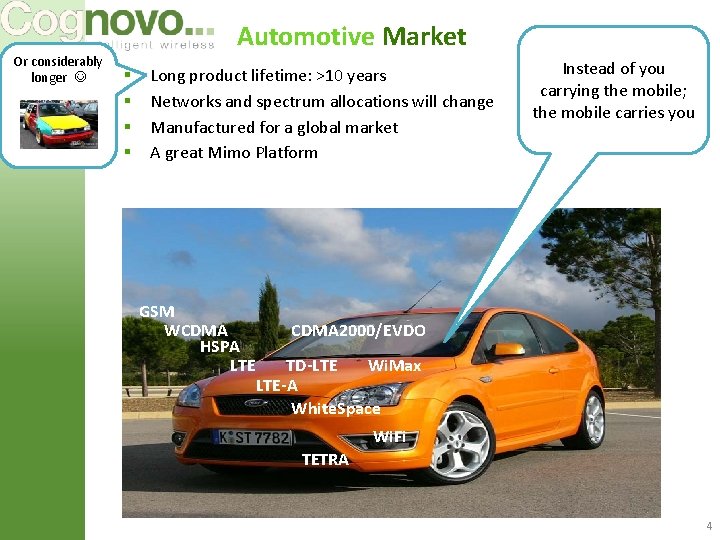

Automotive Market Or considerably longer § § Long product lifetime: >10 years Networks and spectrum allocations will change Manufactured for a global market A great Mimo Platform GSM WCDMA HSPA LTE Instead of you carrying the mobile; the mobile carries you CDMA 2000/EVDO TD-LTE Wi. Max LTE-A White. Space Wi. Fi TETRA 4

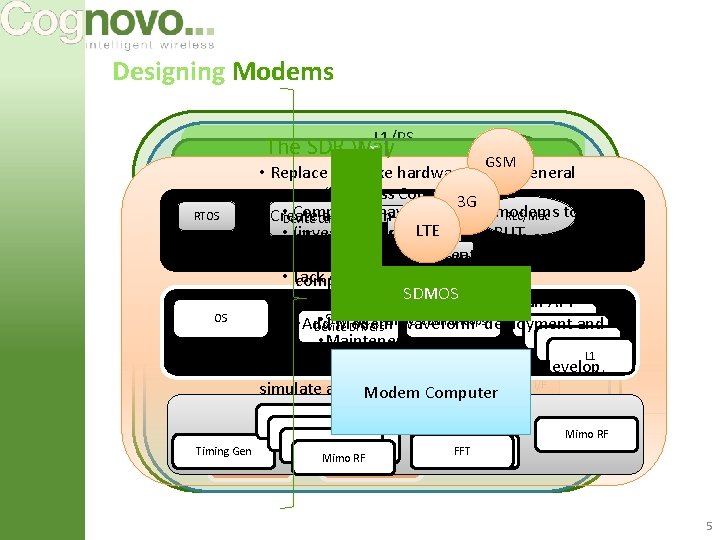

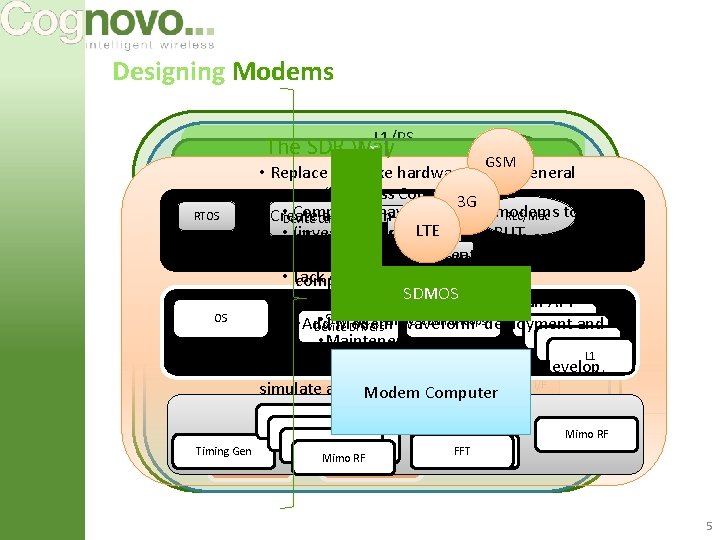

Designing Modems L 1/PS The SDR Way PS RTOS OS L 1 PS GSM Power PS a general • Replace Power bespoke hardware with Managem Saving“Wireless Device purpose Computer ent and 3 G“ L 1 • Device Companies have ‘Velcro’ed Man RLC/Mac together • Create a Modem Specific OS modems control Device. Man Ctrl LTEouthigh) • (investment in legacy BUT services • To mop up/factor common • The future. DSP predicts greater complexity • Hide/abstract the underlying h/w DSP costs • Lack of reuse complexity SDMOS • Si. Channel area Control Speechan API • Publish the modem developer RTOS Measurements Loops Codecs L 1 and • SW dev time Control loops • Add Modem ‘waveform’ deployment Speech Device Drivers L 1 • Maintenence L 1 management functions L 1 • Create tools (like the Android SDK) to develop, Equalser simulate Cipher and test modem apps Radio I/F Modem Computer Timing Gen Rake Power Controller Mimo RF Demapper Radio Mimo RF Controller Channel Timebase Mimo System RF Eq Time FFT Codec Counters Mimo RF Controller Mimo RF 5

The Complexity Problem 6

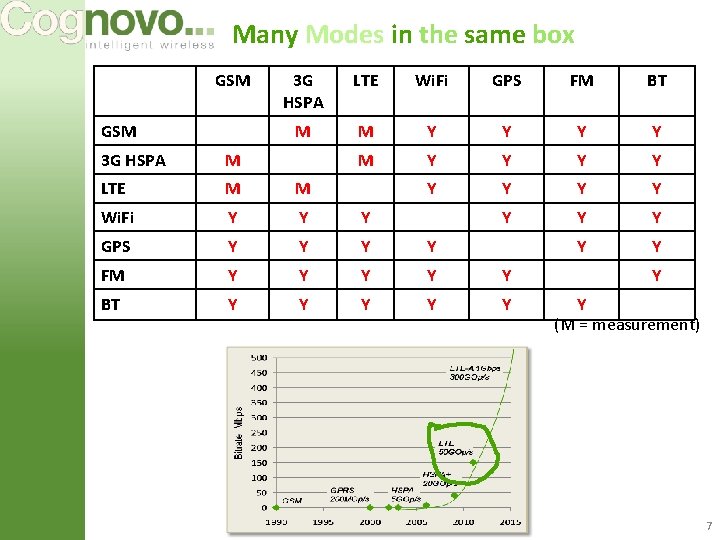

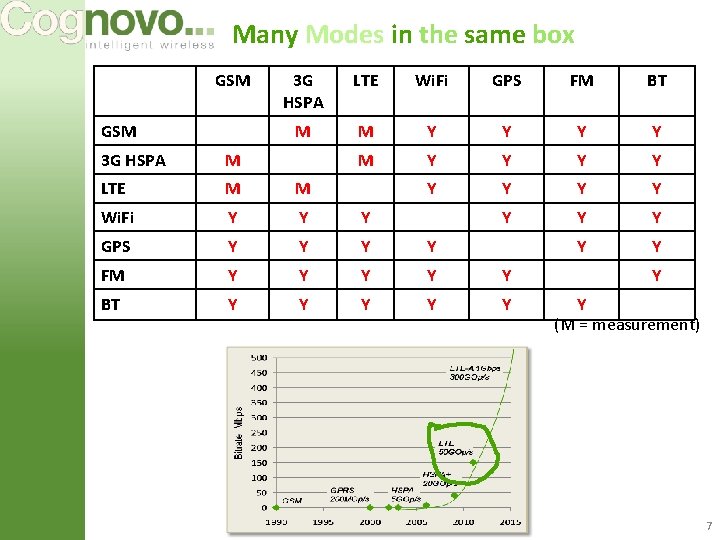

Many Modes in the same box GSM 3 G HSPA LTE Wi. Fi GPS FM BT M M Y Y Y Y Y 3 G HSPA M LTE M M Wi. Fi Y Y Y GPS Y Y FM Y Y Y BT Y Y Y Y (M = measurement) 7

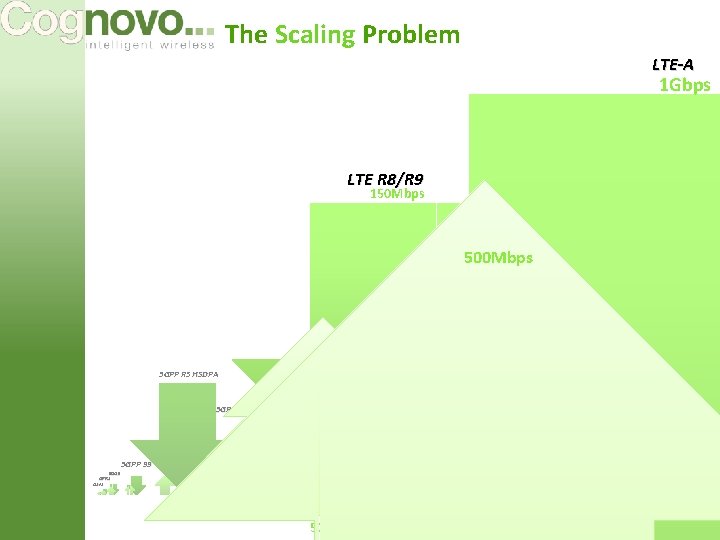

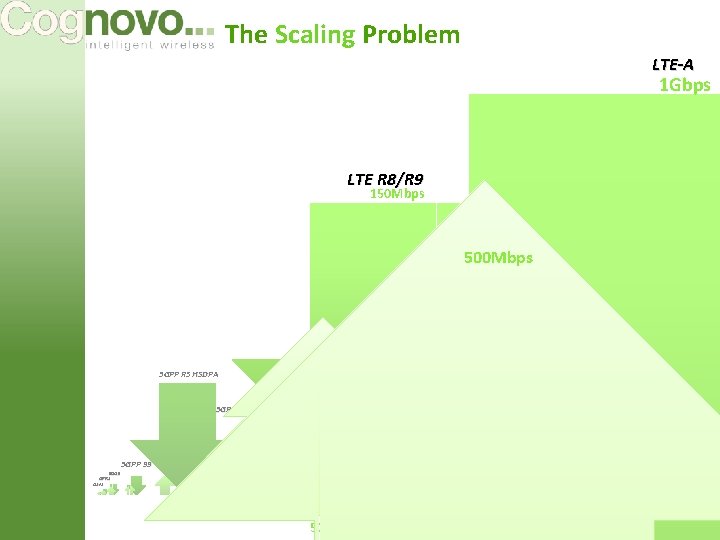

The Scaling Problem LTE-A 1 Gbps 3 GPP R 10 164 Mbps LTE R 8/R 9 3 GPP R 9 150 Mbps 84 Mbps 500 Mbps 3 GPP R 8 3 GPP R 7 HSPA+ 42 Mbps 28 Mbps 3 GPP R 5 HSDPA 3 GPP R 6 HSUPA 3 GPP 99 EDGE GPRS GSM 11 Mbps 50 Mbps 23 Mbps 8

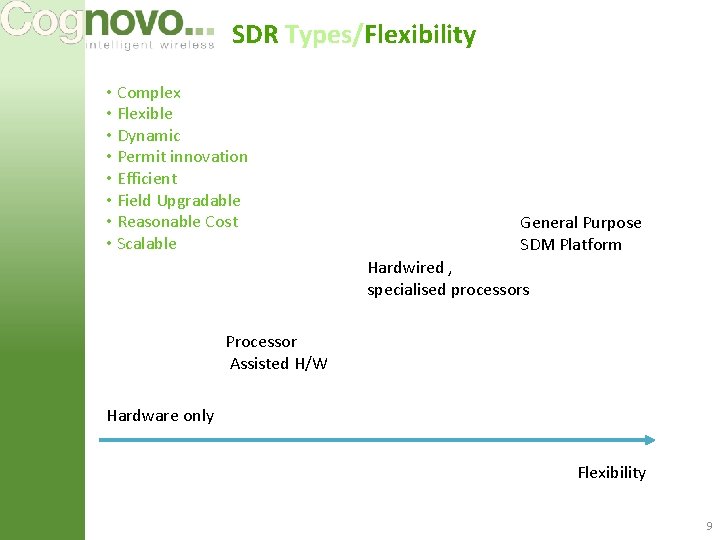

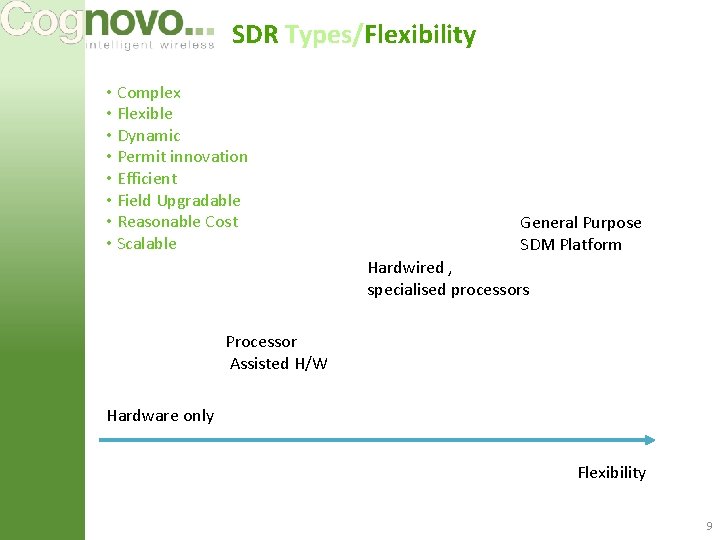

SDR Types/Flexibility • Complex • Flexible • Dynamic • Permit innovation • Efficient • Field Upgradable • Reasonable Cost • Scalable General Purpose SDM Platform Hardwired , specialised processors Processor Assisted H/W Hardware only Flexibility 9

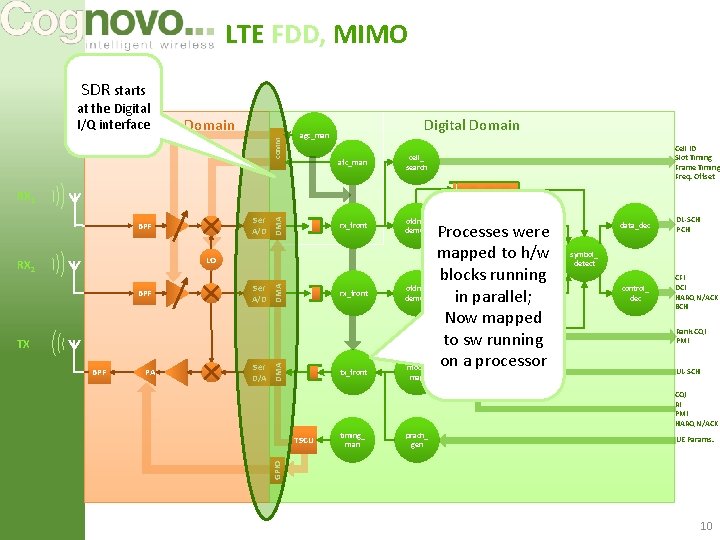

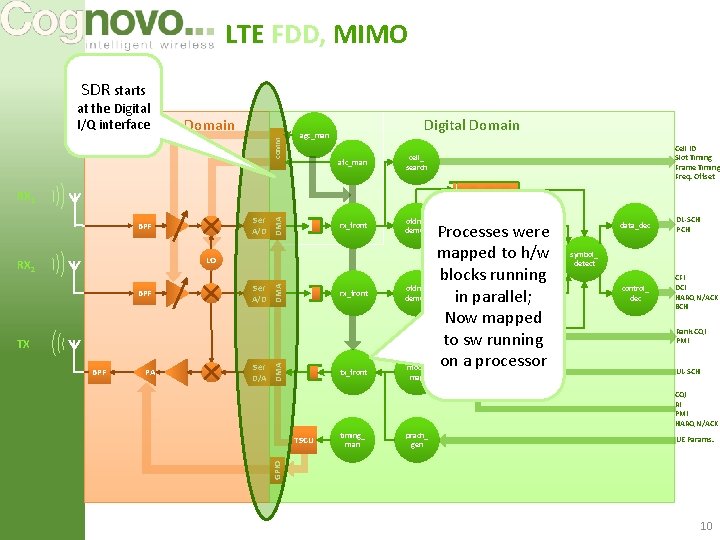

LTE FDD, MIMO SDR starts COMM at the Digital I/Q interface Analogue Domain Digital Domain agc_man afc_man cell_ search rx_front ofdm_ demux Cell ID Slot Timing Frame Timing Freq. Offset Ser A/D BPF DMA RX 1 BPF Ser A/D DMA LO RX 2 rx_front ofdm_ demux PA Ser D/A tx_front mod_ map enc data_dec DL-SCH PCH control_ dec CFI DCI HARQ N/ACK BCH symbol_ detect Rank CQI PMI UL-SCH CQI RI PMI HARQ N/ACK TSCU timing_ man prach_ gen UE Params. GPIO BPF DMA TX Processes were mapped tometrics h/w blocks running chan_est in parallel; Now mapped to sw running on auplink_ processor chan_est 10

The VSP – a key enabling technology 15

The VSP – 3 forms of Parallelism So can’t be interrupted – run to completion Connection Network Like a ‘Dragster’ – incredible quick in a straight line Register File SIMDFUUnit FU FU FU Control Unit Scalar unit • Instruction Level Parallelism § Data Parallelism • VLIW – eg 256, 512. . . § § bits • Several ‘Functional in parallel Add 1 or more SIMDUnits’ unitswork (Single Instruction Multiple Data) • Register and memory accesses/write-backs are pipelined Wide Data paths eg 512 bit • Pipeline is exposed to the Compiler SIMD (Vector) lanesand - iedata 64 dependencies MAC operations in 1 cycle • The Compilerwidths analyseseg the 64 control of the whole program to be expressed correctly to exploit vector Requires Algorithms • The Compiler converts eg ‘C’ to an execution schedule by processing: reordering the program • Parallelising compilers are well understood and mature 16

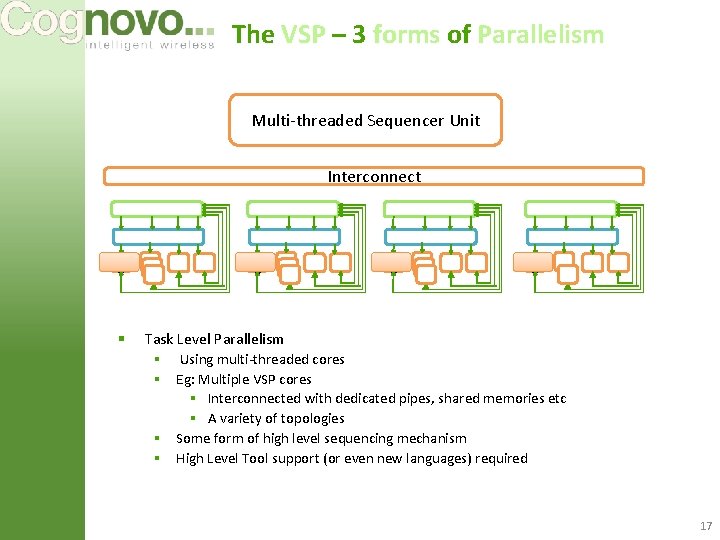

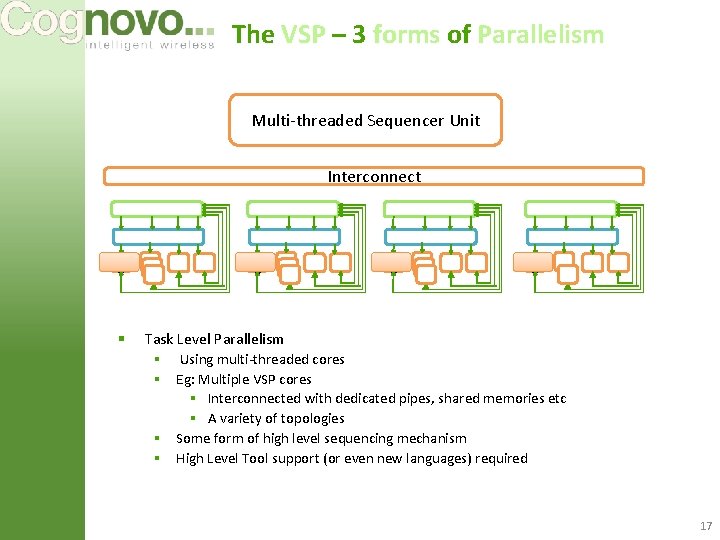

The VSP – 3 forms of Parallelism Multi-threaded Sequencer Unit Interconnect F U § U U F U Task Level Parallelism § Using multi-threaded cores § Eg: Multiple VSP cores § Interconnected with dedicated pipes, shared memories etc § A variety of topologies § Some form of high level sequencing mechanism § High Level Tool support (or even new languages) required 17

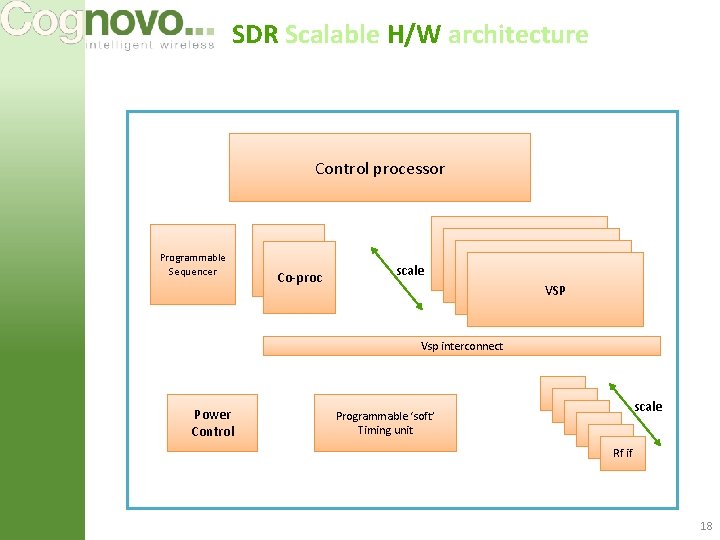

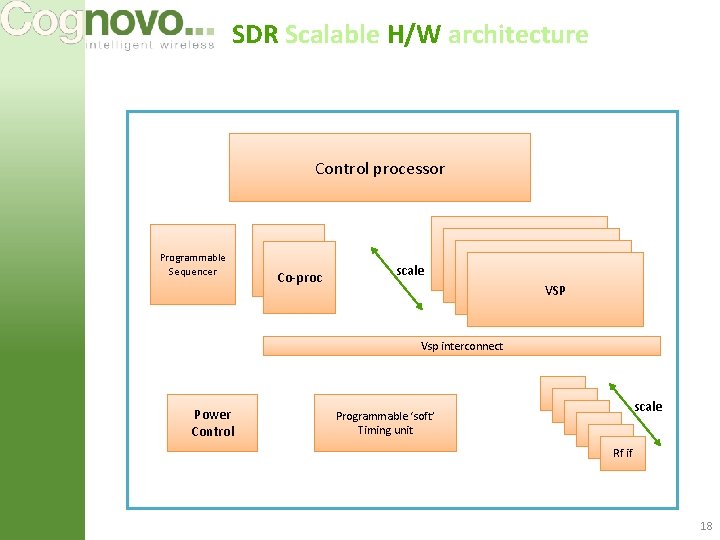

SDR Scalable H/W architecture Control processor Programmable Sequencer Co-proc scale VSP Vsp interconnect Power Control scale Programmable ‘soft’ Timing unit Rf if 18

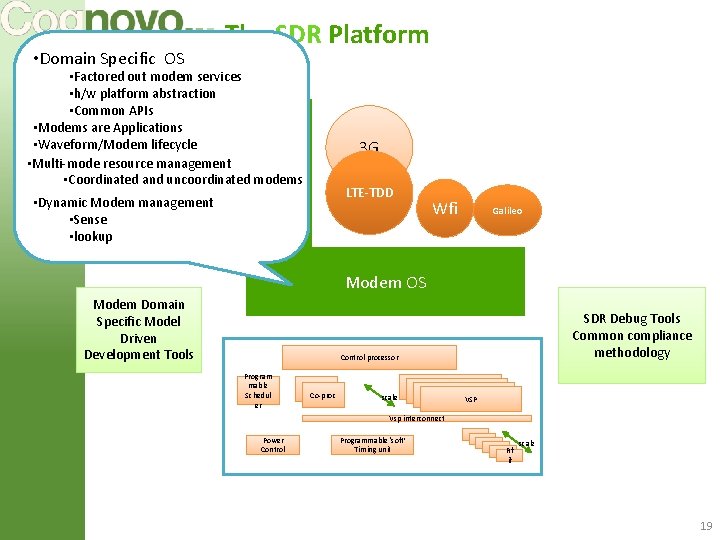

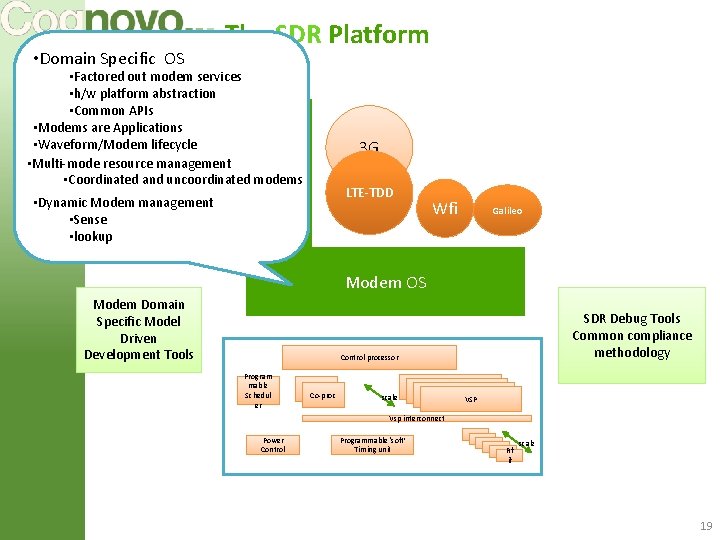

• Domain Specific OS The SDR Platform • Factored out modem services • h/w platform abstraction • Common APIs • Modems are Applications • Waveform/Modem lifecycle • Multi-mode resource management • Coordinated and uncoordinated modems 3 G LTE-TDD LTE • Dynamic Modem management • Sense • lookup Wfi BT Galileo GPS Modem OS Modem Domain Specific Model Driven Development Tools SDR Debug Tools Common compliance methodology Control processor Program mable Schedul er Co-proc scale VSP Vsp interconnect Power Control Programmable ‘soft’ Timing unit Rf if scale 19

An example Multi-Core methodology Using UML 20

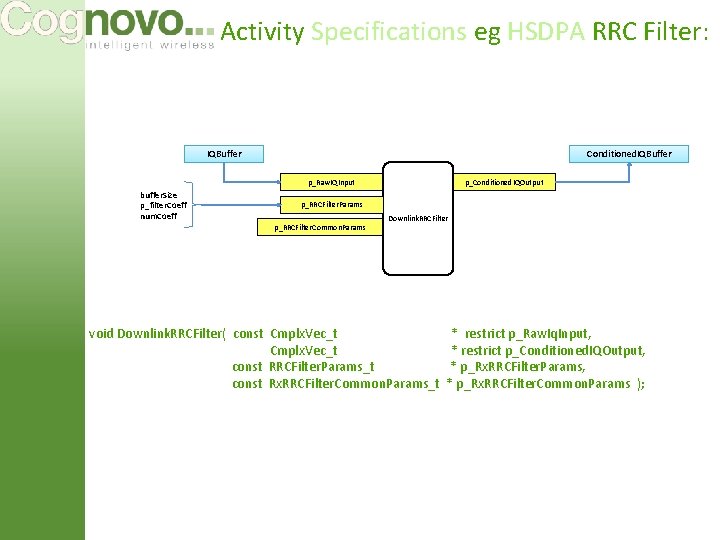

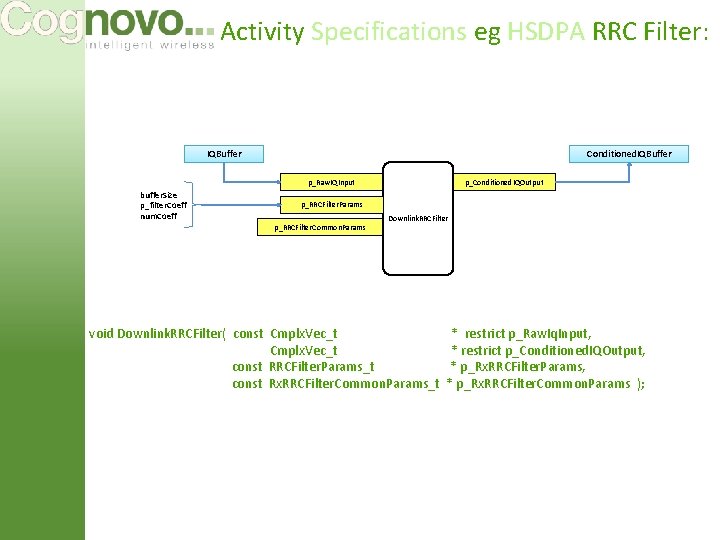

Activity Specifications eg HSDPA RRC Filter: IQBuffer Conditioned. IQBuffer p_Raw. IQInput buffer. Size p_filter. Coeff num. Coeff p_Conditioned. IQOutput p_RRCFilter. Params p_RRCFilter. Common. Params Downlink. RRCFilter void Downlink. RRCFilter( const Cmplx. Vec_t const RRCFilter. Params_t const Rx. RRCFilter. Common. Params_t * restrict p_Raw. Iq. Input, * restrict p_Conditioned. IQOutput, * p_Rx. RRCFilter. Params, * p_Rx. RRCFilter. Common. Params );

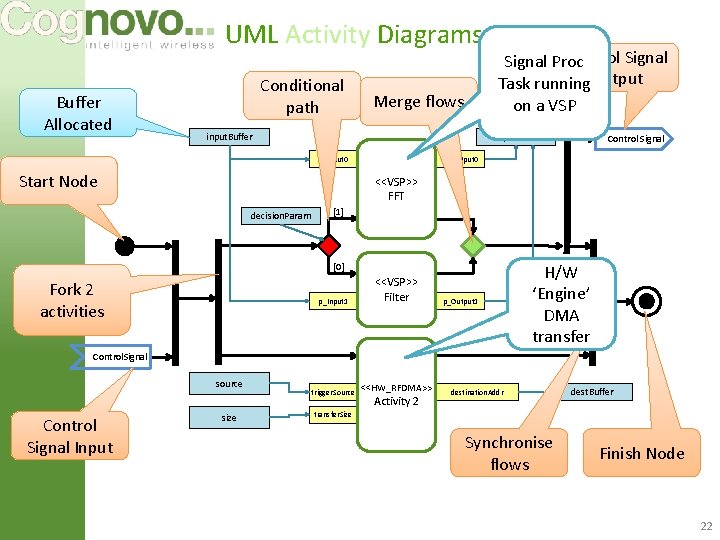

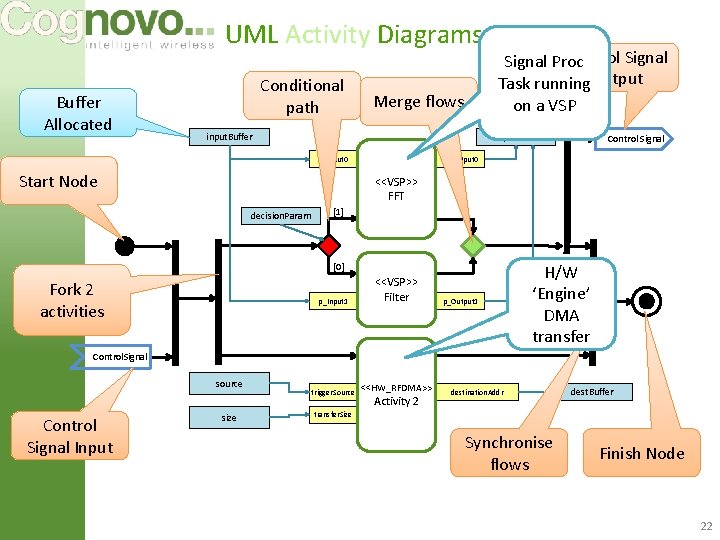

UML Activity Diagrams Buffer Allocated Conditional path Merge flows input. Buffer Control Signal Proc Task running. Output on a VSP output. Buffer p_Input 0 Start Node Control Signal p_Output 0 <<VSP>> FFT decision. Param [1] [0] Fork 2 activities p_Input 1 <<VSP>> Filter trigger. Source <<HW_RFDMA>> p_Output 1 H/W ‘Engine’ DMA transfer Control. Signal source Control Signal Input size Activity 2 destination. Addr dest. Buffer transfer. Size Synchronise flows Finish Node 22

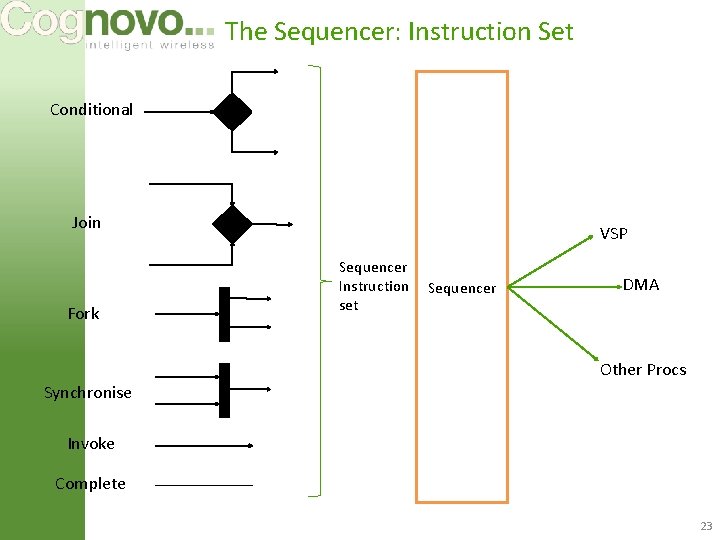

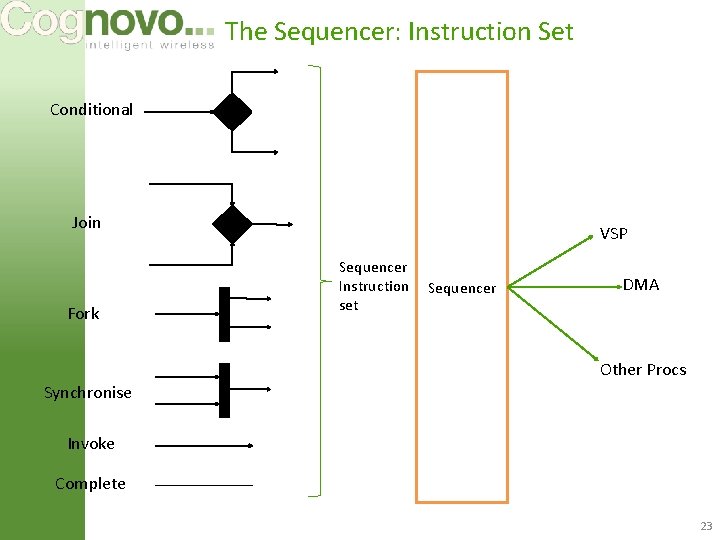

The Sequencer: Instruction Set Conditional Join Fork VSP Sequencer Instruction set Sequencer DMA Other Procs Synchronise Invoke Complete 23

A Real Platform 24

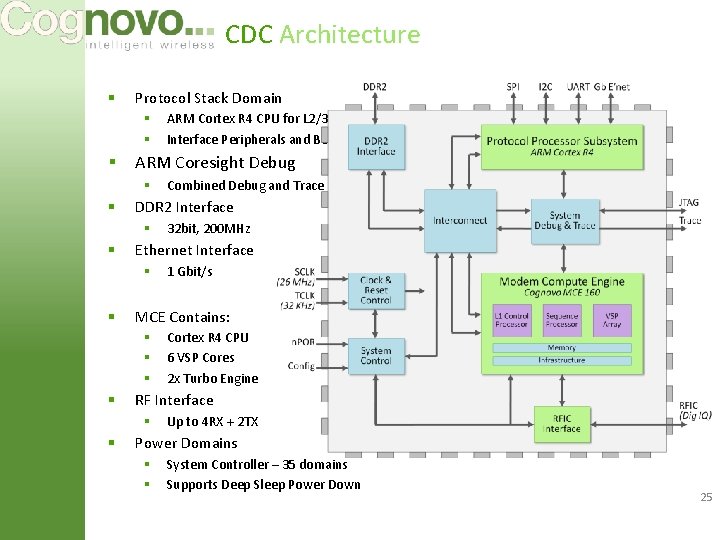

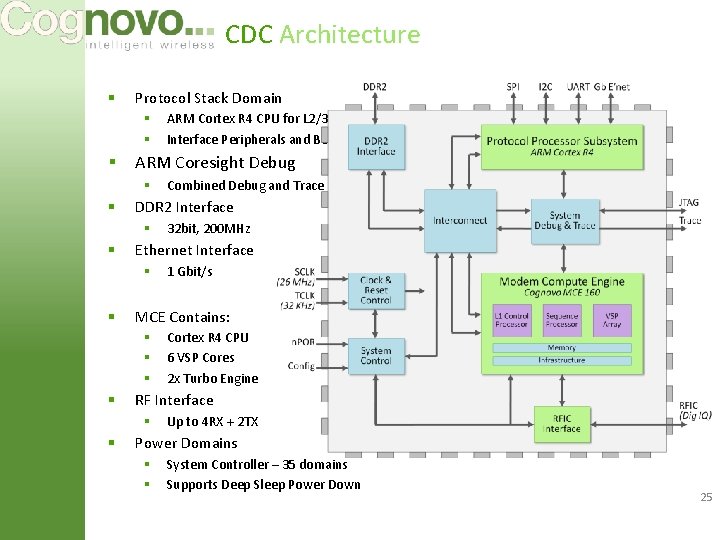

CDC Architecture § Protocol Stack Domain § § § ARM Coresight Debug § § Cortex R 4 CPU 6 VSP Cores 2 x Turbo Engine RF Interface § § 1 Gbit/s MCE Contains: § § 32 bit, 200 MHz Ethernet Interface § § Combined Debug and Trace DDR 2 Interface § § ARM Cortex R 4 CPU for L 2/3 Protocol S/W Interface Peripherals and Boot ROM Up to 4 RX + 2 TX Power Domains § § System Controller – 35 domains Supports Deep Sleep Power Down 25

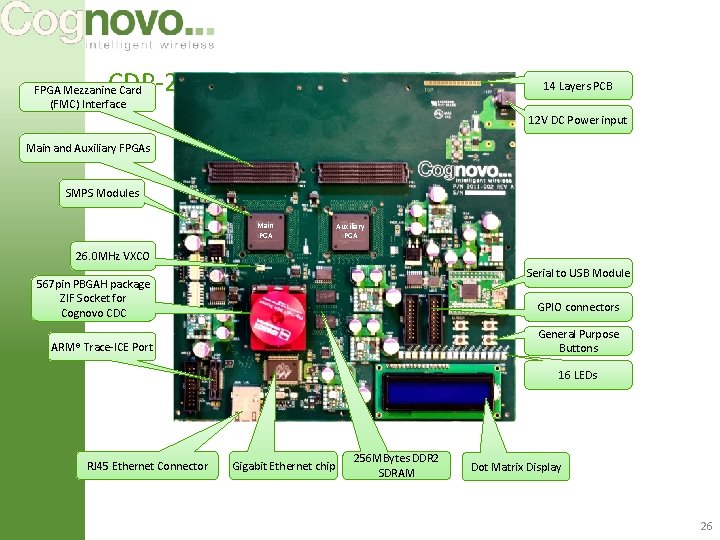

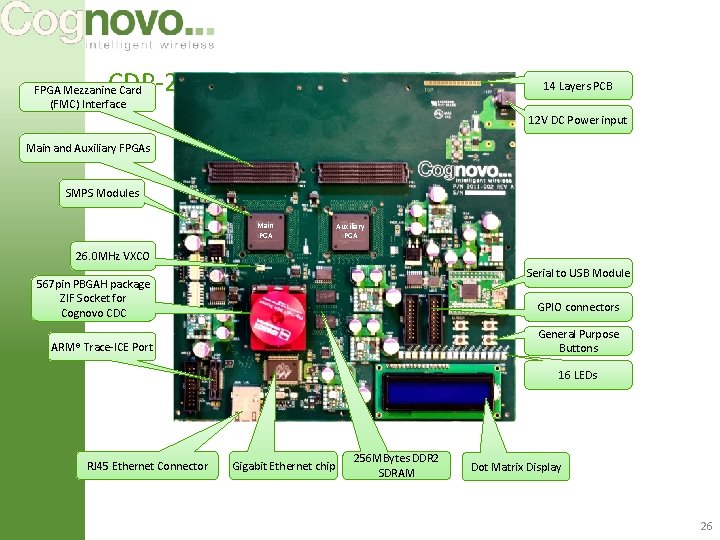

CDP-2 Board 14 Layers PCB FPGA Mezzanine Card (FMC) Interface 12 V DC Power input Main and Auxiliary FPGAs SMPS Modules Main PGA Auxiliary PGA 26. 0 MHz VXCO Serial to USB Module 567 pin PBGAH package ZIF Socket for Cognovo CDC GPIO connectors General Purpose Buttons ARM® Trace-ICE Port 16 LEDs RJ 45 Ethernet Connector Gigabit Ethernet chip 256 MBytes DDR 2 SDRAM Dot Matrix Display 26

Final Thoughts § SDR platforms will deliver our wireless future § BUT it is potentially disruptive: § Who owns the Standards/waveforms – OEM, Google, Sky, ETSI, Qualcomm, IP companies, new entrants? § Separating the h/w and standardising it disrupts the Si supply chain § How is compliance tested – who is responsible now? § How is Essential IPR paid/managed? 27