Set 11 Asynchronous Consensus DISTRIBUTED ALGORITHMS AND SYSTEMS

Set 11: Asynchronous Consensus DISTRIBUTED ALGORITHMS AND SYSTEMS Spring 2014 Prof. Jennifer Welch 1

Impossibility of Asynchronous Consensus 2 Show impossible in read/write shared memory with n processors and n - 1 faults prove directly: not hard since so many faults implies there is no 2 -proc algorithm for 1 fault Show impossible in r/w shared memory with n processors and 1 fault. Two approaches: Reduction: use a hypothetical n-proc algorithm for 1 fault as a subroutine to design a 2 -proc algorithm for 1 fault Direct proof: Use similar ideas to n-1 failures Set 11: Asynchronous Consensus case

Impossibility of Asynchronous Consensus 3 Show impossible in message passing with n processors and 1 fault. Two approaches: Reduction: Use a hypothetical message passing algorithm for n procs and 1 fault as a subroutine to design a shared memory algorithm for n procs and 1 fault. This would contradict previous result. Direct approach: Use similar ideas to shared memory case, augmented to handle messages. (Historically, this was the first version that was proven. ) Set 11: Asynchronous Consensus

Modeling Asynchronous Systems with Crash Failures 4 Let f be the maximum number of faulty processors. For both SM and MP: All but f of the processors must take an infinite number of steps in an admissible execution. For MP: Also require that all messages sent to a nonfaulty processor must eventually be delivered, except for those sent by a faulty processor in its last step, which might or might not be delivered. Set 11: Asynchronous Consensus

Wait-Free Algorithms 5 An algorithm for n processors is wait-free if it can tolerate n - 1 failures. Intuition is that a nonfaulty processor does not wait for other processors to do something: it cannot, because it might be the only processor left alive. First result is to show that there is no wait-free consensus algorithm in the asynchronous r/w shared memory model. Set 11: Asynchronous Consensus

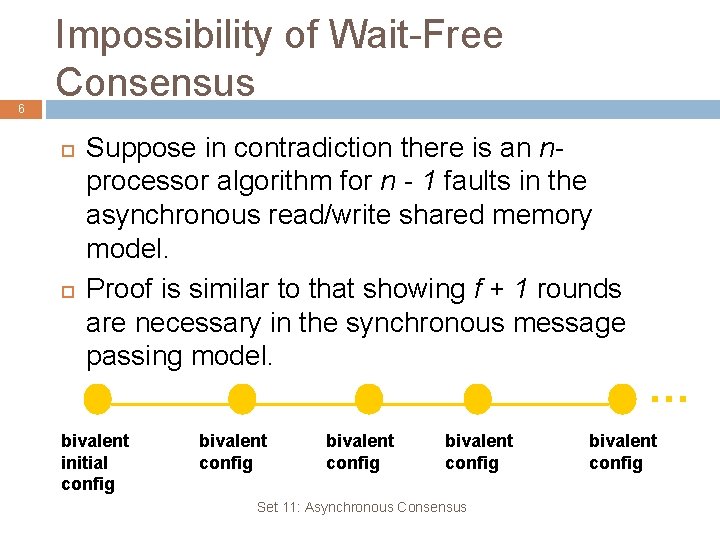

6 Impossibility of Wait-Free Consensus Suppose in contradiction there is an nprocessor algorithm for n - 1 faults in the asynchronous read/write shared memory model. Proof is similar to that showing f + 1 rounds are necessary in the synchronous message passing model. bivalent initial config bivalent config Set 11: Asynchronous Consensus … bivalent config

Modified Notion of Bivalence 7 In the synchronous round lower bound proof, valency referred to which decisions are reachable in failure-sparse admissible executions. For this proof, we are concerned with which decisions are reachable in any execution, as long as it is admissible (for the asynchronous shared memory model with up to n - 1 failures). Set 11: Asynchronous Consensus

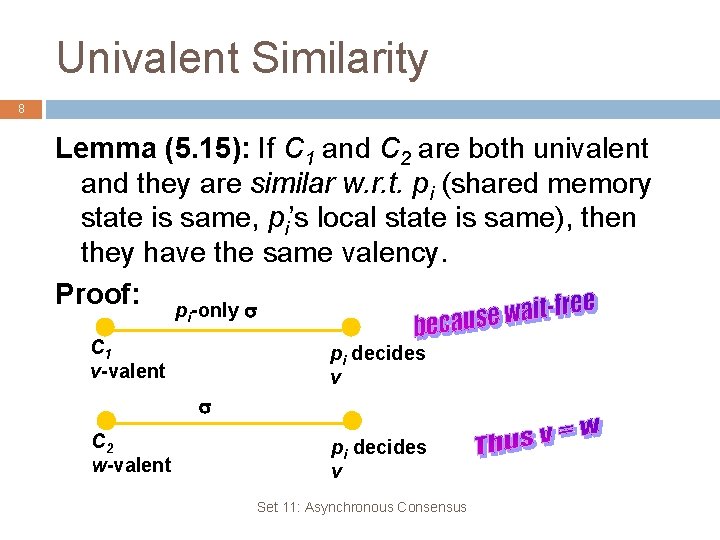

Univalent Similarity 8 Lemma (5. 15): If C 1 and C 2 are both univalent and they are similar w. r. t. pi (shared memory state is same, pi’s local state is same), then they have the same valency. Proof: p -only i C 1 v-valent pi decides v C 2 w-valent pi decides v Set 11: Asynchronous Consensus

Bivalent Initial Configuration 9 Lemma (5. 16): There exists a bivalent initial configuration. Proof is similar to what we did for the synchronous f + 1 round lower bound proof. Set 11: Asynchronous Consensus

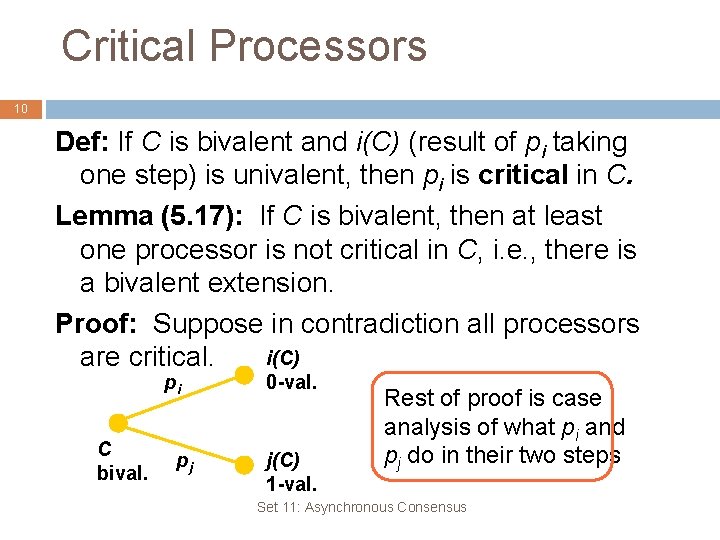

Critical Processors 10 Def: If C is bivalent and i(C) (result of pi taking one step) is univalent, then pi is critical in C. Lemma (5. 17): If C is bivalent, then at least one processor is not critical in C, i. e. , there is a bivalent extension. Proof: Suppose in contradiction all processors i(C) are critical. pi C bival. pj 0 -val. j(C) 1 -val. Rest of proof is case analysis of what pi and pj do in their two steps Set 11: Asynchronous Consensus

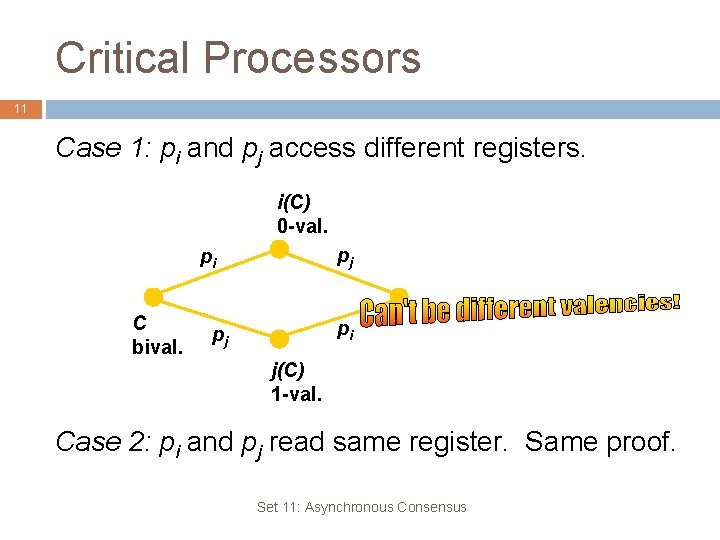

Critical Processors 11 Case 1: pi and pj access different registers. i(C) 0 -val. pj pi C bival. pi pj j(C) 1 -val. Case 2: pi and pj read same register. Same proof. Set 11: Asynchronous Consensus

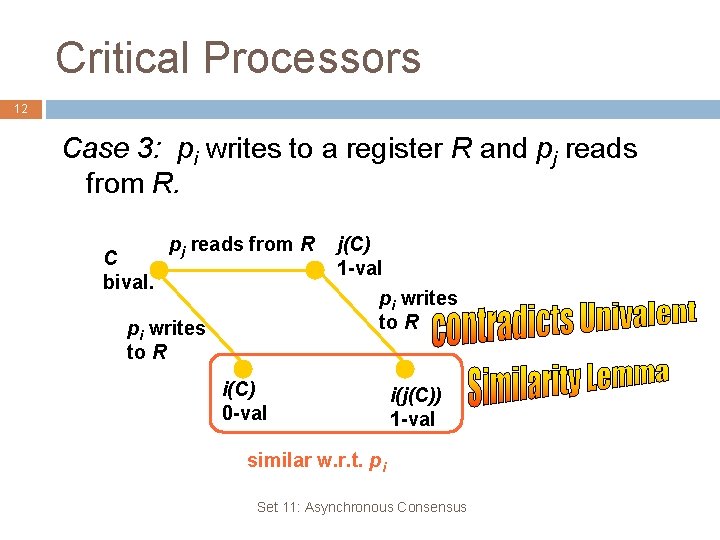

Critical Processors 12 Case 3: pi writes to a register R and pj reads from R. C bival. pj reads from R pi writes to R j(C) 1 -val pi writes to R i(C) 0 -val i(j(C)) 1 -val similar w. r. t. pi Set 11: Asynchronous Consensus

Critical Processors 13 Case 4: What if pi and pj both write to the same shared variable? Can "assume away" the problem by assuming we only have single-writer shared variables. Or, can do a similar proof for this case. Set 11: Asynchronous Consensus

Finishing the Impossibility Proof 14 Create an admissible execution C 0, i 1, C 1, i 2, C 2, … in which all configurations are bivalent. contradicts termination requirement Start with bivalent initial configuration. Suppose we have bivalent Ck. To get bivalent Ck+1: Let pi_k+1 be a processor that is not critical in Ck. Let Ck+1 be ik+1(Ck). Set 11: Asynchronous Consensus

Impossibility of 1 -Resilient Consensus: Reduction Idea 15 Even if the ratio of nonfaulty processors becomes overwhelming, consensus still cannot be solved in asynchronous SM (with read/write registers). 1. Assume there exists an algorithm A for n processors and 1 failure. 2. Use A as a subroutine to design an algorithm A' for 2 processors and 1 failure. 3. We just showed such an A' cannot exist. 4. Thus A cannot exist. Set 11: Asynchronous Consensus

Impossibility of 1 -Resilient Consensus: Direct Proof Idea 16 Suppose in contradiction there is such an algorithm. Strategy: Construct an admissible execution (at most 1 fault) that never terminates: show there is a bivalent initial configuration show to go from one bivalent configuration to another, forever (so can never terminate) Technically more involved because in constructing this execution, we cannot kill more than one processor.

Impossibility of Consensus in Message Passing: Reduction 17 Strategy: 1. Assume there exists an n-processor 1 resilient consensus algorithm A for the asynchronous message passing model. 2. Use A as a subroutine to design an nprocessor 1 -resilient consensus algorithm A' for asynchronous shared memory (with read/write variables). 3. Previous result shows A' cannot exist. 4. Thus A cannot exist.

Impossibility of Consensus in MP 18 Idea of A': Simulate message channels with read/write registers. Then run algorithm A on top of these simulated channels. To simulate channel from pi to pj: Use one register to hold the sequence of messages sent over the channel pi "sends" a message m by writing the old value of the register with m appended pj "receives" a message by reading the register and checking for new values at the end

- Slides: 18