Reversible Circuit Synthesis II Vivek Shende Aditya Prasad

Reversible Circuit Synthesis, II Vivek Shende, Aditya Prasad, Igor Markov, and John Hayes

Our Constraints n Fixed wire count n CNT gate library n Permutations, not 1 -output functions DARPA

Previous Results n Theoretical q q q n DARPA Synthesis methods Even permutations need no extra wires Odd permutations need one extra wire Practical q q Optimal synthesis methods Work for 3 -wire synthesis, but not much further V. Shende et. Al. , “Synthesis of Reversible Logic Circuits, ” Proc. ICCAD, 2002.

T|C|T|N decomposition n A T|C|T|N circuit is q n DARPA a T-circuit, followed by a C-circuit, followed by another T-circuit, followed by an N-circuit Any circuit has an equiv. T|C|T|N circuit q q Using no more wires than the original Final C|T|N portion quadratic in number of wires V. Shende et. Al. , “Synthesis of Reversible Logic Circuits, ” to appear in TCAD, 2003.

T|C|T|N decomposition n Can convert a circuit to CT|N form q n DARPA The resultant circuit is about 3 times longer The T|C|T|N case q q No known conversion algorithm Don’t know how suboptimal an optimal T|C|T|N circuit can be n Worst-case optimal T|C|T|N-circuits are suboptimal by at most a logarithmic factor V. Shende et. Al. , “Synthesis of Reversible Logic Circuits, ” to appear in TCAD, 2003.

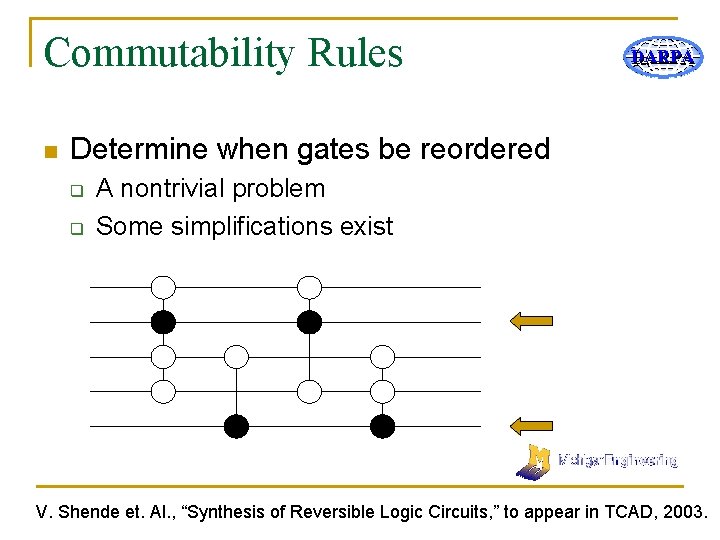

Commutability Rules n DARPA Determine when gates be reordered q q A nontrivial problem Some simplifications exist V. Shende et. Al. , “Synthesis of Reversible Logic Circuits, ” to appear in TCAD, 2003.

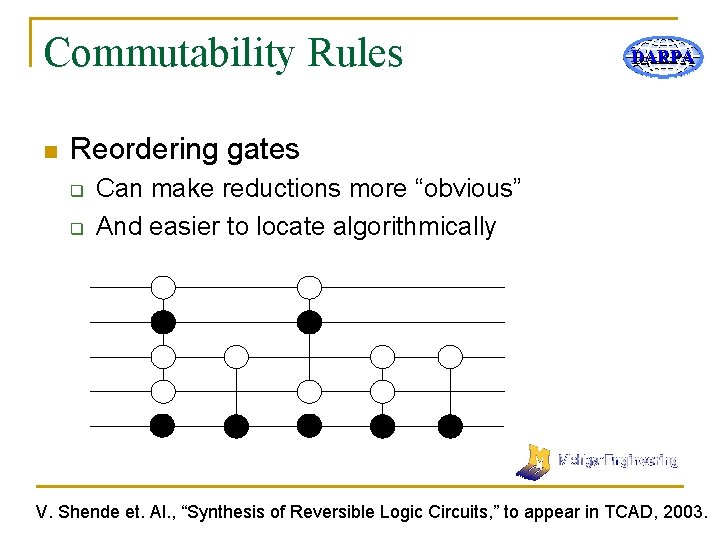

Commutability Rules n DARPA Reordering gates q q Can make reductions more “obvious” And easier to locate algorithmically V. Shende et. Al. , “Synthesis of Reversible Logic Circuits, ” to appear in TCAD, 2003.

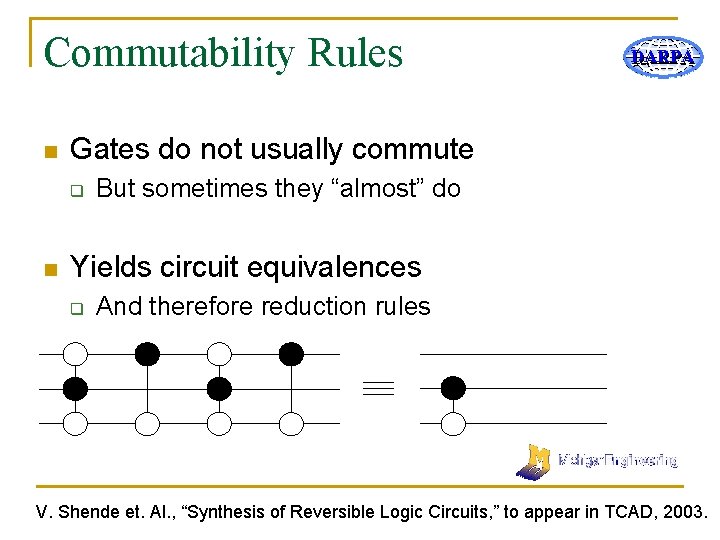

Commutability Rules n Gates do not usually commute q n DARPA But sometimes they “almost” do Yields circuit equivalences q And therefore reduction rules V. Shende et. Al. , “Synthesis of Reversible Logic Circuits, ” to appear in TCAD, 2003.

Local Optimization n Optimal synthesis methods q q n DARPA Use huge amounts of resources in the general case But can be used to quickly generate libraries of small, optimal circuits Idea: q q Isolate small pieces of a large circuit Reduce via circuit-library lookups A. Prasad et. Al. , “Simplification of Reversible Logic, ” to be submitted to IWLS 2003.

Local Optimization n Challenges q q n DARPA Finding sub-circuits amenable to optimization is a nontrivial problem Use commutability rules to re-order the circuit Results in about 30% gate count decrease q q In certain randomly generated circuits Depends on specific circuit characteristics A. Prasad et. Al. , “Simplification of Reversible Logic, ” to be submitted to IWLS 2003.

Circuit Libraries n Central to our algorithms q n DARPA Both previous & new synthesis methods Improved generation & storage q q Due to a cleaner implementation And bit-packing techniques A. Prasad et. Al. , “Simplification of Reversible Logic, ” to be submitted to IWLS 2003.

Future Work n Improve circuit library storage q n By taking advantage of symmetry Connect local optimization with synthesis algorithm from T|C|T|N-decomposition q q A complete tool for reversible logic synthesis Applicable to even 20 -input circuits DARPA

Future Work n Determine fruitful local optimizations q n Investigate simulated annealing approach q n Are some optimizations better than others? Local de-optimizations are also allowed Extend methods to non-classical logic DARPA

Thank You For Your Attention DARPA

- Slides: 14