Reconfigurable Processing Module RPM Kevin Somervill 1 kevin

Reconfigurable Processing Module (RPM) Kevin Somervill 1 (kevin. m. somervill@nasa. gov) Dr. Robert Hodson 1 (robert. f. hodson@nasa. gov) Dr. John Williams 2 (jwilliams@itee. uq. edu. au) Dr. Robert Jones 3 (robert. jones@akspace. com) NASA Langley Research Center 2 The University of Queensland, Australia 3 ASRC Aerospace Corp. 1 RSC Somervill 1 125/MAPLD'05

Presentation Topics • • RSC Platform Architectural Overview RPM Architecture Block Diagram Interface On-Chip Network Diagram Example Applications – Soft processor Based – Custom Hardware • • • Major Components System Modeling Embedded Computing (Microblaze. TM) Development Challenges and Issues Current Status RSC Somervill 2 125/MAPLD'05

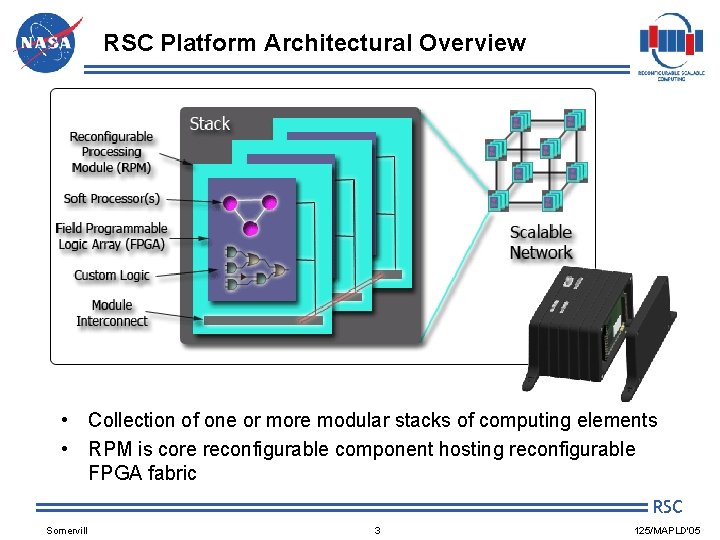

RSC Platform Architectural Overview • Collection of one or more modular stacks of computing elements • RPM is core reconfigurable component hosting reconfigurable FPGA fabric RSC Somervill 3 125/MAPLD'05

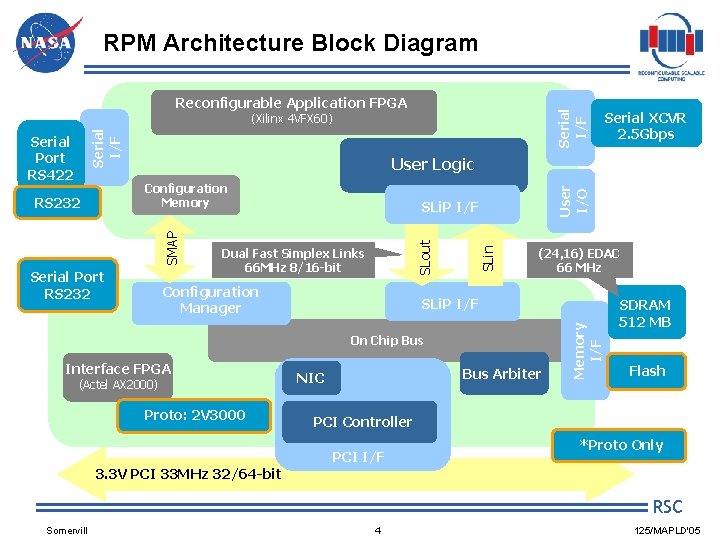

RPM Architecture Block Diagram Serial I/F Reconfigurable Application FPGA Serial I/F (Xilinx 4 VFX 60) Configuration Memory Dual Fast Simplex Links 66 MHz 8/16 -bit Configuration Manager (24, 16) EDAC 66 MHz SLi. P I/F On Chip Bus Interface FPGA (Actel AX 2000) Proto: 2 V 3000 Bus Arbiter NIC Memory I/F Serial Port RS 232 SLi. P I/F SLin SMAP RS 232 User I/O User Logic SLout Serial Port RS 422 Serial XCVR 2. 5 Gbps SDRAM 512 MB Flash PCI Controller PCI I/F *Proto Only 3. 3 V PCI 33 MHz 32/64 -bit RSC Somervill 4 125/MAPLD'05

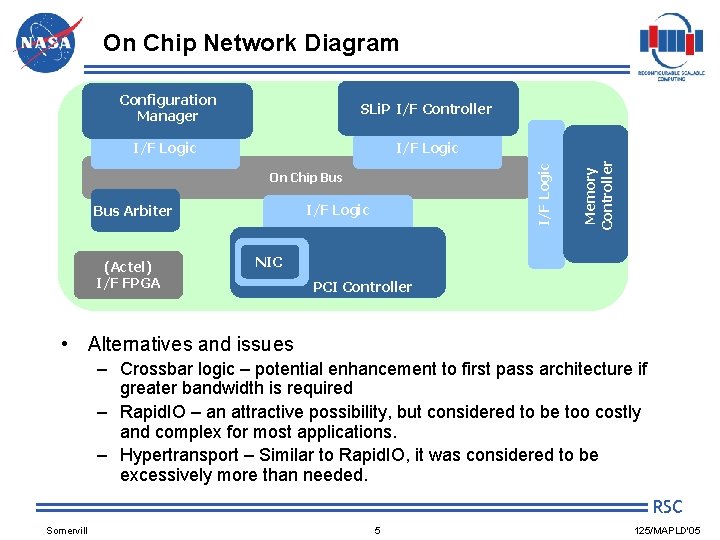

SLi. P I/F Controller I/F Logic Configuration Manager On Chip Bus I/F Logic Bus Arbiter (Actel) I/F FPGA Memory Controller On Chip Network Diagram NIC PCI Controller • Alternatives and issues – Crossbar logic – potential enhancement to first pass architecture if greater bandwidth is required – Rapid. IO – an attractive possibility, but considered to be too costly and complex for most applications. – Hypertransport – Similar to Rapid. IO, it was considered to be excessively more than needed. RSC Somervill 5 125/MAPLD'05

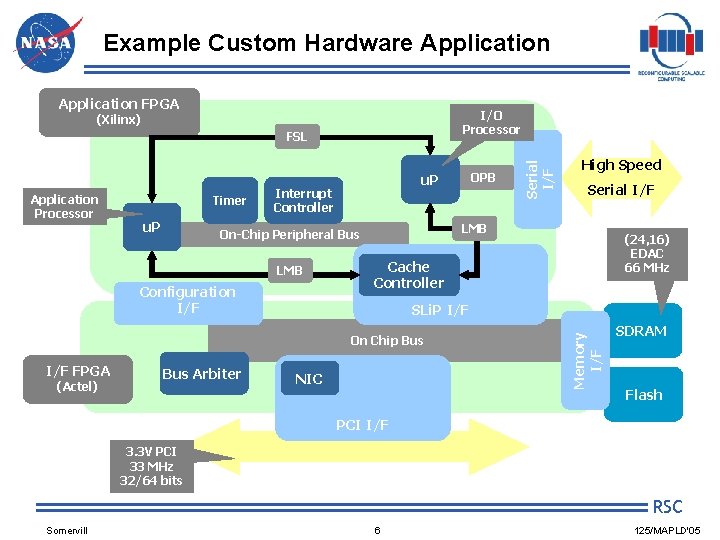

Example Custom Hardware Application FPGA FSL Timer u. P Interrupt Controller Configuration I/F (Actel) Bus Arbiter (24, 16) EDAC 66 MHz Cache Controller SLi. P I/F On Chip Bus I/F FPGA Serial I/F LMB On-Chip Peripheral Bus LMB High Speed NIC Memory I/F Application Processor OPB Serial I/F I/O Processor (Xilinx) SDRAM Flash PCI I/F 3. 3 V PCI 33 MHz 32/64 bits RSC Somervill 6 125/MAPLD'05

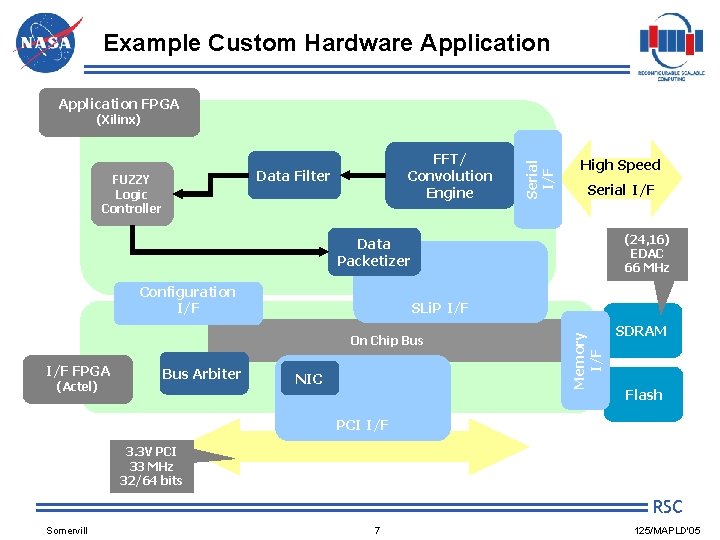

Example Custom Hardware Application FPGA FFT/ Convolution Engine Data Filter FUZZY Logic Controller Serial I/F (Xilinx) High Speed Serial I/F (24, 16) EDAC 66 MHz Data Packetizer Configuration I/F On Chip Bus I/F FPGA (Actel) Bus Arbiter NIC Memory I/F SLi. P I/F SDRAM Flash PCI I/F 3. 3 V PCI 33 MHz 32/64 bits RSC Somervill 7 125/MAPLD'05

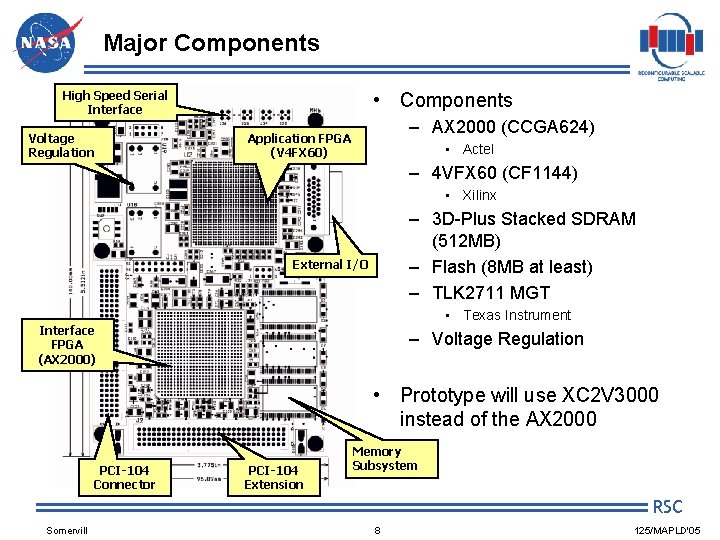

Major Components High Speed Serial Interface Voltage Regulation • Components – AX 2000 (CCGA 624) Application FPGA (V 4 FX 60) • Actel – 4 VFX 60 (CF 1144) • Xilinx – 3 D-Plus Stacked SDRAM (512 MB) – Flash (8 MB at least) – TLK 2711 MGT External I/O • Texas Instrument Interface FPGA (AX 2000) – Voltage Regulation • Prototype will use XC 2 V 3000 instead of the AX 2000 PCI-104 Connector PCI-104 Extension Memory Subsystem RSC Somervill 8 125/MAPLD'05

Systems Modeling • Development support with formal modeling – Petri nets providing performability modeling which considers both reliability and performance aspects in a unified model – Petri nets provides mathematically based rigorous approach to system evaluation and development • Petri nets converted to System. C models – To serve as faster lower level system simulation models – Provides step wise refinement of the model towards RTL while providing the eventual test bench for the final VHDL – System. C model provides simplified path to software evaluation for prospective applications RSC Somervill 9 125/MAPLD'05

Embedded Processing • Primary target microprocessor is the Microblaze. TM processor. – Leverage work done with XRTC – Design mitigated with XTMR tool (or manually) • u. Clinux (Let the penguins fly!) – Host to u. Clinux operating system in a pseudo-MP structure – Provides easy path to high level development for instrument applications (C, sockets, file systems, etc) – Development environment similar (if not identical) to typical Linux desktop RSC Somervill 10 125/MAPLD'05

Development Challenges and Issues • TMR of the reconfigurable logic (especially the Microblaze soft core processor) • Caching architecture across the SLi. P interface. • Fabrication with fine pitch CGA components (4 VFX 60) • Availability of various technologies – Non-volatile memory (FLASH and EEPROM) – Small form factor, high-efficiency DC voltage regulators RSC Somervill 11 125/MAPLD'05

Design Status as of 8/1/2005 • Currently still working architectural formulation, but the base structure is completed. – Reconfigurable nature of the prototype enables architecture trades post hardware development. • Schematics complete and layout proceeding. • Hardware prototypes expected at the end of the fiscal year. RSC Somervill 12 125/MAPLD'05

- Slides: 12