Preventing Interrupt Overload John Regehr Usit Duogsaa School

- Slides: 12

Preventing Interrupt Overload John Regehr, Usit Duogsaa, School of Computing, University of Utah Presented by Jiyong Park Seoul National University, Korea 2005. 2. 22.

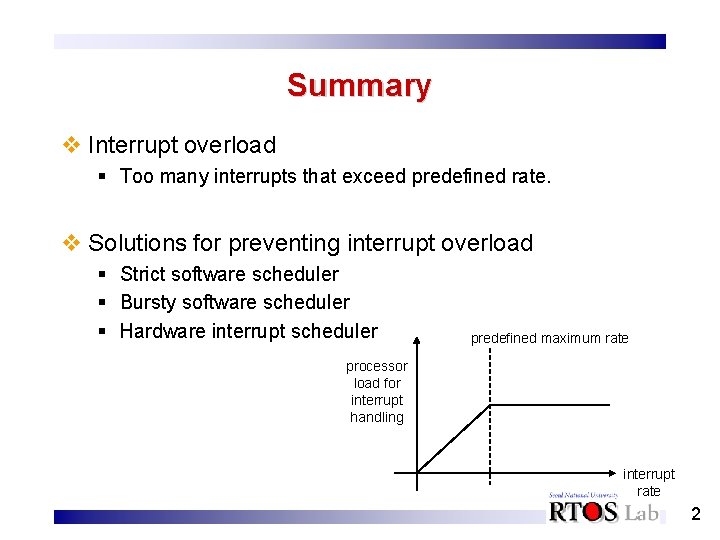

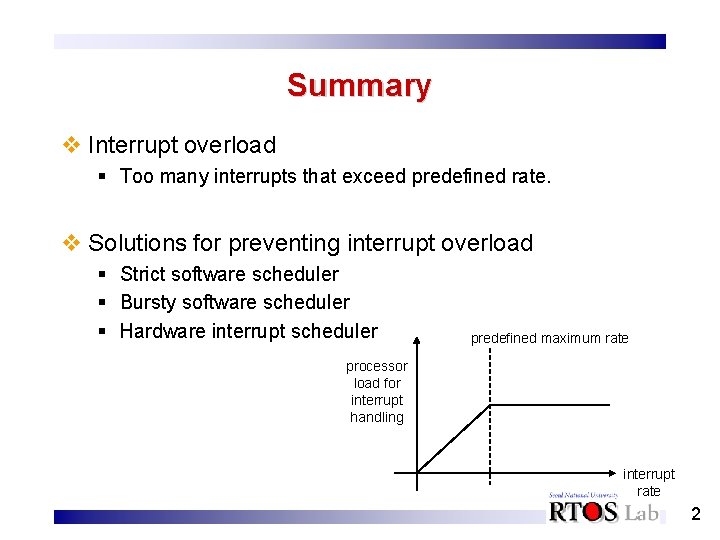

Summary v Interrupt overload § Too many interrupts that exceed predefined rate. v Solutions for preventing interrupt overload § Strict software scheduler § Bursty software scheduler § Hardware interrupt scheduler predefined maximum rate processor load for interrupt handling interrupt rate 2

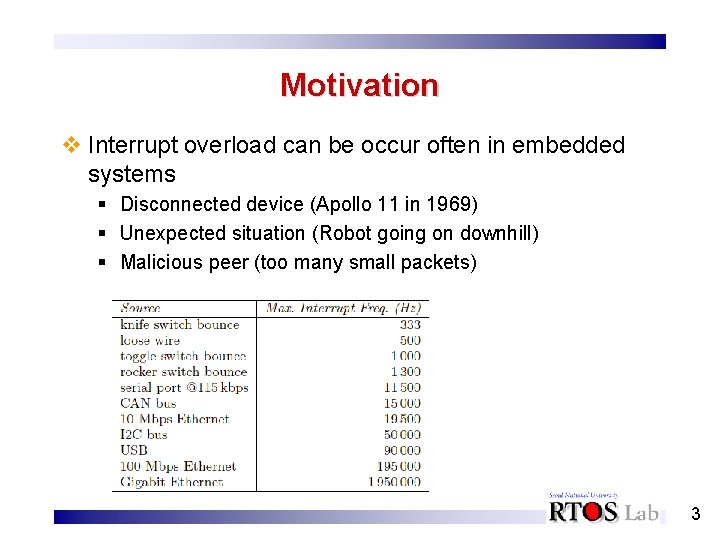

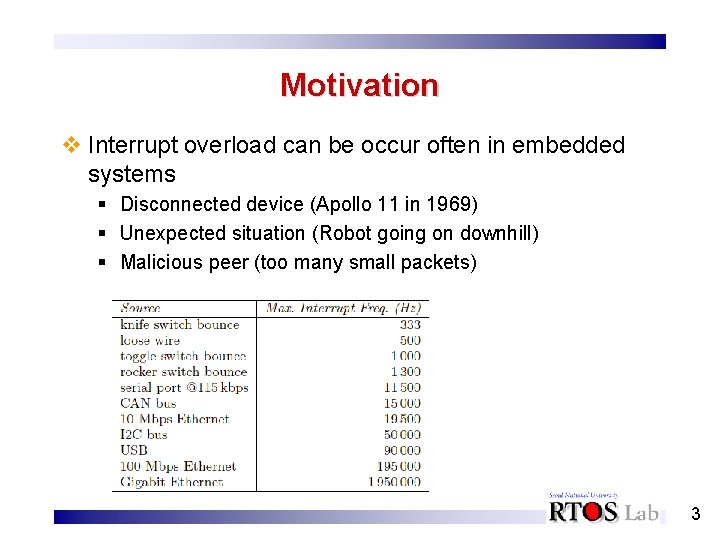

Motivation v Interrupt overload can be occur often in embedded systems § Disconnected device (Apollo 11 in 1969) § Unexpected situation (Robot going on downhill) § Malicious peer (too many small packets) 3

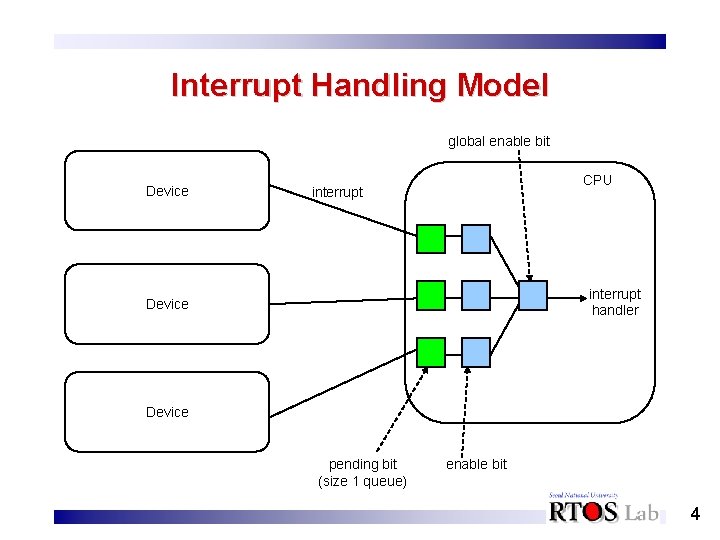

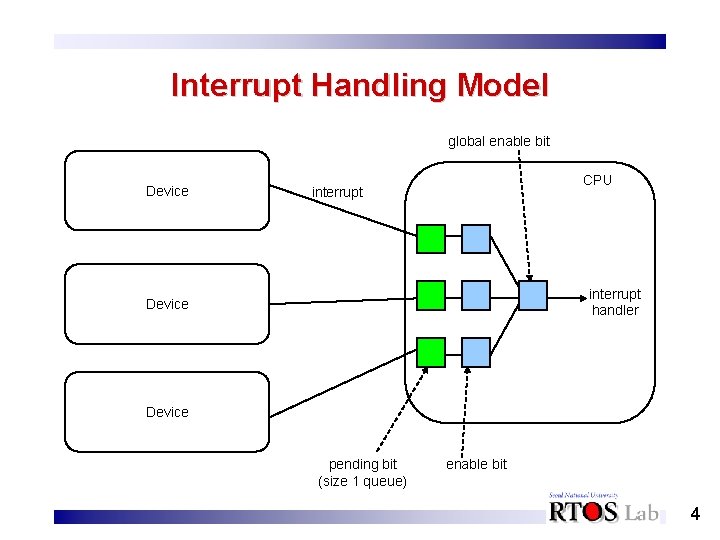

Interrupt Handling Model global enable bit Device CPU interrupt handler Device pending bit (size 1 queue) enable bit 4

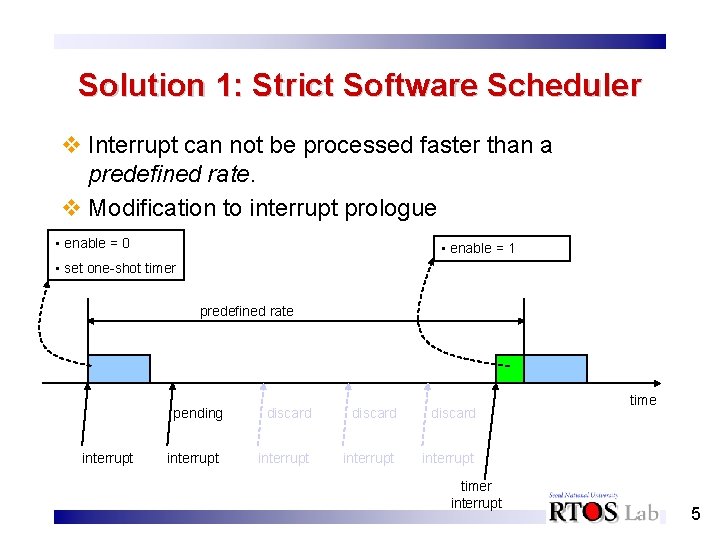

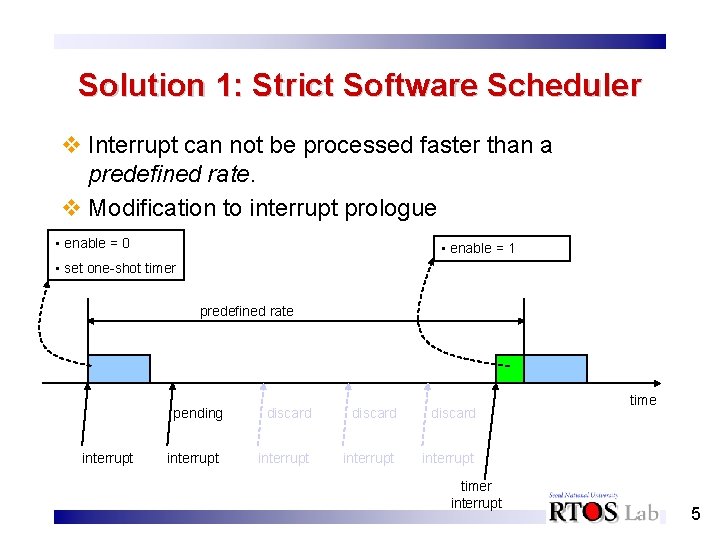

Solution 1: Strict Software Scheduler v Interrupt can not be processed faster than a predefined rate. v Modification to interrupt prologue • enable = 0 • enable = 1 • set one-shot timer predefined rate pending interrupt discard interrupt timer interrupt time 5

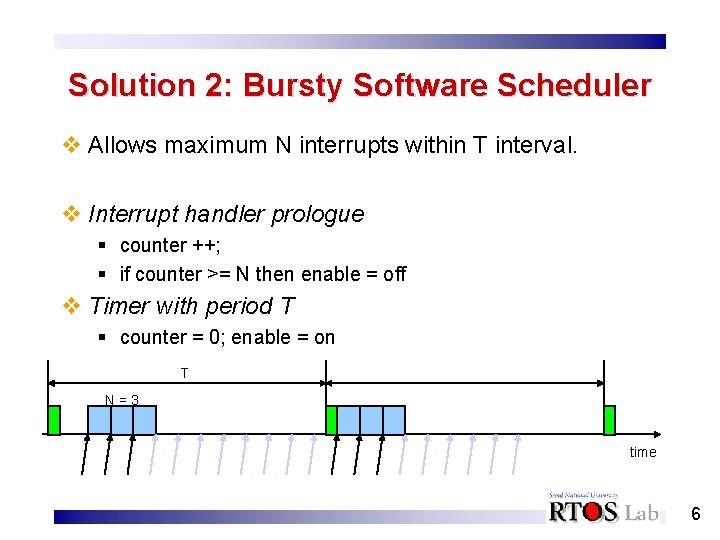

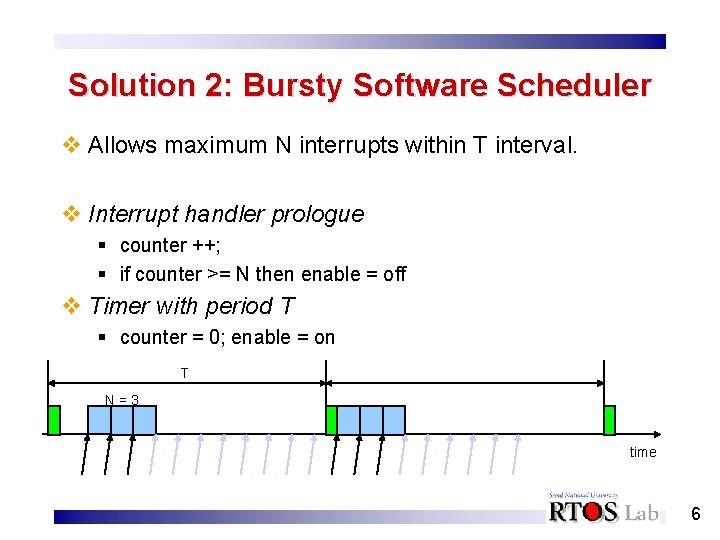

Solution 2: Bursty Software Scheduler v Allows maximum N interrupts within T interval. v Interrupt handler prologue § counter ++; § if counter >= N then enable = off v Timer with period T § counter = 0; enable = on T N=3 time 6

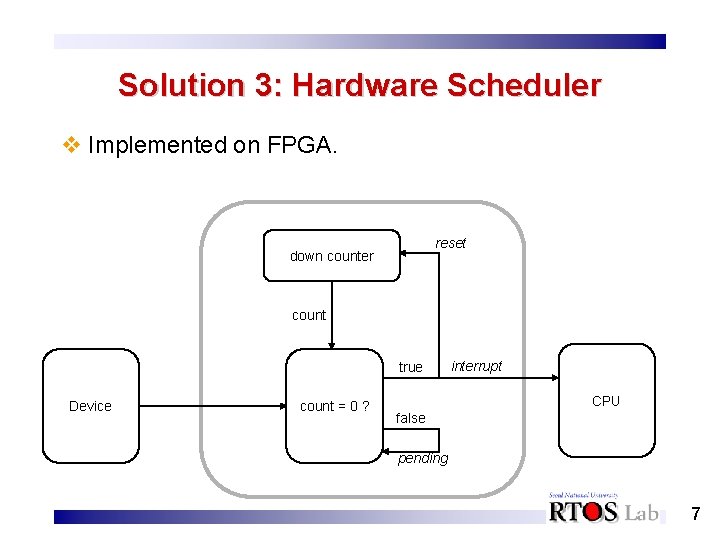

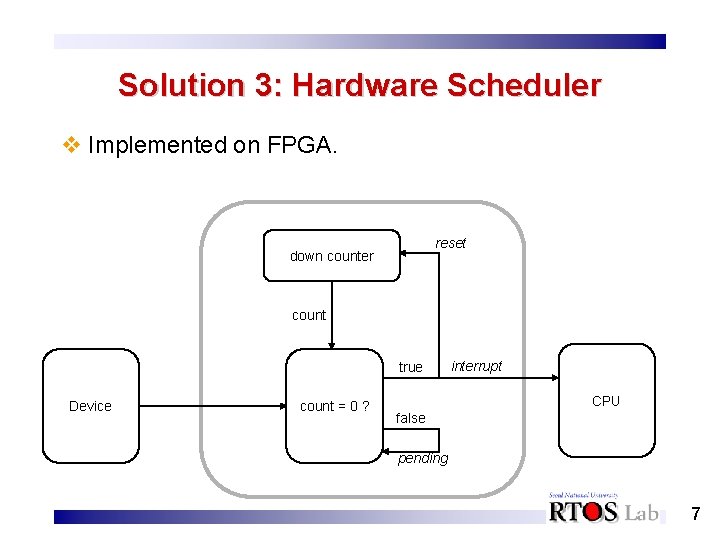

Solution 3: Hardware Scheduler v Implemented on FPGA. reset down counter count true Device count = 0 ? interrupt CPU false pending 7

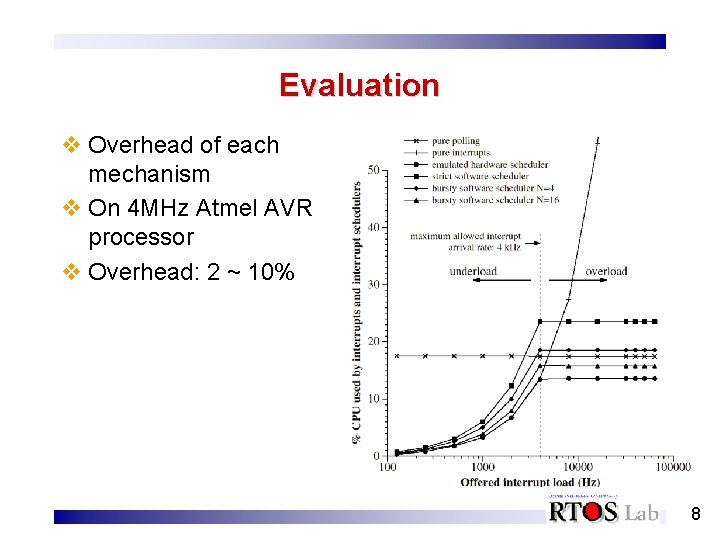

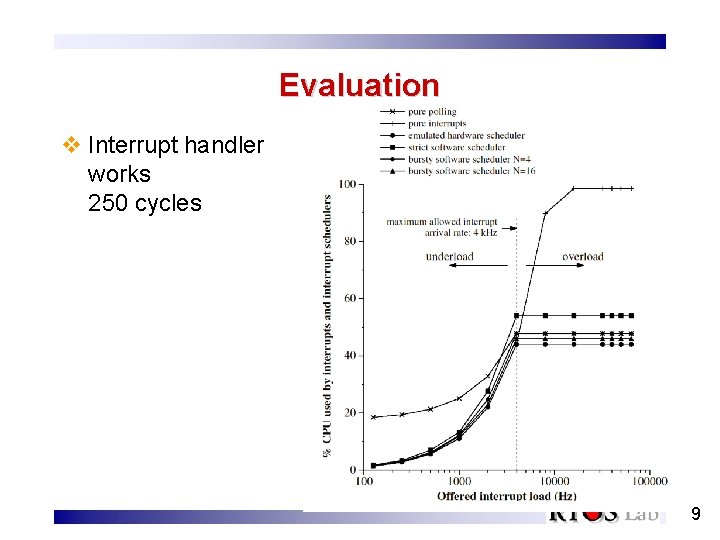

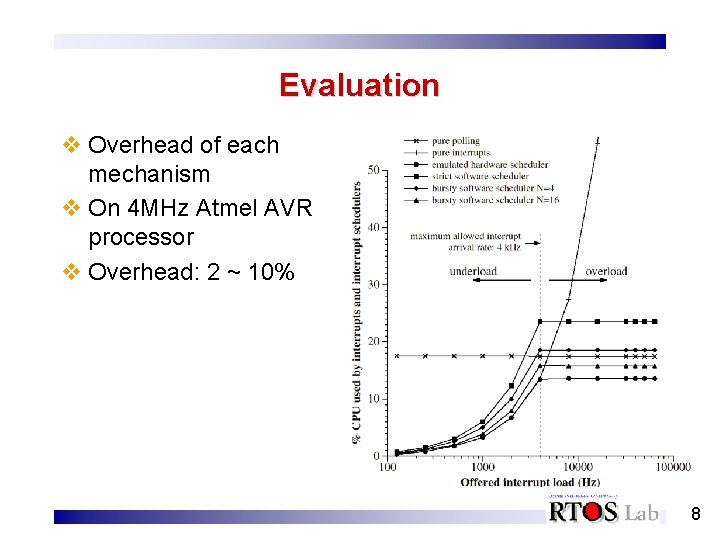

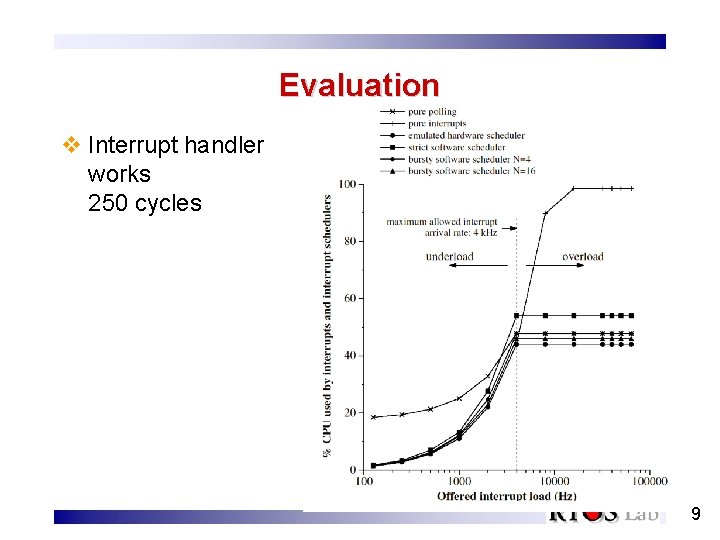

Evaluation v Overhead of each mechanism v On 4 MHz Atmel AVR processor v Overhead: 2 ~ 10% 8

Evaluation v Interrupt handler works 250 cycles 9

Related Work v Receive live-lock, Lazy Receiver Processing § § Switch to polling when overload Early demultiplexing Network centric Concentrate on maximizing throughput (no consideration to timely execution of application) v Interrupt Thread § Just delays interrupt overload. Does not prevent it. § Big overhead on very small embedded systems 10

Strong Points v Simple but very effective solution v Modeling the interrupt handler as periodic task (C, T) v The urgent need for preventing interrupt overload is well explained using various examples. v The interrupt scheduler is extended to support multiple interrupt sources. v Hardware solution requires only small amount of transistors (600). 11

Weak Points v Not very much 12