MSP 432 MCUs Training Part 3 Power System

- Slides: 7

MSP 432™ MCUs Training Part 3: Power System 1

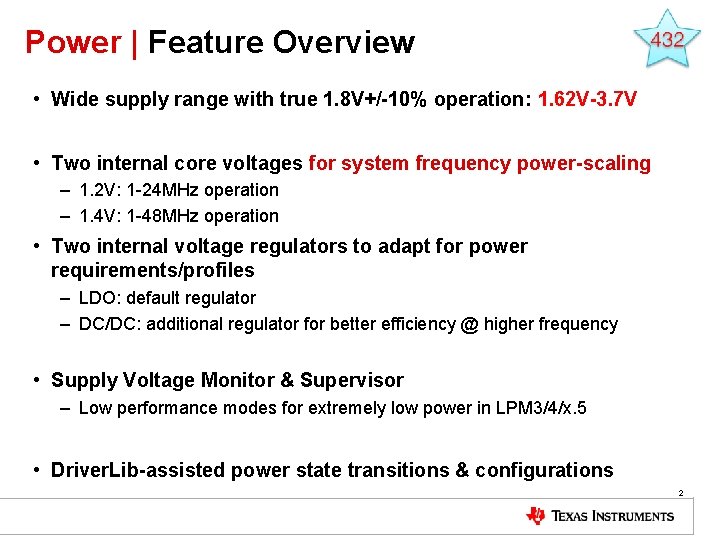

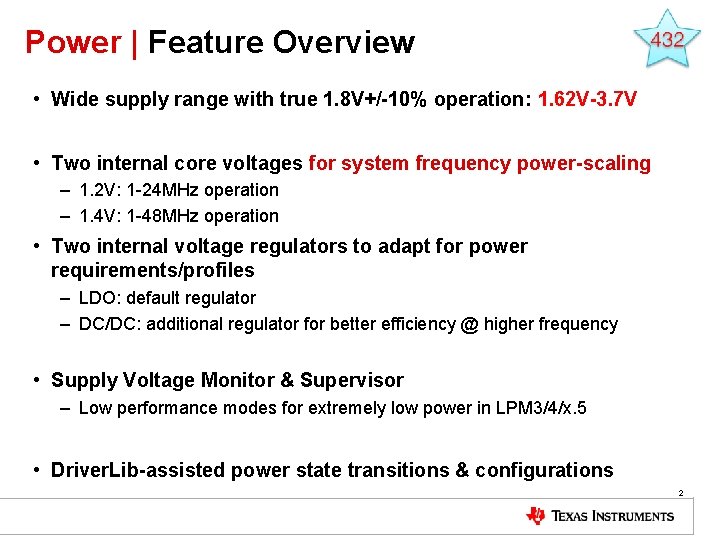

Power | Feature Overview • Wide supply range with true 1. 8 V+/-10% operation: 1. 62 V-3. 7 V • Two internal core voltages for system frequency power-scaling – 1. 2 V: 1 -24 MHz operation – 1. 4 V: 1 -48 MHz operation • Two internal voltage regulators to adapt for power requirements/profiles – LDO: default regulator – DC/DC: additional regulator for better efficiency @ higher frequency • Supply Voltage Monitor & Supervisor – Low performance modes for extremely low power in LPM 3/4/x. 5 • Driver. Lib-assisted power state transitions & configurations 2

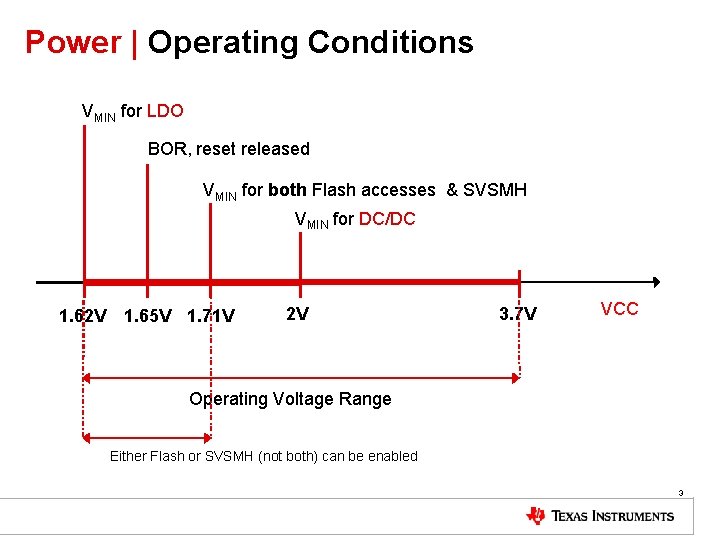

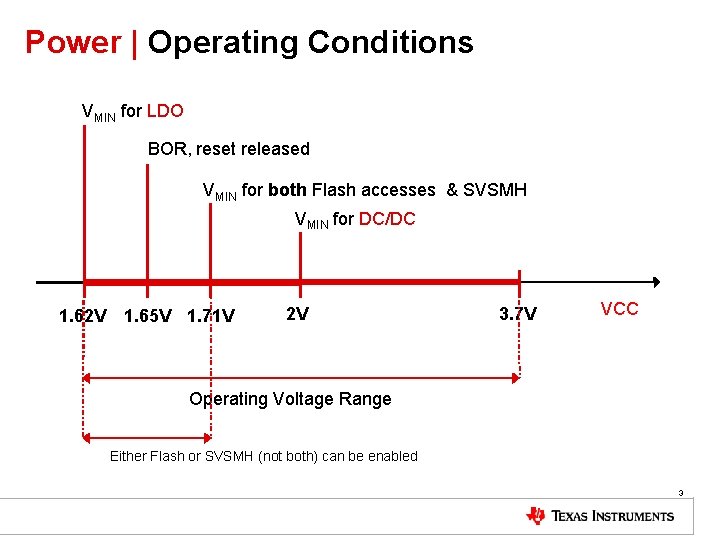

Power | Operating Conditions VMIN for LDO BOR, reset released VMIN for both Flash accesses & SVSMH VMIN for DC/DC 1. 62 V 1. 65 V 1. 71 V 2 V 3. 7 V VCC Operating Voltage Range Either Flash or SVSMH (not both) can be enabled 3

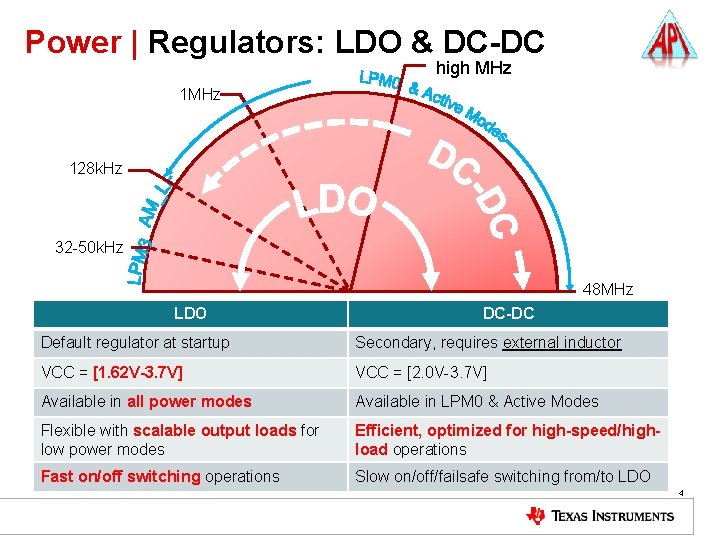

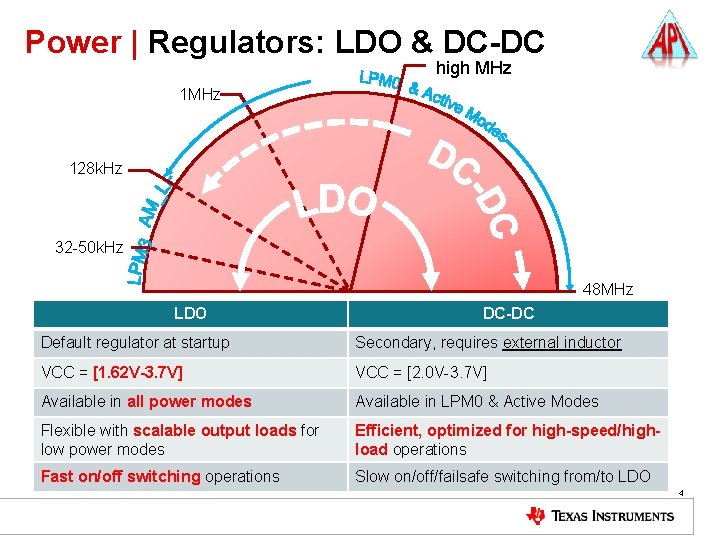

Power | Regulators: LDO & DC-DC high MHz 128 k. Hz 32 -50 k. Hz 48 MHz LDO DC-DC Default regulator at startup Secondary, requires external inductor VCC = [1. 62 V-3. 7 V] VCC = [2. 0 V-3. 7 V] Available in all power modes Available in LPM 0 & Active Modes Flexible with scalable output loads for low power modes Efficient, optimized for high-speed/highload operations Fast on/off switching operations Slow on/off/failsafe switching from/to LDO 4

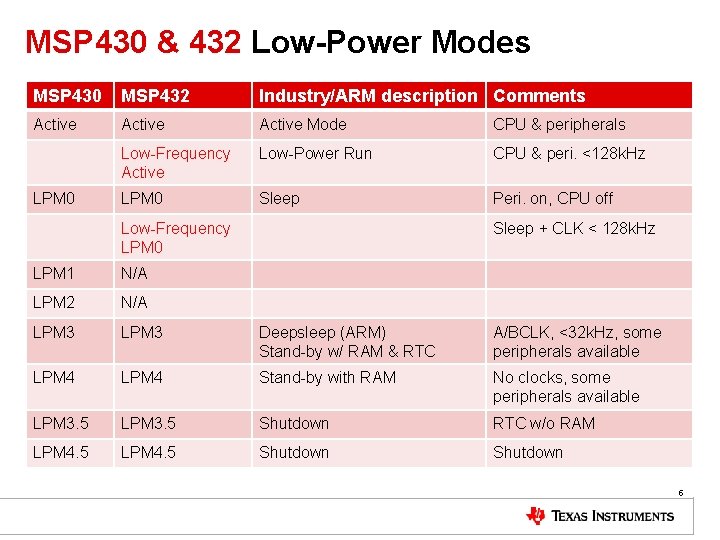

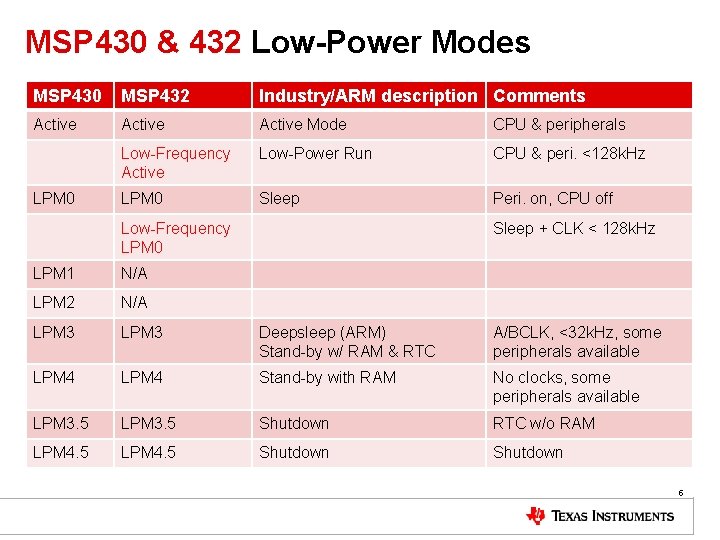

MSP 430 & 432 Low-Power Modes MSP 430 MSP 432 Industry/ARM description Comments Active Mode CPU & peripherals Low-Frequency Active Low-Power Run CPU & peri. <128 k. Hz LPM 0 Sleep Peri. on, CPU off LPM 0 Low-Frequency LPM 0 Sleep + CLK < 128 k. Hz LPM 1 N/A LPM 2 N/A LPM 3 Deepsleep (ARM) Stand-by w/ RAM & RTC A/BCLK, <32 k. Hz, some peripherals available LPM 4 Stand-by with RAM No clocks, some peripherals available LPM 3. 5 Shutdown RTC w/o RAM LPM 4. 5 Shutdown 5

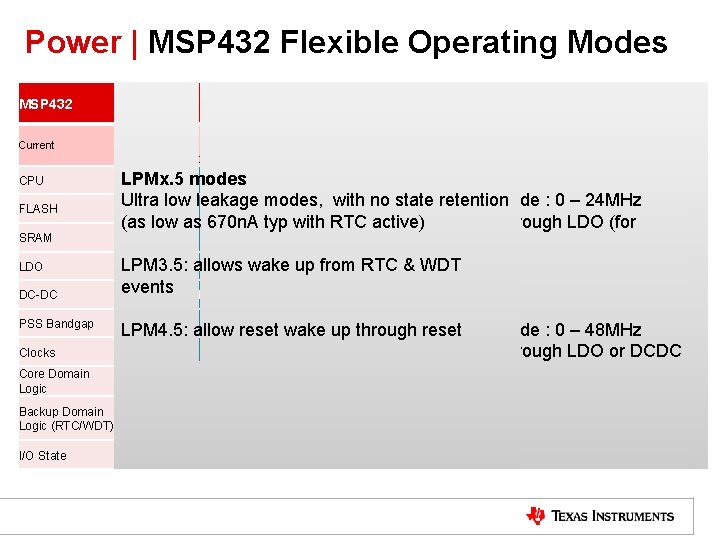

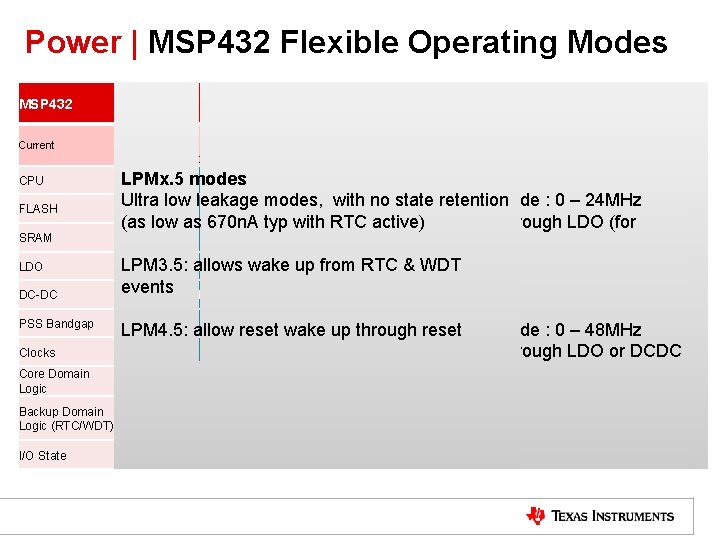

Power | MSP 432 Flexible Operating Modes MSP 432 ACTIVE 100 u. A/MHz Current (DCDC) 166 u. A/MHz (LDO) CPU FLASH SRAM LDO DC-DC PSS Bandgap Clocks Core Domain Logic Backup Domain Logic (RTC/WDT) I/O State Low-Frequency (Active/LPM 0) LPM 0 LPM 3 LPM 4 LPM 3. 5 LPM 4. 5 70 u. A 65 u. A/MHz (DCDC) 100 u. A/MHz (LDO) <900 n. A <670 n. A <100 n. A LPMx. 5 modes Active modes at Core Voltage 0 Retention Low-Frequency modes Ultra low leakage Low power, modes, medium with noperformance state retention mode : 0 – 24 MHz LPM 3 & option LPM 4 Special low power low frequency (as low as 670 n. A Can be typused with RTC with regulation active) either through LDO (for Ultra low leakage available for both active and LPM 0 modes Retention maximum efficiency) or DCDC modes with full state Total device LPM 0 current consumption below In LDO mode Lowwake Drive Mode In LDO mode Low Drive Mode LPM 3. 5: allows up from RTC & WDT (as&low as CPU off, all retention peripherals clocks 80 u. A events In DCDC mode active 900 n. A typ with RTC Active modes at Core Voltage 1 CPU execution at 128 KHz active) max, Flash, Sampled Mode Sampled LPM 4. 5: allow High reset performance, wake up through high efficiency reset mode : 0 –Mode 48 MHz SRAM and peripherals remain active at the BCLKthrough Only BCLK Can be used with regulation. Only either LDO or DCDC lower speeds (for maximum efficiency) Retention Active Retention

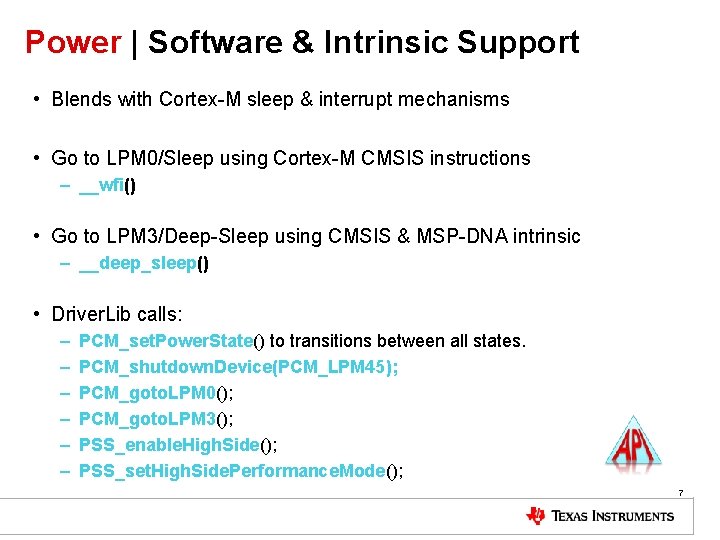

Power | Software & Intrinsic Support • Blends with Cortex-M sleep & interrupt mechanisms • Go to LPM 0/Sleep using Cortex-M CMSIS instructions – __wfi() • Go to LPM 3/Deep-Sleep using CMSIS & MSP-DNA intrinsic – __deep_sleep() • Driver. Lib calls: – – – PCM_set. Power. State() to transitions between all states. PCM_shutdown. Device(PCM_LPM 45); PCM_goto. LPM 0(); PCM_goto. LPM 3(); PSS_enable. High. Side(); PSS_set. High. Side. Performance. Mode(); 7