Lect8 FF Continued 1 2 Latch Timing Problem

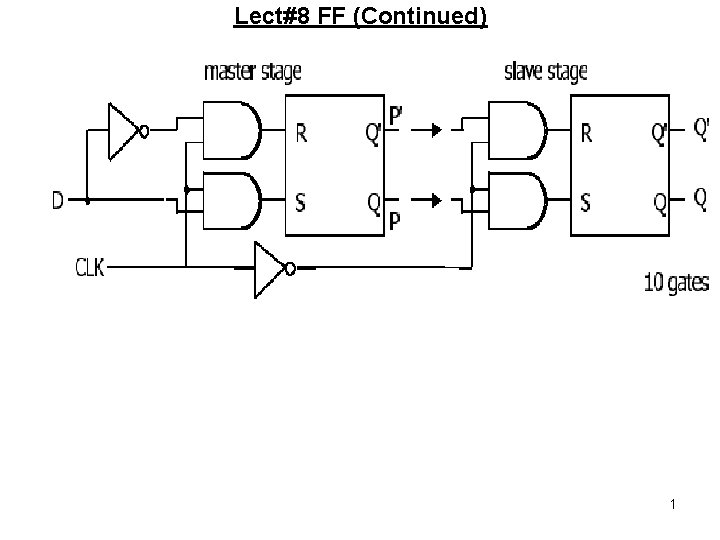

Lect#8 FF (Continued) 1

2

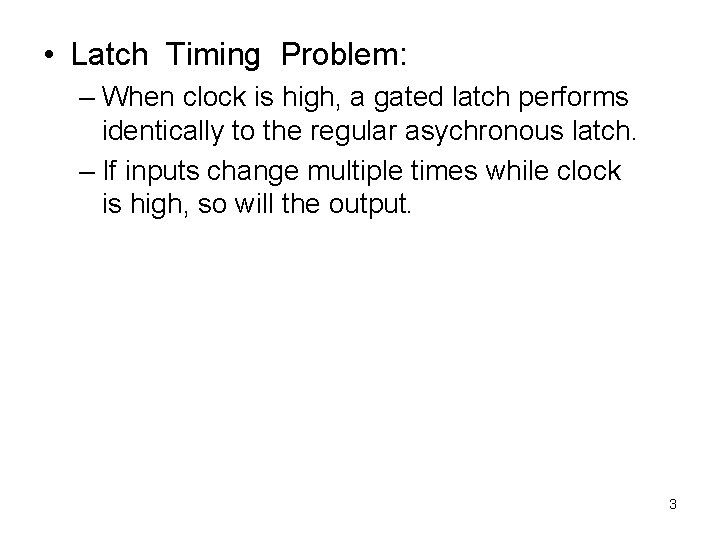

• Latch Timing Problem: – When clock is high, a gated latch performs identically to the regular asychronous latch. – If inputs change multiple times while clock is high, so will the output. 3

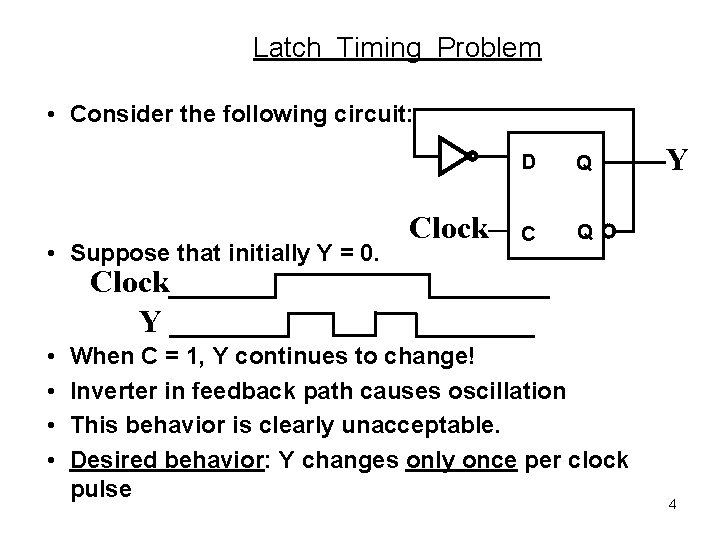

Latch Timing Problem • Consider the following circuit: • Suppose that initially Y = 0. Clock D Q C Q Y Clock Y • • When C = 1, Y continues to change! Inverter in feedback path causes oscillation This behavior is clearly unacceptable. Desired behavior: Y changes only once per clock pulse 4

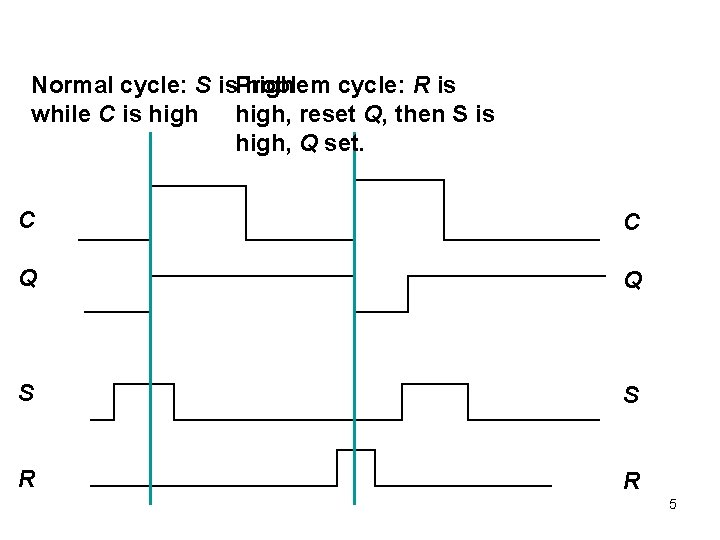

Normal cycle: S is. Problem high cycle: R is while C is high, reset Q, then S is high, Q set. C C Q Q S S R R 5

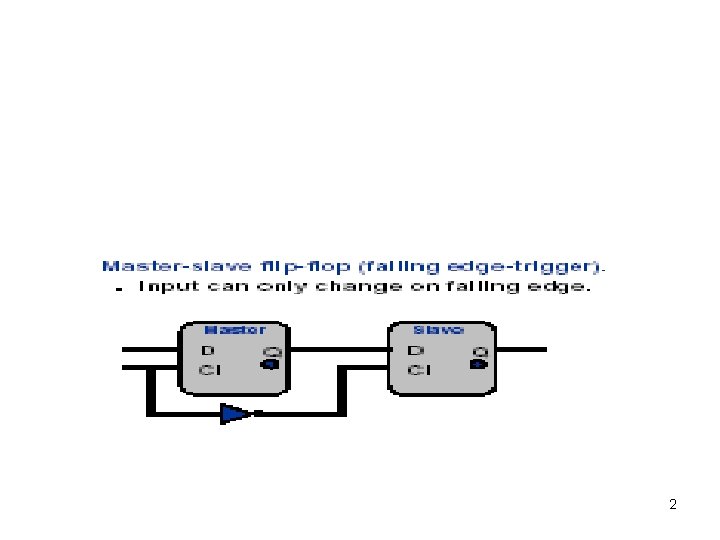

• Solution: – Rising edge-triggered flip-flop. • Inputs are latched to the outputs on the rising edge and ignored until the next rising edge – Falling edge-triggered flip-flop • Inputs considered only on the falling edge of the clock Master Slave Flip Flop 6

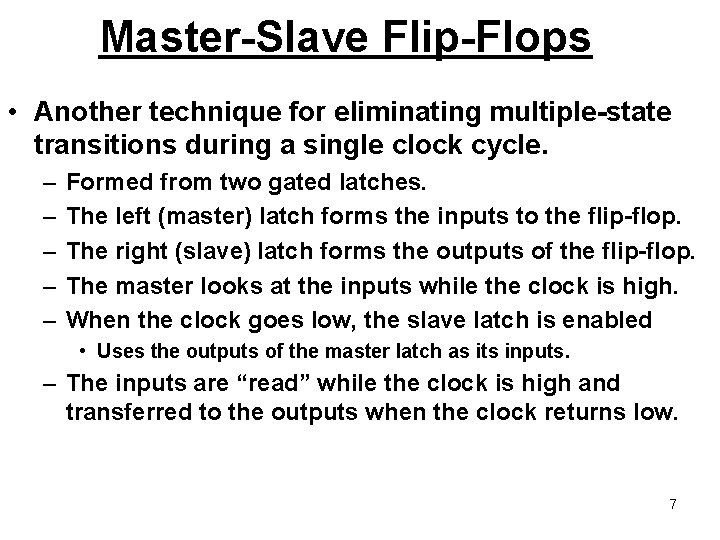

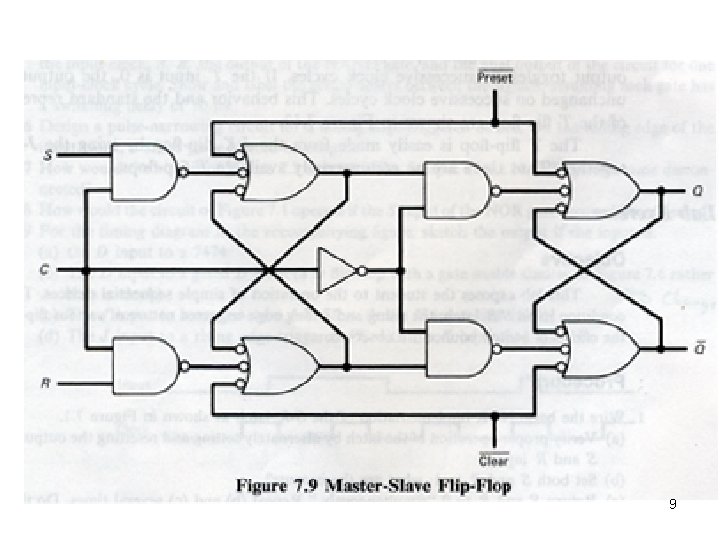

Master-Slave Flip-Flops • Another technique for eliminating multiple-state transitions during a single clock cycle. – – – Formed from two gated latches. The left (master) latch forms the inputs to the flip-flop. The right (slave) latch forms the outputs of the flip-flop. The master looks at the inputs while the clock is high. When the clock goes low, the slave latch is enabled • Uses the outputs of the master latch as its inputs. – The inputs are “read” while the clock is high and transferred to the outputs when the clock returns low. 7

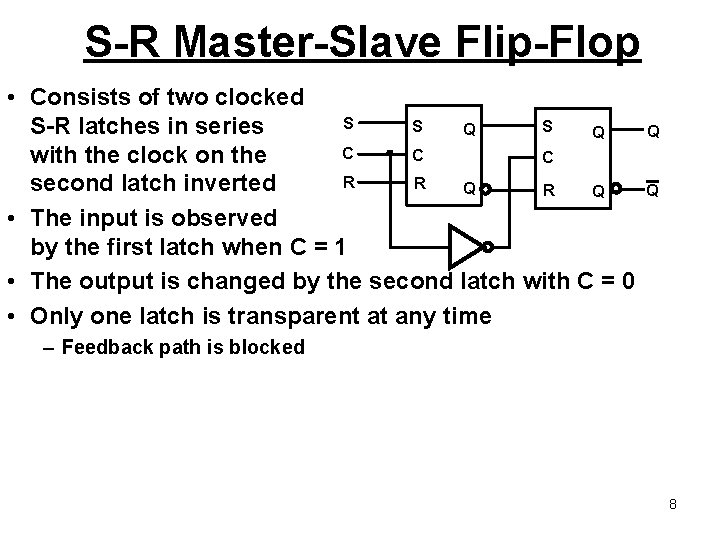

S-R Master-Slave Flip-Flop • Consists of two clocked S S-R latches in series Q Q C C with the clock on the C R R second latch inverted Q R Q • The input is observed by the first latch when C = 1 • The output is changed by the second latch with C = 0 • Only one latch is transparent at any time Q Q – Feedback path is blocked 8

9

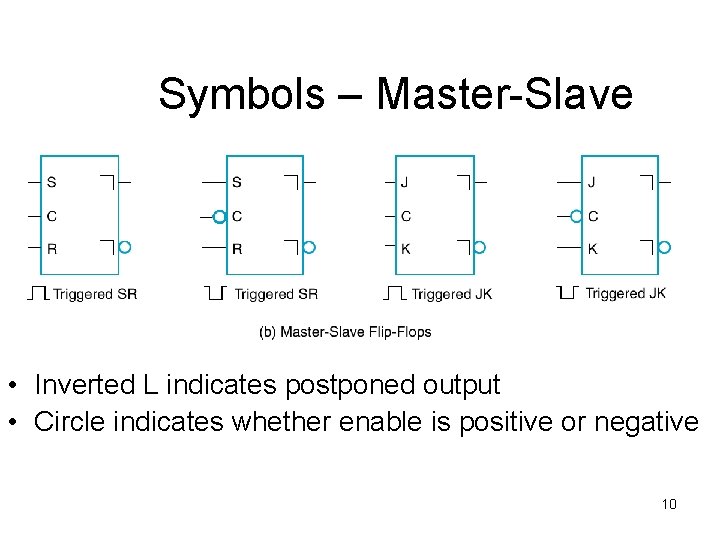

Symbols – Master-Slave • Inverted L indicates postponed output • Circle indicates whether enable is positive or negative 10

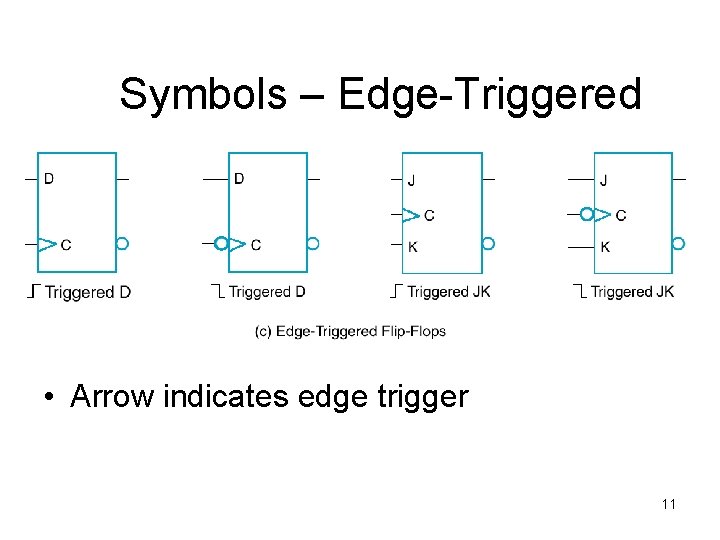

Symbols – Edge-Triggered • Arrow indicates edge trigger 11

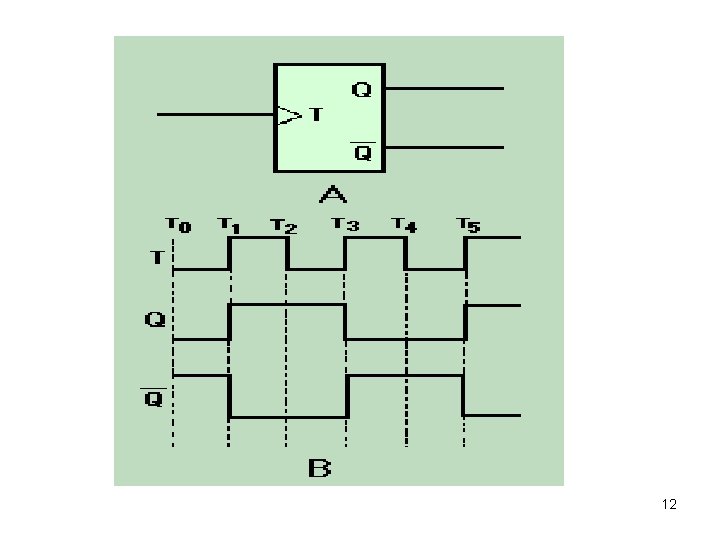

12

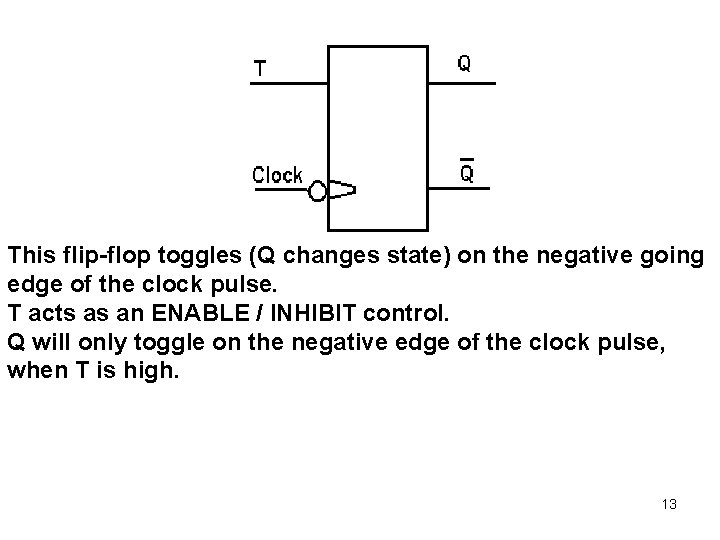

This flip-flop toggles (Q changes state) on the negative going edge of the clock pulse. T acts as an ENABLE / INHIBIT control. Q will only toggle on the negative edge of the clock pulse, when T is high. 13

14

15

- Slides: 15