Komputery macierzowe Komputery macierzowe Co to jest komputer

- Slides: 23

Komputery macierzowe

Komputery macierzowe • Co to jest komputer macierzowy • Organizacje wieloprocesorowe – SMP – CC-NUMA • • Utrzymanie spójności pamięci podręcznych Topologie sieci połączeń Przykłady: ILLIAC IV, Cray-1, DAP Przyszłość

Co to jest komputer macierzowy • Komputer macierzowy to synchroniczna wieloprocesorowa maszyna ze współdzieloną pamięcią. • Komputery macierzowe tradycyjnie należą do klasy SIMD. Pierwsze takie maszyny zaczęły pojawiać się w latach 60 -tych XX wieku. • Żaden SISD z rozszerzeniami SIMD nie jest w stanie zastąpić superkomputera. • Komputer macierzowy nadzoruje jednostka sterująca. W komunikacji z człowiekiem pośredniczy host (komputer „front-end”).

Komputery macierzowe. Mylące nazewnictwo • Bardzo często termin array processor jest synonimem komputera macierzowego. • Określenie array processor oraz vector processor używane są zamiennie. • Bardzo często procesorem macierzowym (tablicowym) nazywane jest urządzenie peryferyjne wykonujące tylko wektorowe elementy programów. • Obecnie komputery macierzowe rozumiane jako maszyny czysto SIMD są rzadkością.

Organizacje wieloprocesorowe • W odróżnieniu od PC, superkomputer działa równolegle w sensie sprzętowym. • Każdy procesor komp. mac. to jednostka przetwarzająca PU (PE). • Wszystkie PU pracują na blokach jednej pamięci operacyjnej. Ważne jest prawidłowe aktualizowanie pamięci, tak aby każdy PU miał jej właściwy obraz.

Komputery o pamięci rozproszonej • Najnowsze superkomputery są budowane w formy klastrów o rozproszonej pamięci. Klaster składa się z wielu pojedynczych (super)komputerów połączonych szybką siecią (Beowulf). Jest to inne podejście niż w przypadku komp. mac. , jednak o wiele tańsze i kilkakrotnie bardziej wydajne.

Najstarsze i najczęściej stosowane rozwiązanie – SMP • Jedna pamięć współużytkowana przez wszystkie synchronicznie działające PU. Czas dostępu każdego PU do pamięci jest taki sam. • Jednostka sterująca (CU lub MCU) nadzoruje wszystkie PU. Ilość PU jest ograniczona (od 16) do 64 – powyżej tej liczby znacznie spada wydajność całego systemu. • Ze względu na sposób połączeń miedzy procesorami SMP dzieli się na trzy klasy.

Klasy SMP: Wspólna magistrala z podziałem czasu • Najprostsze rozwiązanie podobne do tego z systemów jednoprocesorowych. • Podział czasu oznacza, że w danej chwili czasu tylko jeden moduł steruje magistralą – pozostałe są blokowane. • Zalety: elastyczność rozbudowy, niezawodność. • Wady: ograniczona wydajność magistrali może ją doprowadzić do postaci „wąskiego gardła”.

Klasy SMP: Pamięć wieloportowa • Każdy procesor i urządzenie I/O ma niezależny i bezpośredni dostęp do dowolnego bloku pamięci. • Nie ma możliwości poinformowania innych procesorów o aktualizacji pamięci, dlatego stosuje się zapis jednoczesny (zmiana cache procesora równa się zmianie określonych danych w pamięci głównej).

Klasy SMP: Pamięć wieloportowa • Dostęp każdego PU do bloku pamięci realizuje tzw. architektura przełączana. Jest to sieć układów logicznych działająca jak zestaw przełączników (switches). • Dwa najczęściej stosowane systemy przełączania to wybierak krzyżowy (crossbar switch) i sieć omega.

Wybierak krzyżowy • Szybki dostęp wielu procesorów jednocześnie do różnych bloków pamięci. Wydajność spada w przypadku odwoływania się wielu procesorów do tego samego bloku pamięci jednocześnie. • Dla n procesorów i n bloków pamięci trzeba n 2 przełączników. punkt przełączający

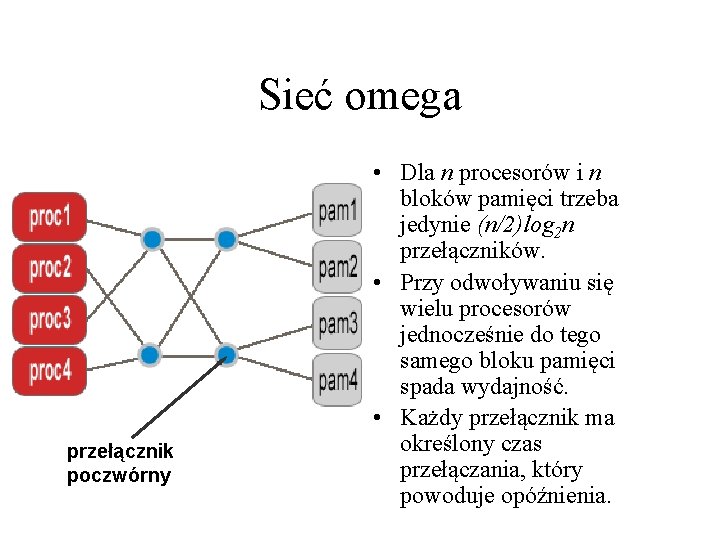

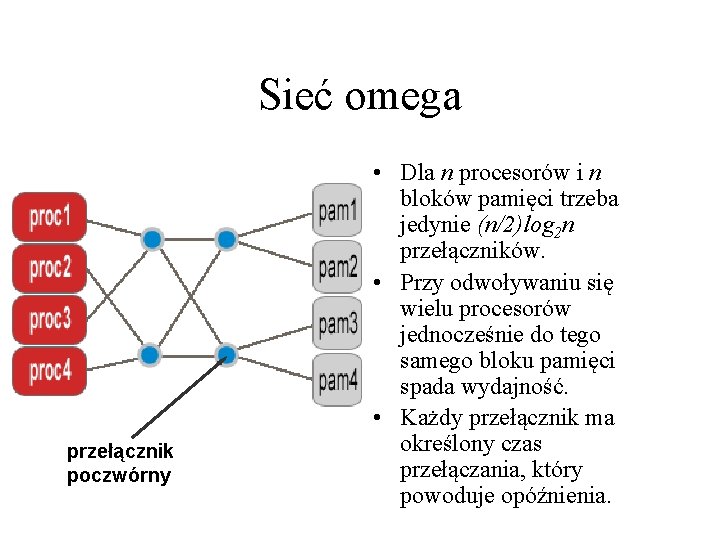

Sieć omega przełącznik poczwórny • Dla n procesorów i n bloków pamięci trzeba jedynie (n/2)log 2 n przełączników. • Przy odwoływaniu się wielu procesorów jednocześnie do tego samego bloku pamięci spada wydajność. • Każdy przełącznik ma określony czas przełączania, który powoduje opóźnienia.

Klasy SMP: Centralna jednostka sterująca (CU lub MCU) • Najstarsze rozwiązanie SMP, obecnie należy do rzadkości. • CU inicjuje i nadzoruje pracę wszystkich PU. • Rozwiązanie podobne do rozwiązania ze wspólną magistralą, tutaj także wadą jest ograniczona wydajność – w tym przypadku CU. • Realizacje: ILLIAC IV, Cray-1, DAP i większość pierwszych superkomputerów.

Nowoczesne rozwiązanie NUMA/CC-NUMA • Czas dostępu poszczególnych procesorów do bloków pamięci zależy od rejonu pamięci, którego ten dostęp dotyczy. Teoretycznie liczba procesorów może być nieograniczona. • NUMA składa się z węzłów sprzęgniętych siecią połączeń. Dostęp do pamięci „cudzej” (odległe węzły) jest dużo wolniejszy niż do pamięci „własnej”. • CC-NUMA dodatkowo zachowuje spójność pamięci podręcznych.

Utrzymywanie spójności pamięci podręcznych (cache coherence ) • Każdy PU ma własny cache oraz dostęp do pamięci wspólnej. Musi być zastosowane rozwiązanie zapewniające każdemu PU dostęp do aktualnego obrazu pamięci wspólnej. • Wyróżnia się rozwiązania programowe (wolniejsze) i sprzętowe (szybsze).

Utrzymywanie spójności pamięci podręcznych (cache coherence ) • Rozwiązanie programowe – kompilator reorganizuje kod w przypadku wykrycia miejsca potencjalnej niespójności. • Rozwiązania sprzętowe - protokoły spójności: podglądania, katalogowe (realizacja np. w NUMA), MESI (realizacja np. w SMP).

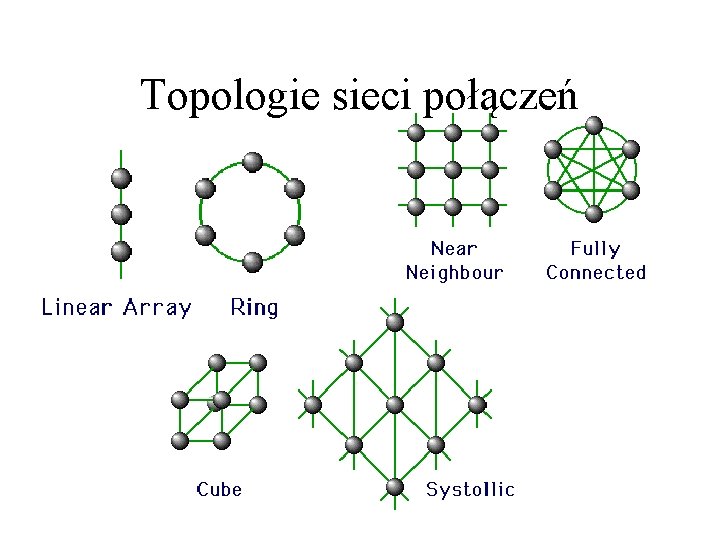

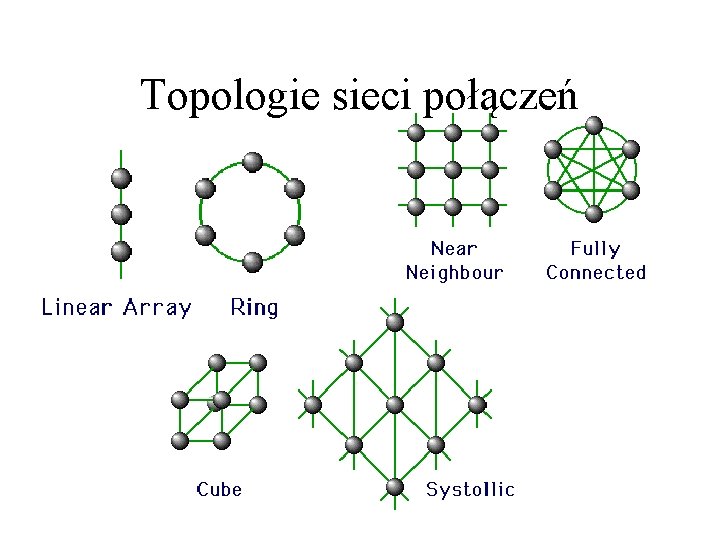

Topologie sieci połączeń

Topologie sieci połączeń • Realizacja połączeń pomiędzy PU (topologia) jest bardzo ważnym zagadnieniem wpływającym na wydajność całego systemu. • Należy projektować taką topologię, która będzie szybka w działaniu i odporna na uszkodzenie któregoś z procesorów.

ILLIAC IV

ILLIAC IV

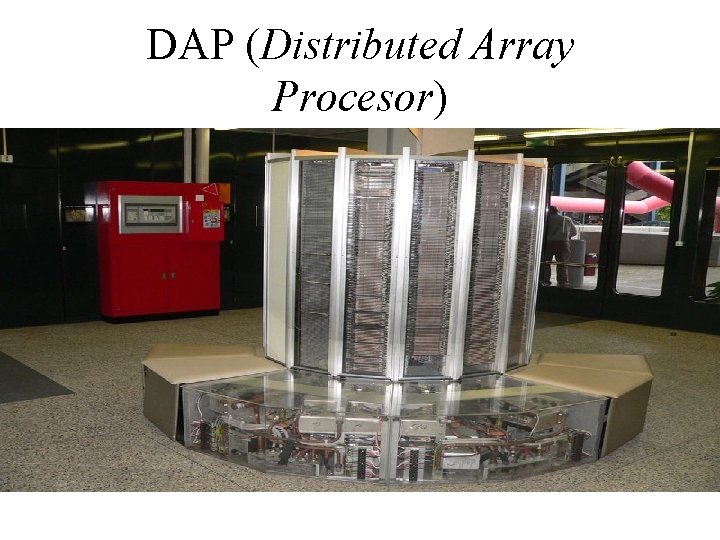

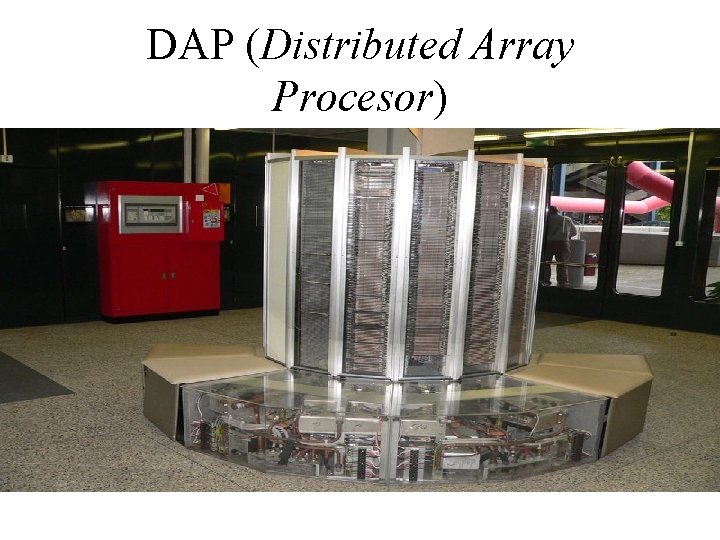

DAP (Distributed Array Procesor)

Cray-1

Przyszłość • Obecnie komputery macierzowe klasy SIMD należą do maszyn bardzo niszowych wykorzystywanych głównie w realizacjach systemów czasu rzeczywistego. • Kierunek rozwoju maszyn realizujących obliczenia na wielką skalę to systemy klasy MIMD z pamięcią rozproszoną. Klastry i niejednorodny dostęp do pamięci (CC-NUMA) wskazują przyszłość superkomputerów. • Ciągle jednak powstają superkomputery „w jednej obudowie”. Przykładem może być Cray XD 1 z roku 2005.