Information Calcul Communication Systmes Informatiques Leon 2 Mmoires

- Slides: 8

Information, Calcul, Communication Systèmes Informatiques – Leçon 2: Mémoires Hiérarchiques – Clip 4: Implémentation B. Falsafi, A. Schiper, W. Zwaenepoel, A. Ailamaki, commentaire: P. Janson 1/8 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

Où en sommes-nous ? 1. Technologie des mémoires 2. Hiérarchie de mémoires Concept Objectif Réalisation 2. 3. 4. 5. 6. 7. 8. 9. 2/8 Lecture Ecriture Gestion LRU Exemple Pourquoi – Localité 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

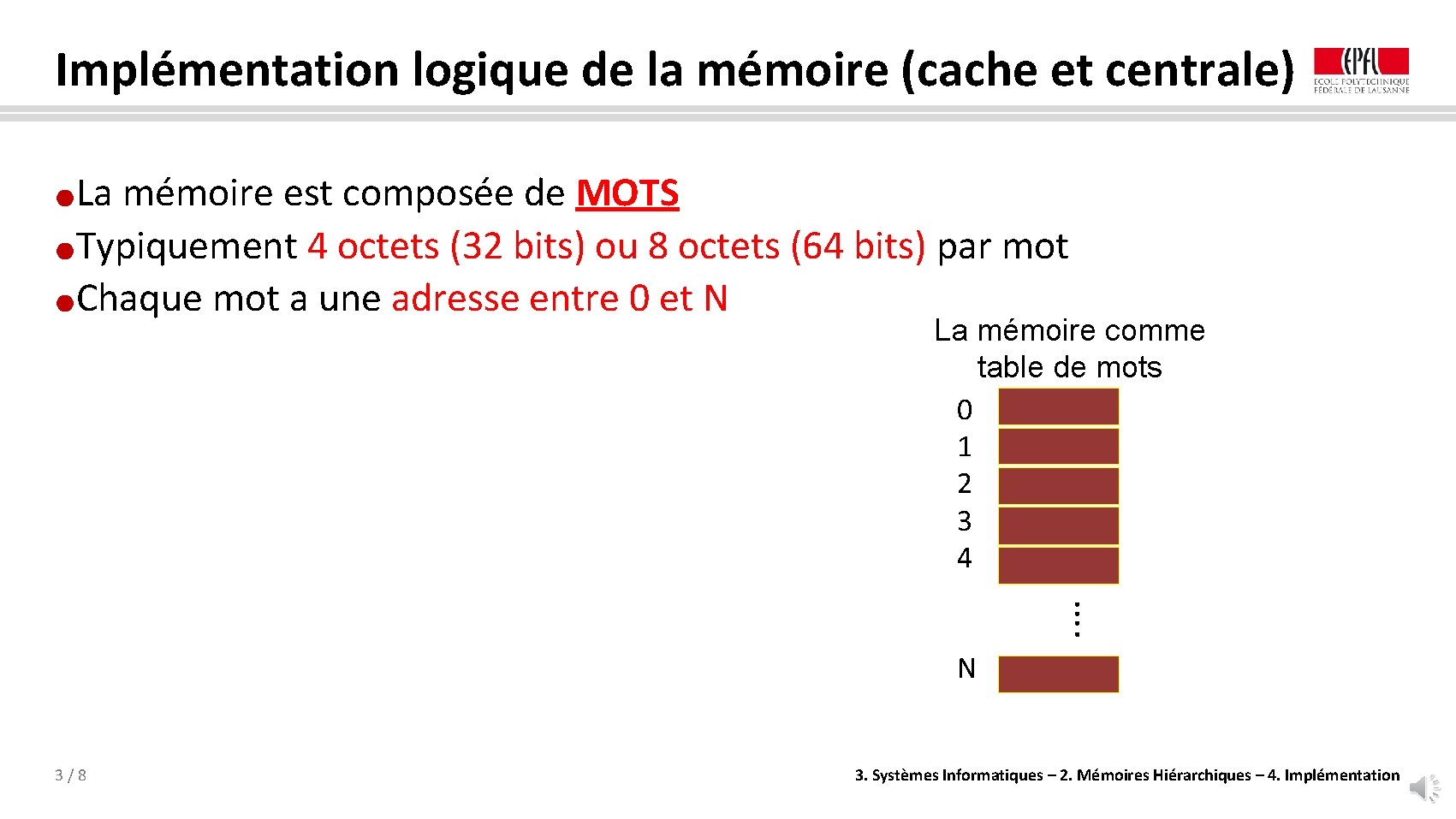

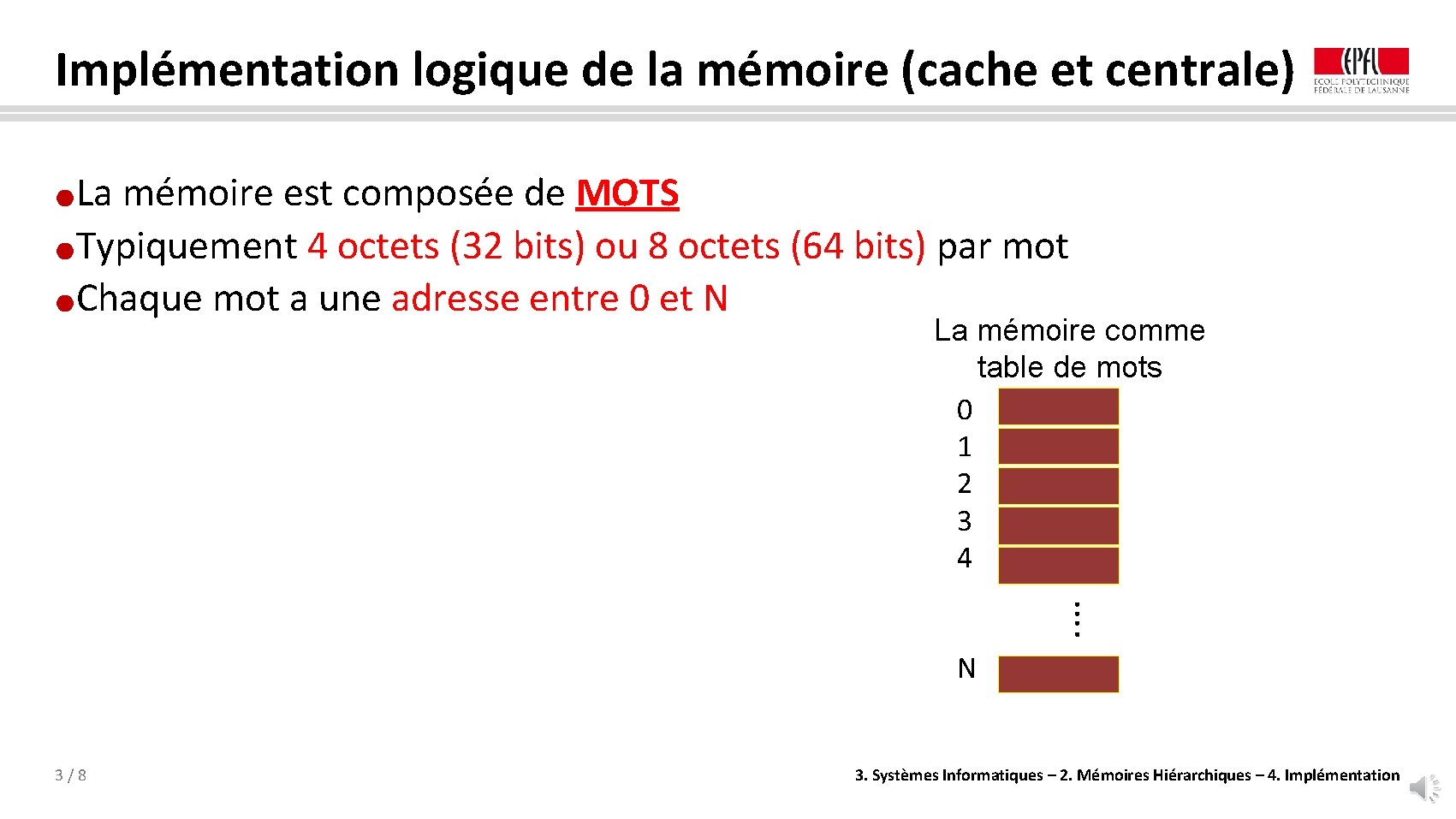

Implémentation logique de la mémoire (cache et centrale) La mémoire est composée de MOTS ●Typiquement 4 octets (32 bits) ou 8 octets (64 bits) par mot ●Chaque mot a une adresse entre 0 et N ● La mémoire comme table de mots 0 1 2 3 4 …. N 3/8 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

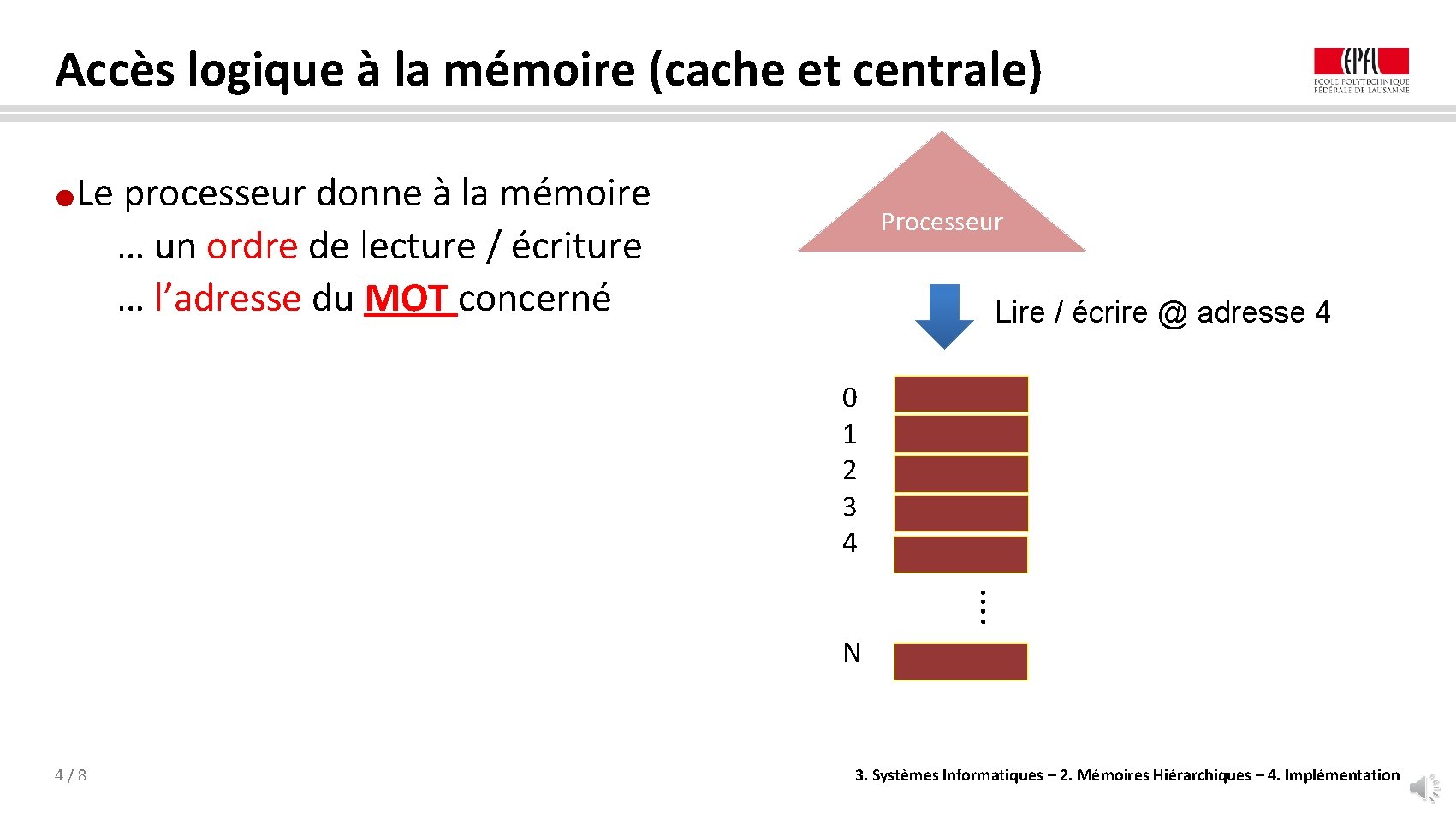

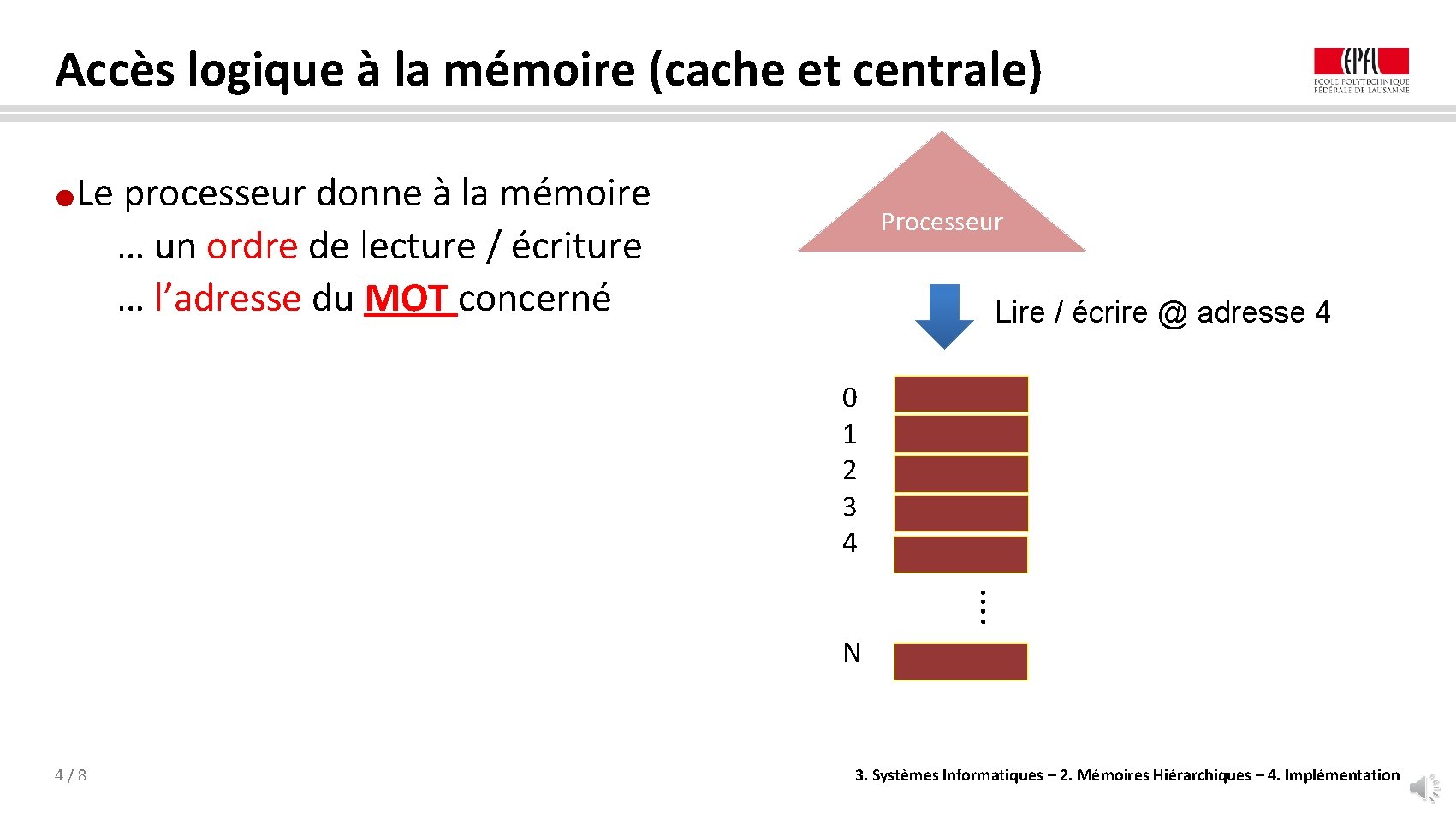

Accès logique à la mémoire (cache et centrale) Le processeur donne à la mémoire … un ordre de lecture / écriture … l’adresse du MOT concerné ● Processeur Lire / écrire @ adresse 4 0 1 2 3 4 …. N 4/8 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

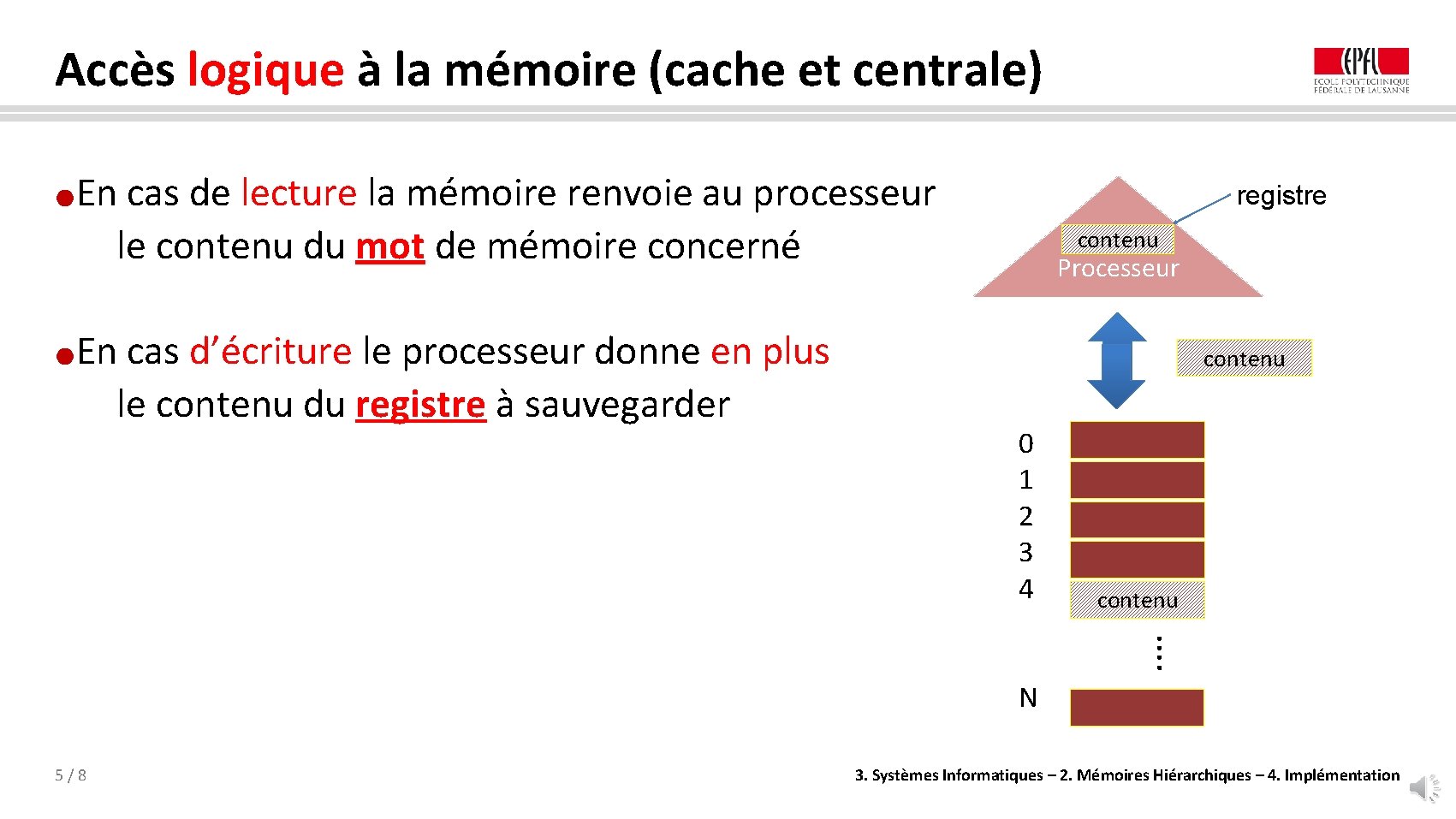

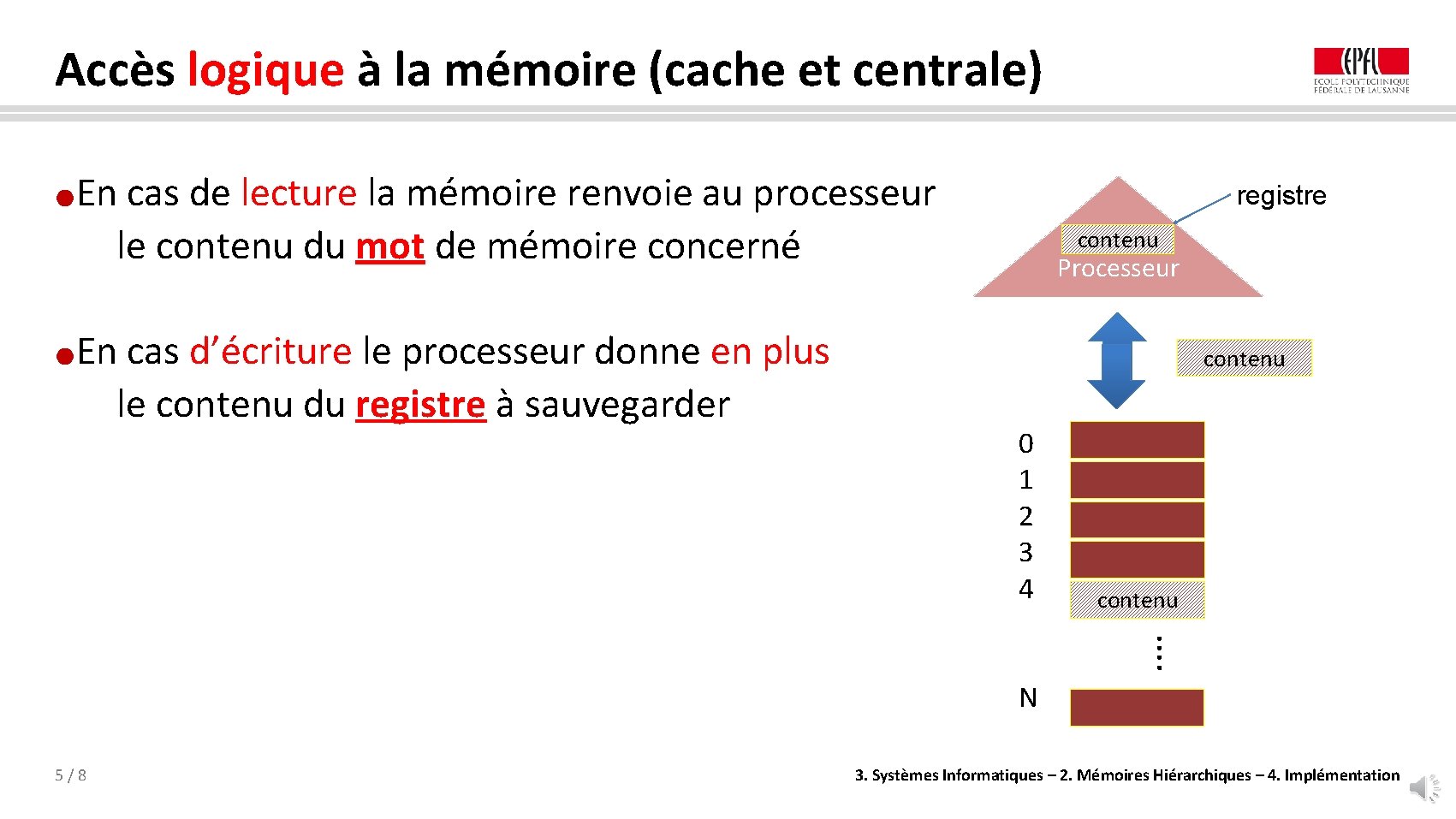

Accès logique à la mémoire (cache et centrale) En cas de lecture la mémoire renvoie au processeur le contenu du mot de mémoire concerné registre ● En cas d’écriture le processeur donne en plus le contenu du registre à sauvegarder contenu Processeur contenu ● 0 1 2 3 4 contenu …. N 5/8 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

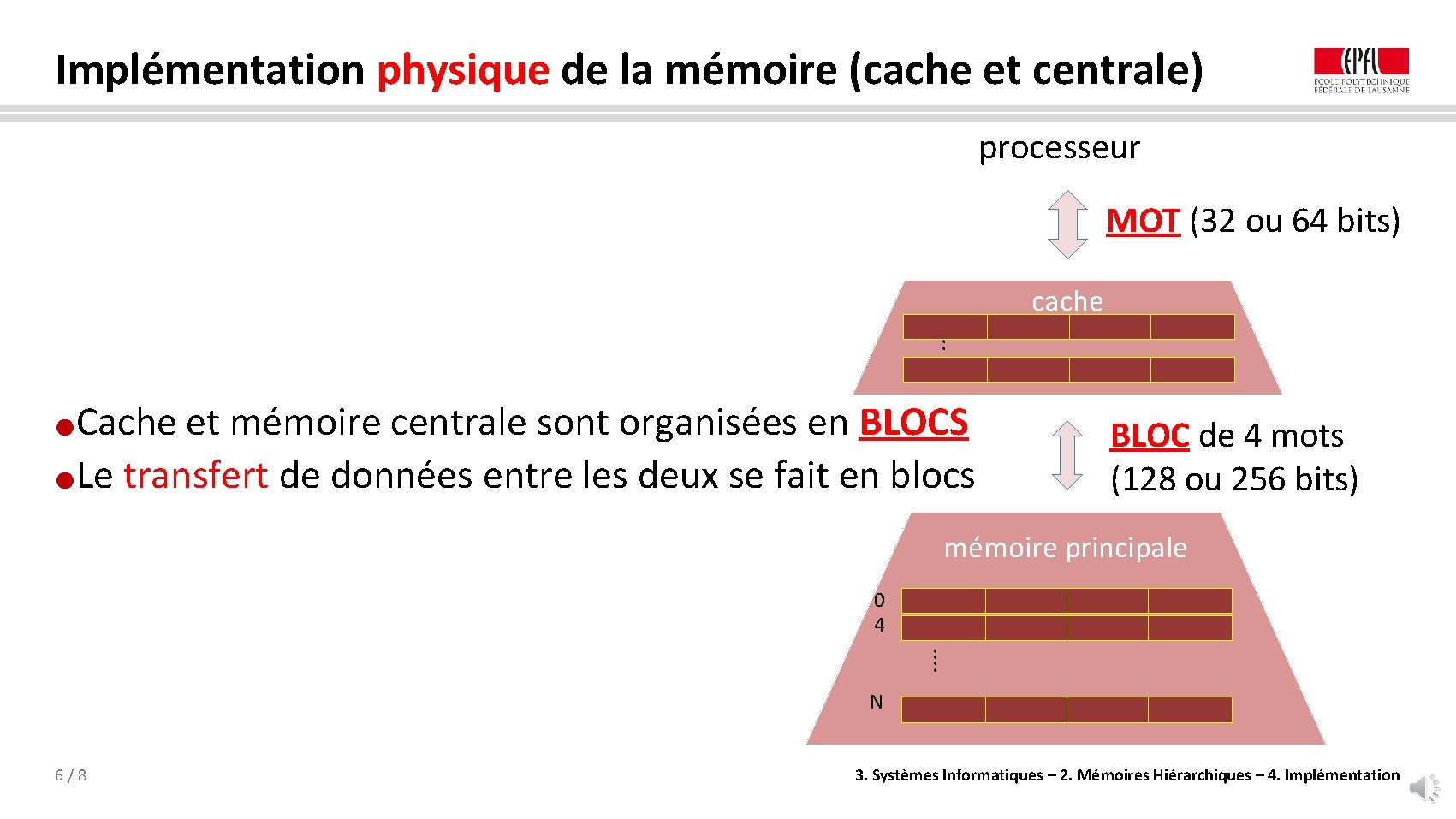

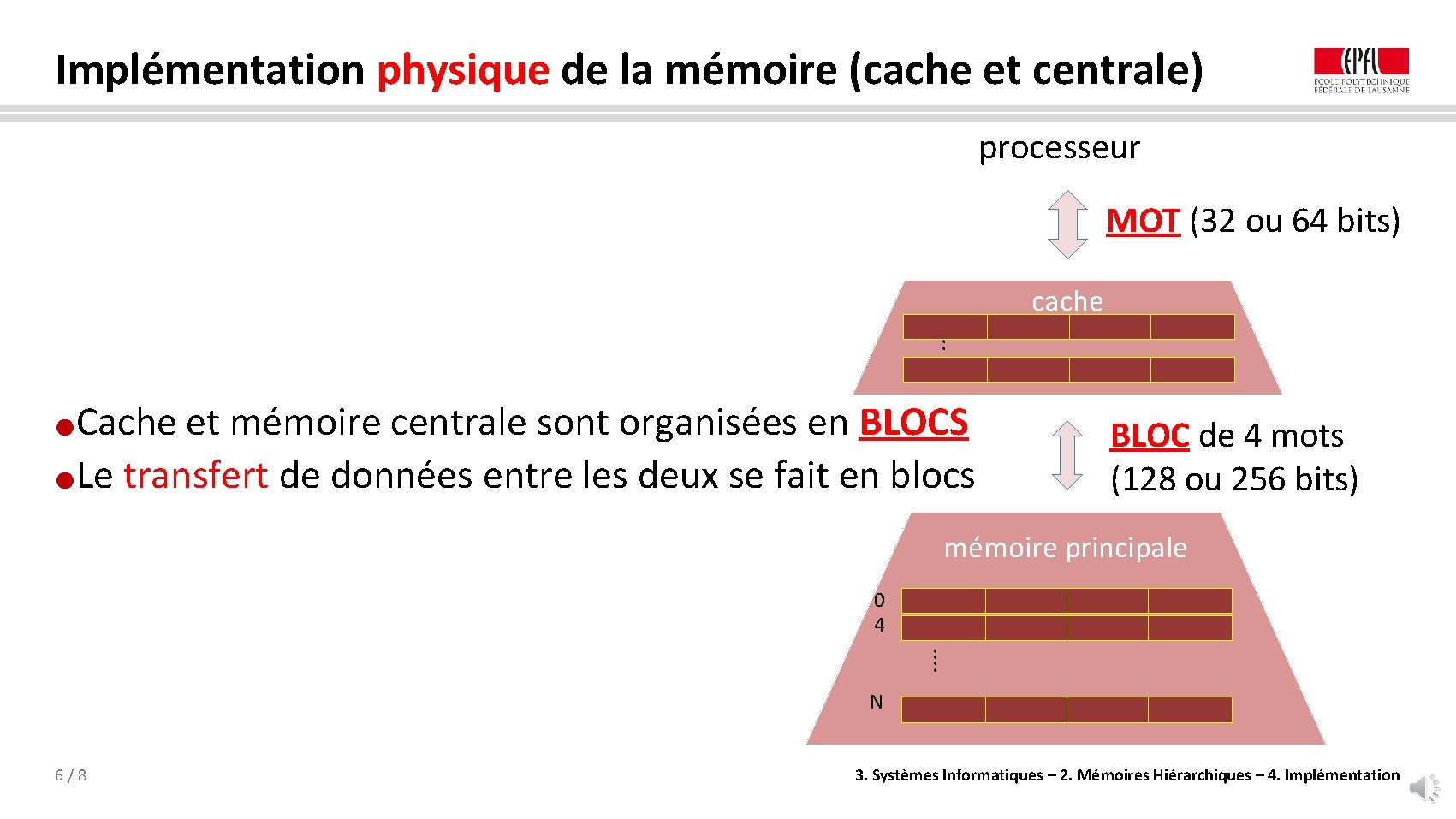

Implémentation physique de la mémoire (cache et centrale) processeur MOT (32 ou 64 bits) cache. . Cache et mémoire centrale sont organisées en BLOCS ●Le transfert de données entre les deux se fait en blocs ● BLOC de 4 mots (128 ou 256 bits) mémoire principale 0 4 …. N 6/8 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

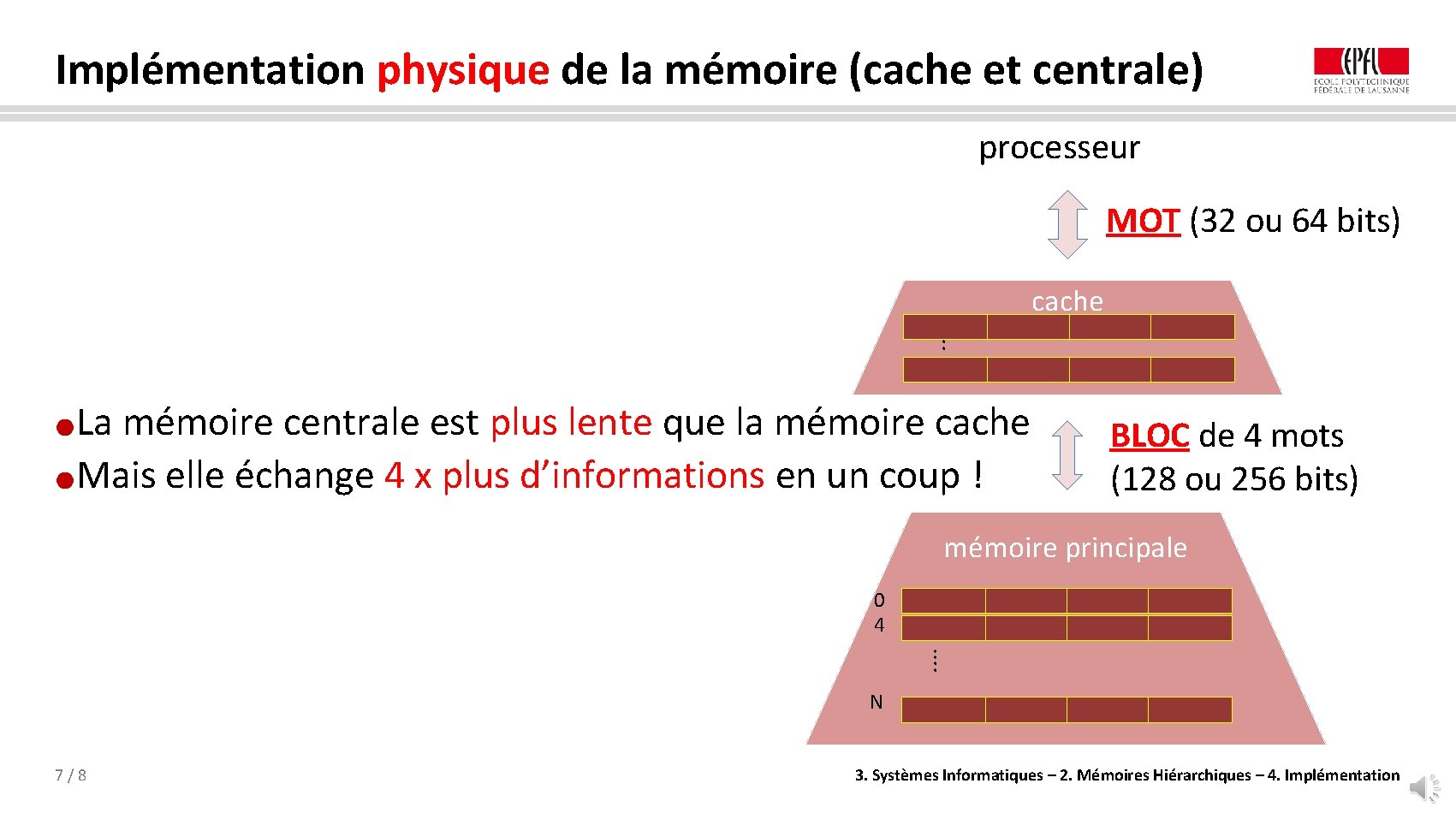

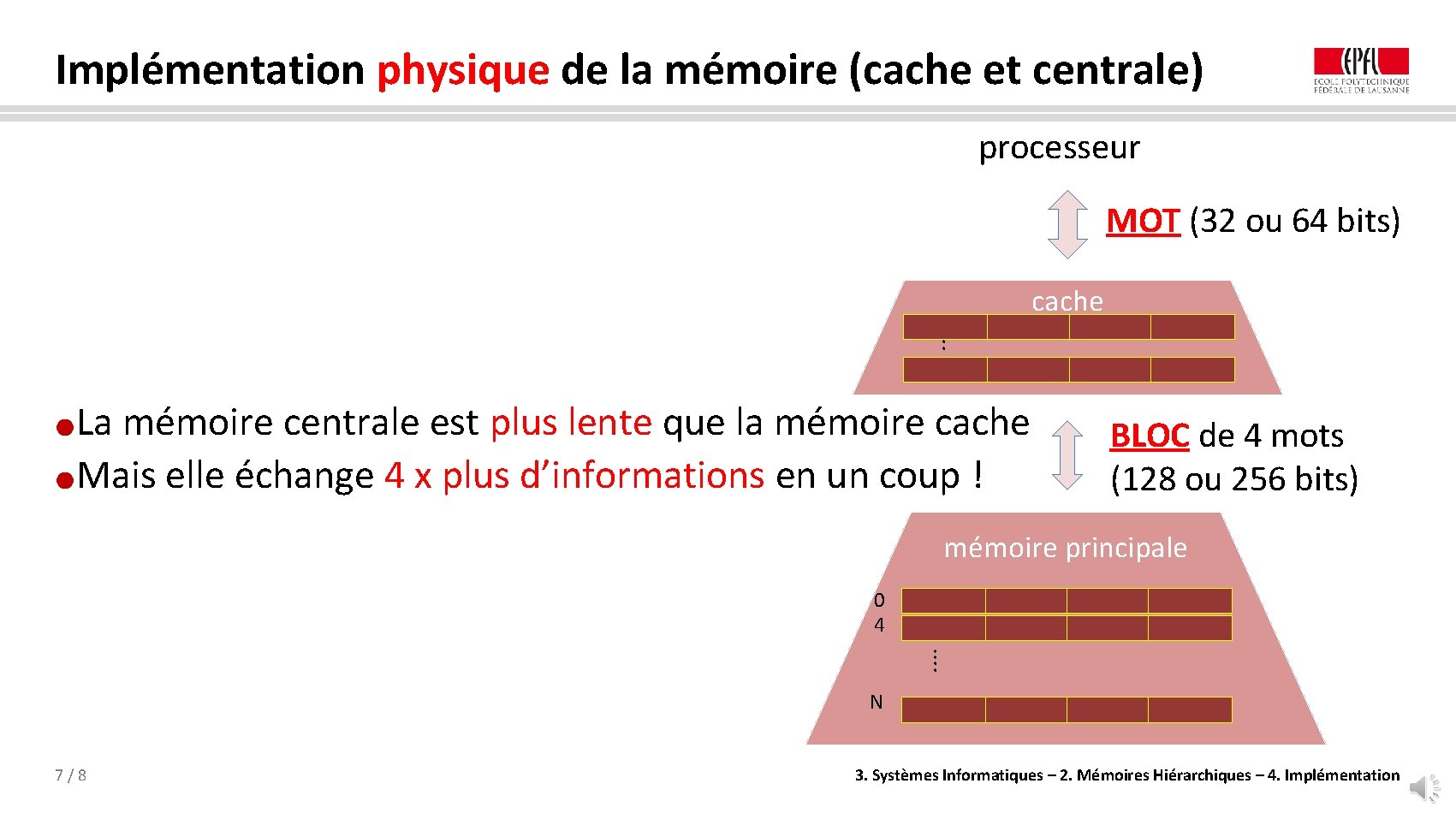

Implémentation physique de la mémoire (cache et centrale) processeur MOT (32 ou 64 bits) cache. . La mémoire centrale est plus lente que la mémoire cache ●Mais elle échange 4 x plus d’informations en un coup ! ● BLOC de 4 mots (128 ou 256 bits) mémoire principale 0 4 …. N 7/8 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation

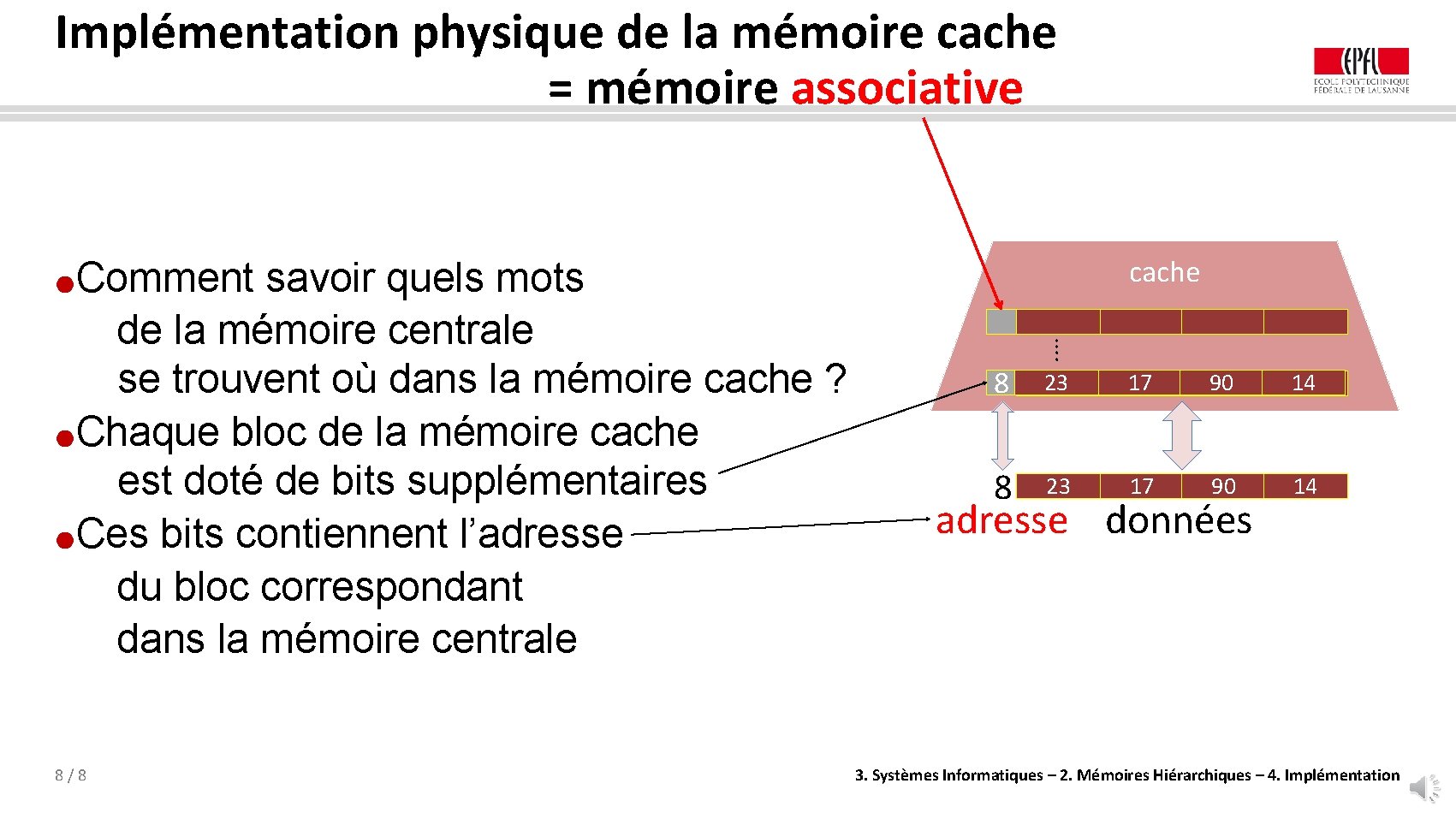

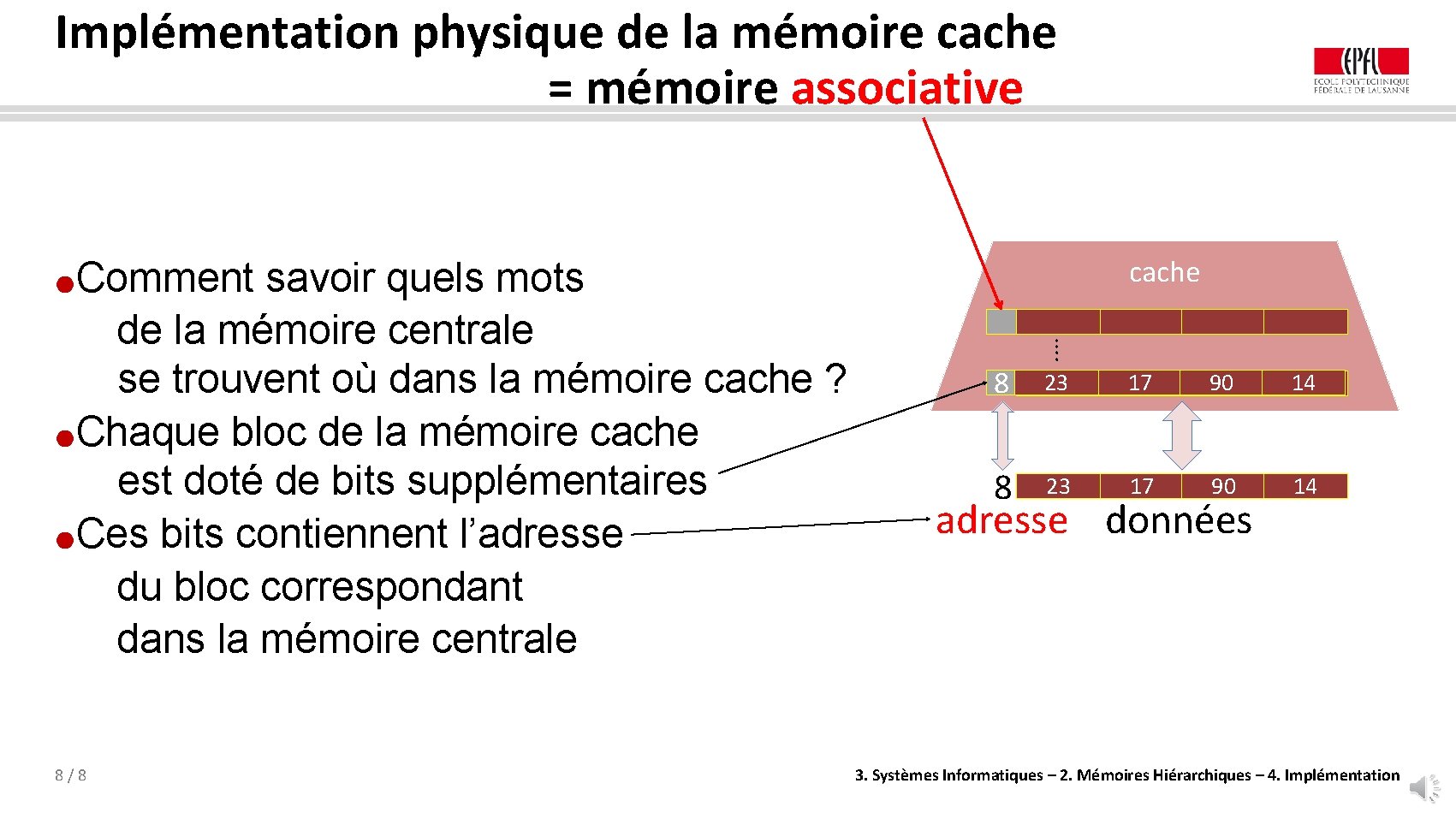

Implémentation physique de la mémoire cache = mémoire associative Comment savoir quels mots de la mémoire centrale se trouvent où dans la mémoire cache ? ●Chaque bloc de la mémoire cache est doté de bits supplémentaires ●Ces bits contiennent l’adresse du bloc correspondant dans la mémoire centrale cache ● …. 8/8 8 23 17 90 14 adresse données 3. Systèmes Informatiques – 2. Mémoires Hiérarchiques – 4. Implémentation