DAGAware AIG Rewriting A Fresh Look at TechnologyIndependent

- Slides: 17

DAG-Aware AIG Rewriting A Fresh Look at Technology-Independent Combinational Logic Synthesis Alan Mishchenko Satrajit Chatterjee Robert Brayton UC Berkeley

Overview n n n Motivation Previous work Example Experiments Conclusions

Motivation for Improved Synthesis n Traditional combinational tech-independent synthesis n n n suboptimal complicated hard to implement slow We propose to replace it with synthesis that is n n suboptimal, but simple easier to implement fast

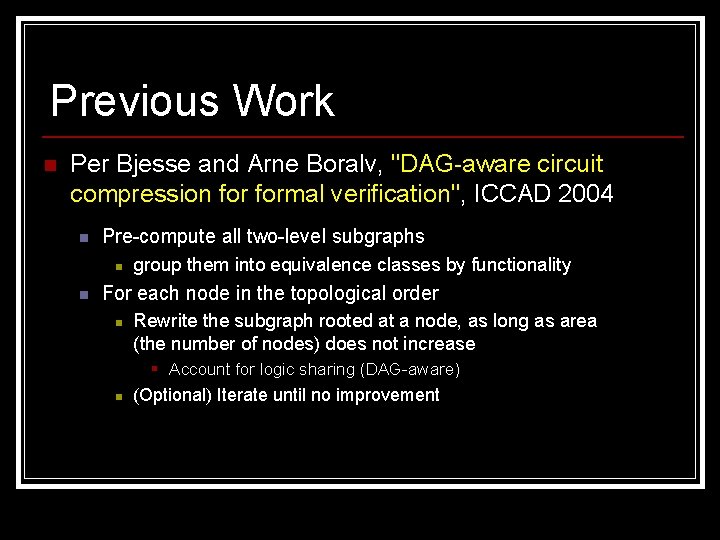

Previous Work n Per Bjesse and Arne Boralv, "DAG-aware circuit compression formal verification", ICCAD 2004 n Pre-compute all two-level subgraphs n n group them into equivalence classes by functionality For each node in the topological order n n Rewrite the subgraph rooted at a node, as long as area (the number of nodes) does not increase § Account for logic sharing (DAG-aware) (Optional) Iterate until no improvement

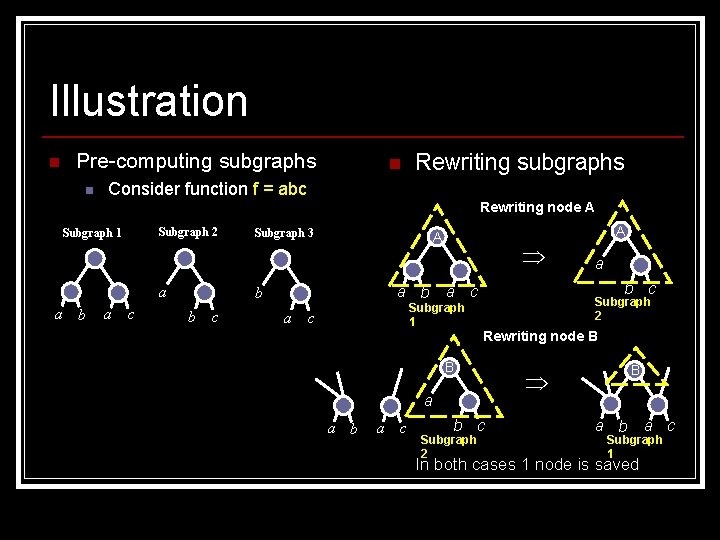

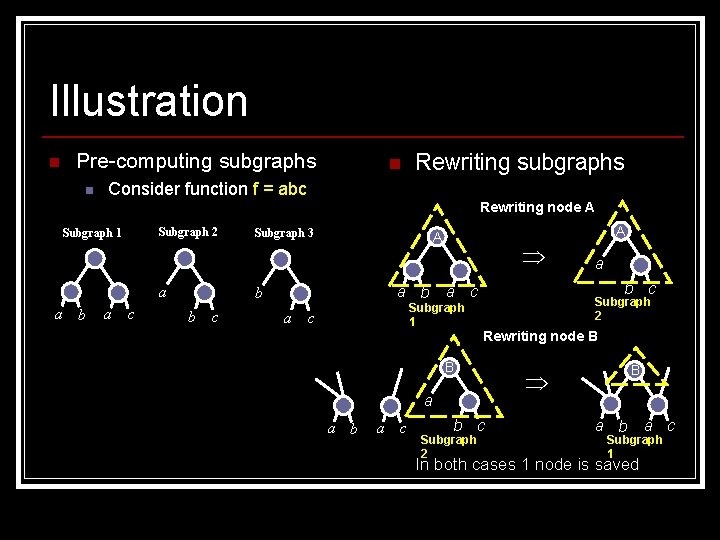

Illustration n Pre-computing subgraphs n n Rewriting subgraphs Consider function f = abc Rewriting node A Subgraph 1 Subgraph 2 a a b a c Subgraph 3 a b b b c a A A b c a c Subgraph 1 c Subgraph 2 Rewriting node B B a a b a c b c Subgraph 2 a B a b a c Subgraph 1 In both cases 1 node is saved

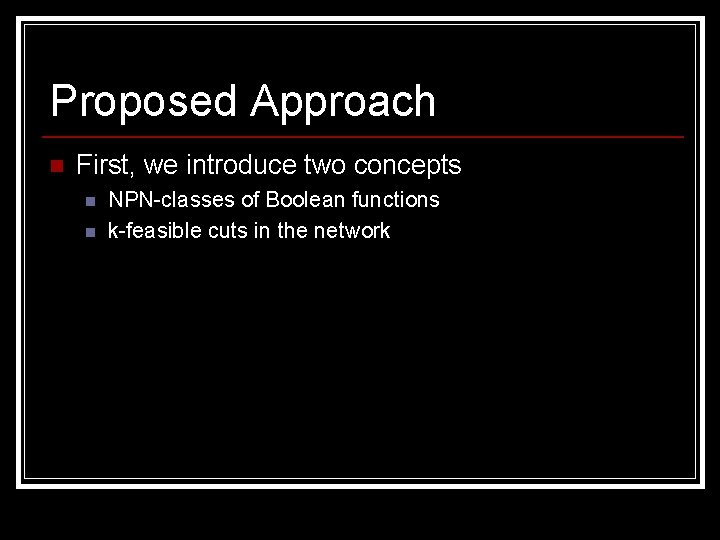

Proposed Approach n First, we introduce two concepts n n NPN-classes of Boolean functions k-feasible cuts in the network

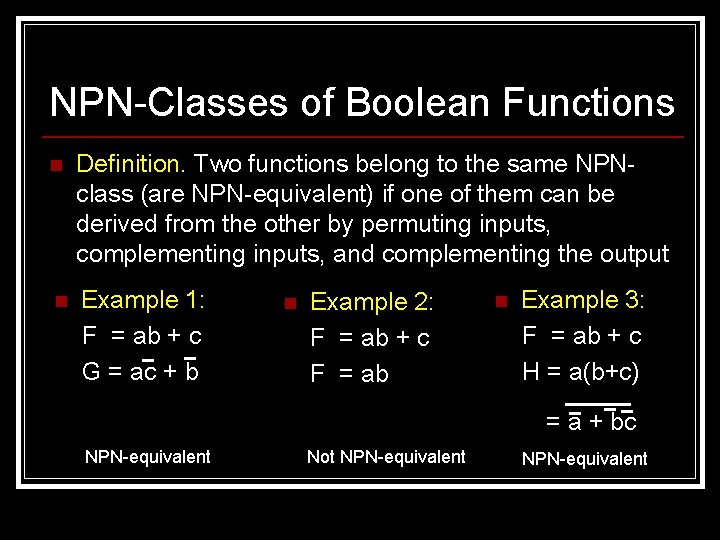

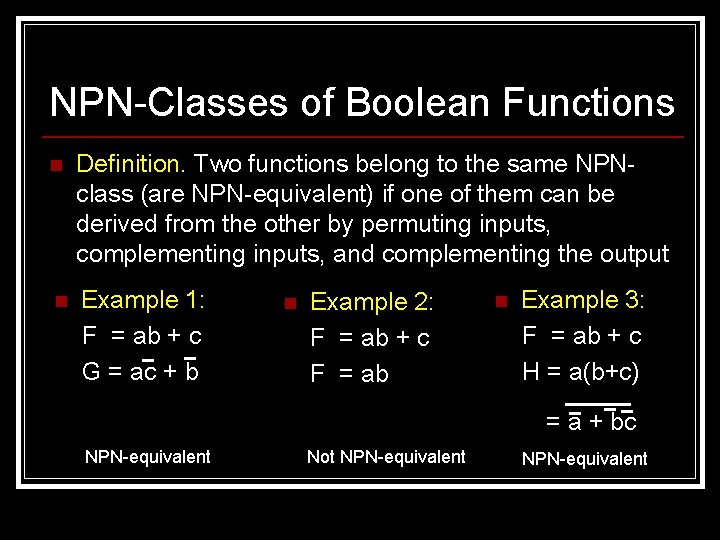

NPN-Classes of Boolean Functions n Definition. Two functions belong to the same NPNclass (are NPN-equivalent) if one of them can be derived from the other by permuting inputs, complementing inputs, and complementing the output n Example 1: F = ab + c G = ac + b n Example 2: F = ab + c F = ab n Example 3: F = ab + c H = a(b+c) = a + bc NPN-equivalent Not NPN-equivalent

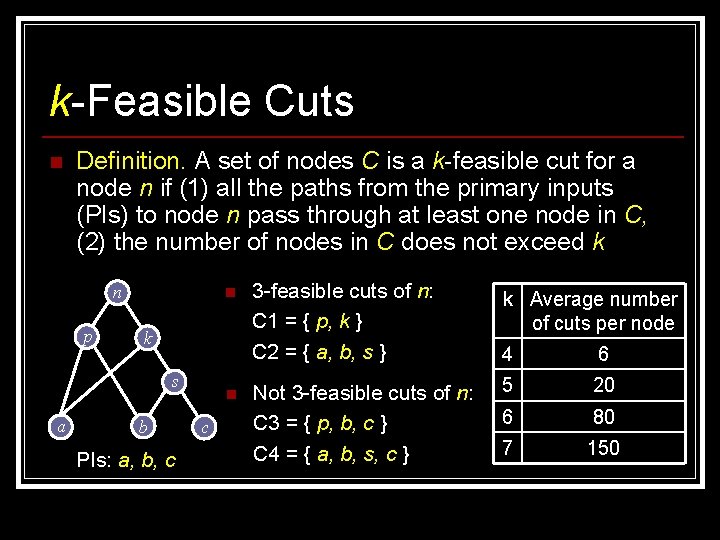

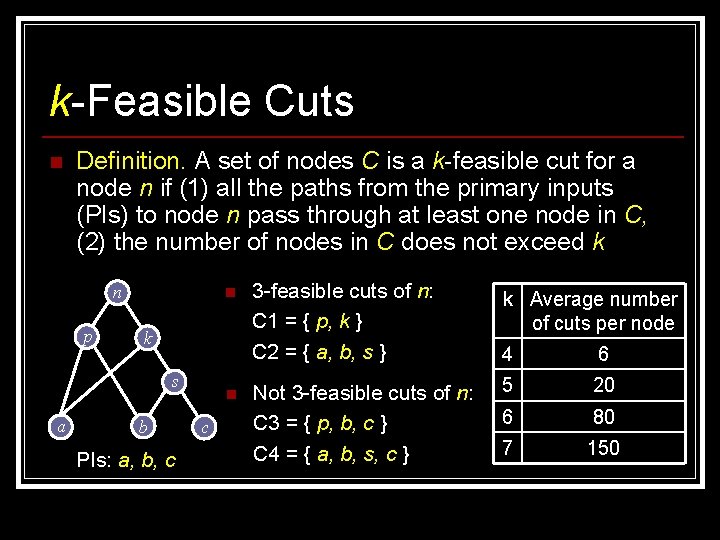

k-Feasible Cuts n Definition. A set of nodes C is a k-feasible cut for a node n if (1) all the paths from the primary inputs (PIs) to node n pass through at least one node in C, (2) the number of nodes in C does not exceed k n p n k s a b PIs: a, b, c n c 3 -feasible cuts of n: C 1 = { p, k } C 2 = { a, b, s } Not 3 -feasible cuts of n: C 3 = { p, b, c } C 4 = { a, b, s, c } k Average number of cuts per node 4 6 5 20 6 80 7 150

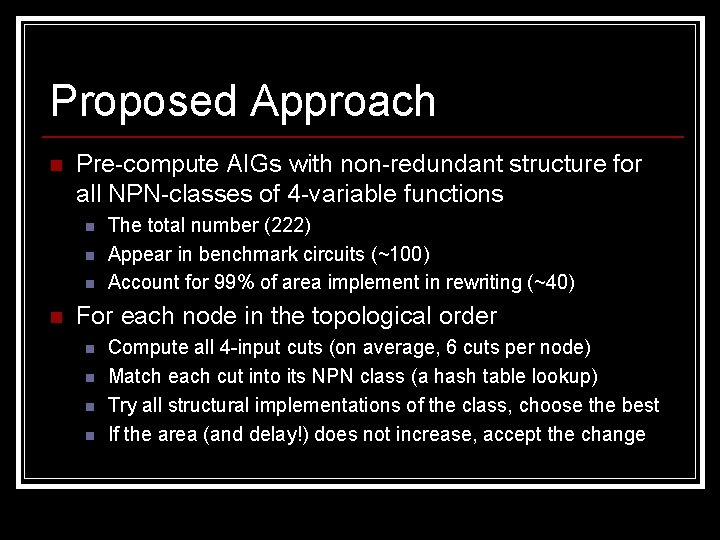

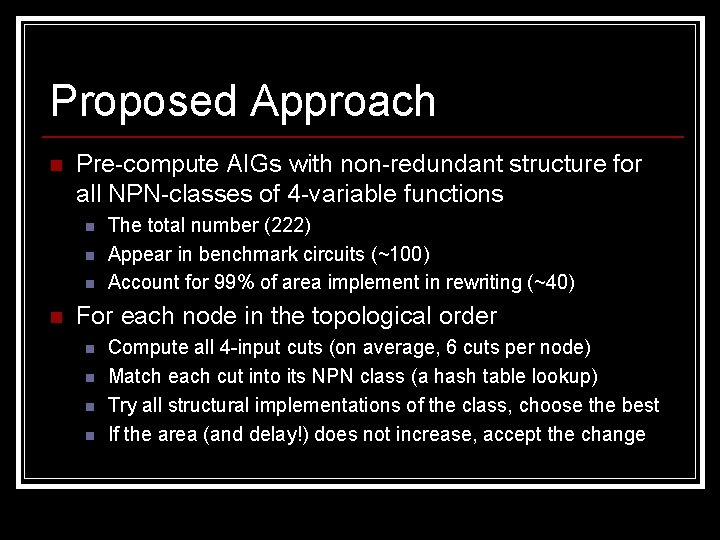

Proposed Approach n Pre-compute AIGs with non-redundant structure for all NPN-classes of 4 -variable functions n n The total number (222) Appear in benchmark circuits (~100) Account for 99% of area implement in rewriting (~40) For each node in the topological order n n Compute all 4 -input cuts (on average, 6 cuts per node) Match each cut into its NPN class (a hash table lookup) Try all structural implementations of the class, choose the best If the area (and delay!) does not increase, accept the change

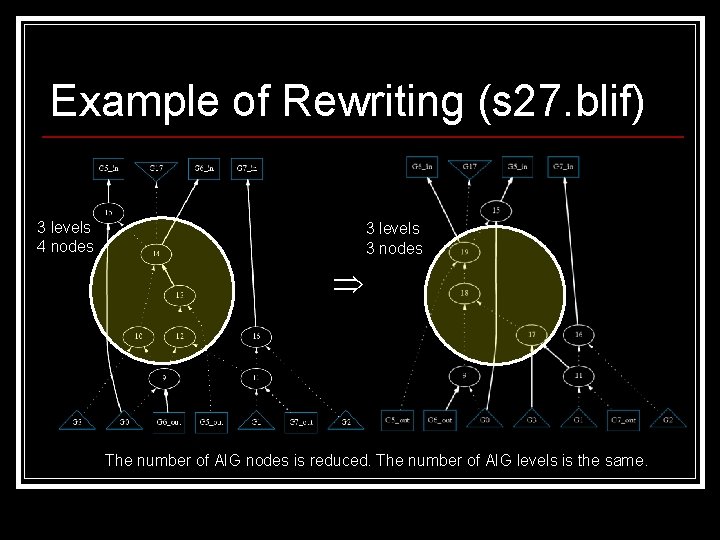

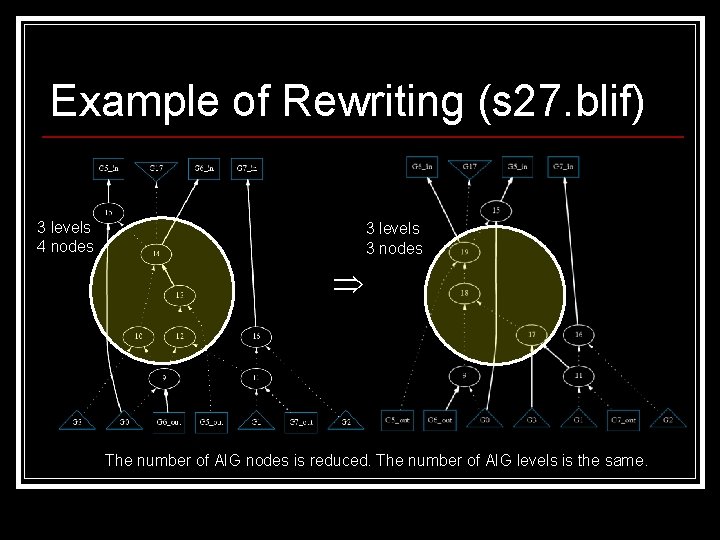

Example of Rewriting (s 27. blif) 3 levels 4 nodes 3 levels 3 nodes The number of AIG nodes is reduced. The number of AIG levels is the same.

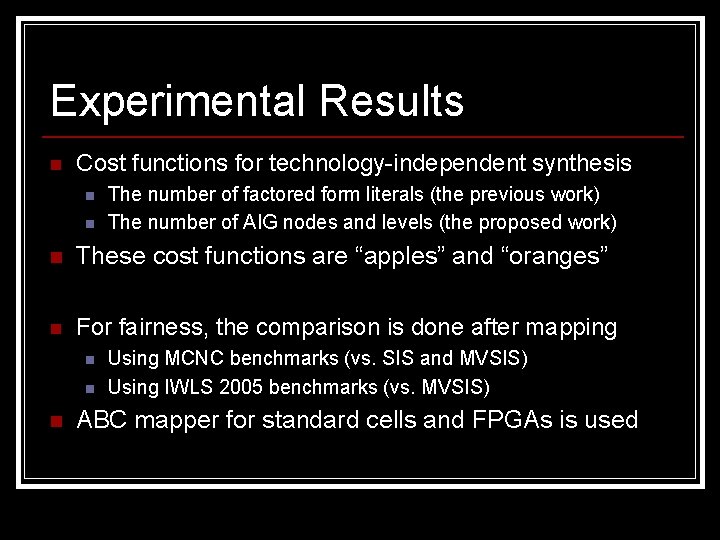

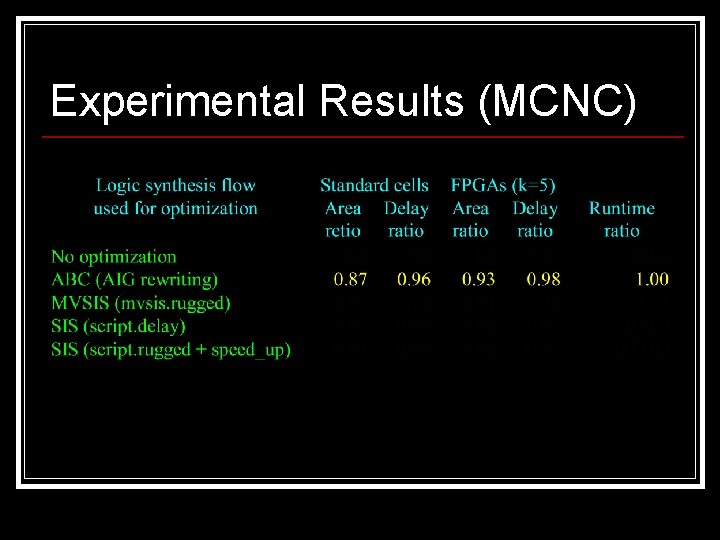

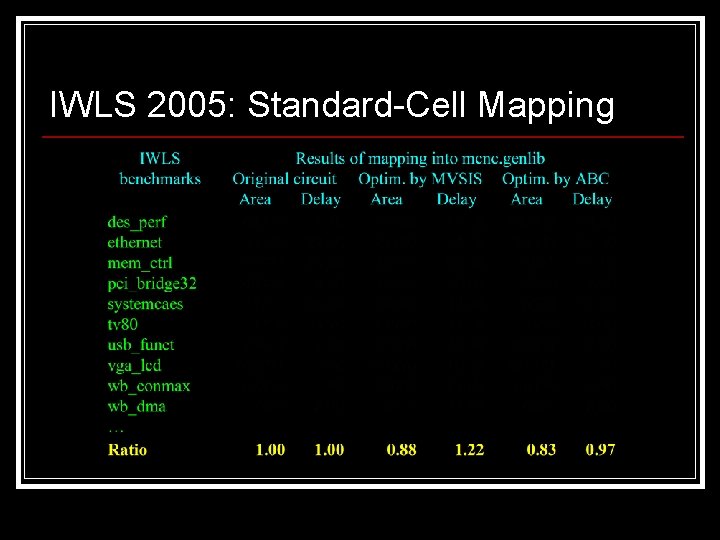

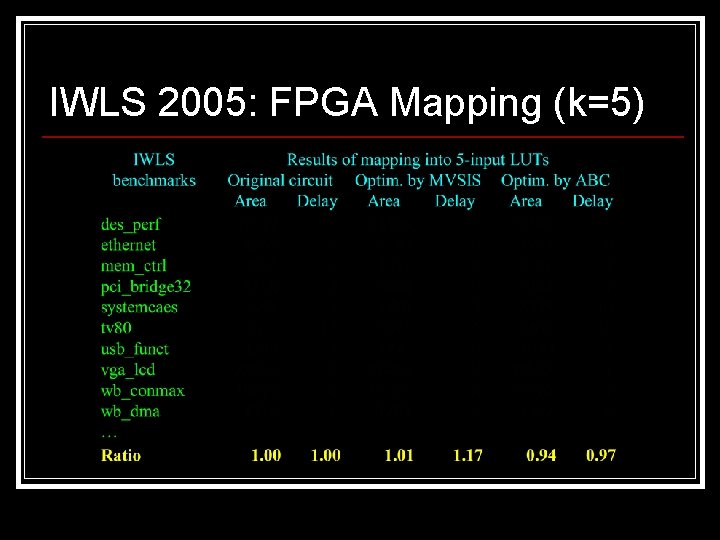

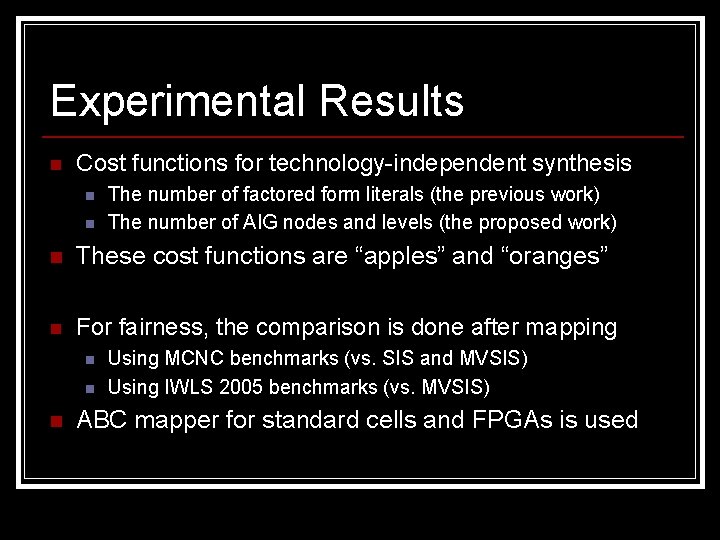

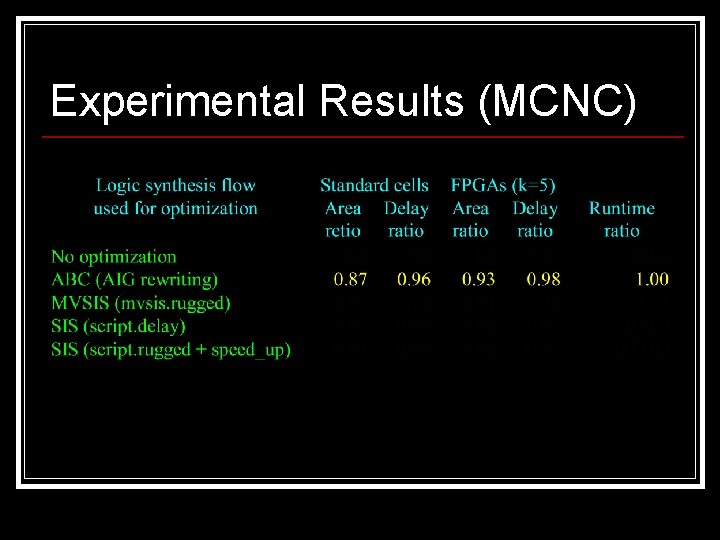

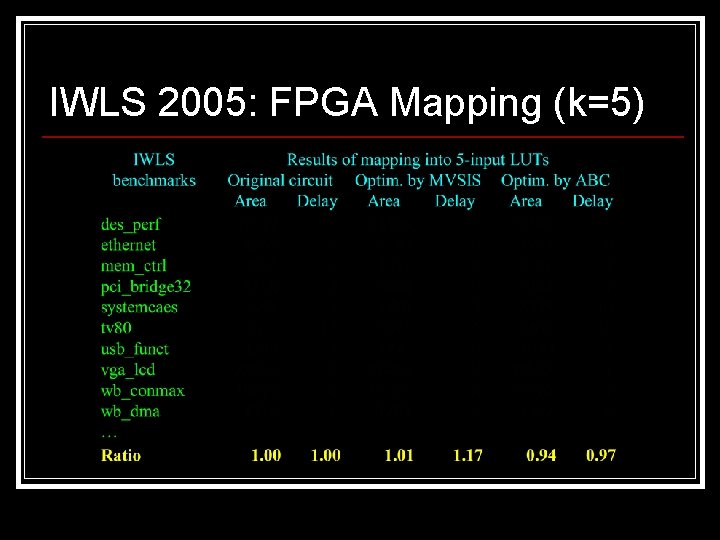

Experimental Results n Cost functions for technology-independent synthesis n n The number of factored form literals (the previous work) The number of AIG nodes and levels (the proposed work) n These cost functions are “apples” and “oranges” n For fairness, the comparison is done after mapping n n n Using MCNC benchmarks (vs. SIS and MVSIS) Using IWLS 2005 benchmarks (vs. MVSIS) ABC mapper for standard cells and FPGAs is used

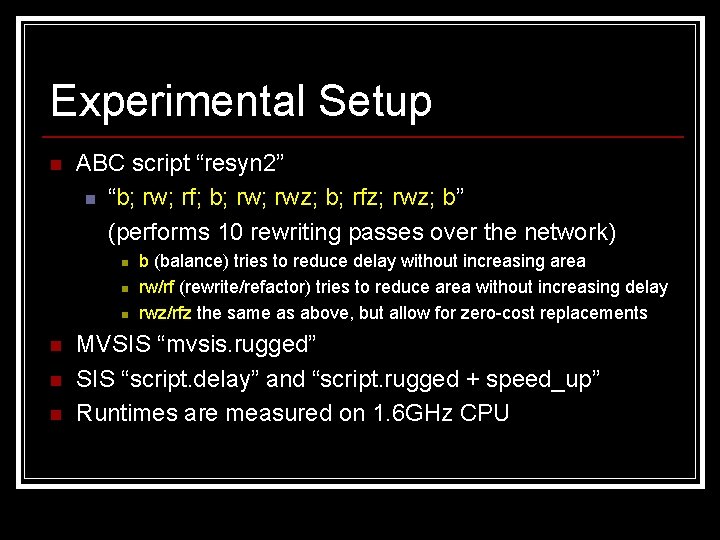

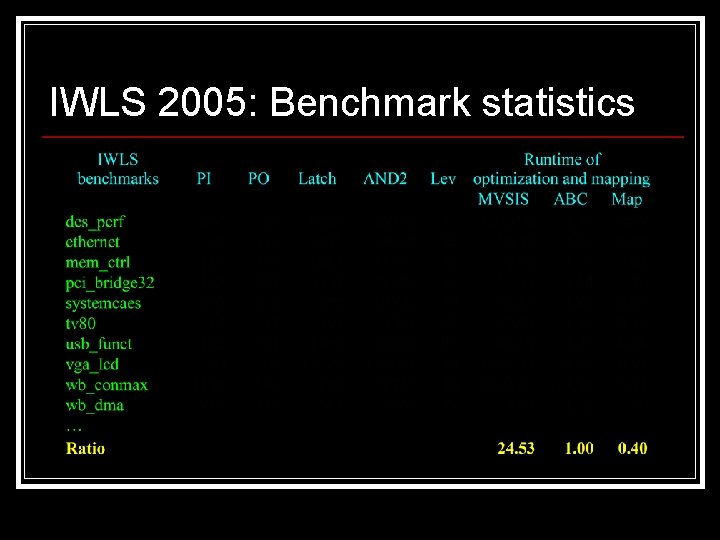

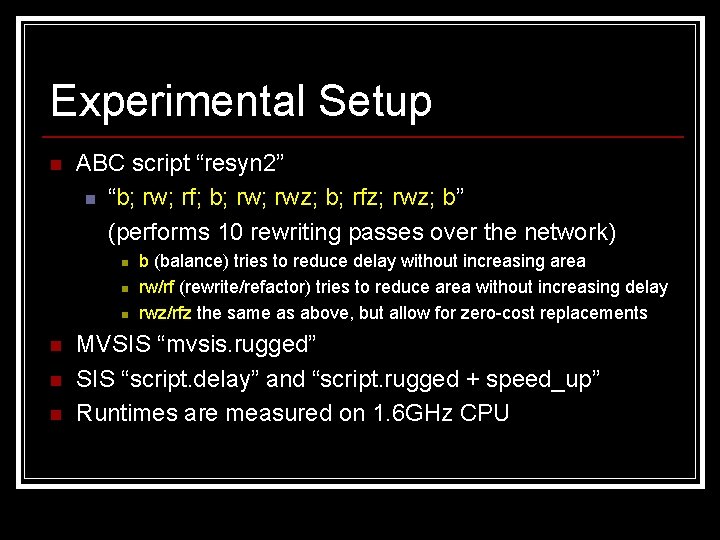

Experimental Setup n ABC script “resyn 2” n “b; rw; rf; b; rwz; b; rfz; rwz; b” (performs 10 rewriting passes over the network) n n n b (balance) tries to reduce delay without increasing area rw/rf (rewrite/refactor) tries to reduce area without increasing delay rwz/rfz the same as above, but allow for zero-cost replacements MVSIS “mvsis. rugged” SIS “script. delay” and “script. rugged + speed_up” Runtimes are measured on 1. 6 GHz CPU

Experimental Results (MCNC)

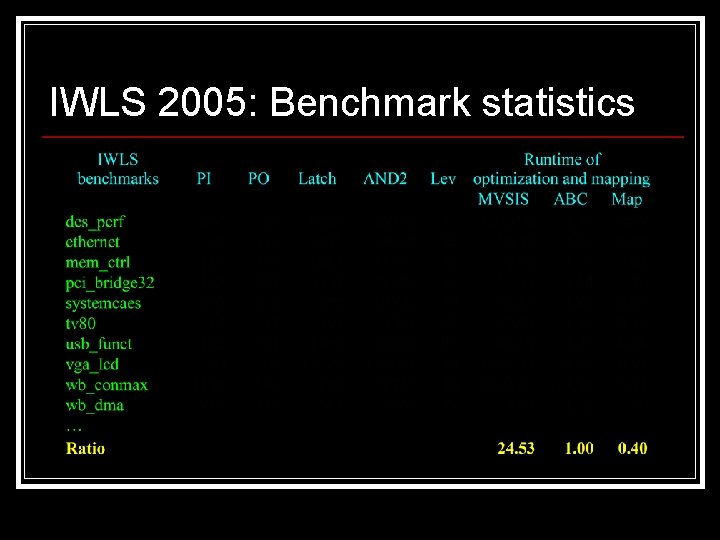

IWLS 2005: Benchmark statistics

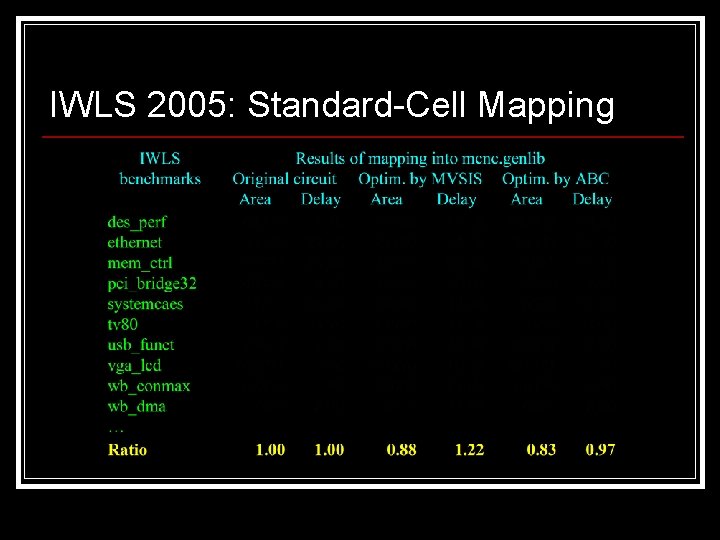

IWLS 2005: Standard-Cell Mapping

IWLS 2005: FPGA Mapping (k=5)

Conclusions n n Introduced ABC Presented DAG-aware AIG rewriting Showed promising experimental results Future work n n AIG rewriting with larger cut size Sequential AIG rewriting