CS 4101 Freescale Tower System Prof ChungTa King

- Slides: 18

CS 4101 嵌入式系統概論 Freescale Tower System Prof. Chung-Ta King Department of Computer Science National Tsing Hua University, Taiwan (Materials from www. freescale. com)

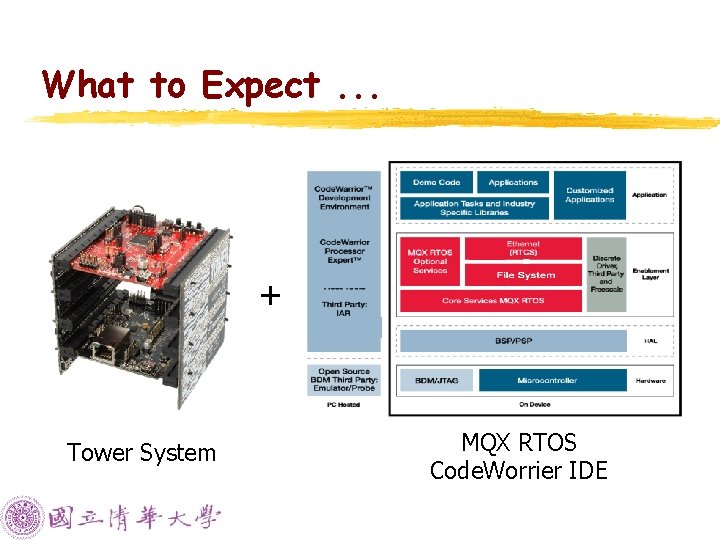

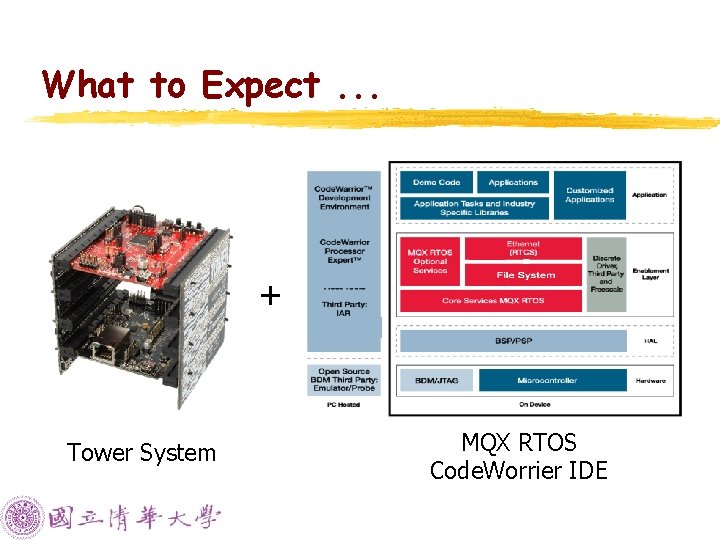

What to Expect. . . + Tower System MQX RTOS Code. Worrier IDE

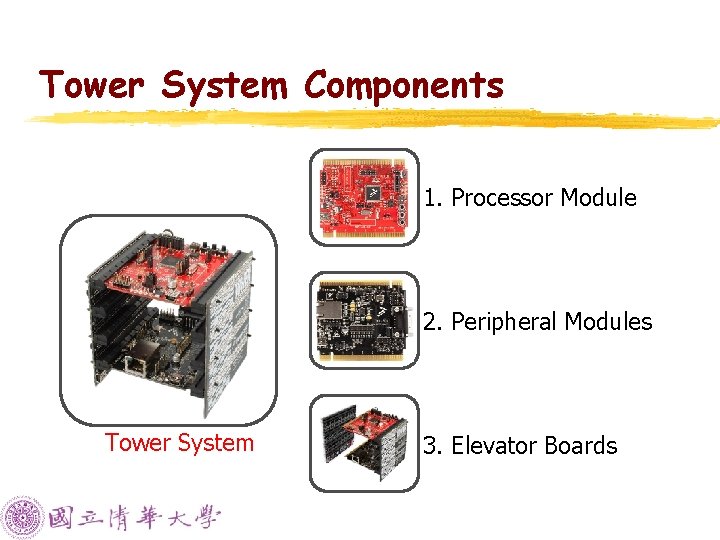

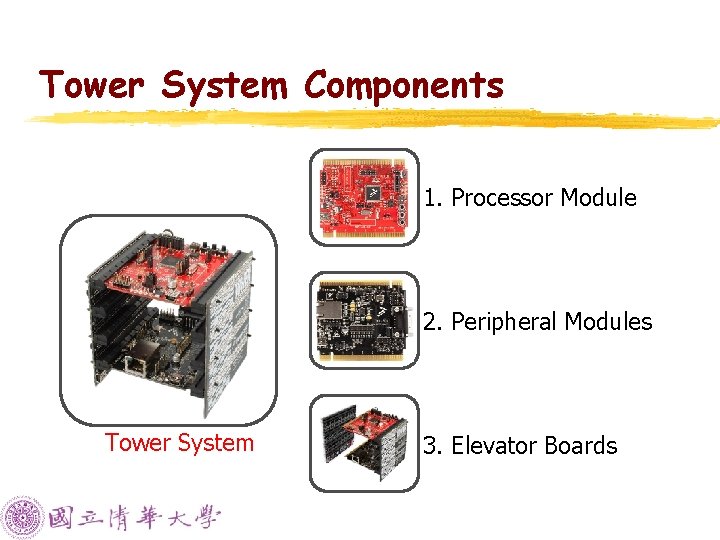

Tower System Components 1. Processor Module 2. Peripheral Modules Tower System 3. Elevator Boards

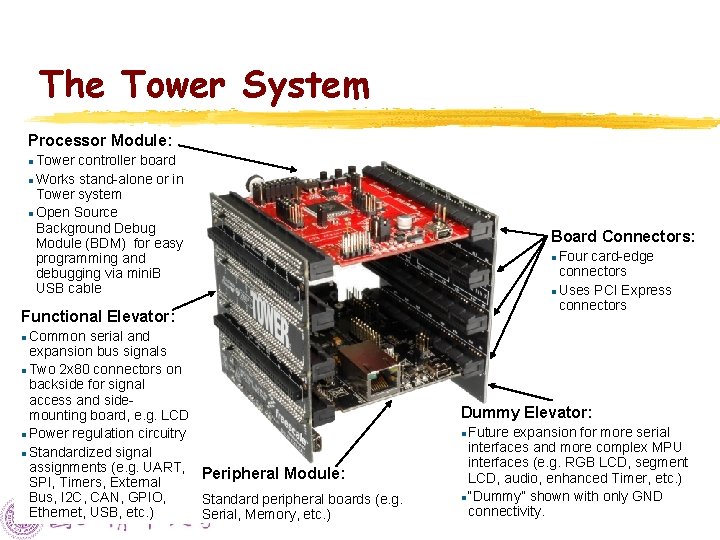

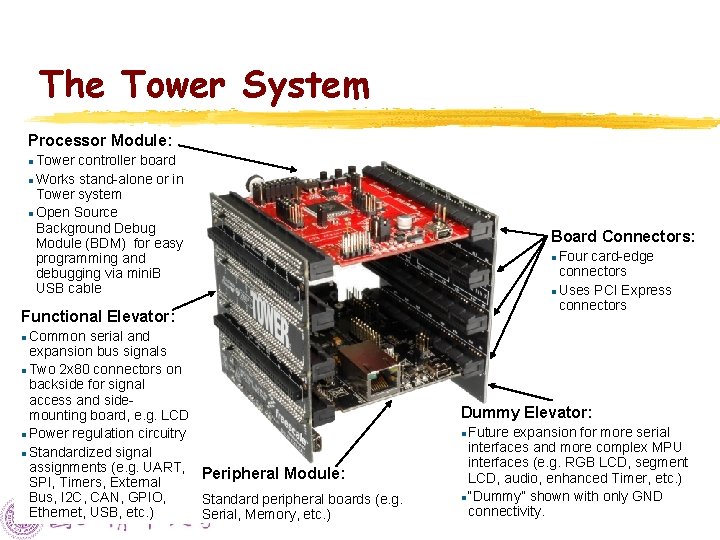

The Tower System Processor Module: Tower controller board l Works stand-alone or in Tower system l Open Source Background Debug Module (BDM) for easy programming and debugging via mini. B USB cable l Board Connectors: Four card-edge connectors l Uses PCI Express connectors l Functional Elevator: Common serial and expansion bus signals l Two 2 x 80 connectors on backside for signal access and sidemounting board, e. g. LCD l Power regulation circuitry l Standardized signal assignments (e. g. UART, Peripheral Module: SPI, Timers, External Bus, I 2 C, CAN, GPIO, Standard peripheral boards (e. g. Ethernet, USB, etc. ) Serial, Memory, etc. ) l Dummy Elevator: Future expansion for more serial interfaces and more complex MPU interfaces (e. g. RGB LCD, segment LCD, audio, enhanced Timer, etc. ) l “Dummy” shown with only GND connectivity. l

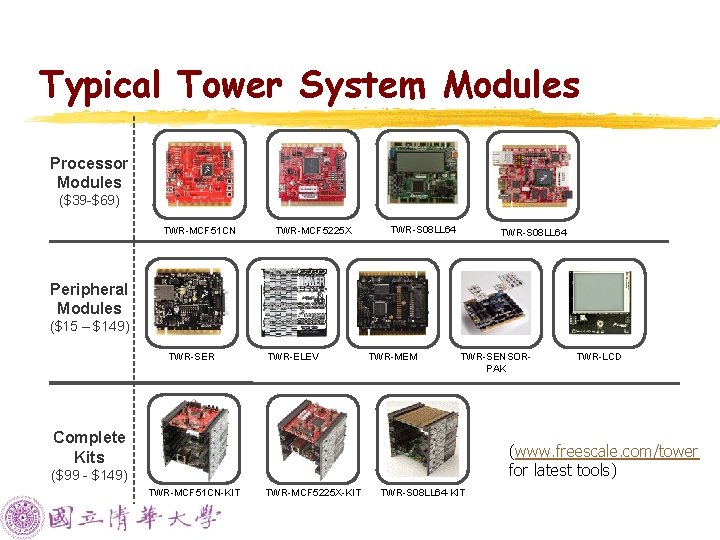

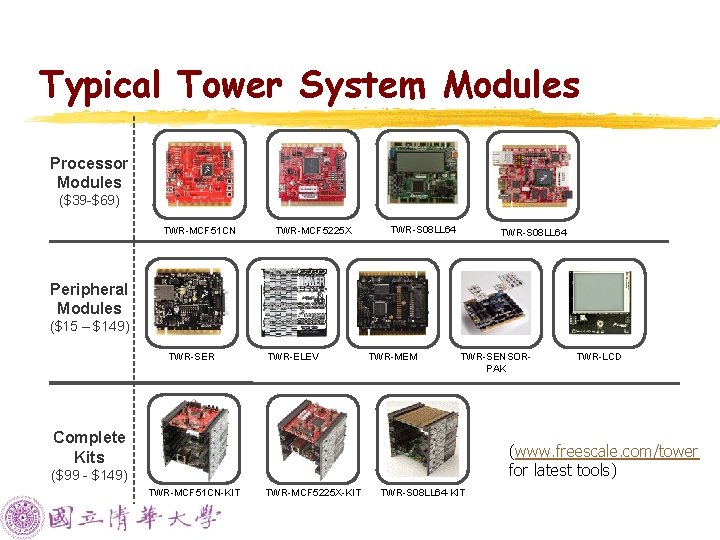

Typical Tower System Modules Processor Modules ($39 -$69) TWR-MCF 51 CN TWR-MCF 5225 X TWR-S 08 LL 64 Peripheral Modules ($15 – $149) TWR-SER TWR-ELEV TWR-MEM TWR-SENSORPAK Complete Kits TWR-LCD (www. freescale. com/tower for latest tools) ($99 - $149) TWR-MCF 51 CN-KIT TWR-MCF 5225 X-KIT TWR-S 08 LL 64 -KIT

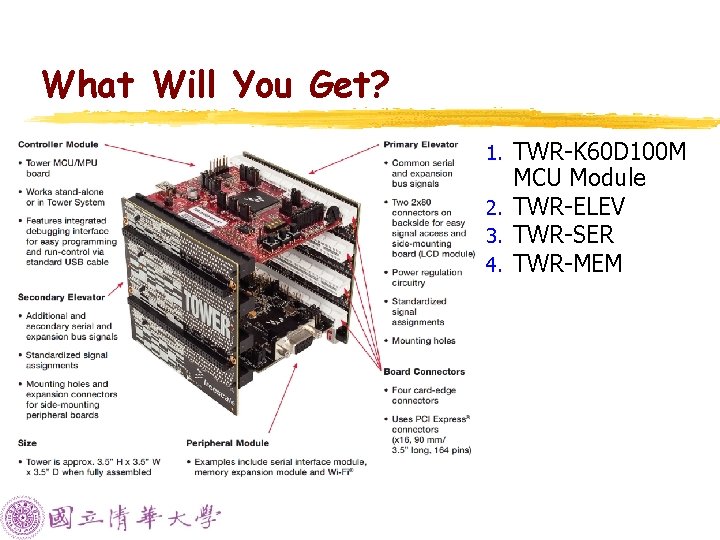

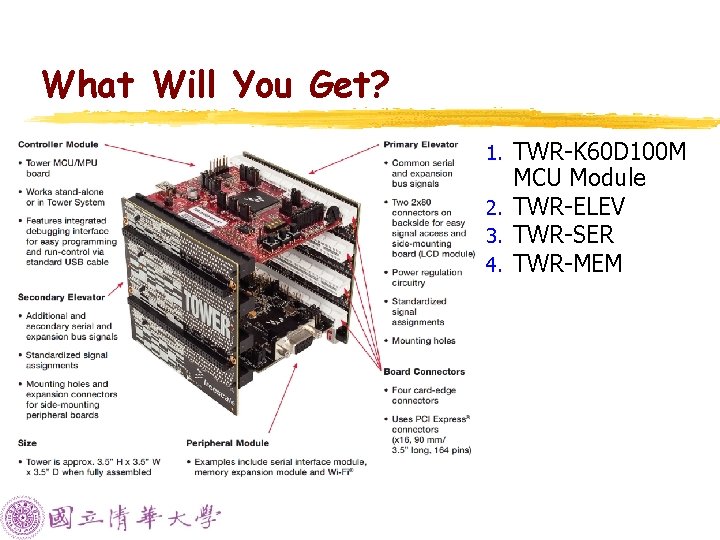

What Will You Get? TWR-K 60 D 100 M MCU Module 2. TWR-ELEV 3. TWR-SER 4. TWR-MEM 1.

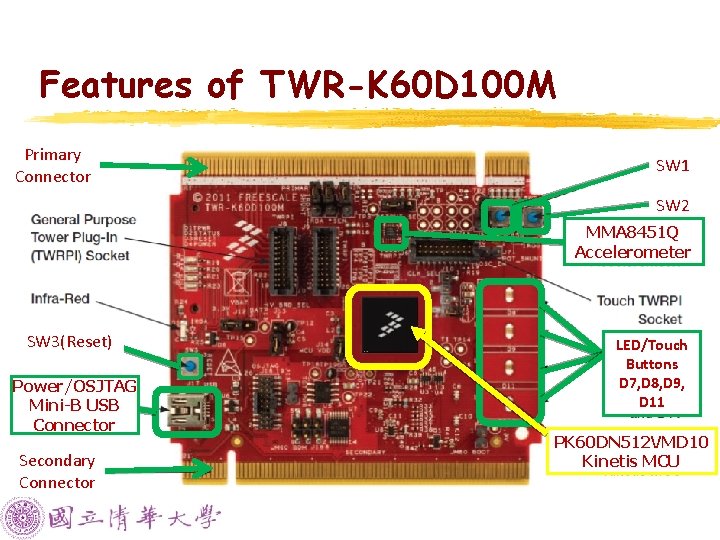

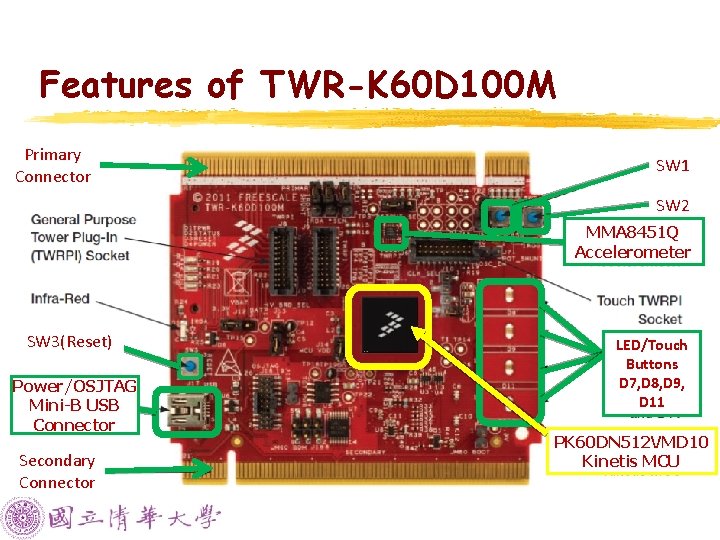

Features of TWR-K 60 D 100 M Primary Connector SW 1 SW 2 MMA 8451 Q Accelerometer SW 3(Reset) Power/OSJTAG Mini-B USB Connector Secondary Connector LED/Touch Buttons D 7, D 8, D 9, D 11 PK 60 DN 512 VMD 10 Kinetis MCU

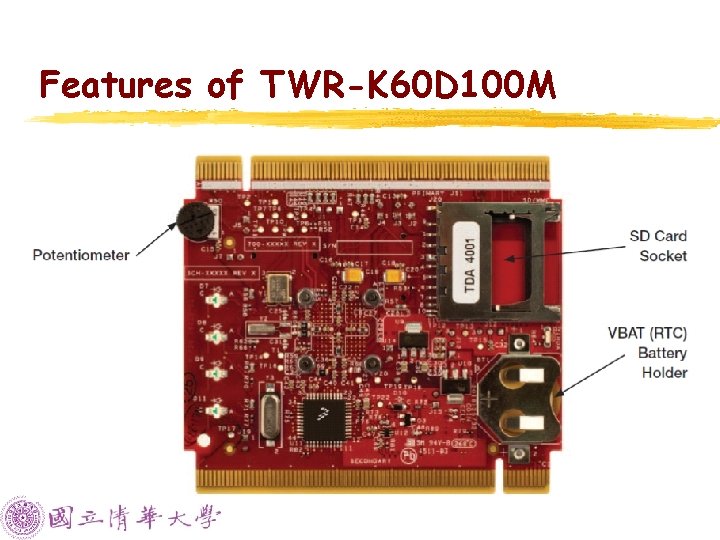

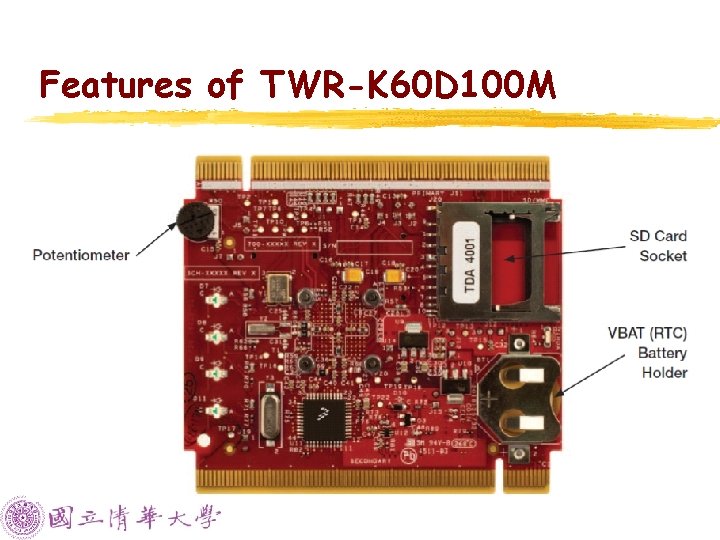

Features of TWR-K 60 D 100 M

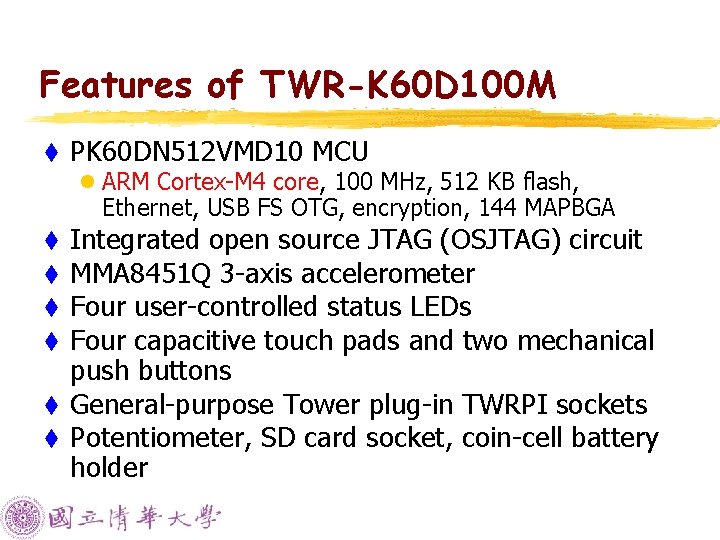

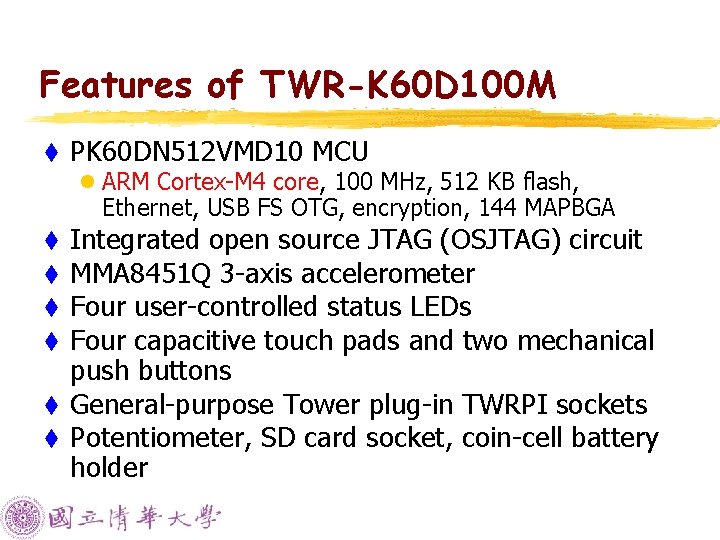

Features of TWR-K 60 D 100 M t PK 60 DN 512 VMD 10 MCU l ARM Cortex-M 4 core, 100 MHz, 512 KB flash, Ethernet, USB FS OTG, encryption, 144 MAPBGA Integrated open source JTAG (OSJTAG) circuit MMA 8451 Q 3 -axis accelerometer Four user-controlled status LEDs Four capacitive touch pads and two mechanical push buttons t General-purpose Tower plug-in TWRPI sockets t Potentiometer, SD card socket, coin-cell battery holder t t

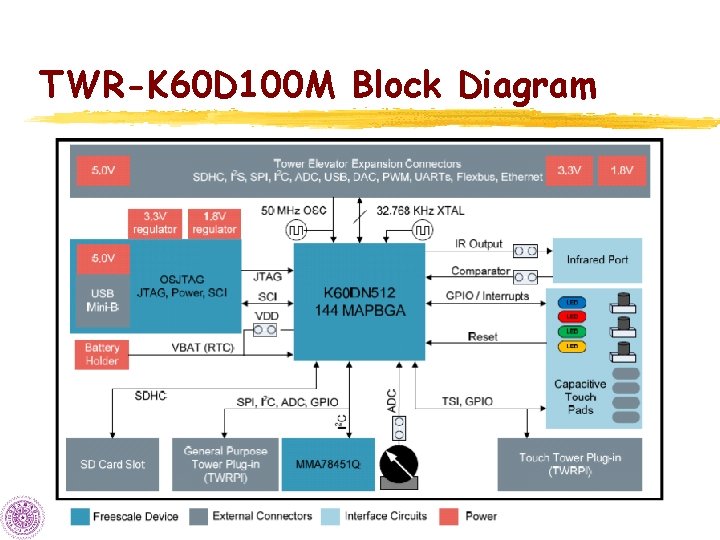

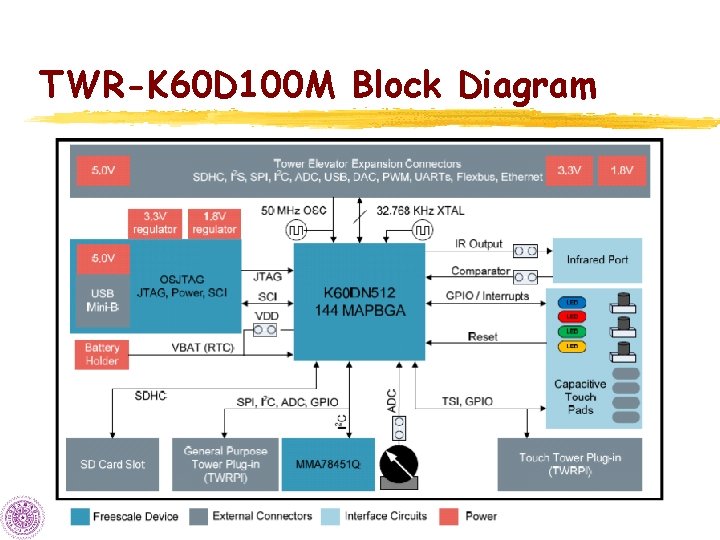

TWR-K 60 D 100 M Block Diagram

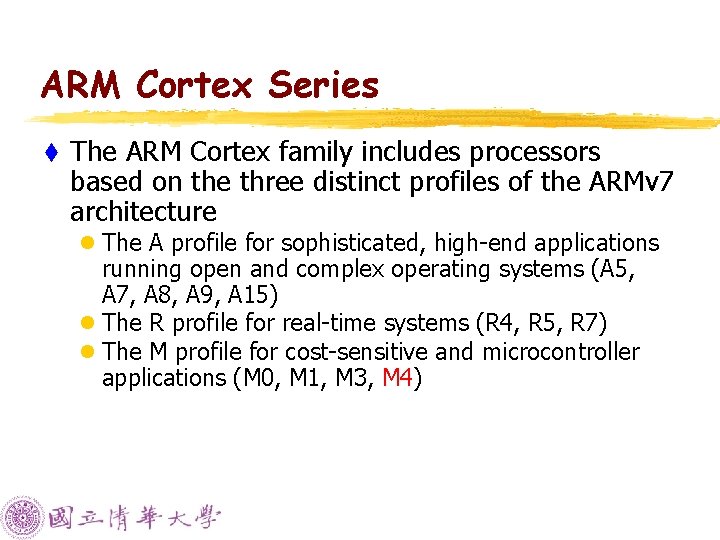

ARM Cortex Series t The ARM Cortex family includes processors based on the three distinct profiles of the ARMv 7 architecture l The A profile for sophisticated, high-end applications running open and complex operating systems (A 5, A 7, A 8, A 9, A 15) l The R profile for real-time systems (R 4, R 5, R 7) l The M profile for cost-sensitive and microcontroller applications (M 0, M 1, M 3, M 4)

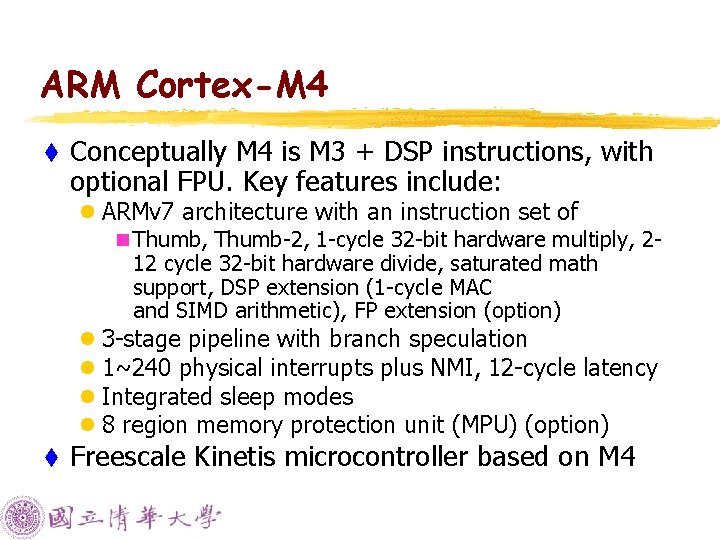

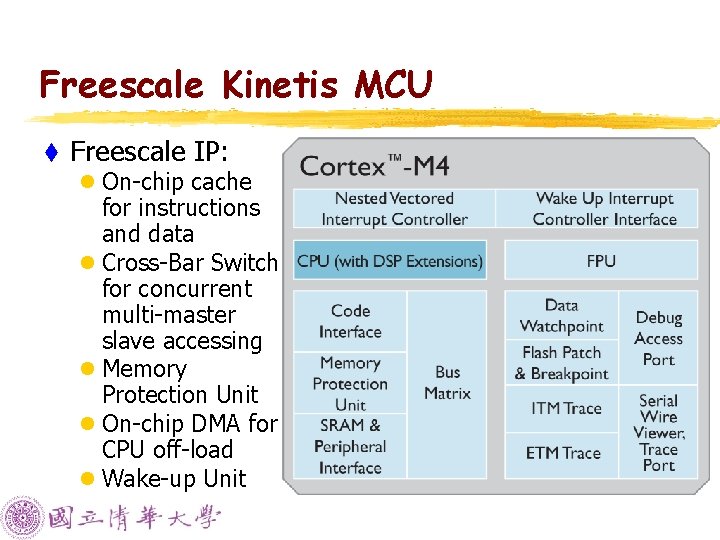

ARM Cortex-M 4 t Conceptually M 4 is M 3 + DSP instructions, with optional FPU. Key features include: l ARMv 7 architecture with an instruction set of n Thumb, Thumb-2, 1 -cycle 32 -bit hardware multiply, 212 cycle 32 -bit hardware divide, saturated math support, DSP extension (1 -cycle MAC and SIMD arithmetic), FP extension (option) l 3 -stage pipeline with branch speculation l 1~240 physical interrupts plus NMI, 12 -cycle latency l Integrated sleep modes l 8 region memory protection unit (MPU) (option) t Freescale Kinetis microcontroller based on M 4

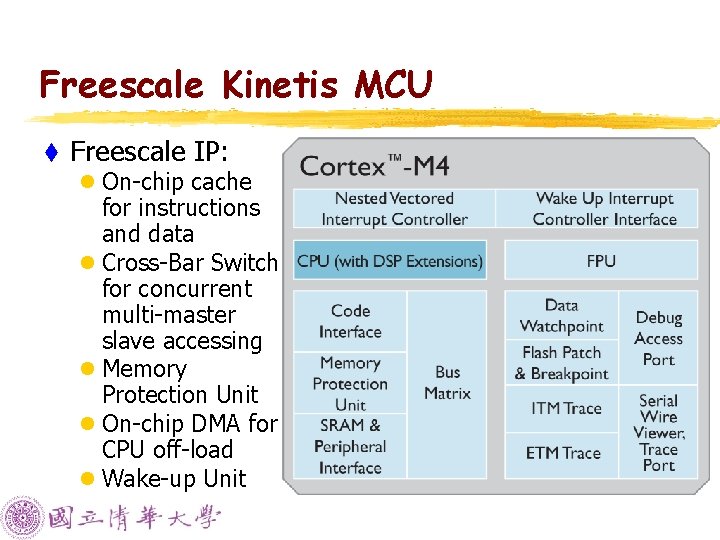

Freescale Kinetis MCU t Freescale IP: l On-chip cache for instructions and data l Cross-Bar Switch for concurrent multi-master slave accessing l Memory Protection Unit l On-chip DMA for CPU off-load l Wake-up Unit

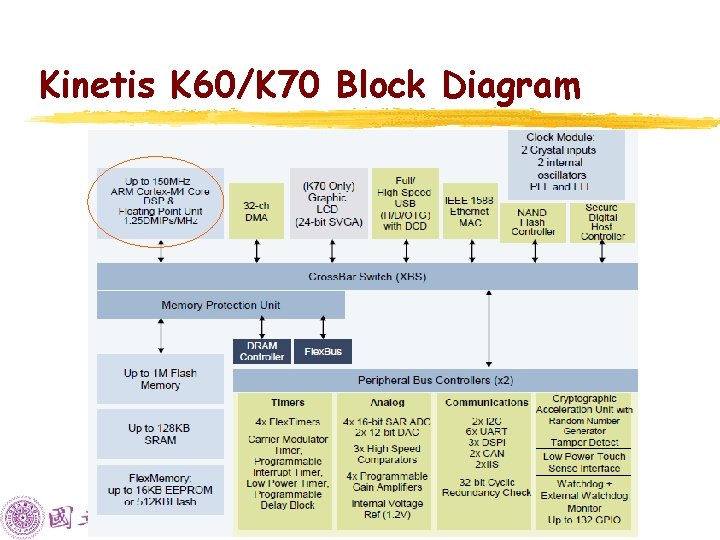

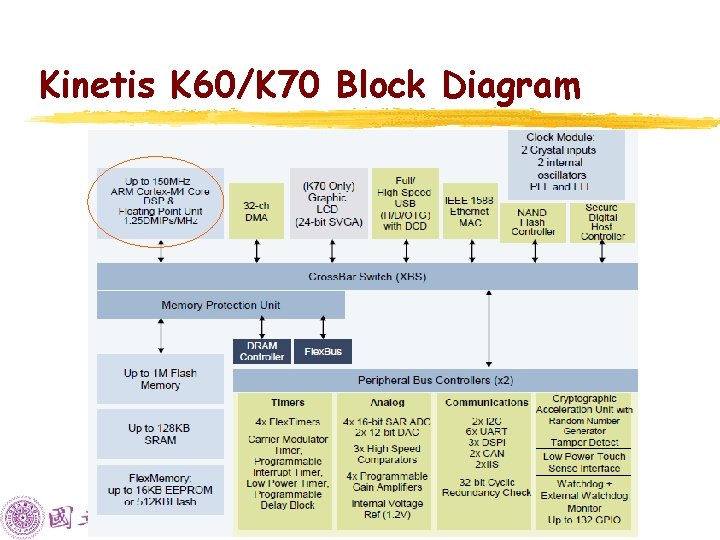

Kinetis K 60/K 70 Block Diagram

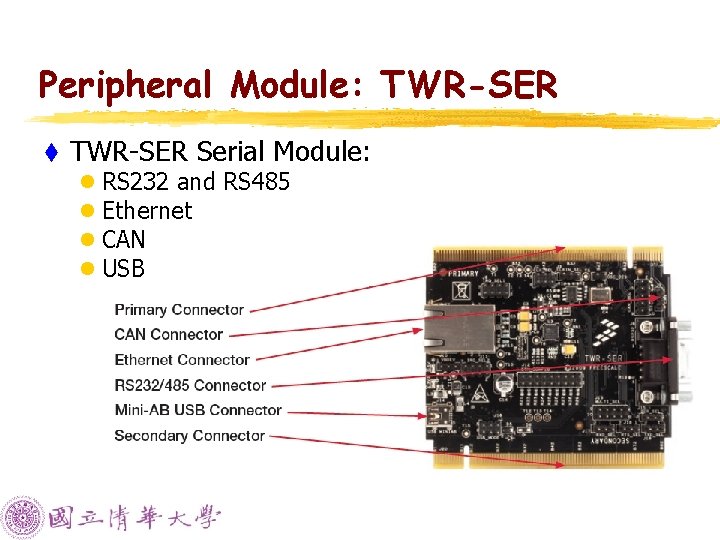

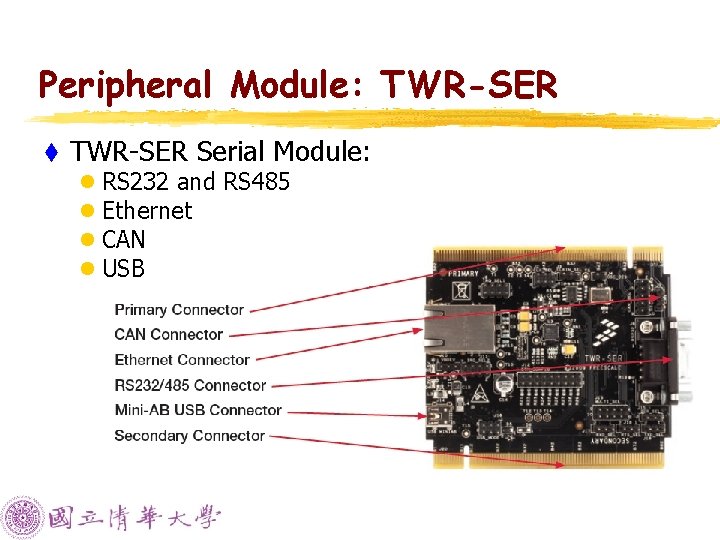

Peripheral Module: TWR-SER t TWR-SER Serial Module: l RS 232 and RS 485 l Ethernet l CAN l USB

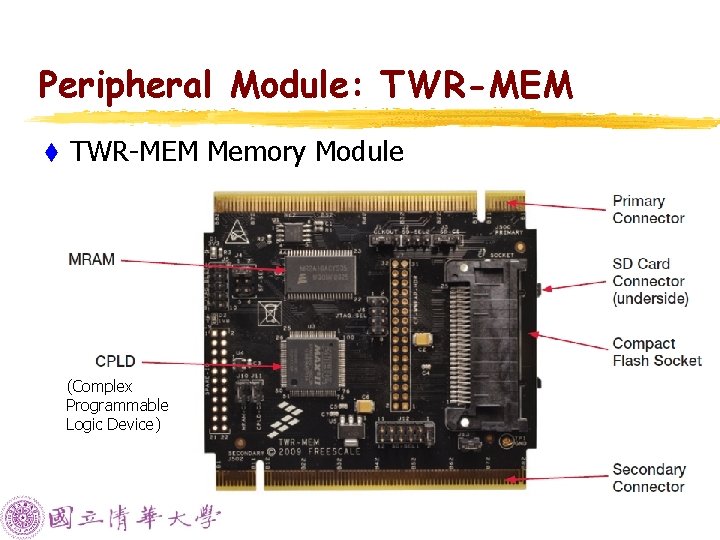

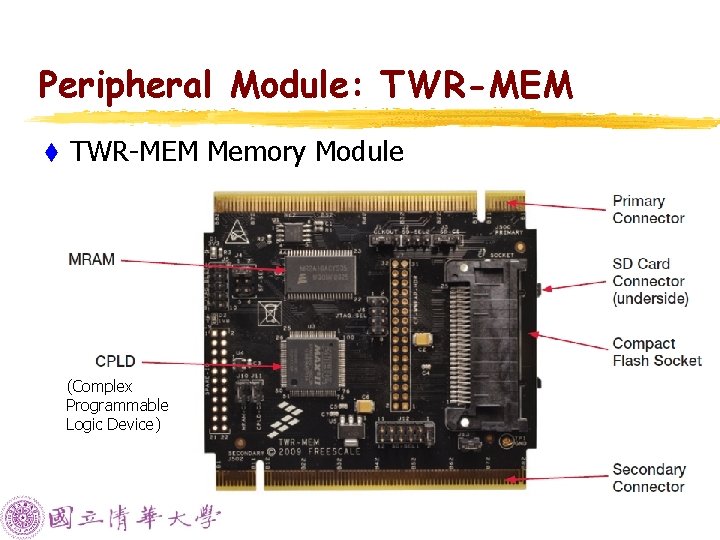

Peripheral Module: TWR-MEM t TWR-MEM Memory Module (Complex Programmable Logic Device)

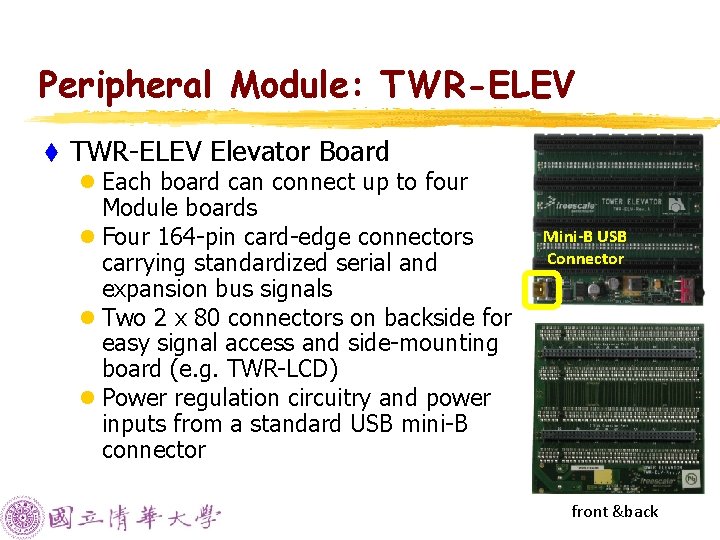

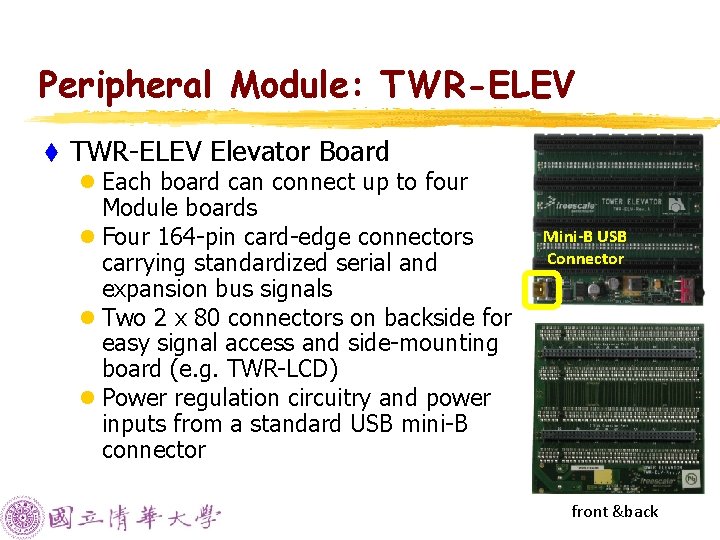

Peripheral Module: TWR-ELEV t TWR-ELEV Elevator Board l Each board can connect up to four Module boards l Four 164 -pin card-edge connectors carrying standardized serial and expansion bus signals l Two 2 x 80 connectors on backside for easy signal access and side-mounting board (e. g. TWR-LCD) l Power regulation circuitry and power inputs from a standard USB mini-B connector Mini-B USB Connector front &back

Related URL t www. freescale. com/tower t https: //community. freescale. com/community/to wer t www. freescale. com/mqx