COMPUTER SYSTEM ARCHITECTURE Prof Lee dae hoon Computer

- Slides: 24

COMPUTER SYSTEM ARCHITECTURE Prof : Lee dae hoon

Computer System Analysis …… for CPU Unit 1. Central Processing Unit 2. Advanced Computer system Unit 3. Personal Computer system Unit 4. Operation Overview

Unit. 1 Central Processing Unit Analysis 1. Architecture Analysis 2. Instruction Analysis 3. Performance Analysis

1. Architecture Analysis 1. 1 Operation Device : ALU(Arithmetic Logic Unit) 1. 2 Memory Device : Register 1. 3 Decoding Device : Decoder 1. 4 Control Device : Controller, 3 -state Buffer 1. 5 System bus : Data bus, Address bus, Control bus

1. 1. 1 ALU Arithmetic Unit : Adder Logic Unit : MUX, AND, OR, XOR, NOT

1. 1. 2 Register Unit AC : Accumulator IR : Instruction Register MAR : Memory Address Register MBR : Memory Buffer Register PC : Program Counter Stack Status(Flag) Register

1. 1. 3 Decoding Unit Decoder Multiplexer

1. 1. 4 Control Unit Controller, 3 -state Buffer ID : Instruction decoder CAR : Control Address Register CM : Control Memory CBR : Control buffer Register SBR : Subroutine Buffer Register SM : Sequencing Control Module

1. 1. 5 System Bus Data bus : dual path parallel bus Address bus : single path parallel bus Control bus :

2. Instruction Analysis 2. 1 Instruction Process 2. 2 Instruction format 2. 3 Addressing Instruction format 2. 4 Specify the method of Addressing

2. 1. 1 Instruction Process Fetch Decoding Execution Store Interrupt

2. 1. 2 Instruction Format Op-code : ADD, SUB, MUL, DIV, LD, STO Operand : Address, Data

2. 1. 3 Addressing Instruction format 0 -Addressing format 1 -Addressing format 2 -Addressing format 3 -Addressing format

2. 1. 4 Specify the method of Addressing Immediate Addressing Direct Addressing Indirect Addressing Register Indirect Addressing Displacement Addressing Stack Addressing

3. Performance Analysis 3. 1 Pipeline Technique 3. 2 RISC Processing Technique 3. 3 Super scalar Architecture 3. 4 Super pipeline Architecture 3. 5 VLIW Architecture 3. 6 Co-processor

Unit. 2 Advanced Computer system 1. Parallel Computer System 1. 1 Parallel Processing 1. 2 Multiple Processor system 1. 3 High Technology Computer system

1. 1 Parallel Processing SISD SIMD MISD MIMD

1. 2 Multiple Processor system Shared-memory system Distributed- Shared-memory system

1. 3 High Technology Computer system 1. Neural computer system 2. Optical Computer system 3. Fuzzy Computer system

Unit. 3 Personal Computer system 1. 2. 3. 4. 5. 6. 7. 8. 9. CPU Memory Device Main board Hard Disk Driver Optical disk Driver Graphic Card C-MOS setup Chip set BUS System

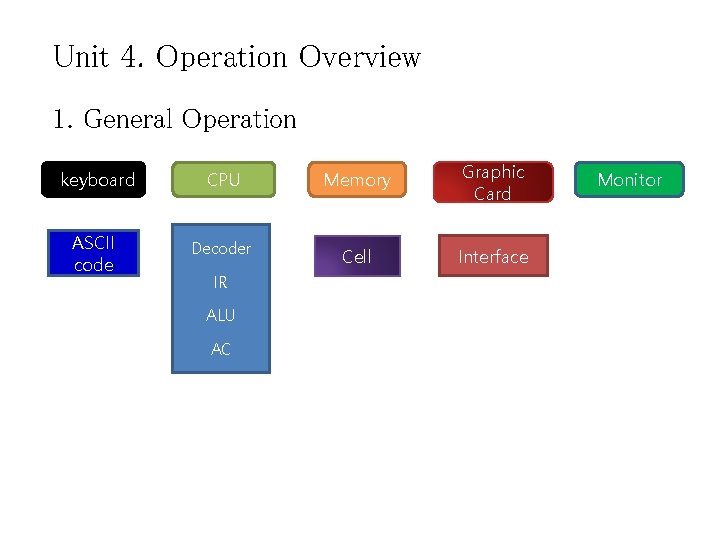

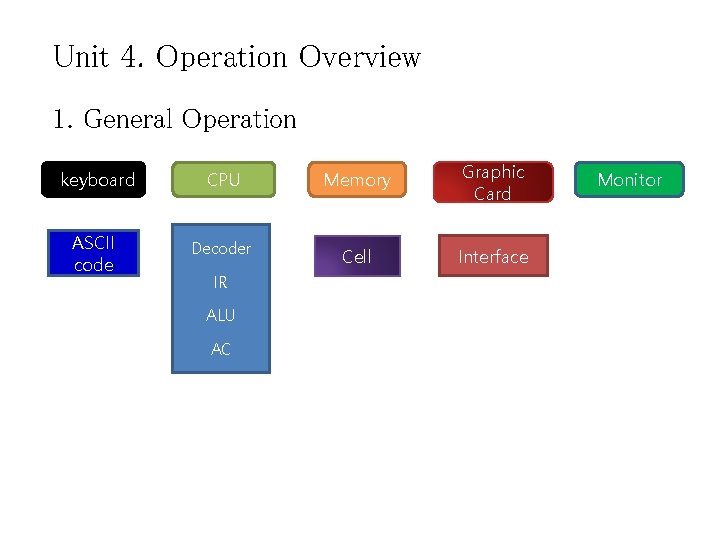

Unit 4. Operation Overview 1. General Operation keyboard CPU Memory Graphic Card ASCII code Decoder Cell Interface IR ALU AC Monitor

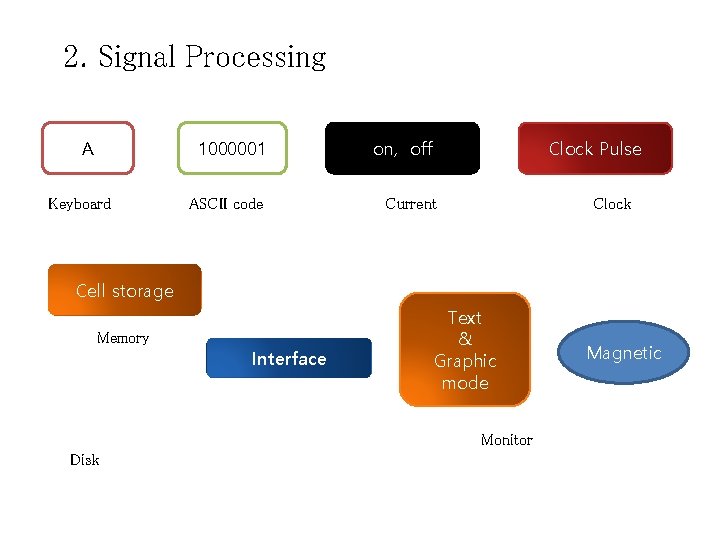

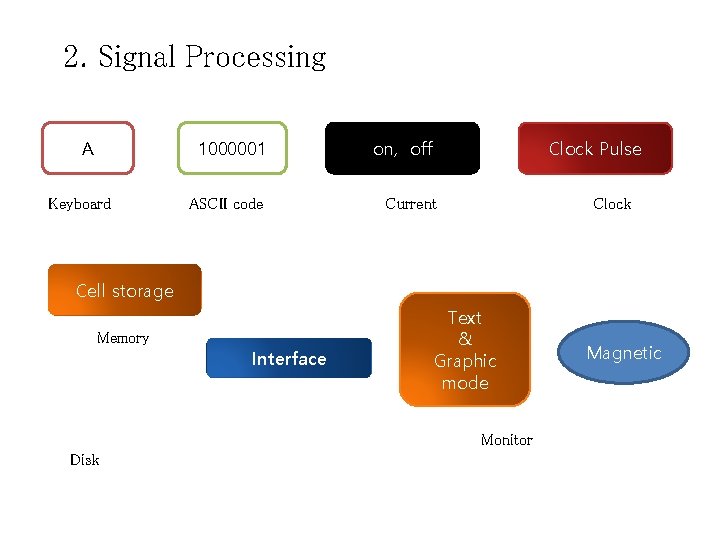

2. Signal Processing A 1000001 Keyboard ASCII code on, off Clock Pulse Current Clock Cell storage Memory Interface Text & Graphic mode Monitor Disk Magnetic

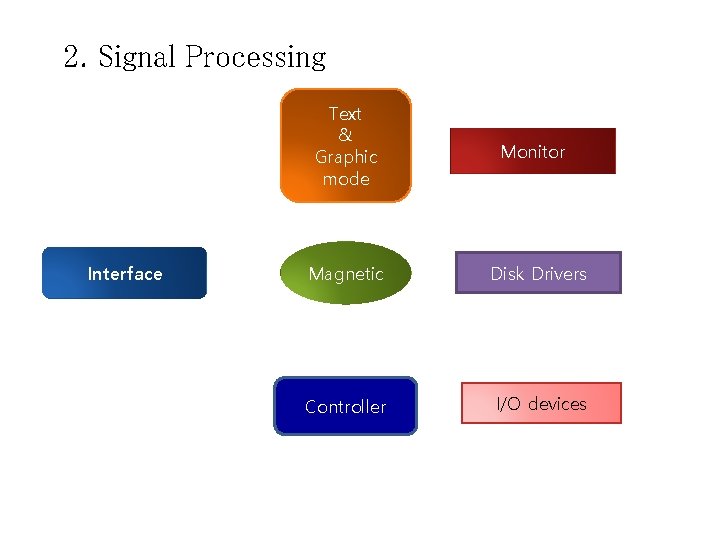

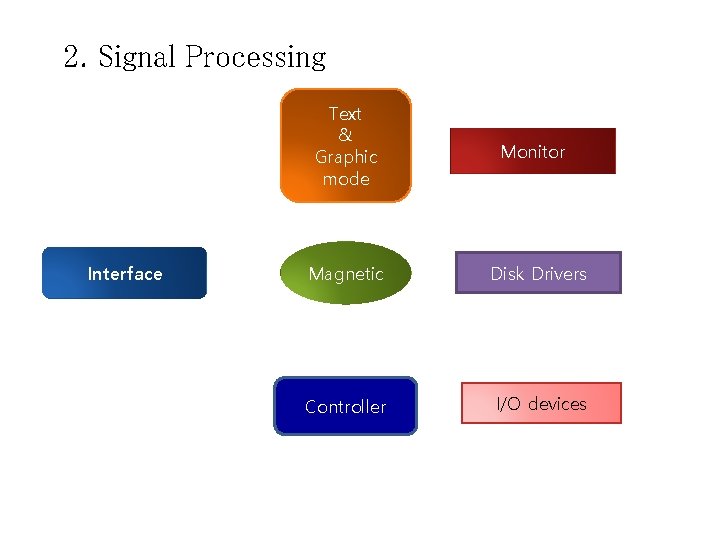

2. Signal Processing Text & Graphic mode Interface Monitor Magnetic Disk Drivers Controller I/O devices

Q&A