Computer Architecture Organization Instructions Language of Computer Engr

![Example # 6 l Convert in machine language. – – 23 A[300] = h Example # 6 l Convert in machine language. – – 23 A[300] = h](https://slidetodoc.com/presentation_image/aa2f992e7b1dac143fa216b2d5064402/image-23.jpg)

- Slides: 26

Computer Architecture & Organization Instructions: Language of Computer Engr. Umbreen Sabir Computer Engineering Department, University of Engg. & Technology Taxila. 1 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

Introduction l Instructions: – l Instruction Set: – l The vocabulary of commands understood by a given architecture. Stored Program Concept: – 2 The words of a computer language. The idea that instructions and data of many types can be stored in memory as numbers, leading to the stored program computer. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

Operations of Computer Hardware l l Every computer must be able to perform arithmetic. MIPS assembly language notation – – l l Notation is rigid. Every instruction must follow this format. To perform operation. – – 3 add a, b, c Add two variables b and c and put sum in a. a=b+c+d+e add a, b, c # The sum of b & c is placed in a. add a, a, d # The sum of b, c & d is now in a. add a, a, e # The sum of b, c, d & e is now in a. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

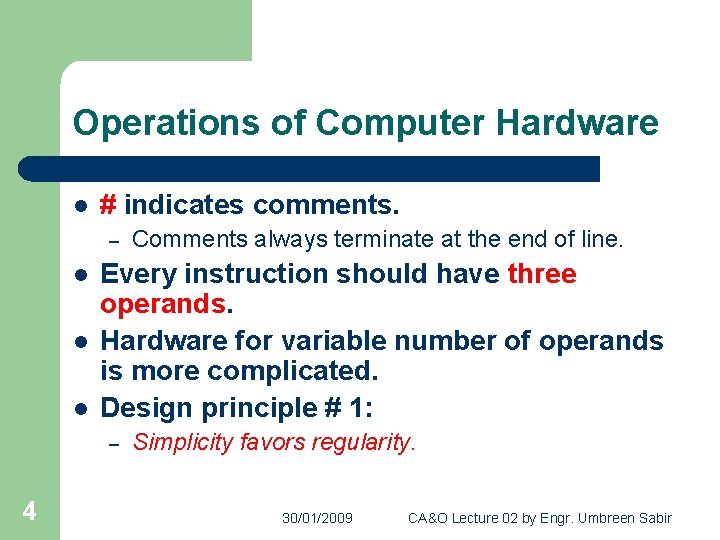

Operations of Computer Hardware l # indicates comments. – l l l Every instruction should have three operands. Hardware for variable number of operands is more complicated. Design principle # 1: – 4 Comments always terminate at the end of line. Simplicity favors regularity. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

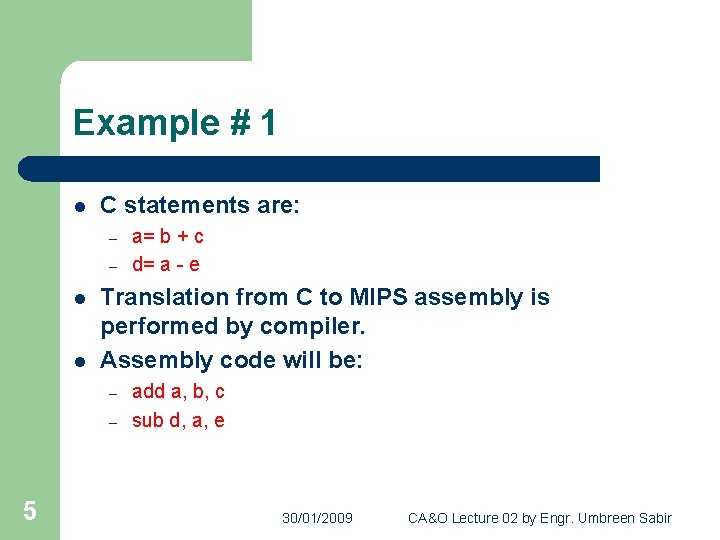

Example # 1 l C statements are: – – l l Translation from C to MIPS assembly is performed by compiler. Assembly code will be: – – 5 a= b + c d= a - e add a, b, c sub d, a, e 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

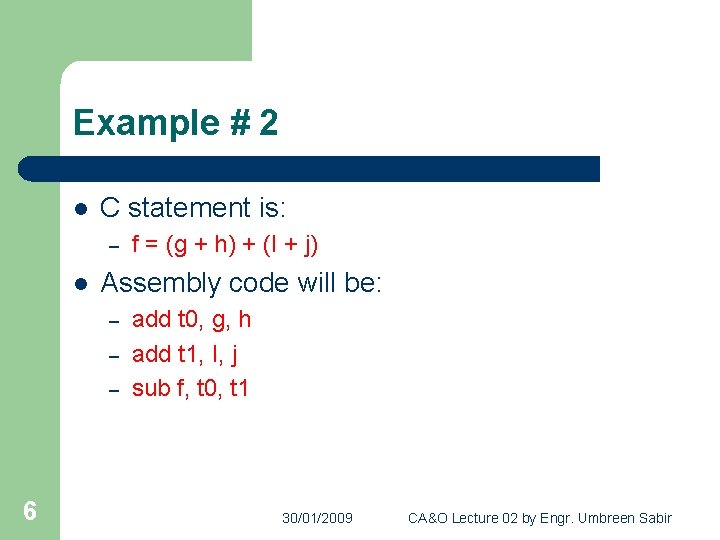

Example # 2 l C statement is: – l Assembly code will be: – – – 6 f = (g + h) + (I + j) add t 0, g, h add t 1, I, j sub f, t 0, t 1 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

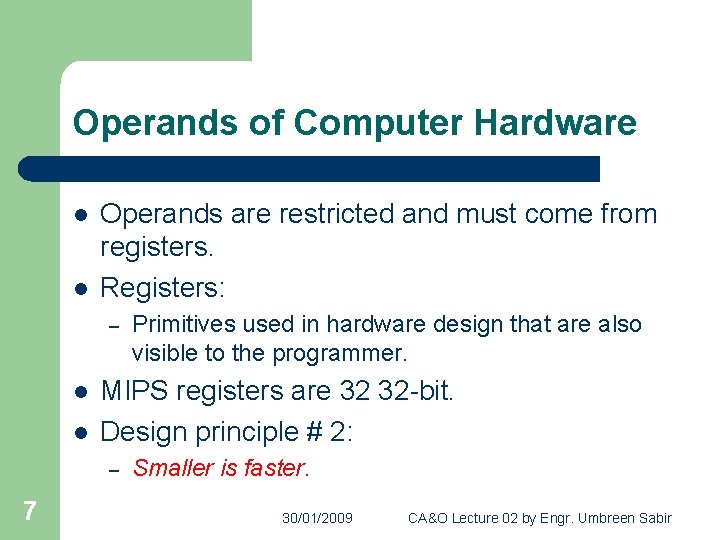

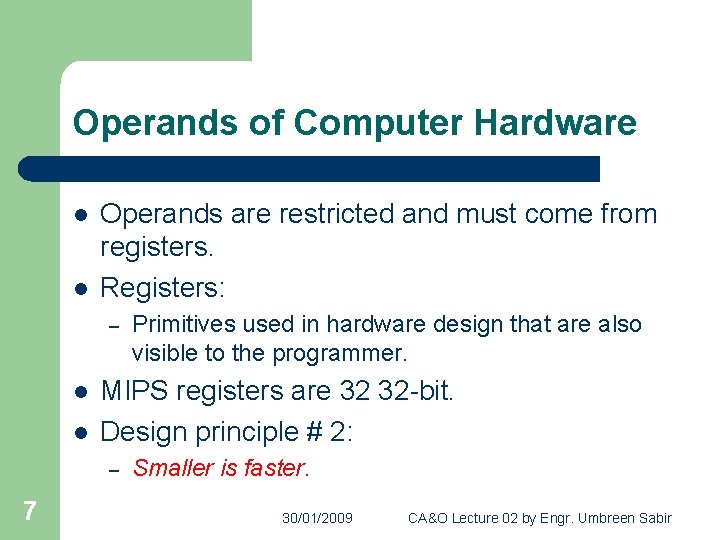

Operands of Computer Hardware l l Operands are restricted and must come from registers. Registers: – l l MIPS registers are 32 32 -bit. Design principle # 2: – 7 Primitives used in hardware design that are also visible to the programmer. Smaller is faster. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

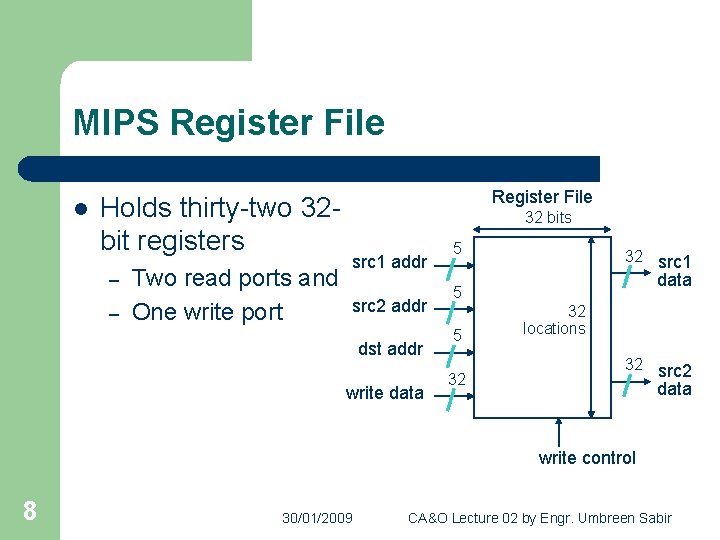

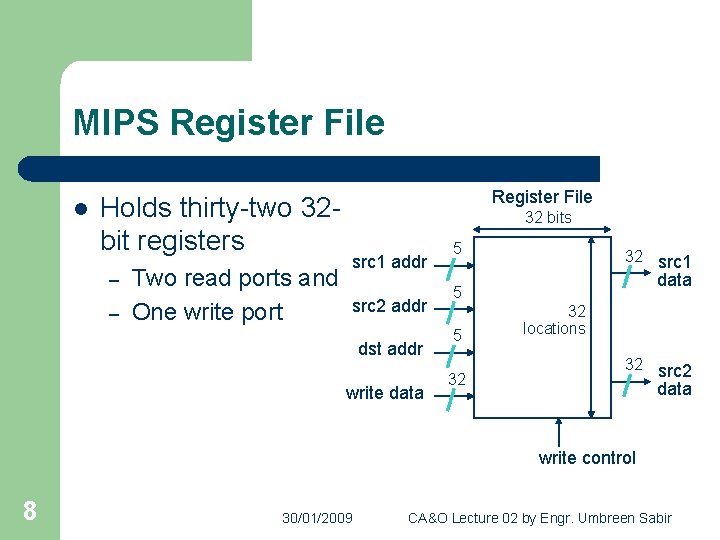

MIPS Register File l Holds thirty-two 32 bit registers – – Two read ports and One write port Register File 32 bits src 1 addr src 2 addr dst addr write data 5 32 src 1 data 5 5 32 32 locations 32 src 2 data write control 8 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

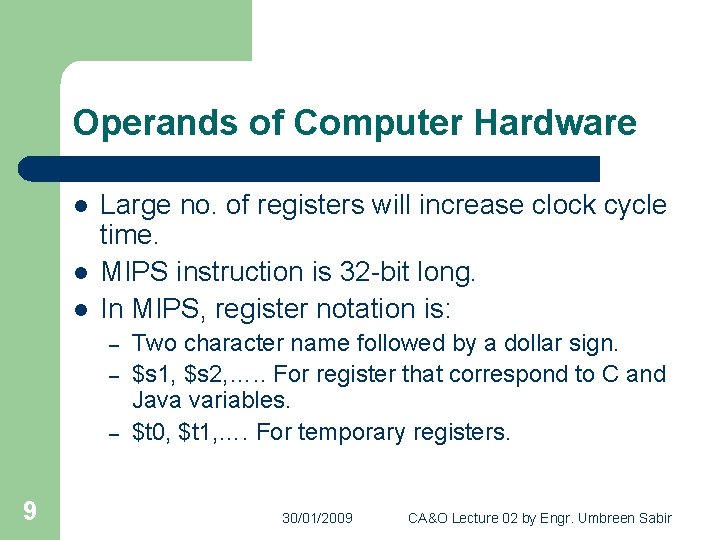

Operands of Computer Hardware l l l Large no. of registers will increase clock cycle time. MIPS instruction is 32 -bit long. In MIPS, register notation is: – – – 9 Two character name followed by a dollar sign. $s 1, $s 2, …. . For register that correspond to C and Java variables. $t 0, $t 1, …. For temporary registers. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

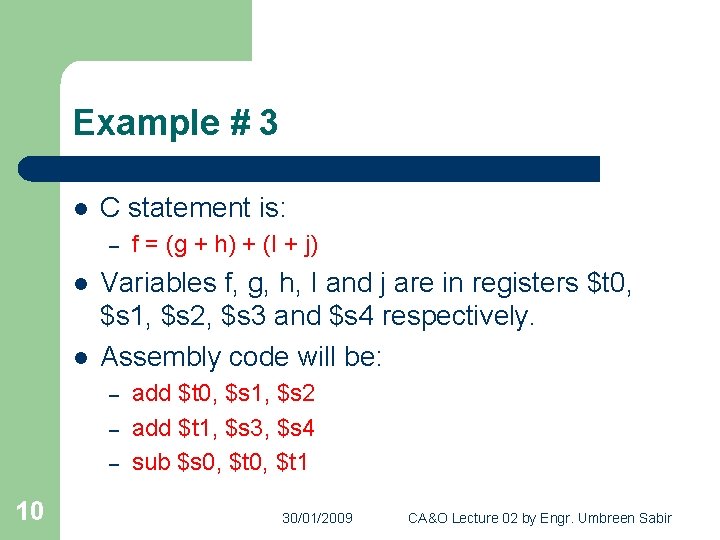

Example # 3 l C statement is: – l l Variables f, g, h, I and j are in registers $t 0, $s 1, $s 2, $s 3 and $s 4 respectively. Assembly code will be: – – – 10 f = (g + h) + (I + j) add $t 0, $s 1, $s 2 add $t 1, $s 3, $s 4 sub $s 0, $t 1 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

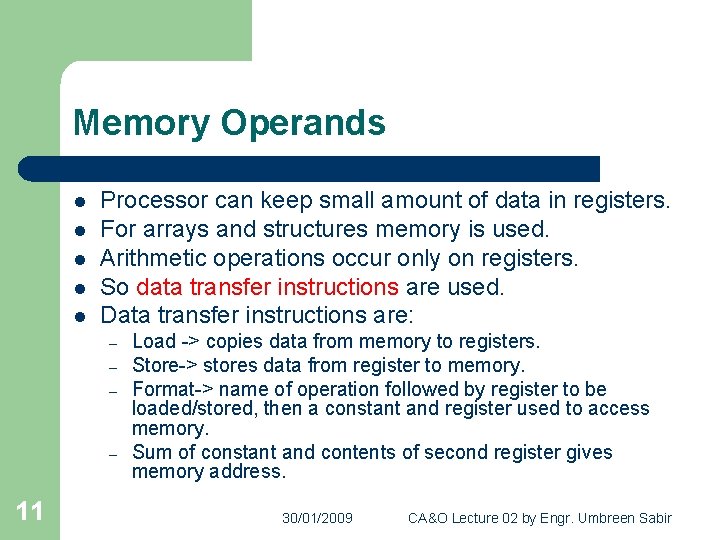

Memory Operands l l l Processor can keep small amount of data in registers. For arrays and structures memory is used. Arithmetic operations occur only on registers. So data transfer instructions are used. Data transfer instructions are: – – 11 Load -> copies data from memory to registers. Store-> stores data from register to memory. Format-> name of operation followed by register to be loaded/stored, then a constant and register used to access memory. Sum of constant and contents of second register gives memory address. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

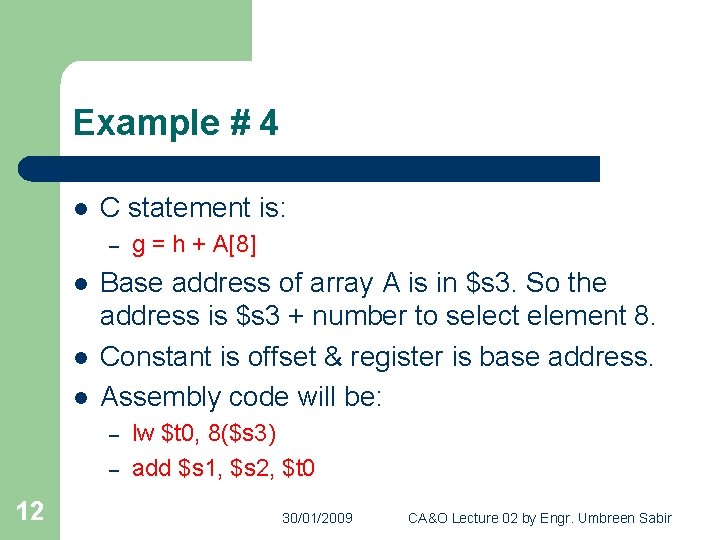

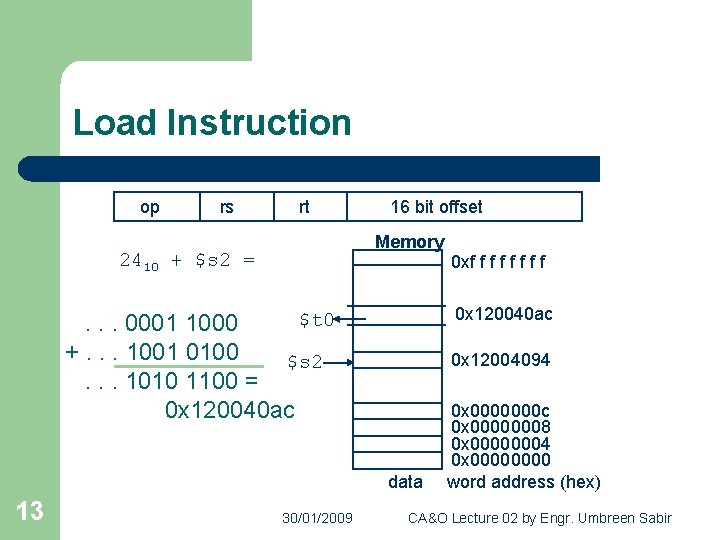

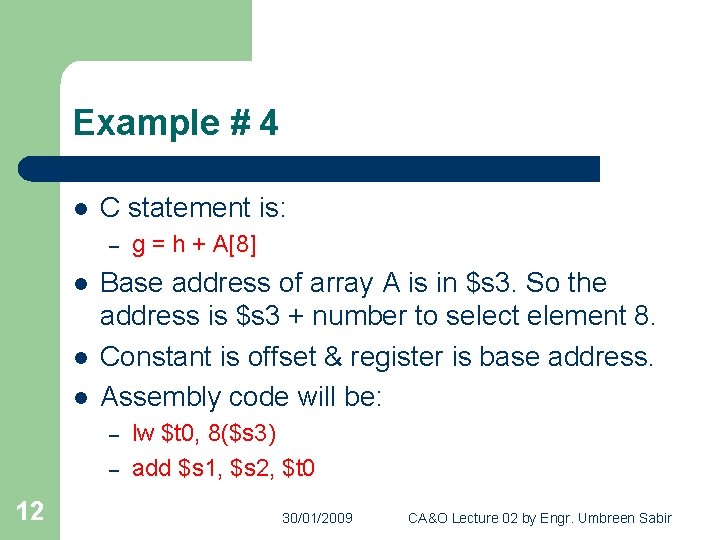

Example # 4 l C statement is: – l l l Base address of array A is in $s 3. So the address is $s 3 + number to select element 8. Constant is offset & register is base address. Assembly code will be: – – 12 g = h + A[8] lw $t 0, 8($s 3) add $s 1, $s 2, $t 0 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

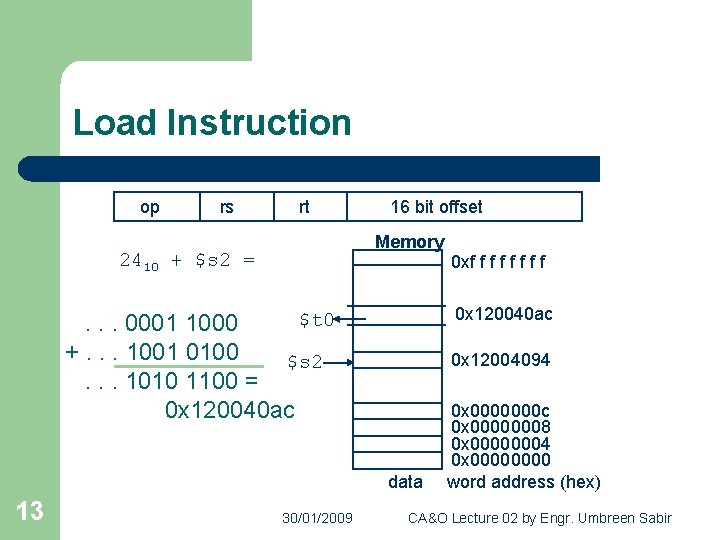

Load Instruction op rs rt 16 bit offset Memory 2410 + $s 2 = 0 xf f f f 0 x 120040 ac $t 0. . . 0001 1000 +. . . 1001 0100 $s 2. . . 1010 1100 = 0 x 120040 ac 0 x 12004094 data 13 30/01/2009 0 x 0000000 c 0 x 00000008 0 x 00000004 0 x 0000 word address (hex) CA&O Lecture 02 by Engr. Umbreen Sabir

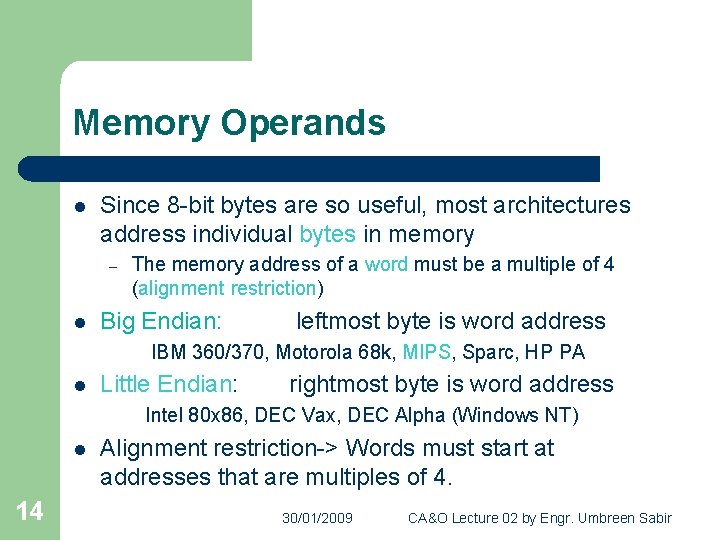

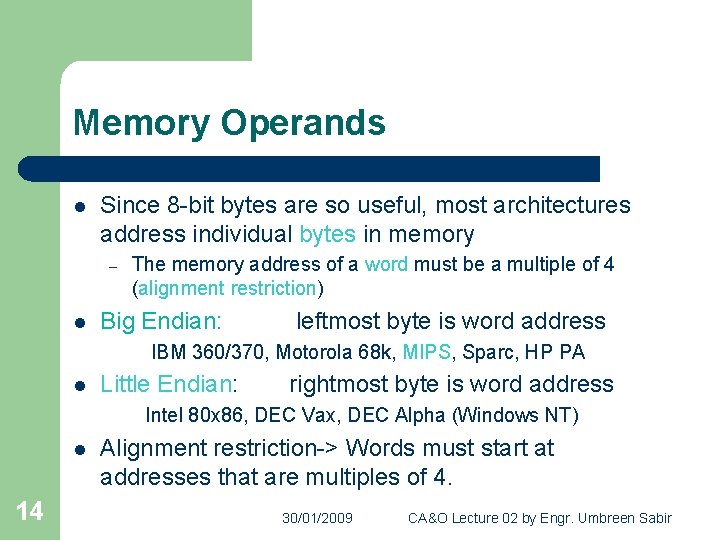

Memory Operands l Since 8 -bit bytes are so useful, most architectures address individual bytes in memory – l The memory address of a word must be a multiple of 4 (alignment restriction) Big Endian: leftmost byte is word address IBM 360/370, Motorola 68 k, MIPS, Sparc, HP PA l Little Endian: rightmost byte is word address Intel 80 x 86, DEC Vax, DEC Alpha (Windows NT) l 14 Alignment restriction-> Words must start at addresses that are multiples of 4. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

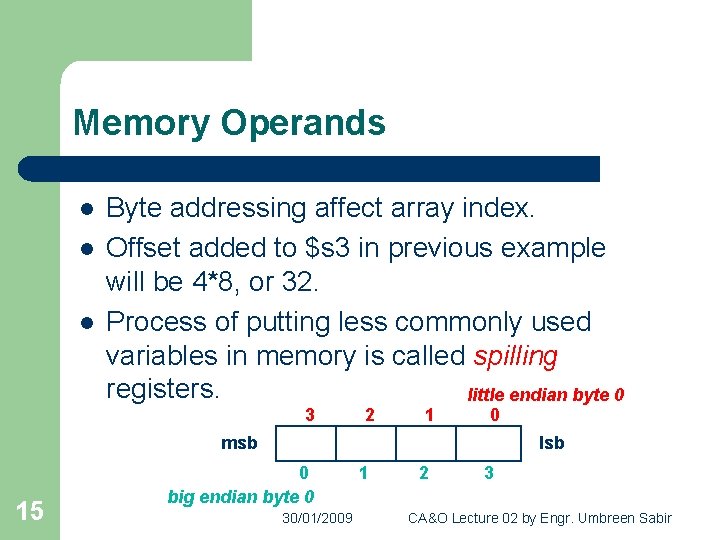

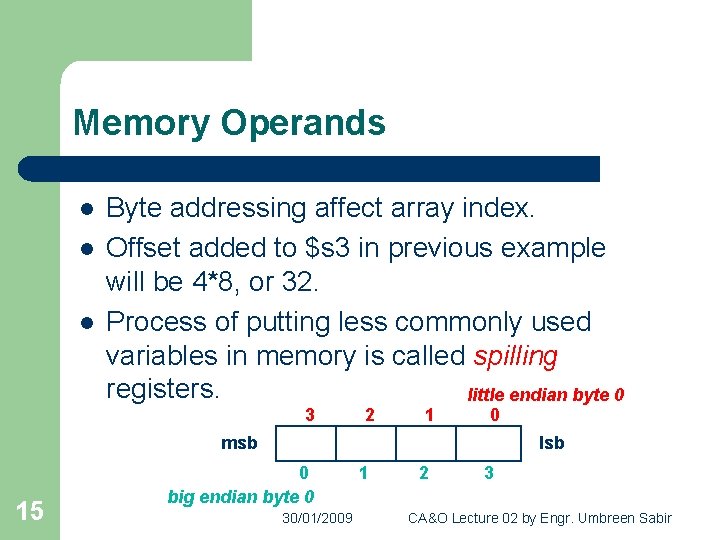

Memory Operands l l l Byte addressing affect array index. Offset added to $s 3 in previous example will be 4*8, or 32. Process of putting less commonly used variables in memory is called spilling registers. little endian byte 0 3 2 1 0 msb 15 lsb 0 big endian byte 0 30/01/2009 1 2 3 CA&O Lecture 02 by Engr. Umbreen Sabir

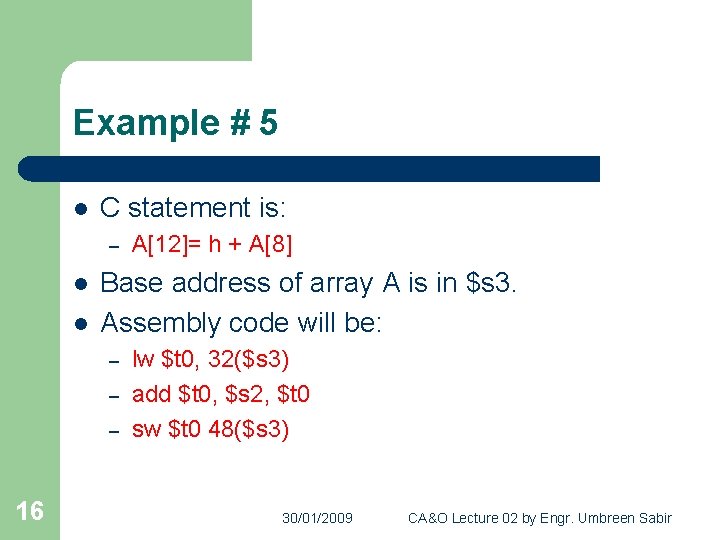

Example # 5 l C statement is: – l l Base address of array A is in $s 3. Assembly code will be: – – – 16 A[12]= h + A[8] lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0 48($s 3) 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

Constant or Immediate Operands l l Constants are used in instructions for certain operations. E. g. to increment an index. Add instruction with constant is: – l Design principle # 3 – 17 addi $s 3, 4 # s 3= s 3 + 4 Make the common case fast. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

MIPS Immediate Instructions l l Small constants are used often in typical code Possible approaches? – – – 18 put “typical constants” in memory and load them create hard-wired registers (like $zero) for constants like 1 have special instructions that contain constants ! 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

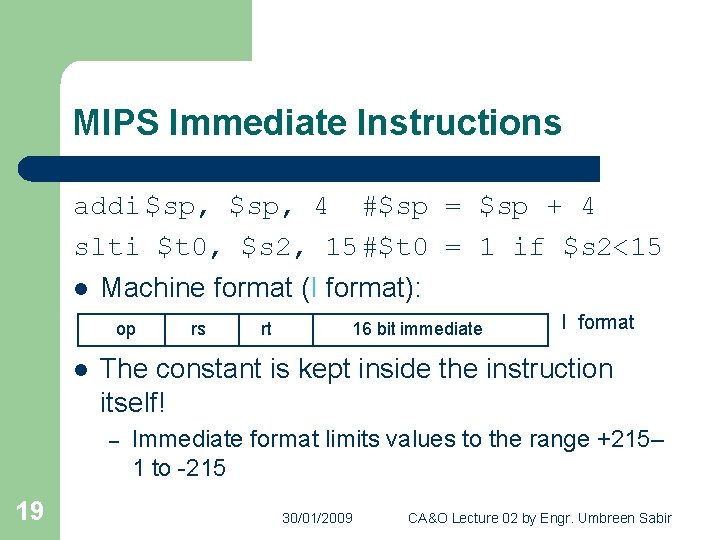

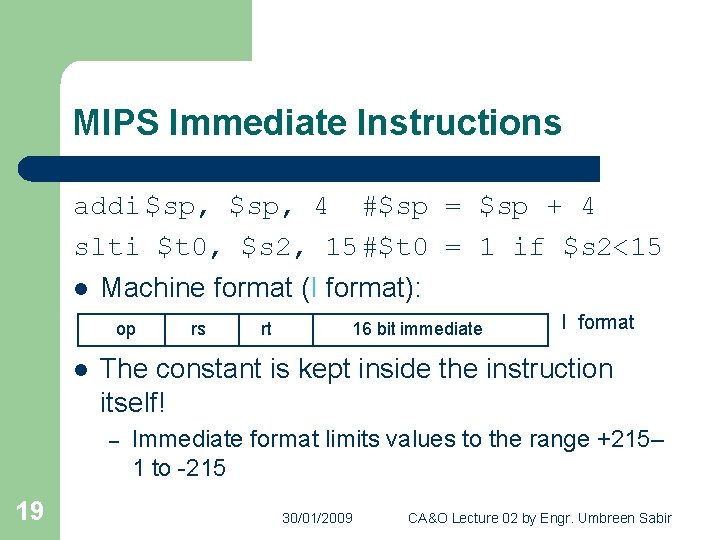

MIPS Immediate Instructions addi $sp, 4 #$sp = $sp + 4 slti $t 0, $s 2, 15#$t 0 = 1 if $s 2<15 l Machine format (I format): op l rt 16 bit immediate I format The constant is kept inside the instruction itself! – 19 rs Immediate format limits values to the range +215– 1 to -215 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

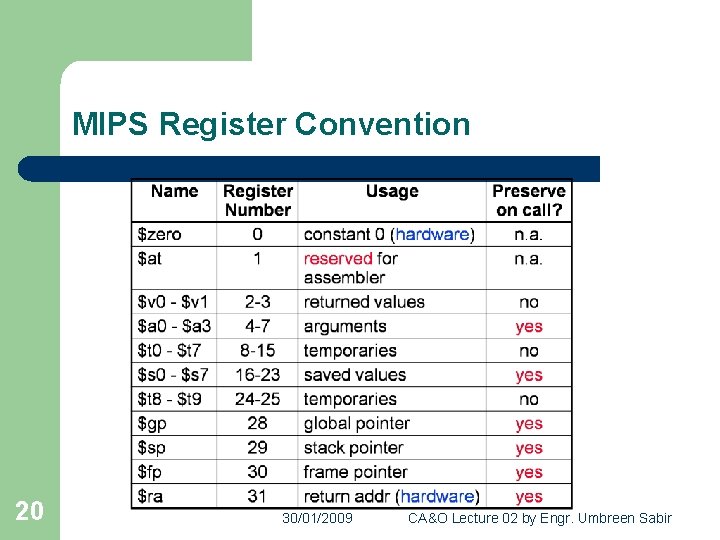

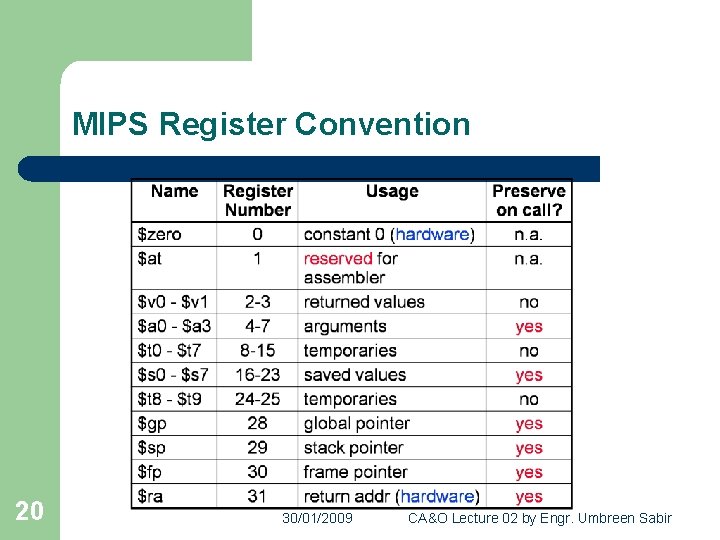

MIPS Register Convention 20 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

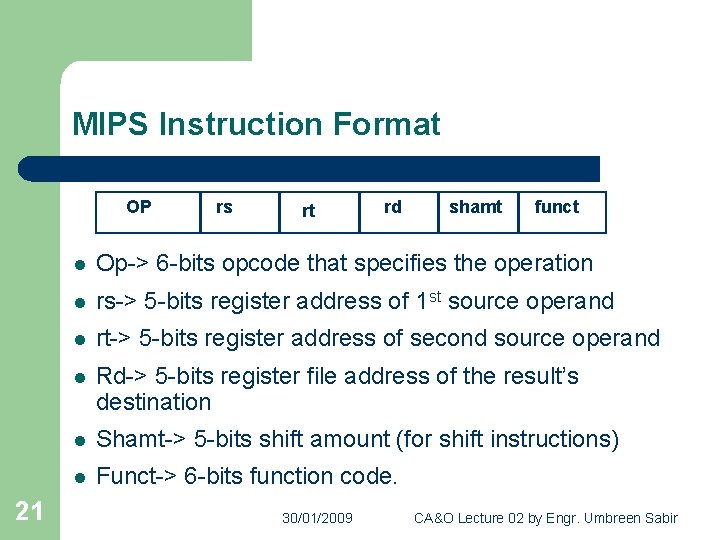

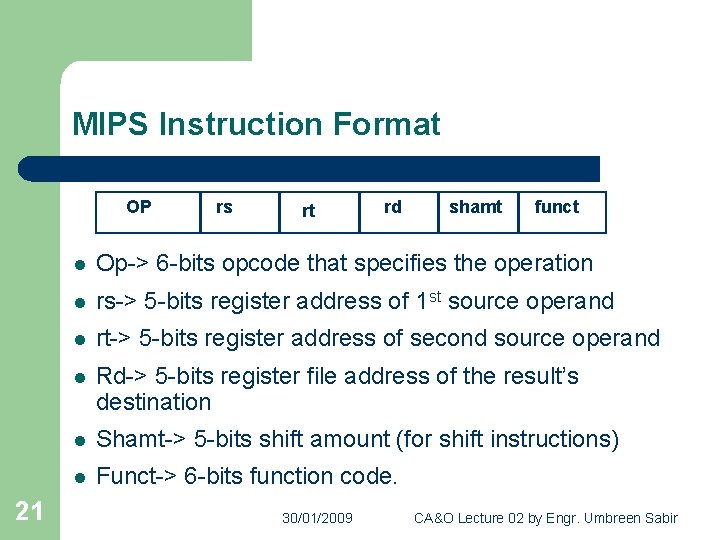

MIPS Instruction Format OP 21 rs rt rd shamt funct l Op-> 6 -bits opcode that specifies the operation l rs-> 5 -bits register address of 1 st source operand l rt-> 5 -bits register address of second source operand l Rd-> 5 -bits register file address of the result’s destination l Shamt-> 5 -bits shift amount (for shift instructions) l Funct-> 6 -bits function code. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

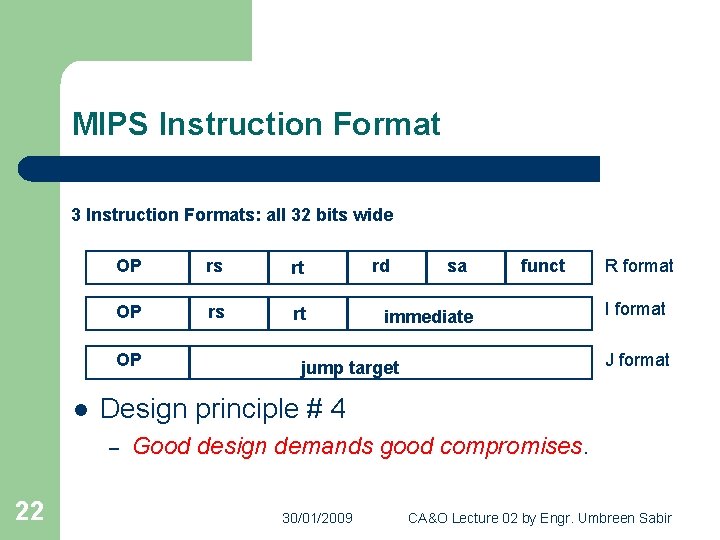

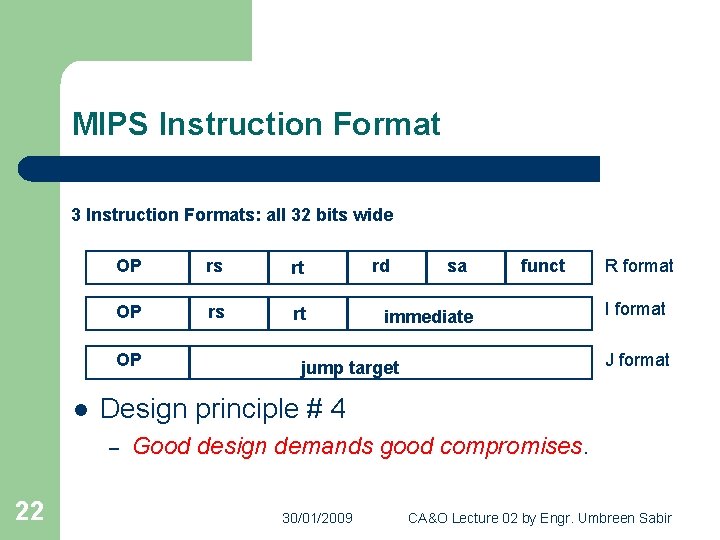

MIPS Instruction Format 3 Instruction Formats: all 32 bits wide OP rs rt OP l sa funct immediate R format I format J format jump target Design principle # 4 – 22 rd Good design demands good compromises. 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

![Example 6 l Convert in machine language 23 A300 h Example # 6 l Convert in machine language. – – 23 A[300] = h](https://slidetodoc.com/presentation_image/aa2f992e7b1dac143fa216b2d5064402/image-23.jpg)

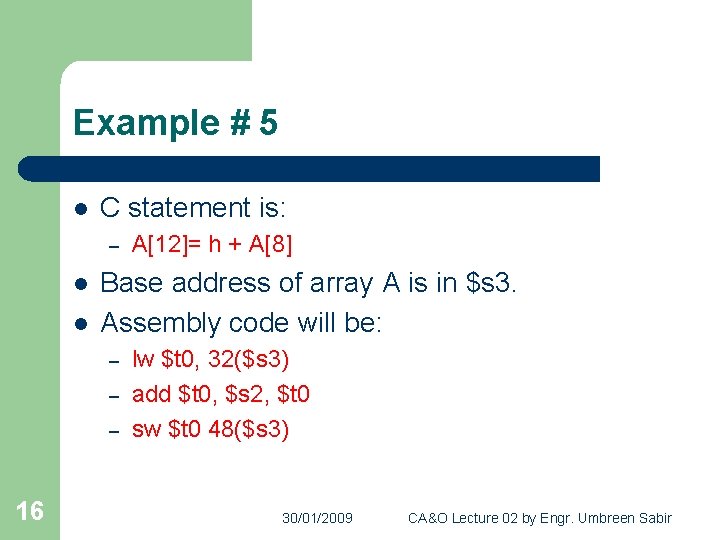

Example # 6 l Convert in machine language. – – 23 A[300] = h + A[300]. Lw $t 0, 1200($t 1) Lw $t 0, $s 2, $t 0 Sw $t 0, 1200($t 1). 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

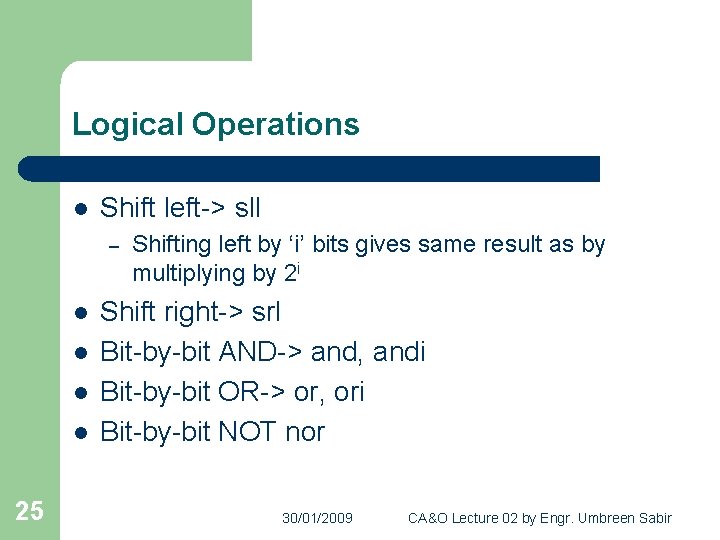

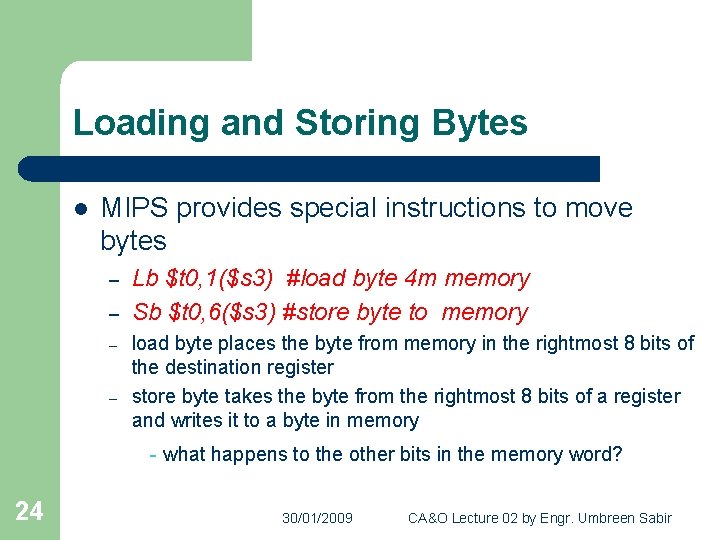

Loading and Storing Bytes l MIPS provides special instructions to move bytes – – Lb $t 0, 1($s 3) #load byte 4 m memory Sb $t 0, 6($s 3) #store byte to memory load byte places the byte from memory in the rightmost 8 bits of the destination register store byte takes the byte from the rightmost 8 bits of a register and writes it to a byte in memory - what happens to the other bits in the memory word? 24 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

Logical Operations l Shift left-> sll – l l 25 Shifting left by ‘i’ bits gives same result as by multiplying by 2 i Shift right-> srl Bit-by-bit AND-> and, andi Bit-by-bit OR-> or, ori Bit-by-bit NOT nor 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir

Next Lecture and Reminders l Next lecture – MIPS ISA Review l 26 Reading assignment – Chapter 2 30/01/2009 CA&O Lecture 02 by Engr. Umbreen Sabir