Ch 7 Design of a USB Protocol Analyzer

Ch. 7: Design of a USB Protocol Analyzer • Major Concepts to be Learned – Basic features and techniques used in the Universal Serial Bus (USB) I/O protocol • Refer to USB tutorial (on class web page) for more detailed information on the USB protocol – How to design a Verilog circuit that “understands” and works with a modern PC interface such as USB – Useful concepts found in USB • • Differential signalling Non-return-to-zero-inverted (NRZI) encoding Cyclic redundancy check (CRC) coding Bit stuffing and destuffing "Computer Design" by Sunggu Lee

Features of USB Protocol • Hot-pluggable • High-performance (up to 480 Mbps for USB 2. 0 and 12 Mbps for USB 1. 1) and low-cost • Supports up to 127 devices for each root hub • Provides automatic error detection and recovery • Provides cable power and power management features • Completely external to the PC • Simple and standard connector "Computer Design" by Sunggu Lee

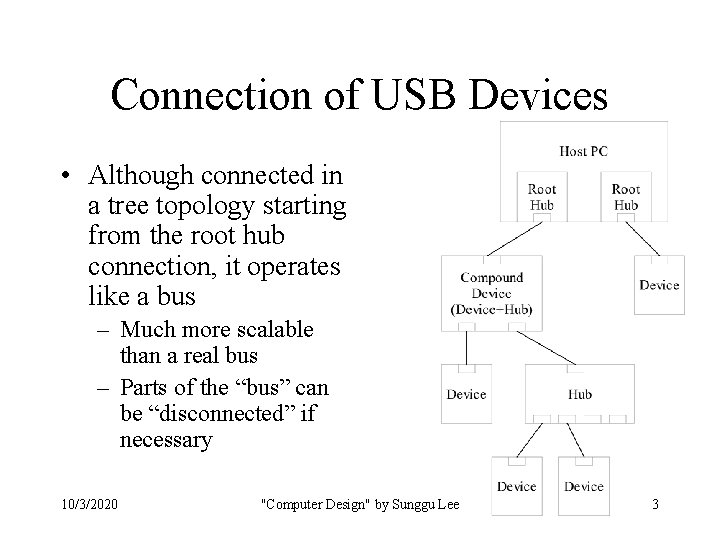

Connection of USB Devices • Although connected in a tree topology starting from the root hub connection, it operates like a bus – Much more scalable than a real bus – Parts of the “bus” can be “disconnected” if necessary 10/3/2020 "Computer Design" by Sunggu Lee 3

Initialization Sequence • New USB device recognized and configured – Attachment of device changes voltage on a signal wire – USB host controller driver in host PC periodically checks for new devices – Port to which new device is attached is enabled – Device is reset by a command from the host PC – SETUP packets are used to configure the device • Assigns a unique USB address to the new USB device • Reads descriptors from device to determine characteristics of device • Reserves resource required by device "Computer Design" by Sunggu Lee

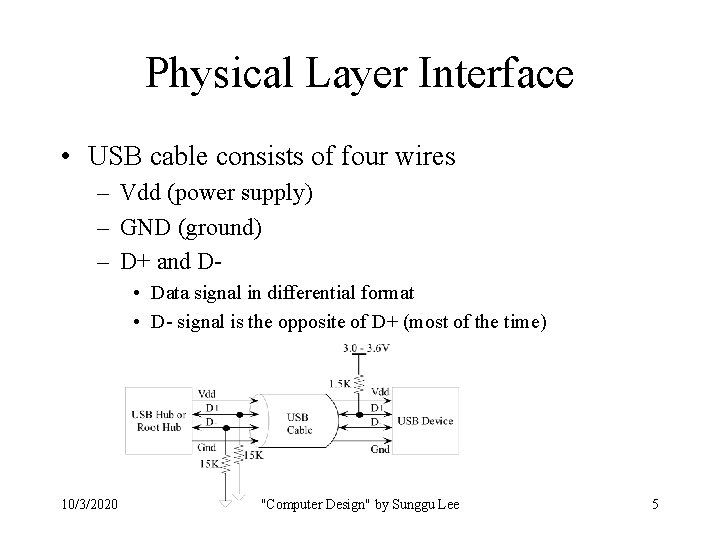

Physical Layer Interface • USB cable consists of four wires – Vdd (power supply) – GND (ground) – D+ and D • Data signal in differential format • D- signal is the opposite of D+ (most of the time) 10/3/2020 "Computer Design" by Sunggu Lee 5

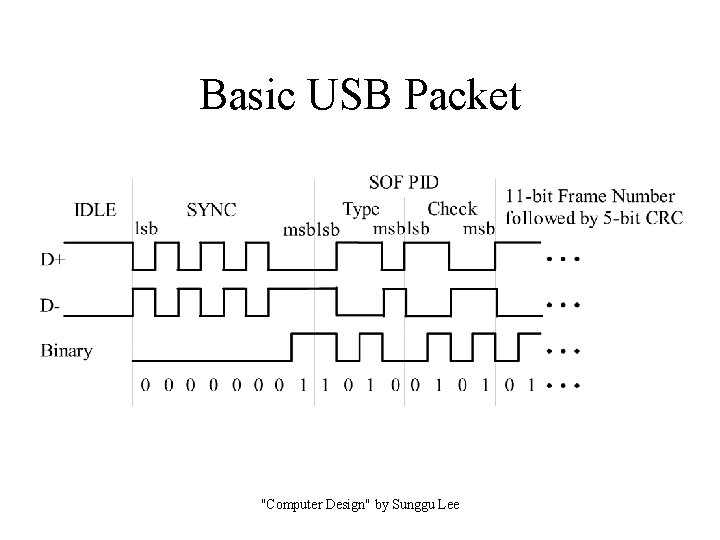

Basic USB Packet "Computer Design" by Sunggu Lee

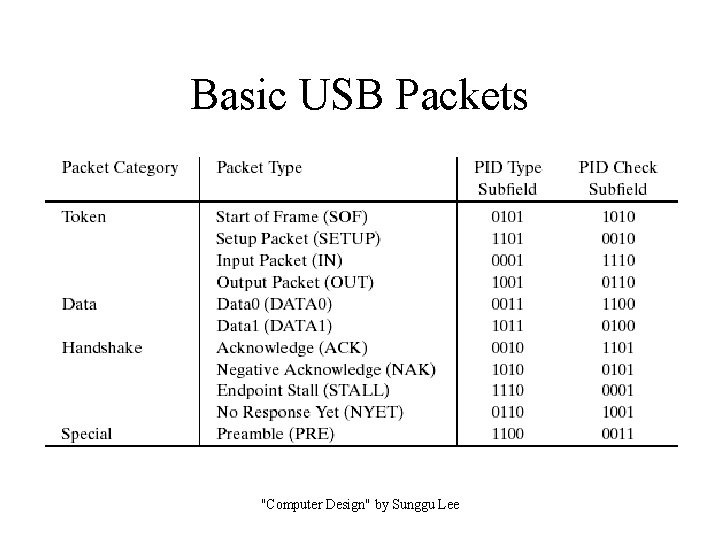

Basic USB Packets "Computer Design" by Sunggu Lee

NRZI Encoding • Method used to send a clock signal and a data signal on a single wire – Clock frequency agreed upon in advance • There will still be differences in phase between the clocks in the two communicating devices • There will also be “clock drift” • Above factors imply the need for a phase-locking mechanism • Refer to earlier example of SOF packet waveform – ‘ 0’ bit indicated by a transition – ‘ 1’ bit indicated by no transition – ‘ 0’ bits can be used to synchronize phases of transmitter clock and receiver clock "Computer Design" by Sunggu Lee

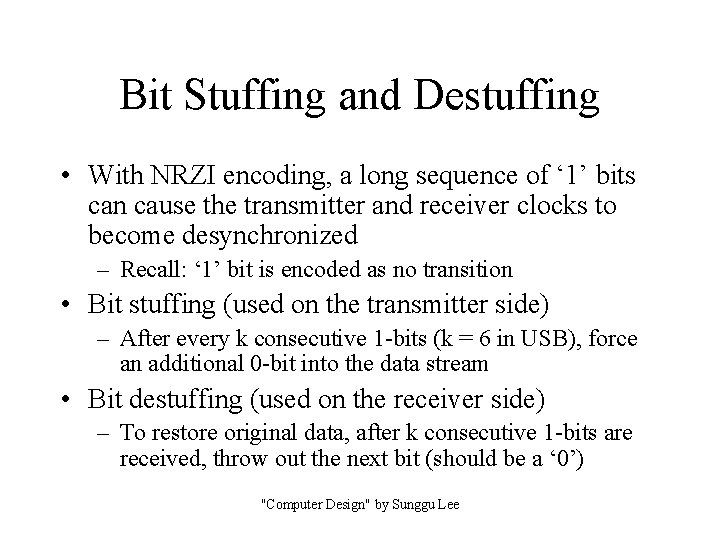

Bit Stuffing and Destuffing • With NRZI encoding, a long sequence of ‘ 1’ bits can cause the transmitter and receiver clocks to become desynchronized – Recall: ‘ 1’ bit is encoded as no transition • Bit stuffing (used on the transmitter side) – After every k consecutive 1 -bits (k = 6 in USB), force an additional 0 -bit into the data stream • Bit destuffing (used on the receiver side) – To restore original data, after k consecutive 1 -bits are received, throw out the next bit (should be a ‘ 0’) "Computer Design" by Sunggu Lee

Cyclic Redundancy Check • CRC is a common error-checking method • Errors can occur in binary data due to many factors – Background radiation from the environment – Weather effects – Electromagnetic noise, etc. • After every n bits of data, a k-bit CRC (checking m+k bits) can be sent – Overhead = k / (n + k) "Computer Design" by Sunggu Lee

CRC Checker Implementation • CRC method works on the concept of division of polynomials – An n-bit binary data stream is considered as an n-bit polynomial function – The k-bit CRC code is another polynomial formed from the residue of the division of the n-bit data polynomial by a generator polynomial • This operation can be accomplished by a linear feedback shift register (LFSR) circuit – e. g. , Figure 7. 4 (p. 242) • The residue will typically change if one or more bits in the data or the check code are changed "Computer Design" by Sunggu Lee

Differential Signalling • To eliminate noise in data transmission, it can be useful to send bit-serial data using a pair of signal wires – Logic 0 or 1 determined based on the difference between the voltages of the two wires (D+ and D- in USB) – If noise affects one wire, it will typically affect the other wire in a similar manner • It helps if the two wires are wound around other (inter-twined) like a pretzel – Particularly useful for very high-speed data transmission "Computer Design" by Sunggu Lee

Digital Phase-Locked Loop • A phase-locked loop (PLL) observes an NRZI data signal and outputs a clock signal – The clock signal should make a positive transition a “safe” time delay before a valid data bit – As the clock signal embedded in the NRZI signal drifts, the output clock signal should follow the “NRZI clock” • A digital phased-locked loop (DPLL or DLL) should implement the functionality of a PLL in a digital circuit – Use a sampling clock to sample the NRZI data signal – Verilog code implementation shown in pp. 252 -253 "Computer Design" by Sunggu Lee

Verilog Implementation • Verilog code shown in pp. 250 -281 – Consists of usb_pll, nrzi_bin, crc 5, crc 16, pidr, usb_interface, and usb_pa (top-level) modules • Test bench shown in pp. 282 -292 – Simulates the transmission of a set of USB packets (SOF, IN, DATA 0, ACK) • Simulation result shown in Fig. 7. 8 (p. 293) "Computer Design" by Sunggu Lee

- Slides: 14