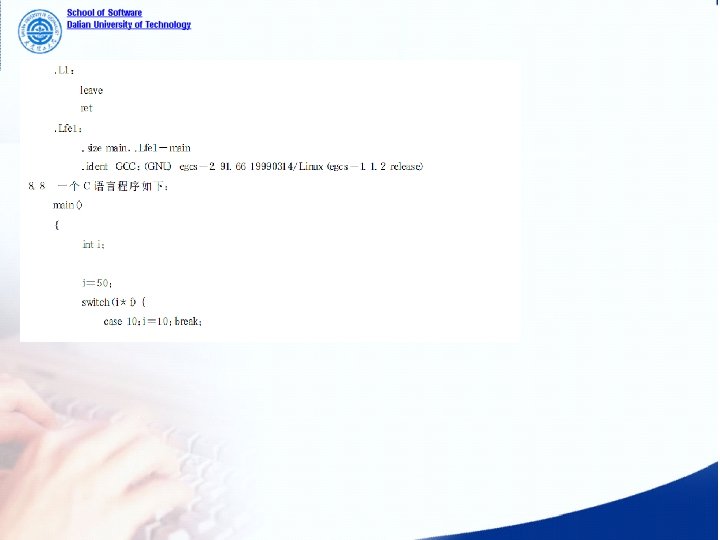

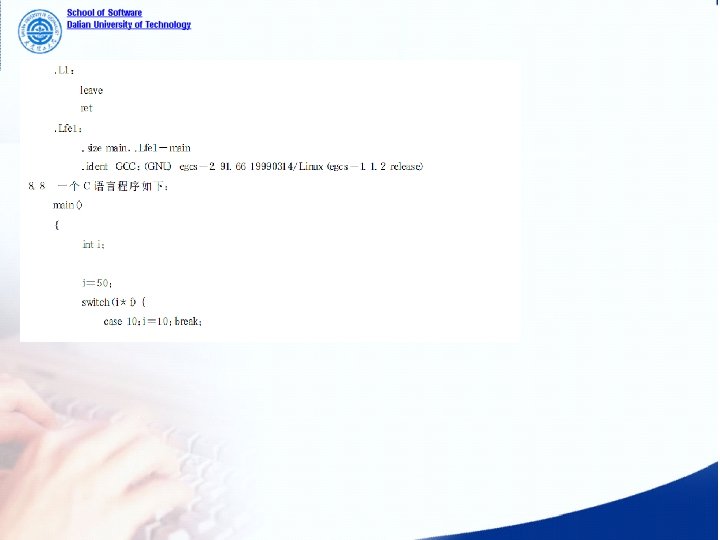

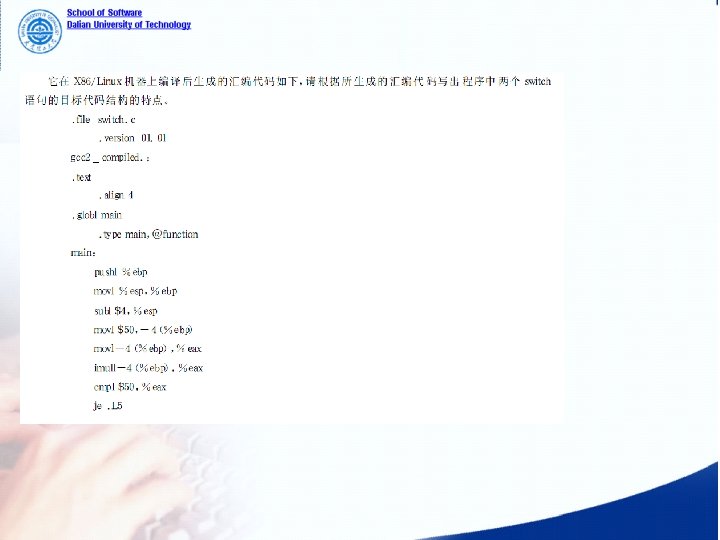

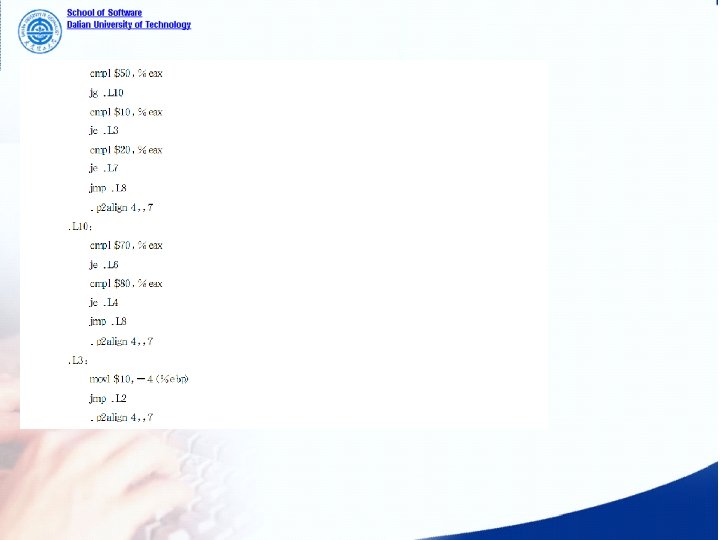

8 Code Generation Topics A simple code generator

- Slides: 36

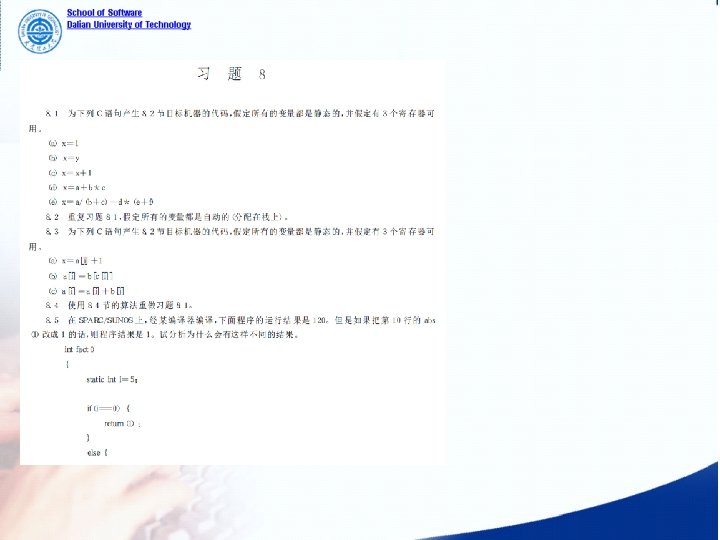

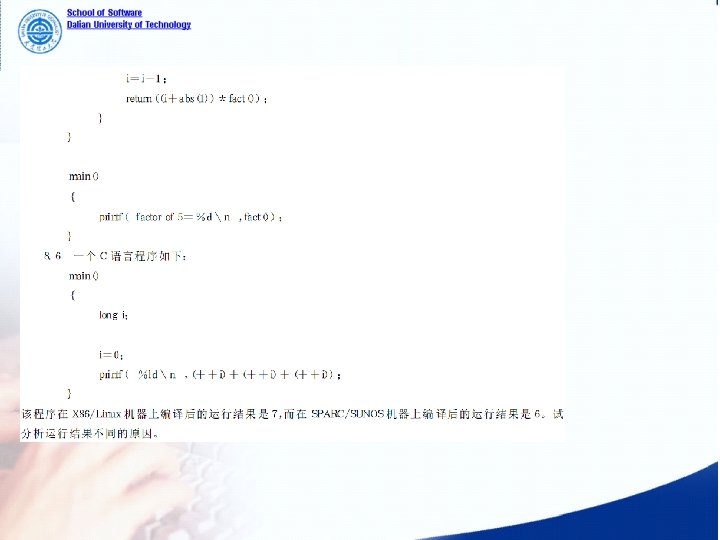

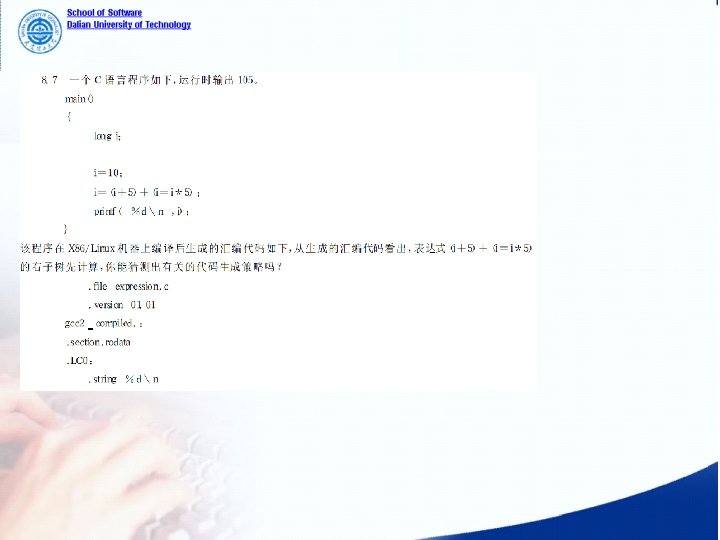

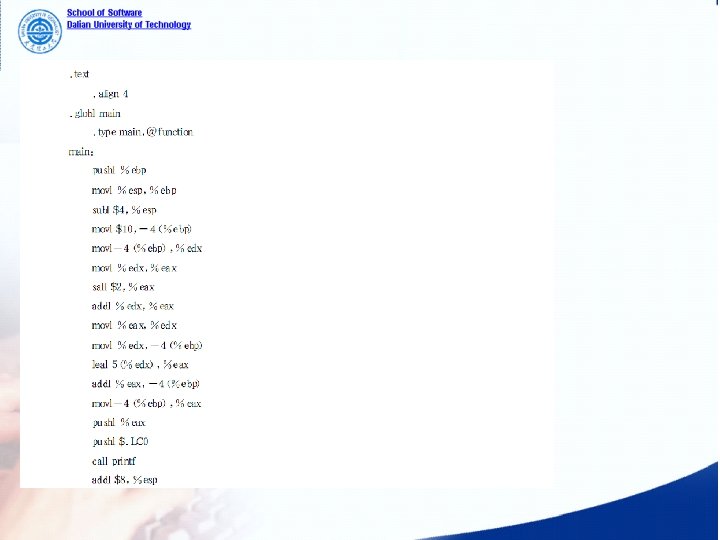

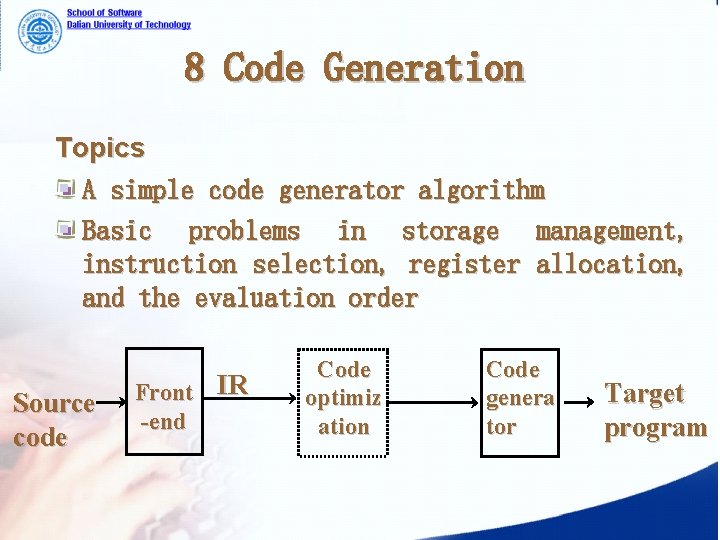

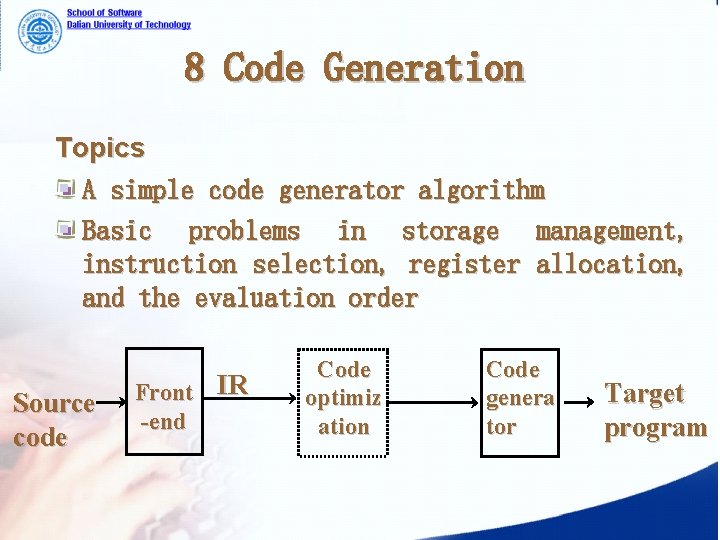

8 Code Generation Topics A simple code generator algorithm Basic problems in storage management, instruction selection, register allocation, and the evaluation order Source code Front IR -end Code optimiz ation Code genera tor Target program

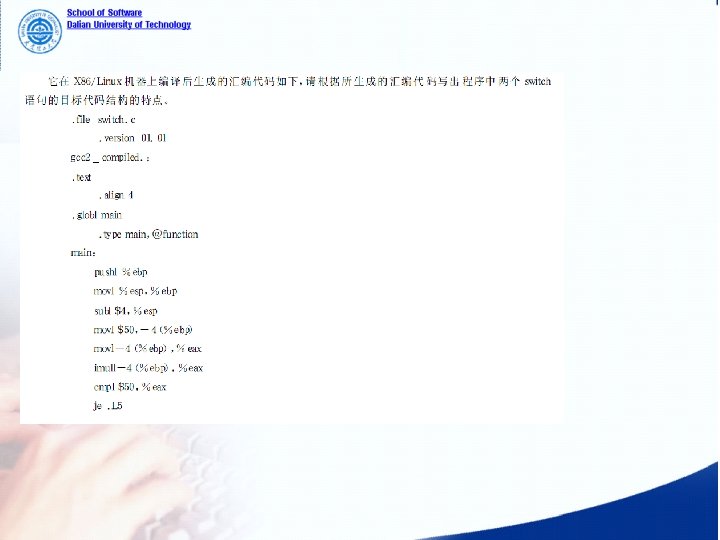

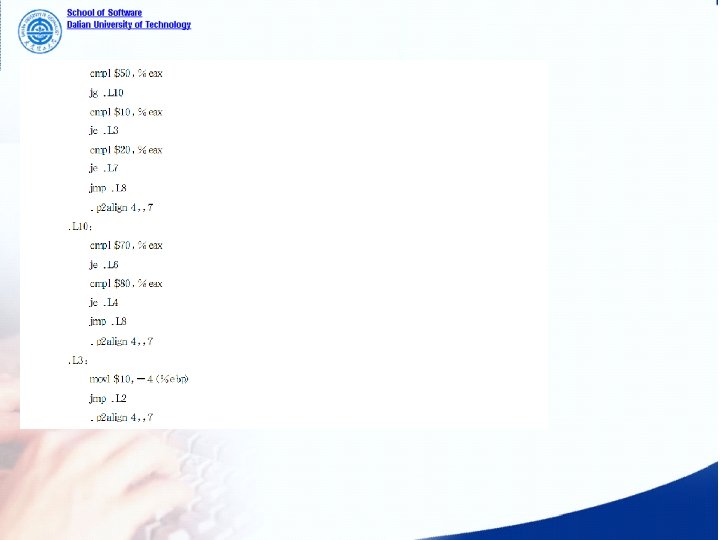

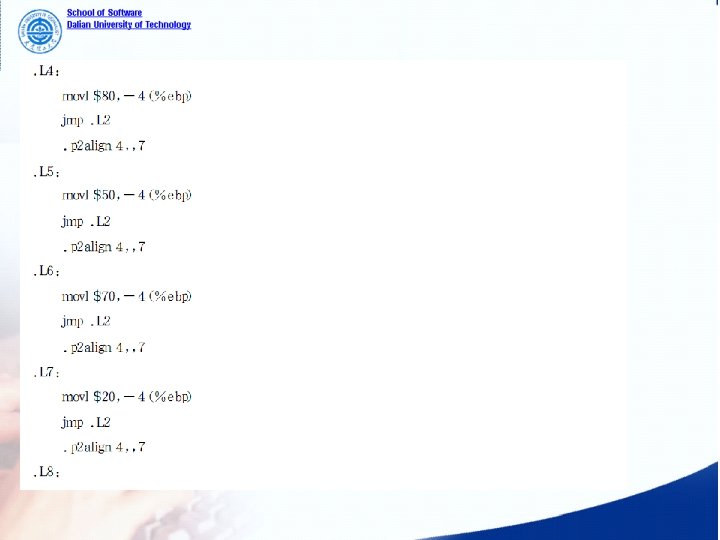

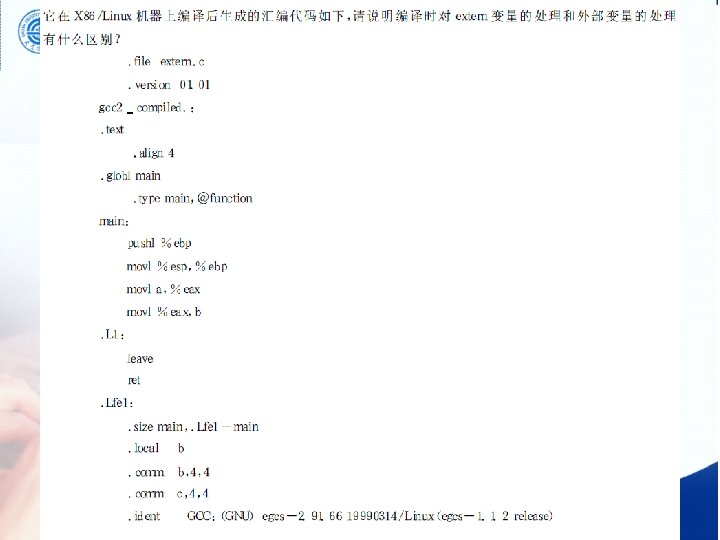

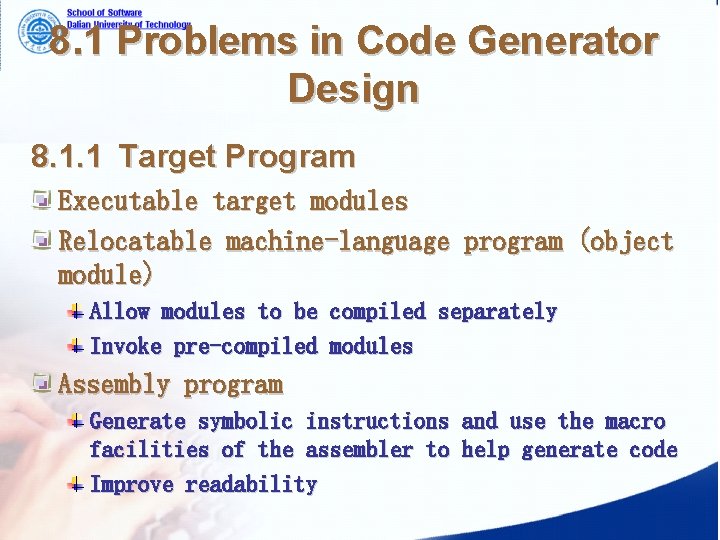

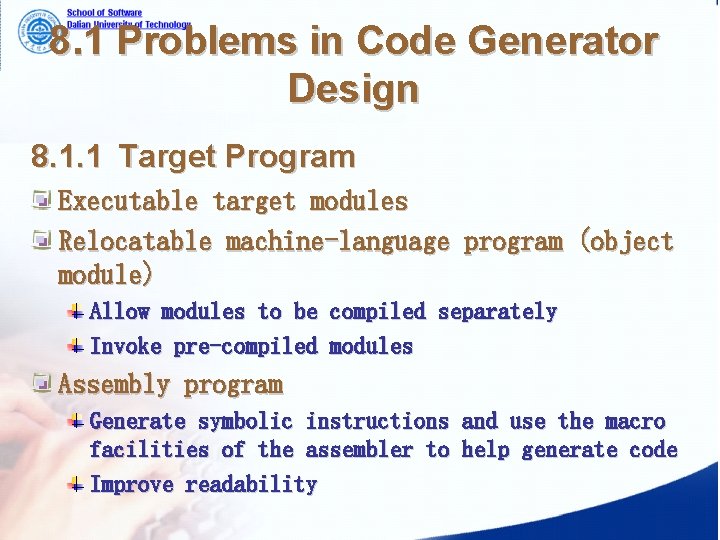

8. 1 Problems in Code Generator Design 8. 1. 1 Target Program Executable target modules Relocatable machine-language program (object module) Allow modules to be compiled separately Invoke pre-compiled modules Assembly program Generate symbolic instructions and use the macro facilities of the assembler to help generate code Improve readability

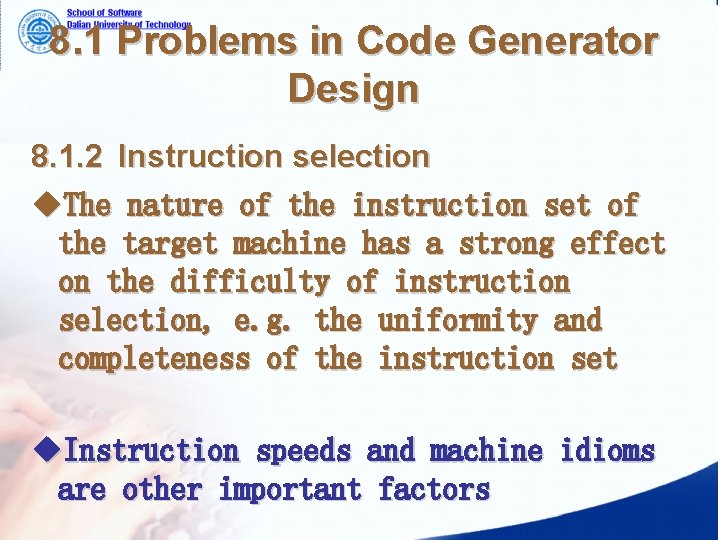

8. 1 Problems in Code Generator Design 8. 1. 2 Instruction selection u. The nature of the instruction set of the target machine has a strong effect on the difficulty of instruction selection, e. g. the uniformity and completeness of the instruction set u. Instruction speeds and machine idioms are other important factors

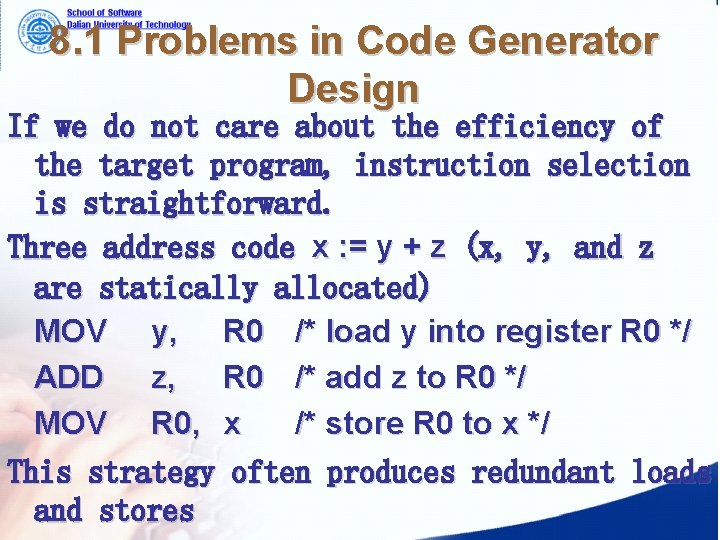

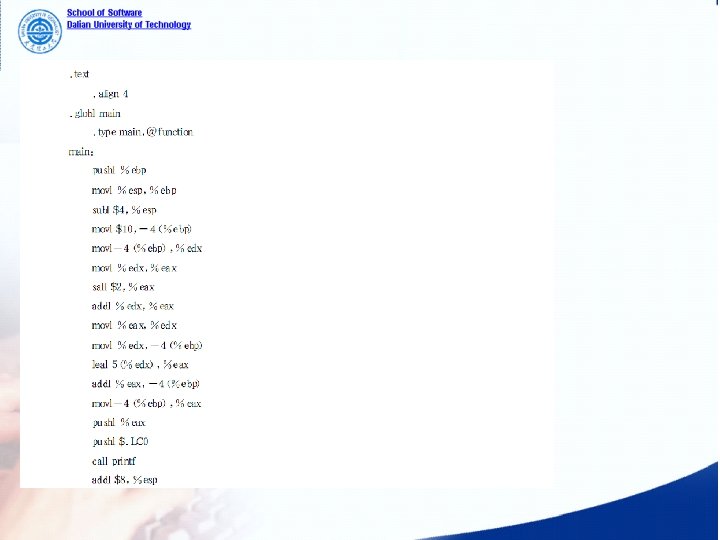

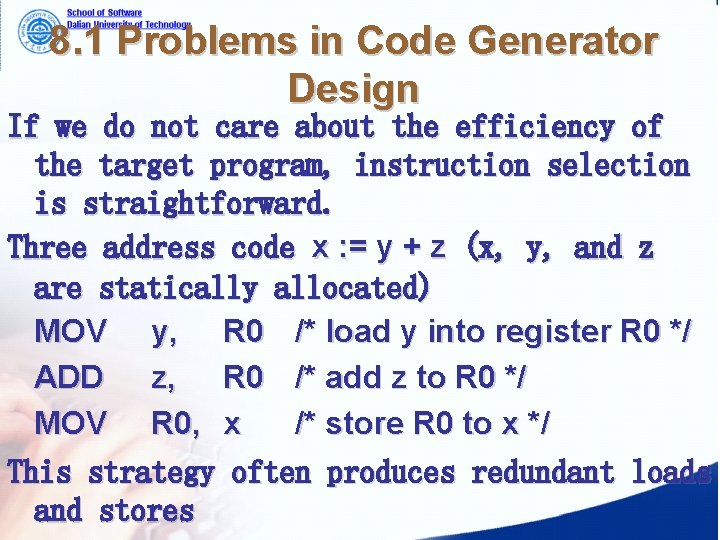

8. 1 Problems in Code Generator Design If we do not care about the efficiency of the target program, instruction selection is straightforward. Three address code x : = y + z (x, y, and z are statically allocated) MOV y, R 0 /* load y into register R 0 */ ADD z, R 0 /* add z to R 0 */ MOV R 0, x /* store R 0 to x */ This strategy often produces redundant loads and stores

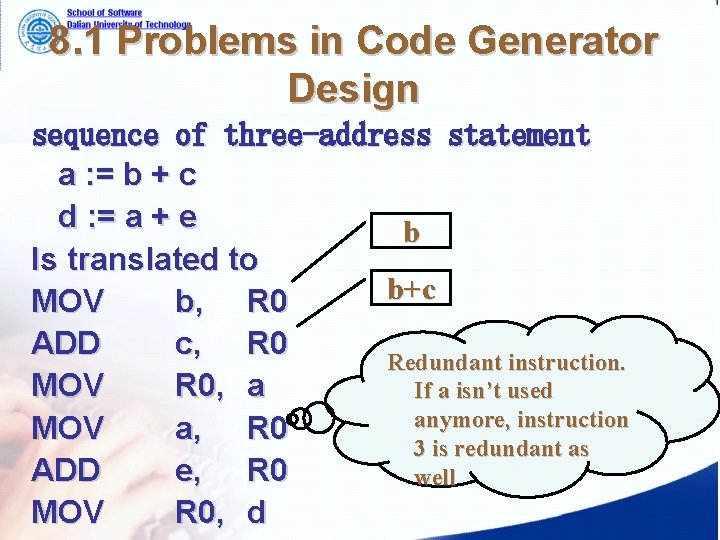

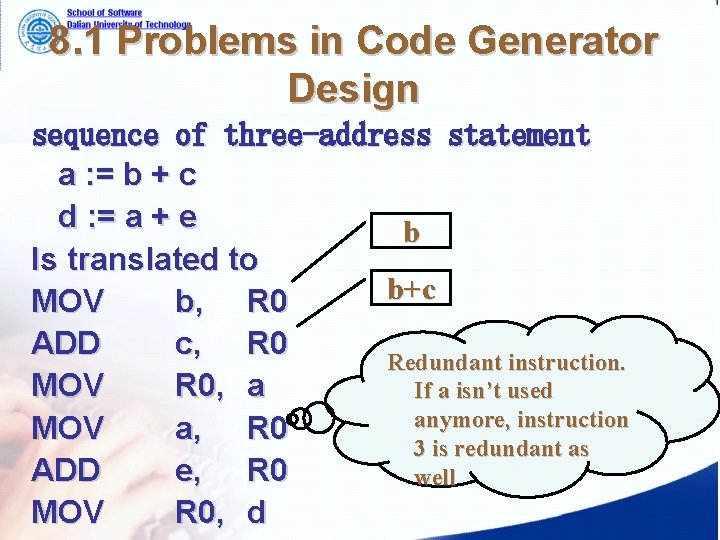

8. 1 Problems in Code Generator Design sequence of three-address statement a : = b + c d : = a + e b Is translated to b+c MOV b, R 0 ADD c, R 0 Redundant instruction. MOV R 0, a If a isn’t used anymore, instruction MOV a, R 0 3 is redundant as ADD e, R 0 well MOV R 0, d

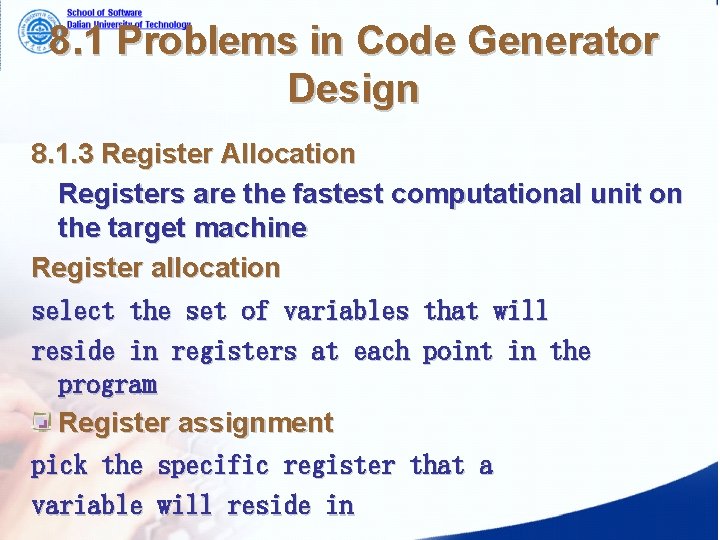

8. 1 Problems in Code Generator Design 8. 1. 3 Register Allocation Registers are the fastest computational unit on the target machine Register allocation select the set of variables that will reside in registers at each point in the program Register assignment pick the specific register that a variable will reside in

8. 1 Problems in Code Generator Design 8. 1. 4 Evaluation Order The order in which computations are performed can affect the efficiency of the target code. Some computation orders require fewer registers to hold intermediate results than others. However, picking a best order in the general case is a difficult NP-complete problem.

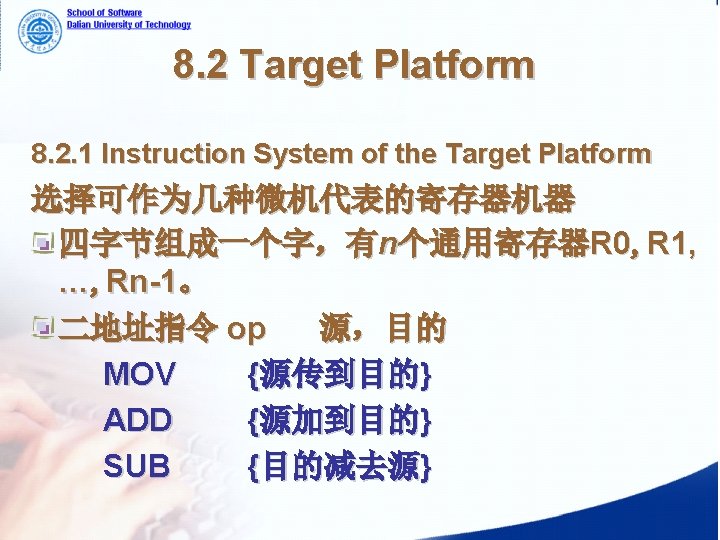

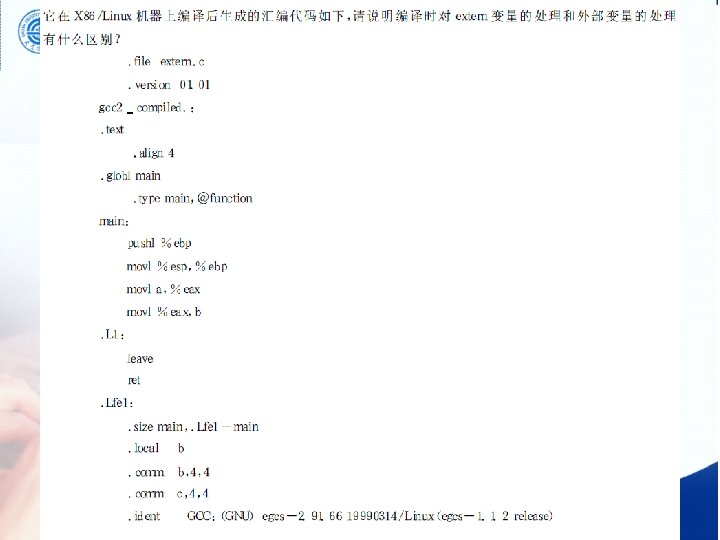

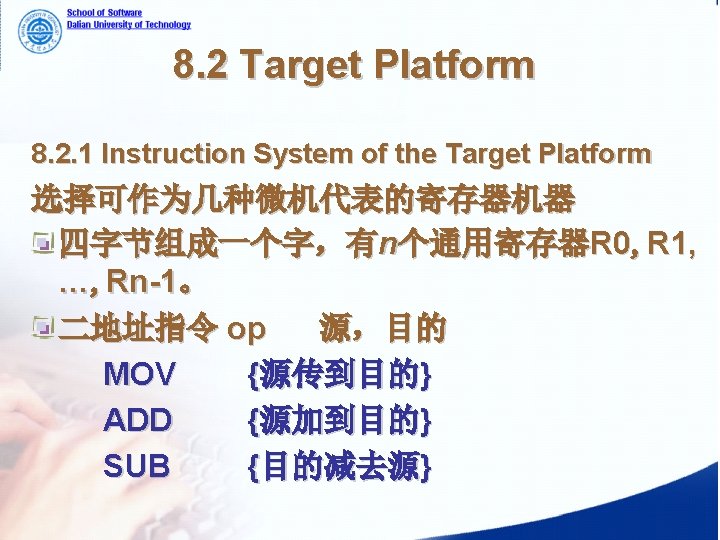

8. 2 Target Platform 指令实例 MOV R 0, 4(R 0), M M 把 contents(4 + contents(R 0)) 放到地址为M的地方去 MOV *4(R 0), M 把contents(contents (4 + contents(R 0) ) )放到地址为M 的地方去 MOV #1, R 0

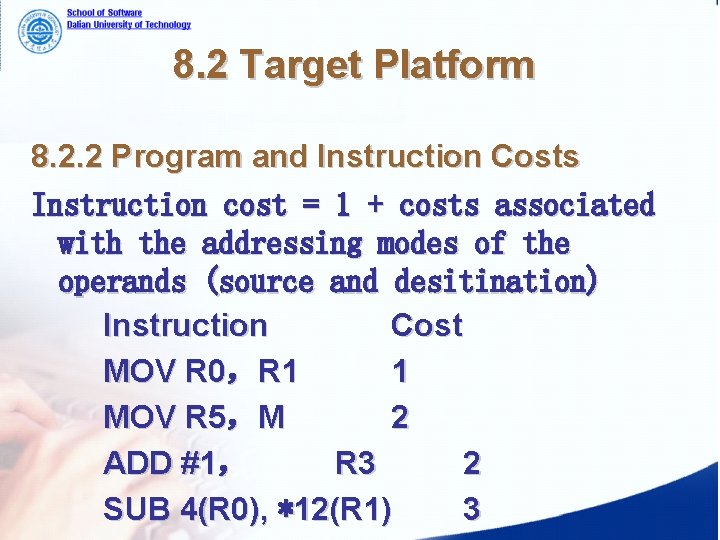

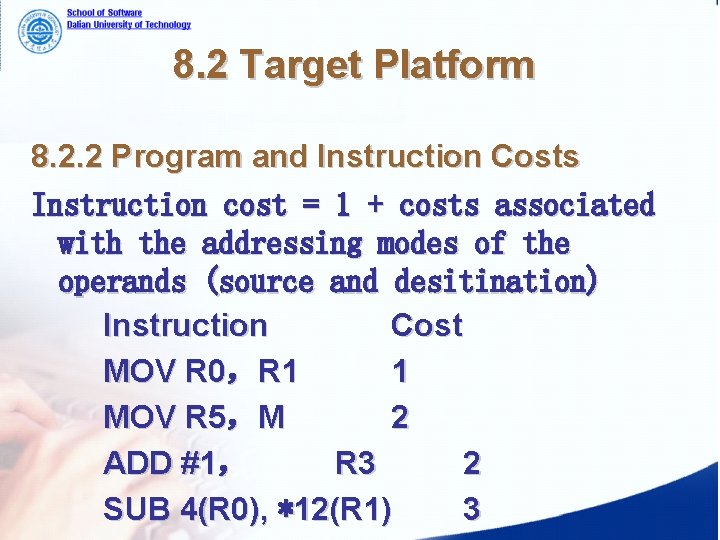

8. 2 Target Platform 8. 2. 2 Program and Instruction Costs Instruction cost = 1 + costs associated with the addressing modes of the operands (source and desitination) Instruction Cost MOV R 0,R 1 1 MOV R 5,M 2 ADD #1, R 3 2 SUB 4(R 0), *12(R 1) 3

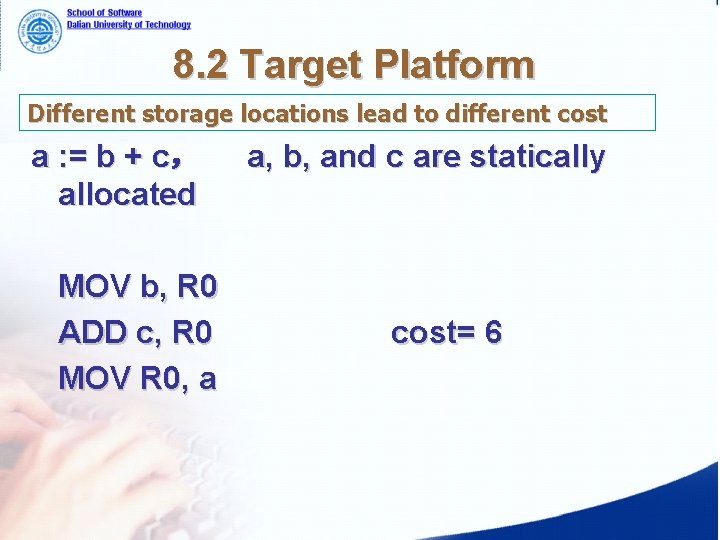

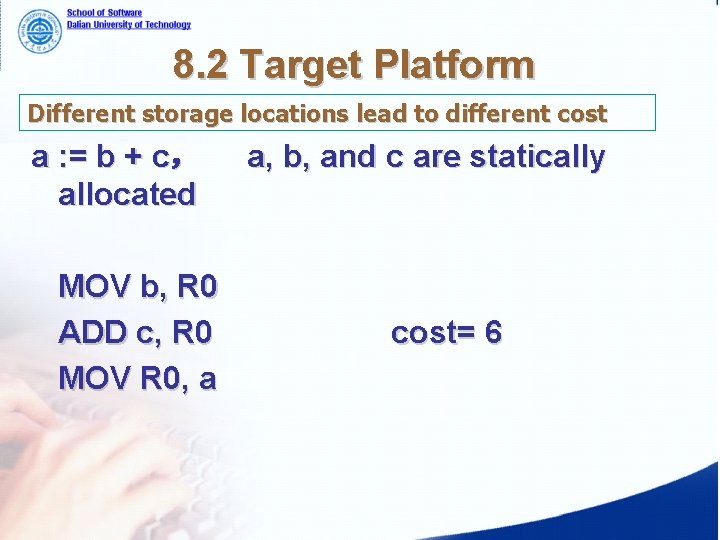

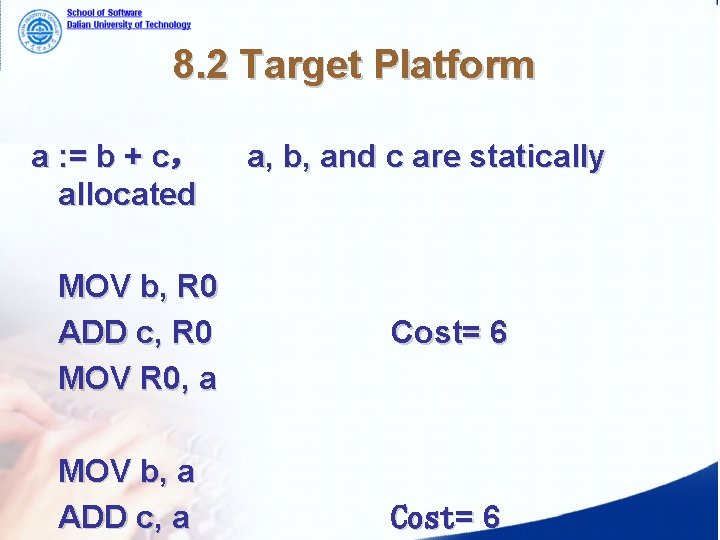

8. 2 Target Platform Different storage locations lead to different cost a : = b + c, allocated MOV b, R 0 ADD c, R 0 MOV R 0, a a, b, and c are statically cost= 6

8. 2 Target Platform a : = b + c, allocated MOV b, R 0 ADD c, R 0 MOV R 0, a MOV b, a ADD c, a a, b, and c are statically Cost= 6

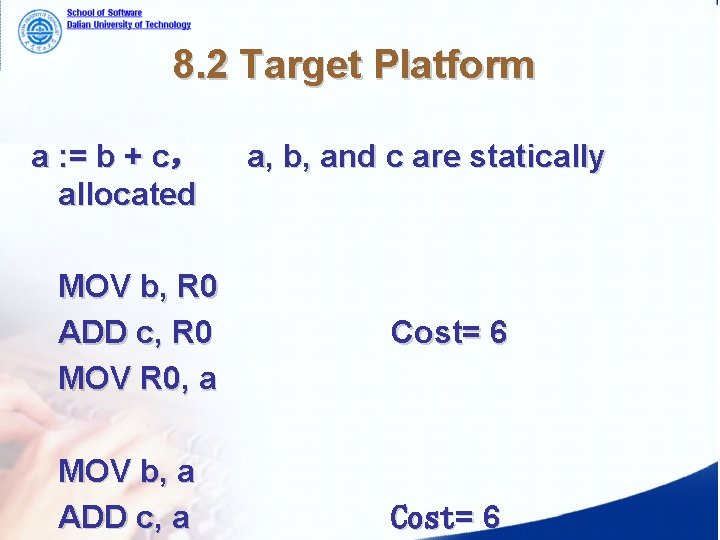

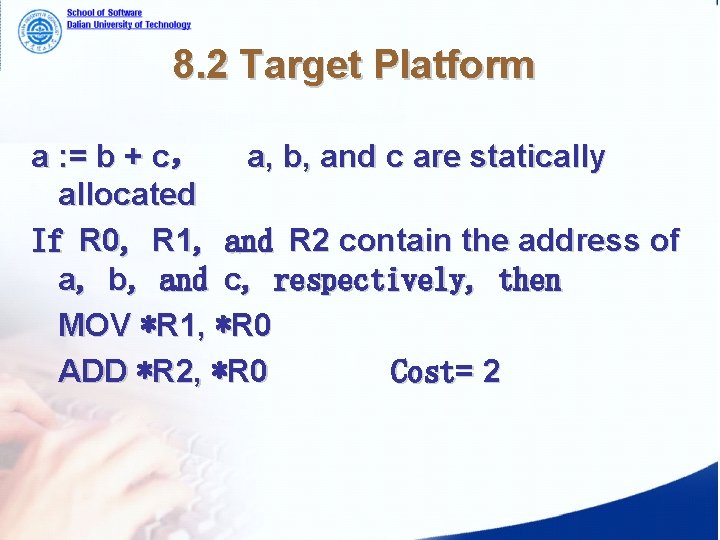

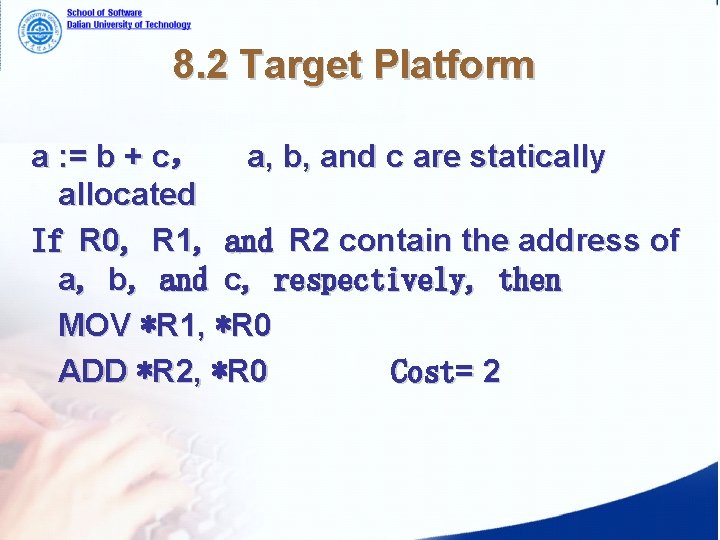

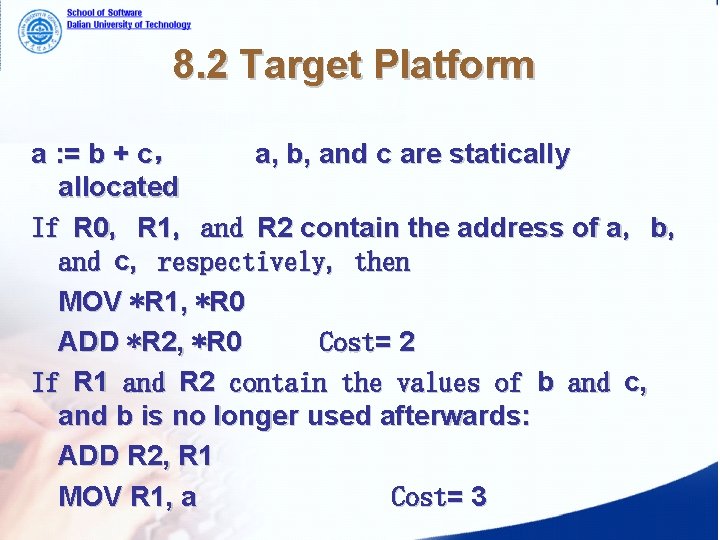

8. 2 Target Platform a : = b + c, a, b, and c are statically allocated If R 0, R 1, and R 2 contain the address of a, b, and c, respectively, then MOV *R 1, *R 0 ADD *R 2, *R 0 Cost= 2

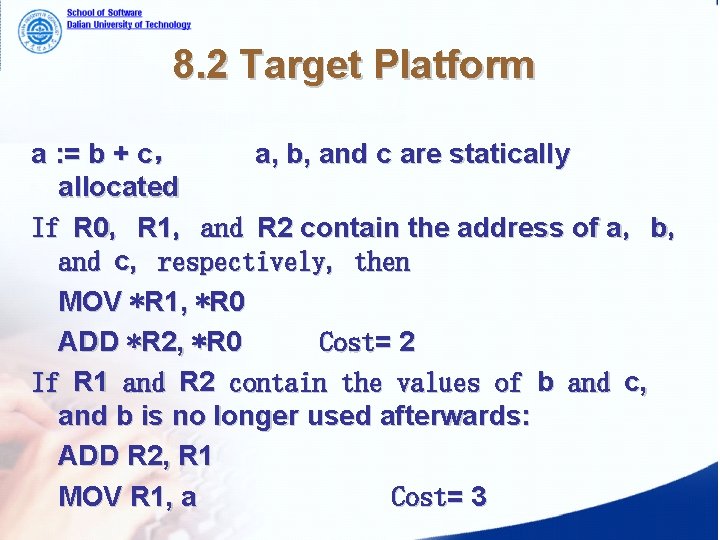

8. 2 Target Platform a : = b + c, a, b, and c are statically allocated If R 0, R 1, and R 2 contain the address of a, b, and c, respectively, then MOV *R 1, *R 0 ADD *R 2, *R 0 Cost= 2 If R 1 and R 2 contain the values of b and c, and b is no longer used afterwards: ADD R 2, R 1 MOV R 1, a Cost= 3

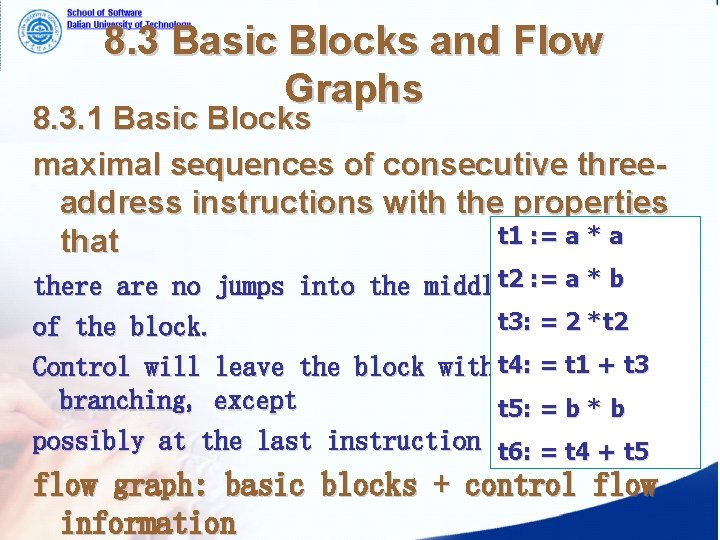

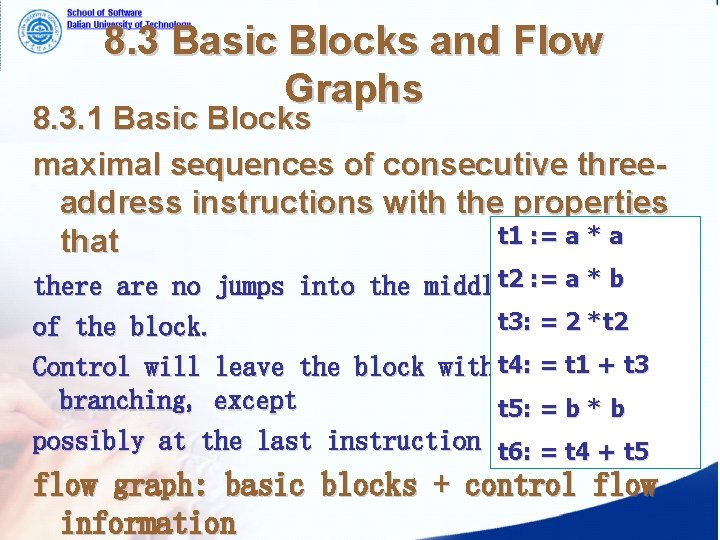

8. 3 Basic Blocks and Flow Graphs 8. 3. 1 Basic Blocks maximal sequences of consecutive threeaddress instructions with the properties t 1 : = a * a that there are no jumps into the middlet 2 : = a * b t 3: = 2 *t 2 of the block. t 4: =halting t 1 + t 3 or Control will leave the block without branching, except t 5: = b * b possibly at the last instruction in t 6: the = t 4 block + t 5. flow graph: basic blocks + control flow information

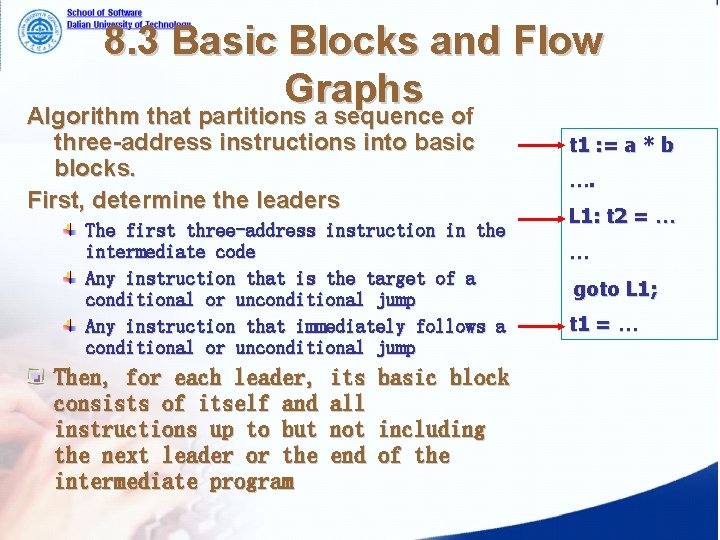

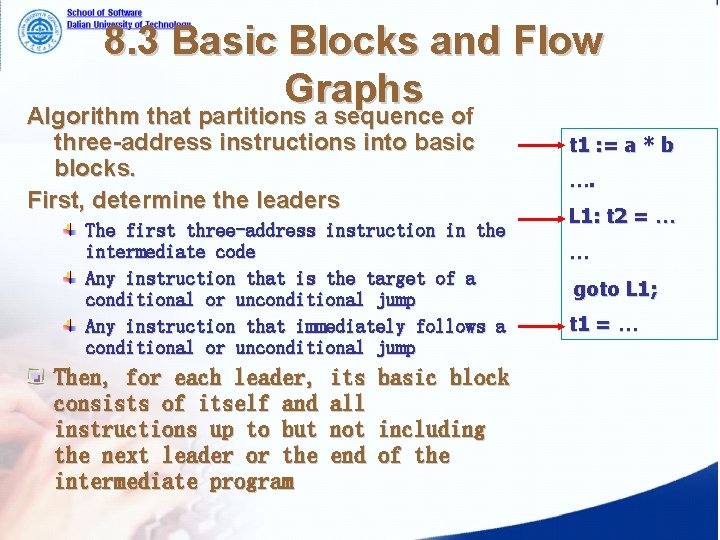

8. 3 Basic Blocks and Flow Graphs Algorithm that partitions a sequence of three-address instructions into basic blocks. First, determine the leaders The first three-address instruction in the intermediate code Any instruction that is the target of a conditional or unconditional jump Any instruction that immediately follows a conditional or unconditional jump Then, for each leader, consists of itself and instructions up to but the next leader or the intermediate program its basic block all not including end of the t 1 : = a * b …. L 1: t 2 = … … goto L 1; t 1 = …

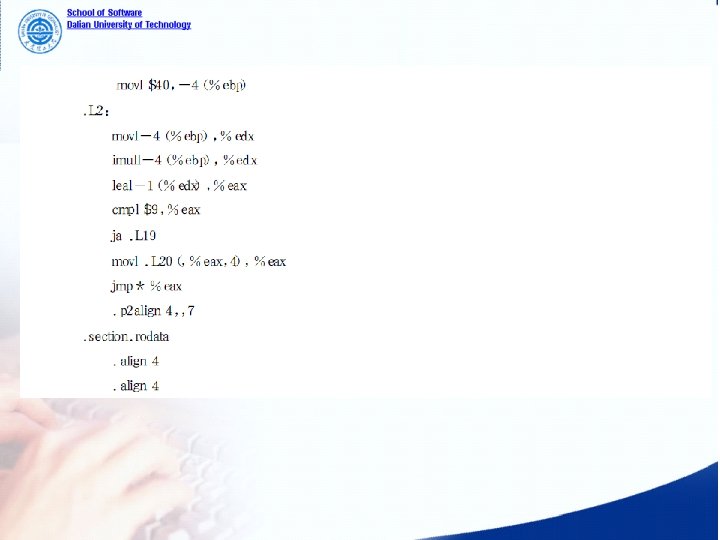

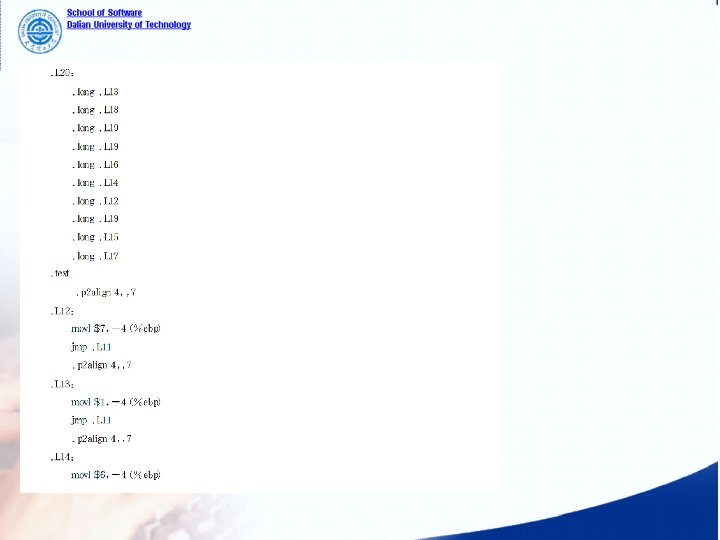

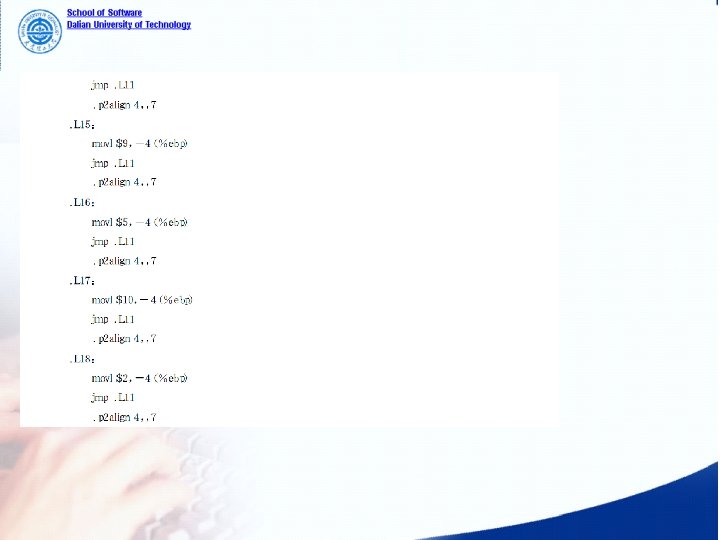

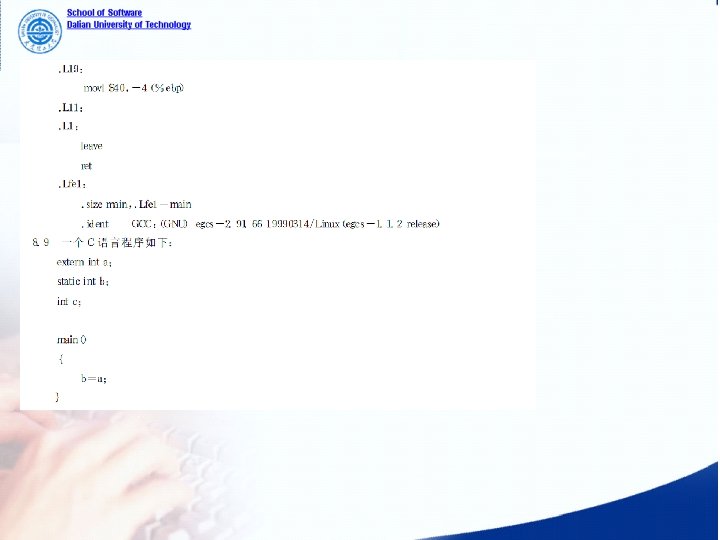

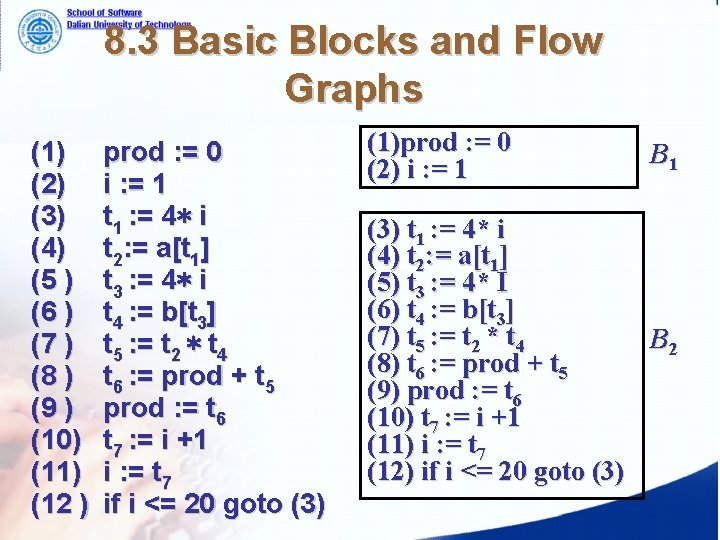

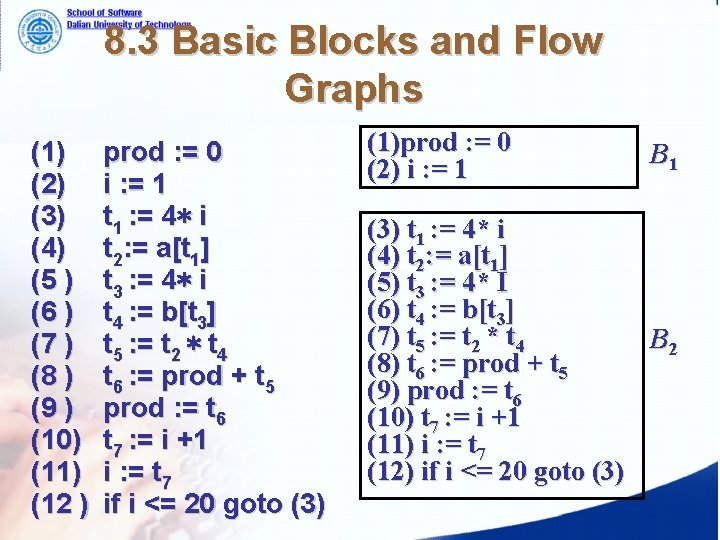

8. 3 Basic Blocks and Flow Graphs (1) (2) (3) (4) (5 ) (6 ) (7 ) (8 ) (9 ) (10) (11) (12 ) prod : = 0 i : = 1 t 1 : = 4* i t 2: = a[t 1] t 3 : = 4* i t 4 : = b[t 3] t 5 : = t 2 * t 4 t 6 : = prod + t 5 prod : = t 6 t 7 : = i +1 i : = t 7 if i <= 20 goto (3) (1)prod : = 0 (2) i : = 1 B 1 (3) t 1 : = 4* i (4) t 2: = a[t 1] (5) t 3 : = 4* I (6) t 4 : = b[t 3] (7) t 5 : = t 2 * t 4 B 2 (8) t 6 : = prod + t 5 (9) prod : = t 6 (10) t 7 : = i +1 (11) i : = t 7 (12) if i <= 20 goto (3)

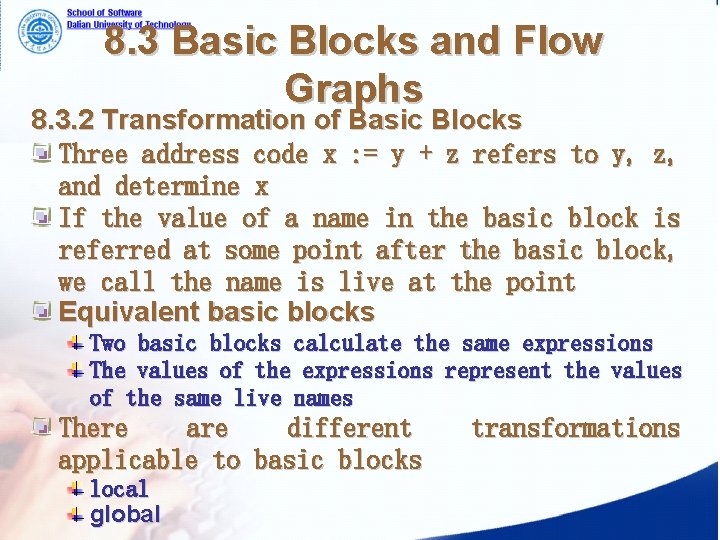

8. 3 Basic Blocks and Flow Graphs 8. 3. 2 Transformation of Basic Blocks Three address code x : = y + z refers to y, z, and determine x If the value of a name in the basic block is referred at some point after the basic block, we call the name is live at the point Equivalent basic blocks Two basic blocks calculate the same expressions The values of the expressions represent the values of the same live names There are different applicable to basic blocks local global transformations

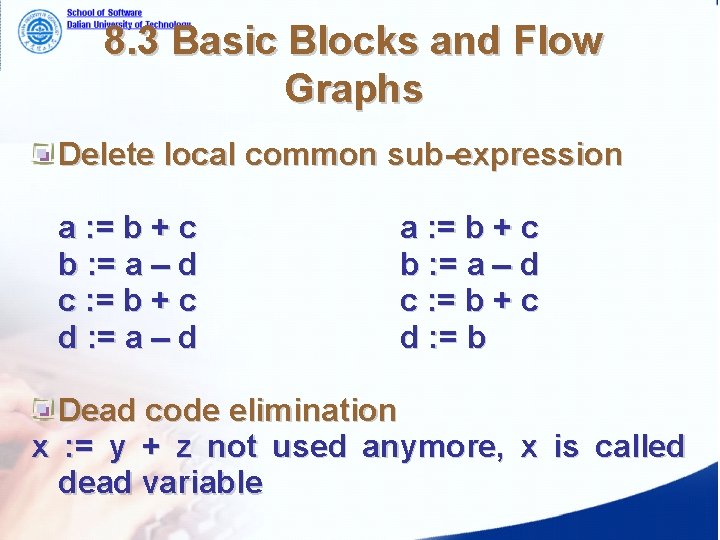

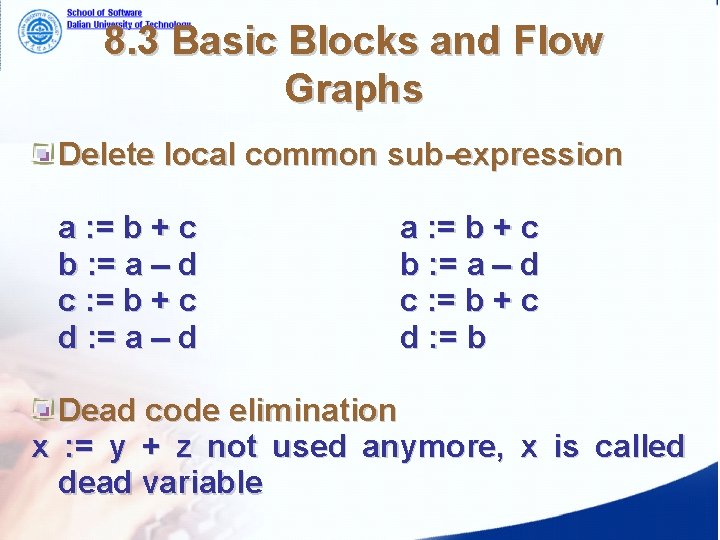

8. 3 Basic Blocks and Flow Graphs Delete local common sub-expression a : = b + c b : = a d c : = b + c d : = a d a : = b + c b : = a d c : = b + c d : = b Dead code elimination x : = y + z not used anymore, x is called dead variable

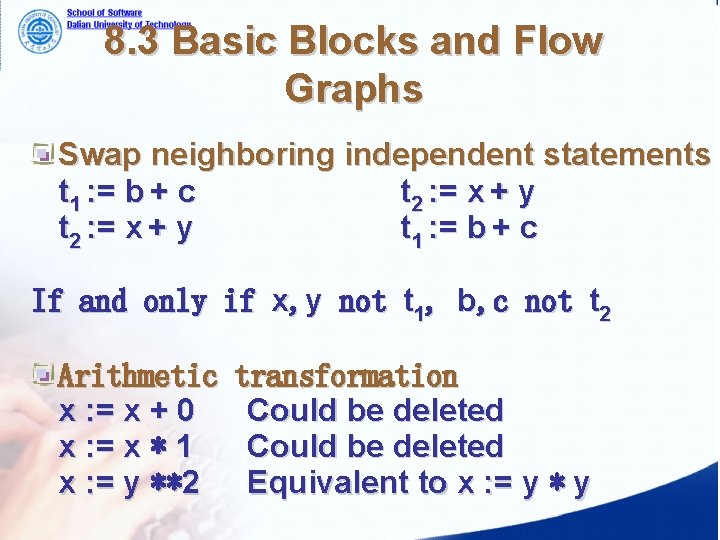

8. 3 Basic Blocks and Flow Graphs Swap neighboring independent statements t 1 : = b + c t 2 : = x + y t 1 : = b + c If and only if x, y not t 1, b, c not t 2 Arithmetic x : = x + 0 x : = x * 1 x : = y **2 transformation Could be deleted Equivalent to x : = y * y

Revision Instruction cost Determination of basic blocks Transformation of basic blocks