332 437 Lecture 15 System Controller Design n

- Slides: 18

332: 437 Lecture 15 System Controller Design n n System Controller Design Mnemonic Documented State Diagram Timing Diagram Flow Diagram Summary Material from An Engineering Approach to Digital Design, by William I. Fletcher, Englewood Cliffs, NJ: Prentice-Hall 11/4/2020 Bushnell: Digital Systems Design Lecture 15 1

Multi-Input System Controller Design General System Level Design n Special Sequential Machine – interprets system level control input sequences and generate system level and pulse output sequences n Controls a data path consisting of Registers, MUXes, etc. n Nerve Center – Has many control inputs & outputs 11/4/2020 Bushnell: Digital Systems Design Lecture 15 2

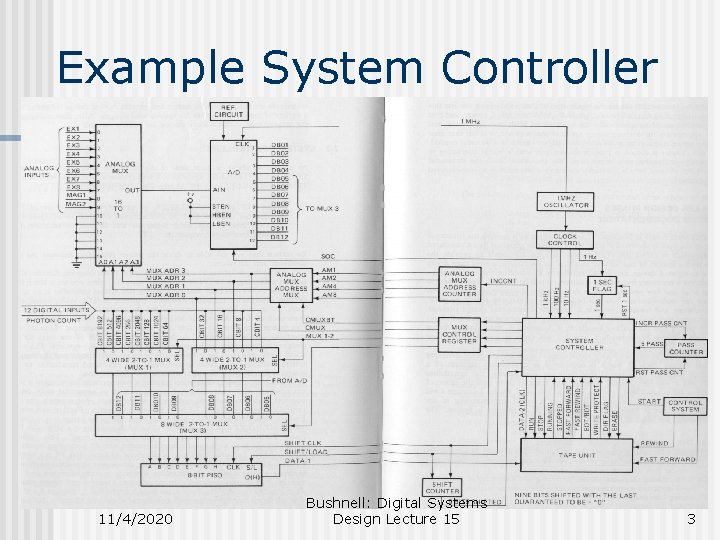

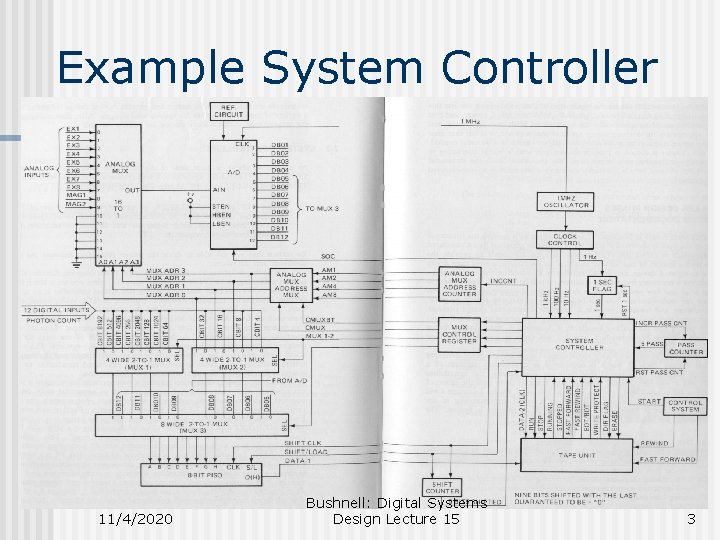

Example System Controller 11/4/2020 Bushnell: Digital Systems Design Lecture 15 3

Controller Implementation In many cases, the system controller will be implemented by a mprocessor and a ROM n Follow a structured design procedure n n It leads to much less work 11/4/2020 Bushnell: Digital Systems Design Lecture 15 4

Design Procedure 1. 2. 3. Know what you are going to do & how you are going to do it Design documentation should be a natural outcome of your work Document your work so that you and others can understand it 11/4/2020 Bushnell: Digital Systems Design Lecture 15 5

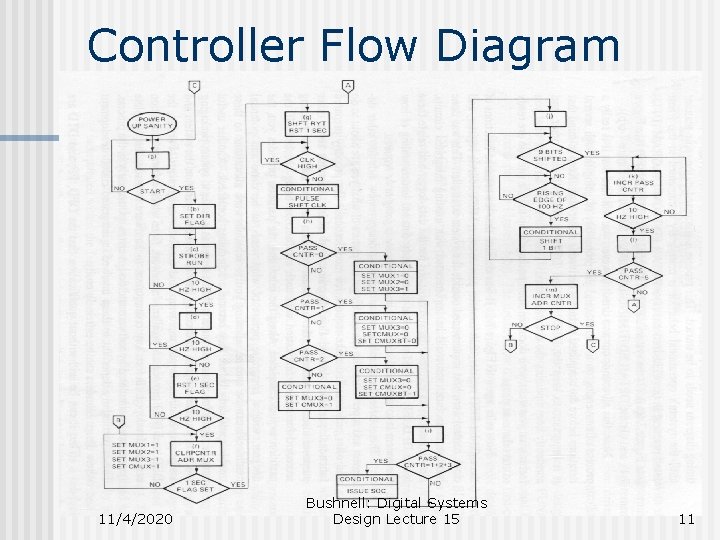

Design Process 1. 2. Define the purpose and role of the digital system in English writing. Define the logic operations & limitations of the systems that the system controller is to control (Data Path Synthesis). n n Aided by designing a first-cut flow diagram and logic clock diagram Leads to Functional Partition 11/4/2020 Bushnell: Digital Systems Design Lecture 15 6

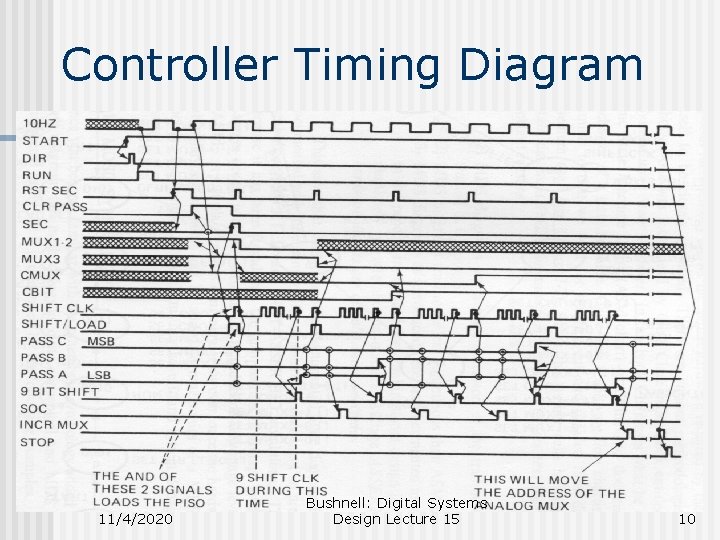

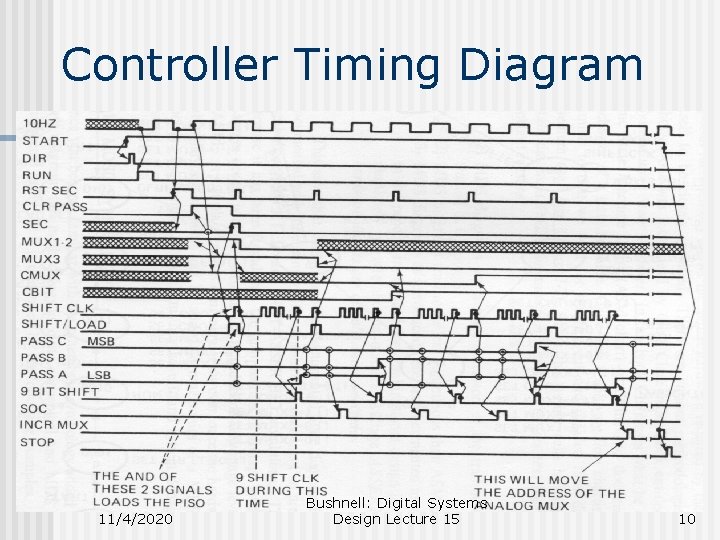

Design Process (continued) 3. Create timing diagram – Define timing & frequency of system level input & output control signals. n 4. Note any specific timing constraints. Detail sequential behavior of system controllers. Determine registers, temporary storage, special circuit & other subfunction requirements. n 11/4/2020 For Bushnell: Digital Systems Design Lecture 15 system controller & overall system 7

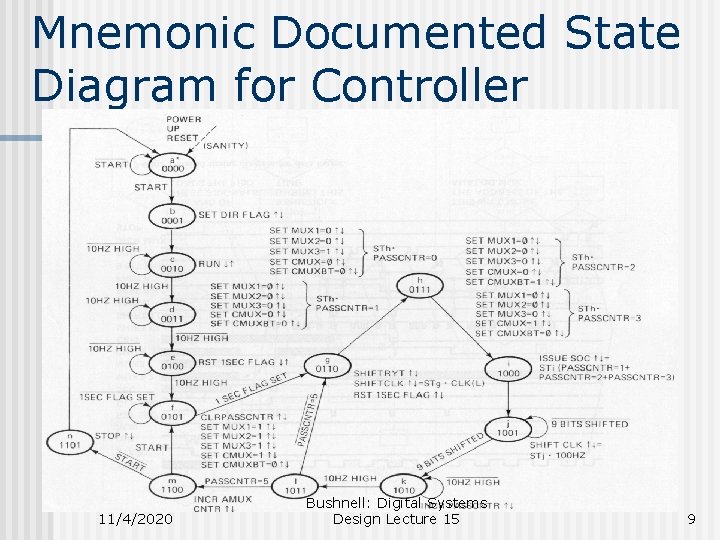

Design Process (continued) n 5. Develop detailed timing diagrams for system level & subfunction control. Develop Mnemonic Documented State Diagram (MDS) for system controller. 11/4/2020 Bushnell: Digital Systems Design Lecture 15 8

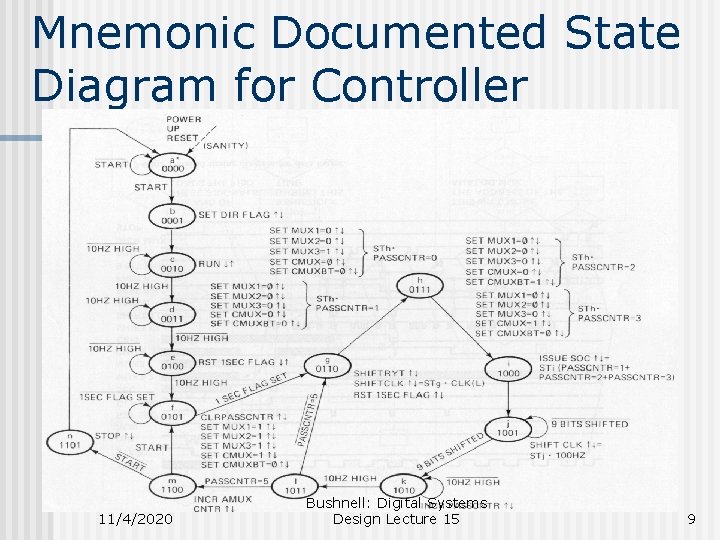

Mnemonic Documented State Diagram for Controller 11/4/2020 Bushnell: Digital Systems Design Lecture 15 9

Controller Timing Diagram 11/4/2020 Bushnell: Digital Systems Design Lecture 15 10

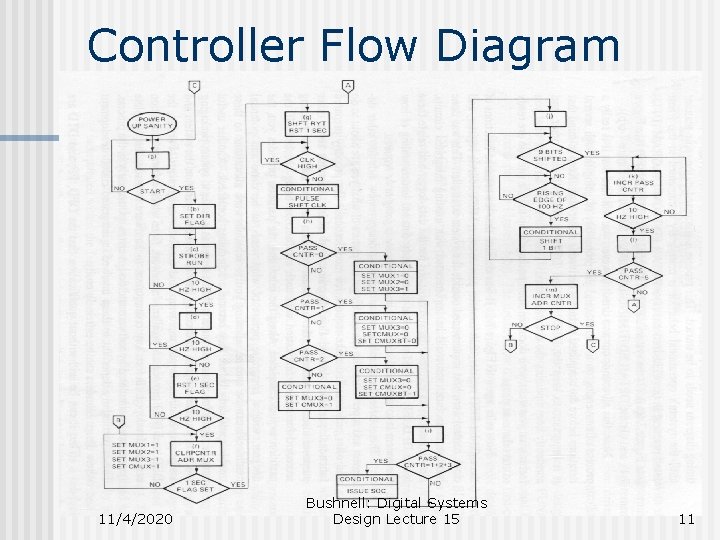

Controller Flow Diagram 11/4/2020 Bushnell: Digital Systems Design Lecture 15 11

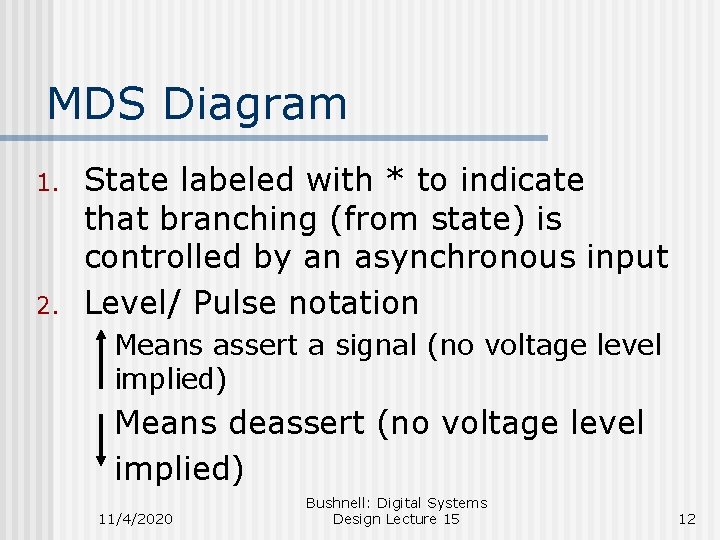

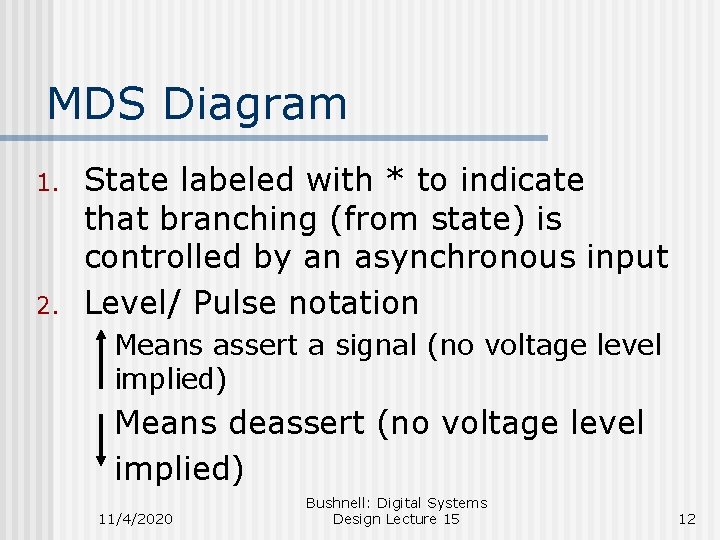

MDS Diagram 1. 2. State labeled with * to indicate that branching (from state) is controlled by an asynchronous input Level/ Pulse notation Means assert a signal (no voltage level implied) Means deassert (no voltage level implied) 11/4/2020 Bushnell: Digital Systems Design Lecture 15 12

MDS Diagram (Continued) 3. Means output a pulse, synchronous either with a clock or with the presence in a state or both Design System Controller Flow Diagram – Like a Software Flow Chart but for hardware 11/4/2020 Bushnell: Digital Systems Design Lecture 15 13

Timing Frequency Considerations 1. 2. 3. 4. 5. At what point in time can a controlling input be expected? Is it synchronous or asynchronous? How long will input be asserted? How much time elapses after the input until a control output is expected? When must the control signal be issued in the time frame? How long with the output signal remain asserted? 11/4/2020 Bushnell: Digital Systems Design Lecture 15 14

Hardest Part n 1. 2. 3. Create Functional Partition Detailed Flow Diagram Detailed Timing diagram 11/4/2020 Bushnell: Digital Systems Design Lecture 15 15

Five Concepts 1. Action block in Flow Diagram corresponds to a state in MDSD n 2. State Diagram begins & ends with an action clock Branching condition for state in MDS Diagram found by tracing decision paths in Flow Diagram 11/4/2020 Bushnell: Digital Systems Design Lecture 15 16

Five Concepts (continued) 3. 4. 5. Avoid making branching decision in one state based on >1 asynchronous inputs Generalized outputs symbolized by action notation in action blocks Unconditional & conditional outputs specified with duration time dependent on an input Bushnell: Digital Systems variable 11/4/2020 Design Lecture 15 17

Summary n n System Controller Design Mnemonic Documented State Diagram Timing Diagram Flow Diagram 11/4/2020 Bushnell: Digital Systems Design Lecture 15 18