Versatile Link for HLLHC Experiments STATUS AND PLANS

- Slides: 13

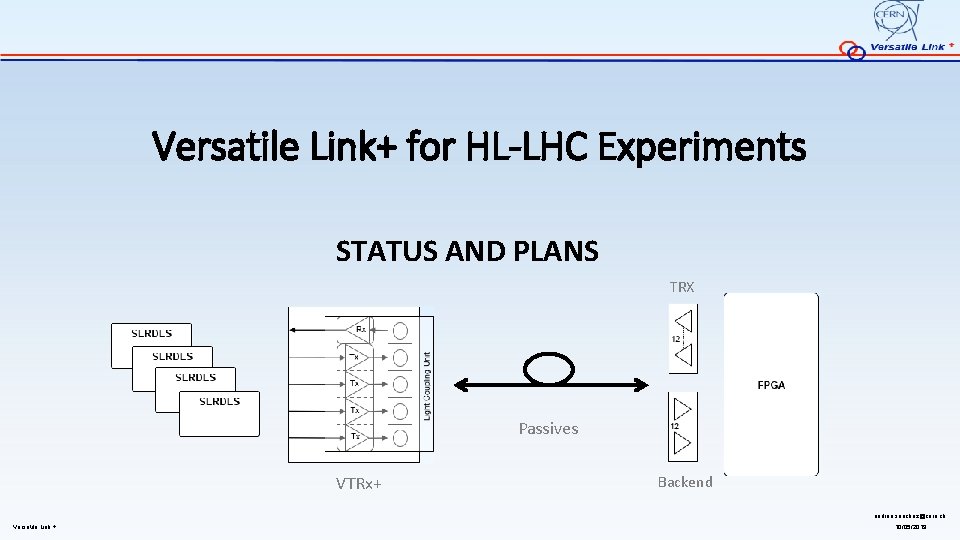

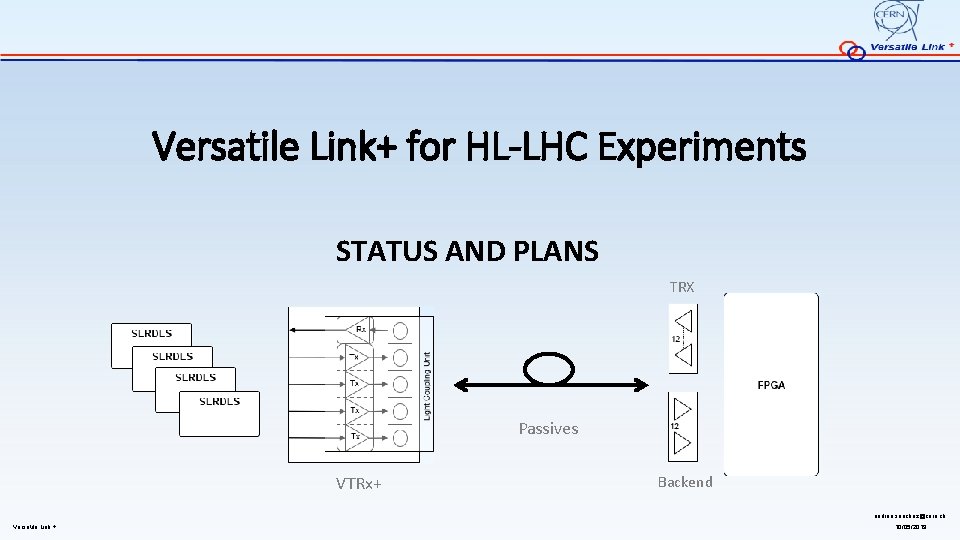

Versatile Link+ for HL-LHC Experiments STATUS AND PLANS TRX Passives VTRx+ Backend andrea. sanchez@cern. ch Versatile Link + 10/05/2019

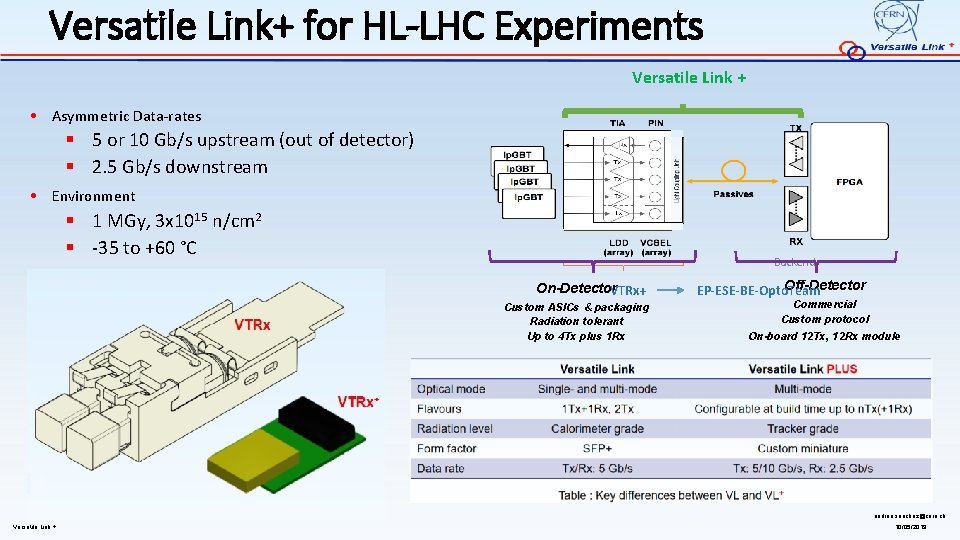

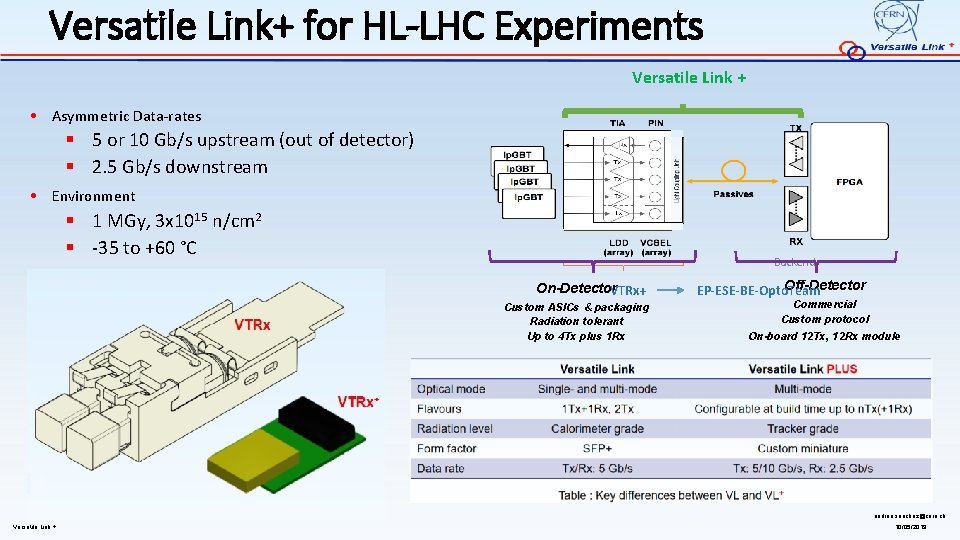

Versatile Link+ for HL-LHC Experiments Versatile Link + • Asymmetric Data-rates § 5 or 10 Gb/s upstream (out of detector) § 2. 5 Gb/s downstream • Environment § 1 MGy, 3 x 1015 n/cm 2 § -35 to +60 °C Backend On-Detector VTRx+ Custom ASICs & packaging Radiation tolerant Up to 4 Tx plus 1 Rx Off-Detector EP-ESE-BE-Opto. Team Commercial Custom protocol On-board 12 Tx, 12 Rx module andrea. sanchez@cern. ch Versatile Link + 10/05/2019

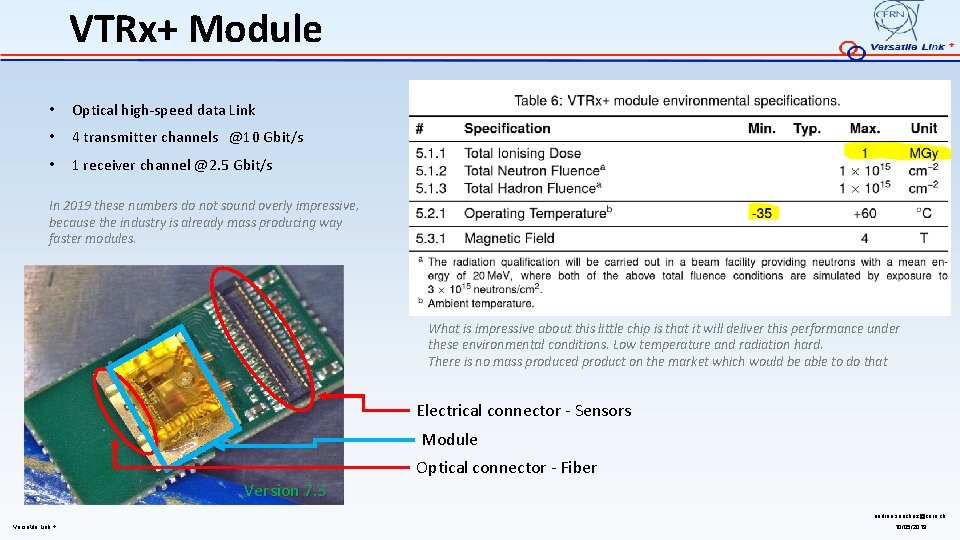

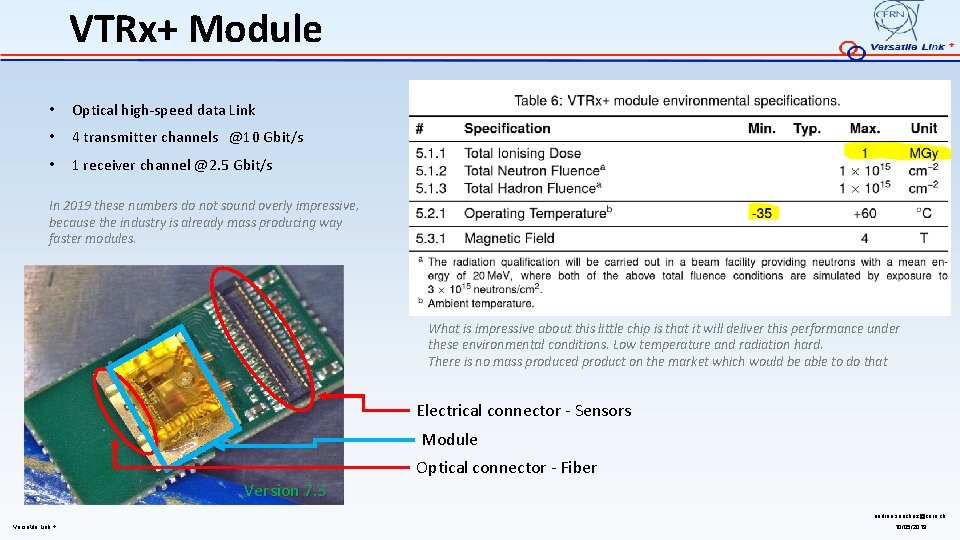

VTRx+ Module • Optical high-speed data Link • 4 transmitter channels @10 Gbit/s • 1 receiver channel @2. 5 Gbit/s In 2019 these numbers do not sound overly impressive, because the industry is already mass producing way faster modules. What is impressive about this little chip is that it will deliver this performance under these environmental conditions. Low temperature and radiation hard. There is no mass produced product on the market which would be able to do that Electrical connector - Sensors Module Optical connector - Fiber Version 7. 3 andrea. sanchez@cern. ch Versatile Link + 10/05/2019

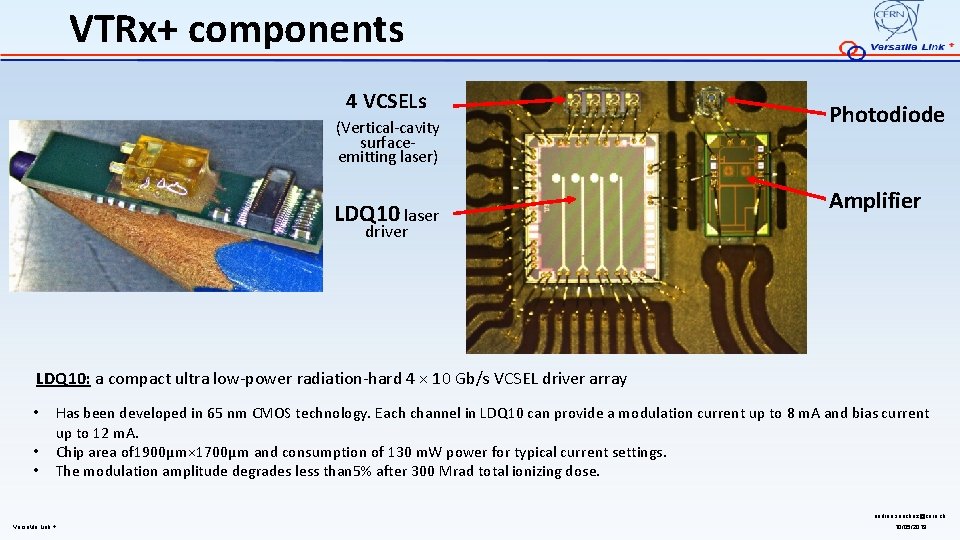

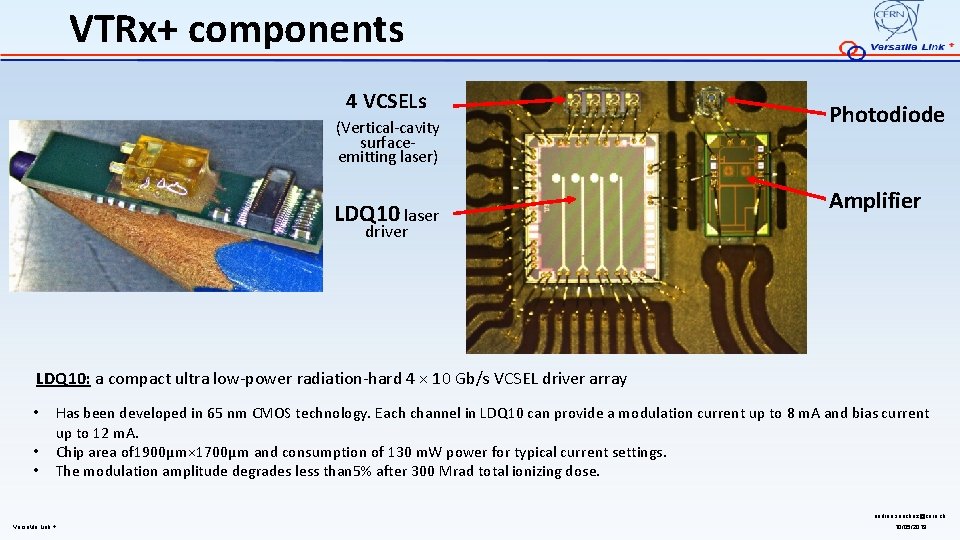

VTRx+ components 4 VCSELs (Vertical-cavity surfaceemitting laser) LDQ 10 laser Photodiode Amplifier driver LDQ 10: a compact ultra low-power radiation-hard 4 × 10 Gb/s VCSEL driver array • • • Has been developed in 65 nm CMOS technology. Each channel in LDQ 10 can provide a modulation current up to 8 m. A and bias current up to 12 m. A. Chip area of 1900μm× 1700μm and consumption of 130 m. W power for typical current settings. The modulation amplitude degrades less than 5% after 300 Mrad total ionizing dose. andrea. sanchez@cern. ch Versatile Link + 10/05/2019

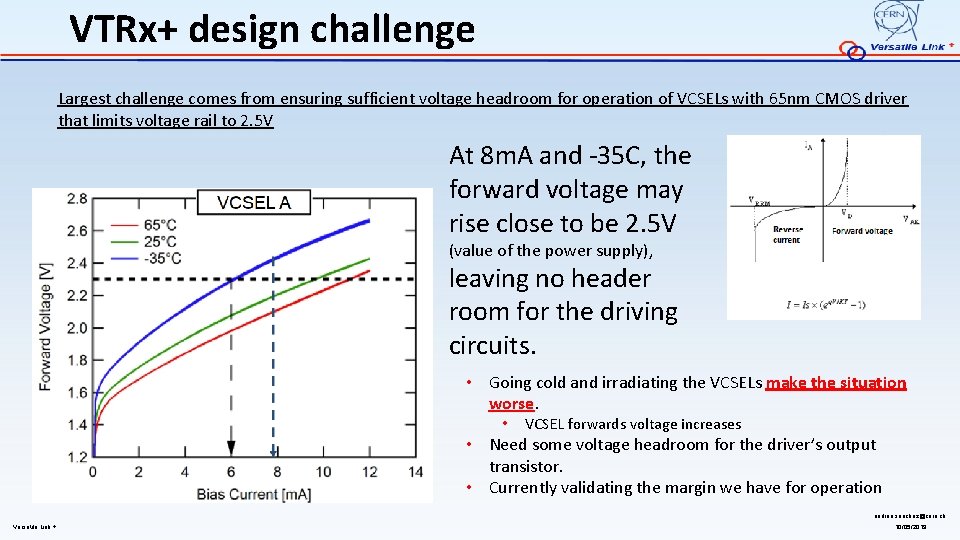

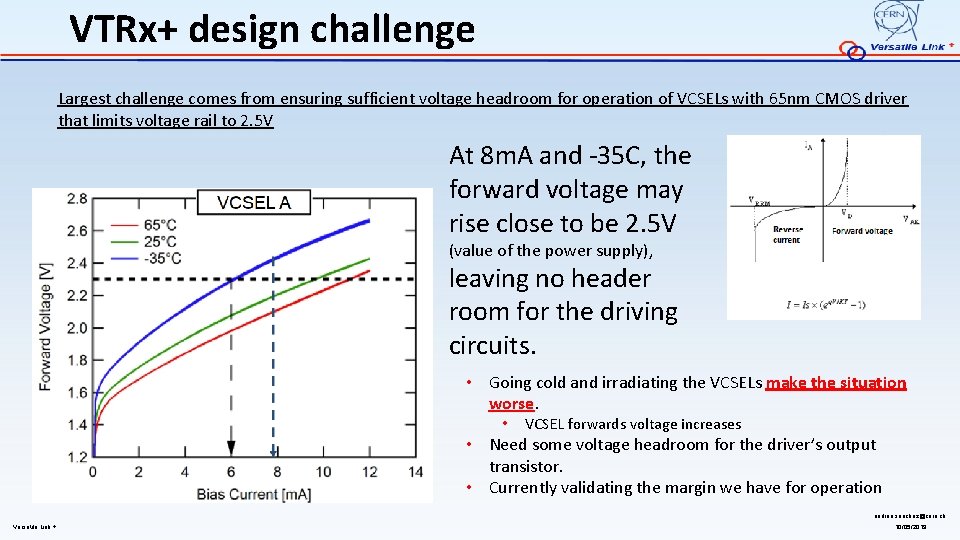

VTRx+ design challenge Largest challenge comes from ensuring sufficient voltage headroom for operation of VCSELs with 65 nm CMOS driver that limits voltage rail to 2. 5 V At 8 m. A and -35 C, the forward voltage may rise close to be 2. 5 V (value of the power supply), leaving no header room for the driving circuits. • Going cold and irradiating the VCSELs make the situation worse. • VCSEL forwards voltage increases • Need some voltage headroom for the driver’s output transistor. • Currently validating the margin we have for operation andrea. sanchez@cern. ch Versatile Link + 10/05/2019

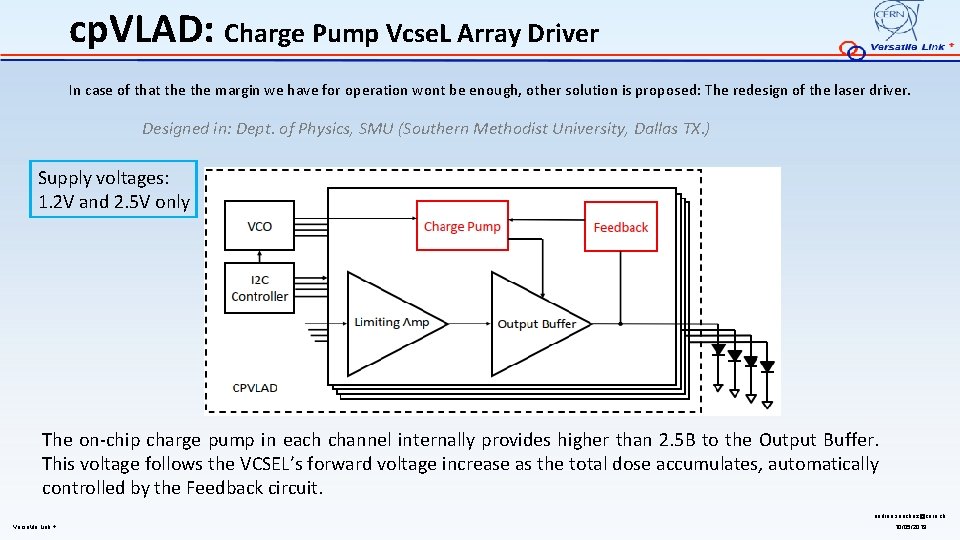

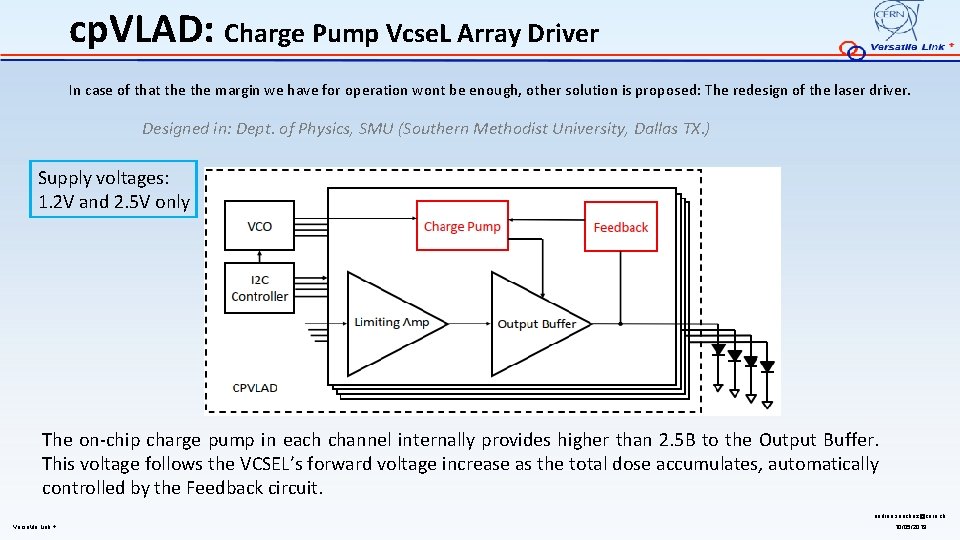

cp. VLAD: Charge Pump Vcse. L Array Driver In case of that the margin we have for operation wont be enough, other solution is proposed: The redesign of the laser driver. Designed in: Dept. of Physics, SMU (Southern Methodist University, Dallas TX. ) Supply voltages: 1. 2 V and 2. 5 V only The on-chip charge pump in each channel internally provides higher than 2. 5 B to the Output Buffer. This voltage follows the VCSEL’s forward voltage increase as the total dose accumulates, automatically controlled by the Feedback circuit. andrea. sanchez@cern. ch Versatile Link + 10/05/2019

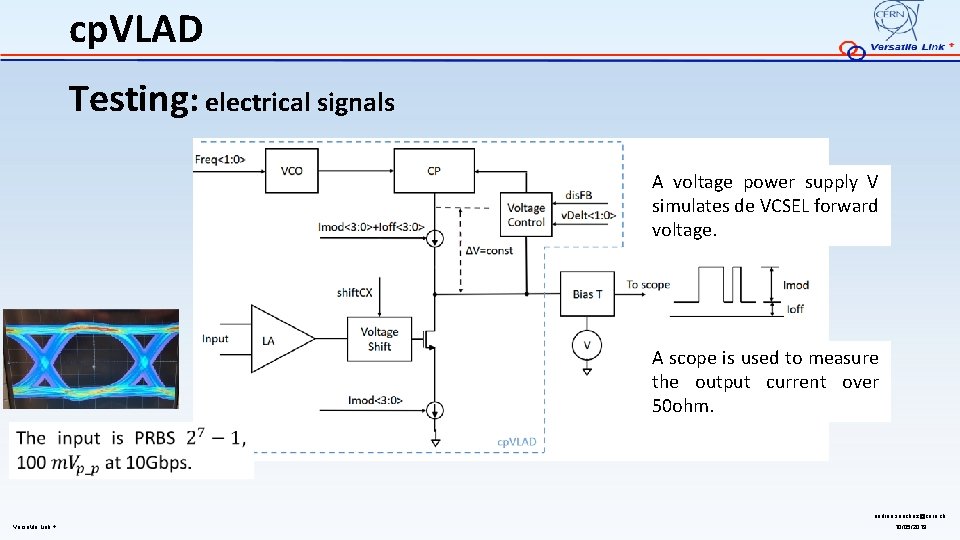

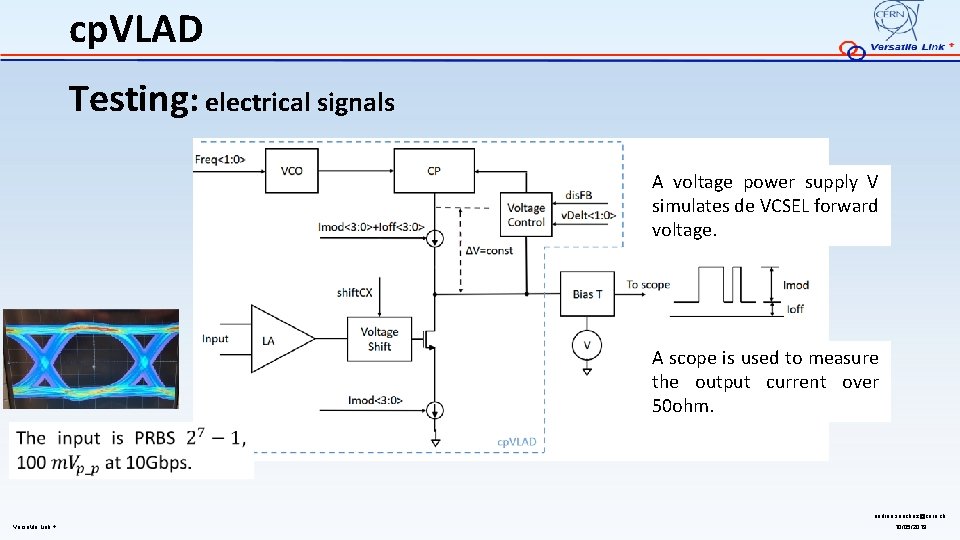

cp. VLAD Testing: electrical signals A voltage power supply V simulates de VCSEL forward voltage. Photo eye diagram from scope A scope is used to measure the output current over 50 ohm. andrea. sanchez@cern. ch Versatile Link + 10/05/2019

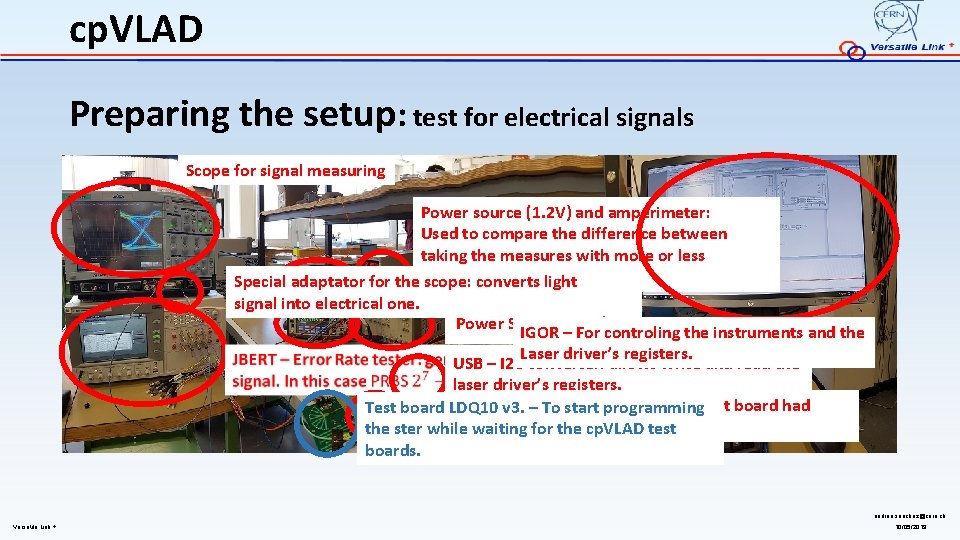

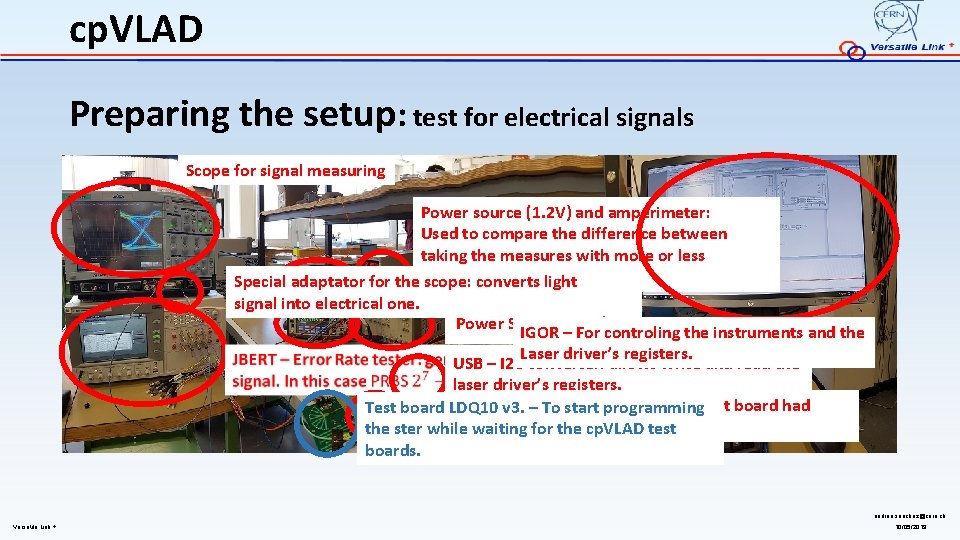

cp. VLAD Preparing the setup: test for electrical signals Scope for signal measuring Power source (1. 2 V) and amperimeter: Used. Amperimeters to compare the difference between – for taking the measures with more or less measuring current Special adaptator for the resolution. scope: converts light consumption of each signal into electrical one of the power Power Source supplies. (2. 5 V) 1. 2 V) IGOR –&For controling the instruments and the Laser driver’s registers. USB – I 2 C converter: allows write and read the laser driver’s registers. because this test board had Test board LDQ 10 Optical v 3. – To. Fiber: start programming installed thecp. VLAD VCSELs. test the ster while waiting for the boards. andrea. sanchez@cern. ch Versatile Link + 10/05/2019

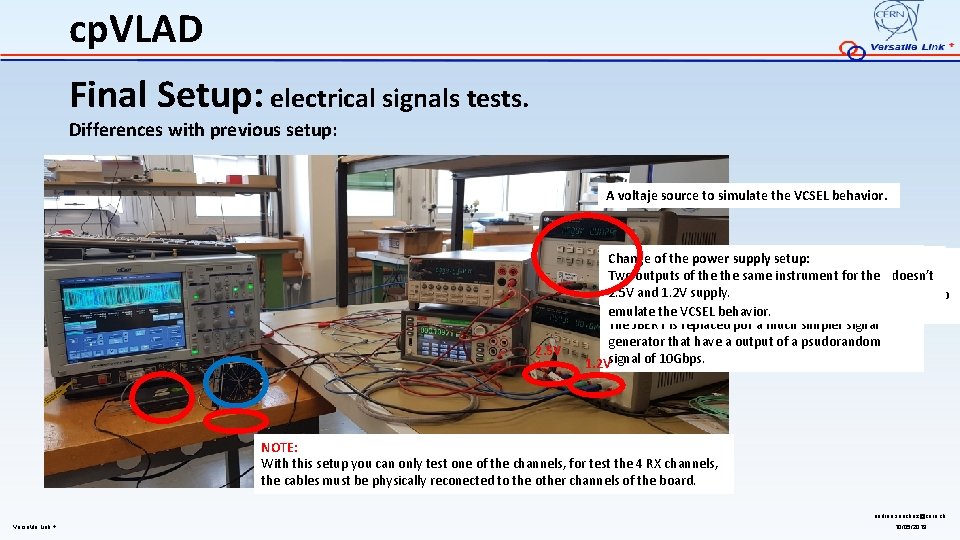

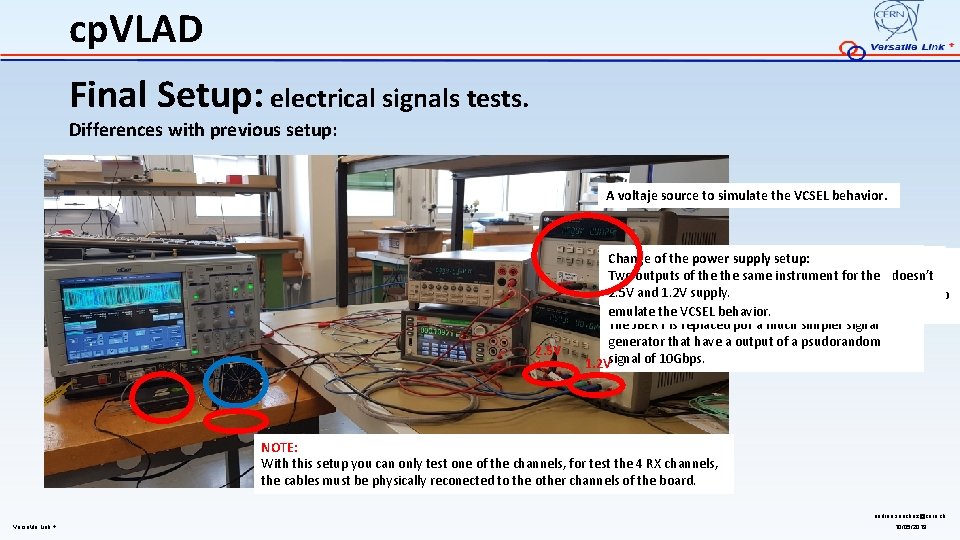

cp. VLAD Final Setup: electrical signals tests. Differences with previous setup: A voltaje source to simulate the VCSEL behavior. 2. 5 V programmable There is of no optical fiber: Change the power supply. JBERT: setup: cp. VLAD test board: After check I dont need to know the input signal Now we only test the electrical signals, this board doesn’t Two outputs of the same instrument for the for have 3 the power supply: capturing it in the samples scope (always conected at one to have the VCSELs only test the laser driver. 2. 5 V and 1. 2 V supply. The same two weanhad before: 2. 5 V & 1. 2 V and a new the Signalthe Generator CLK). emulate VCSEL behavior. The JBERT is replaced por a much simpler signal generator that have a output of a psudorandom 1. 2 Vsignal of 10 Gbps. NOTE: With this setup you can only test one of the channels, for test the 4 RX channels, the cables must be physically reconected to the other channels of the board. andrea. sanchez@cern. ch Versatile Link + 10/05/2019

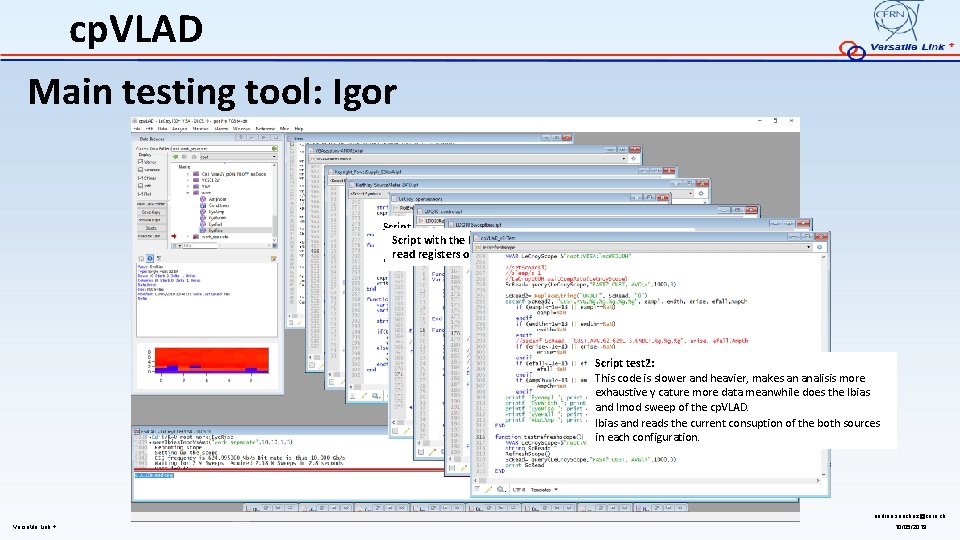

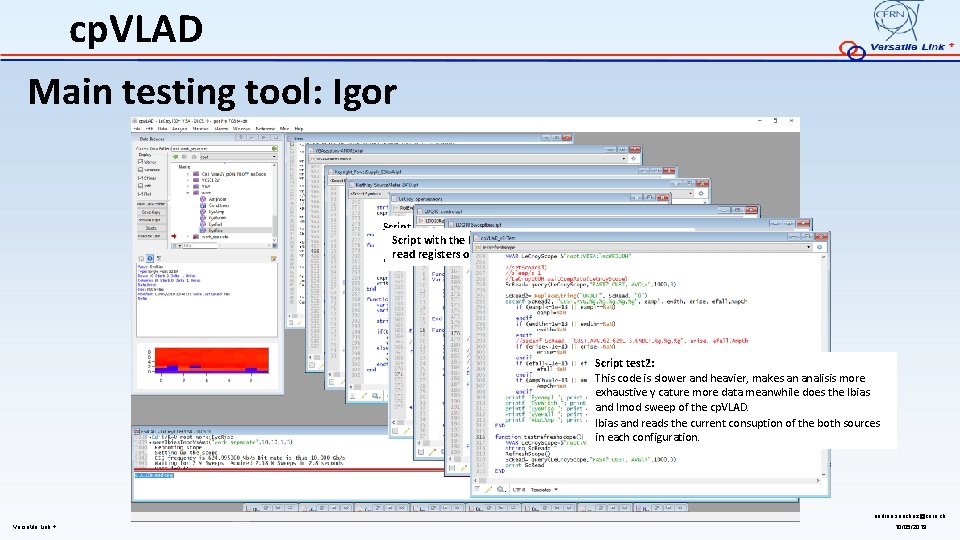

cp. VLAD Main testing tool: Igor Script with the to manage the current and Note pad of thefunctions experiment: Main Igor window: Script of communications: Script with the amperimeter functions manage them. Script with the I 2 C communication to betoable to of write and Script the scope functions. voltaje sources. Annotations to record the status andtesting development the Igor is awith program like Lab. View to do but without the Via Ethernet, GPIB & USB read registers of the cp. VLAD. code. boxes environment, just code. But in change have much better data representations. In this window we can see the folder register and the “waves”, in which Igor store the captured data to plot it after. Script test 2: test 1: This is slower heavier, makes an analisis more Aftercode prepare all theand previous comunication scripts, we can exhaustive cature more data meanwhile does the Ibias start doing ythe test codes. and Imod sweep of the This one makes a sweepcp. VLAD. of all the possible configurations of Ibias and reads the current consuption of the both sources in each configuration. andrea. sanchez@cern. ch Versatile Link + 10/05/2019

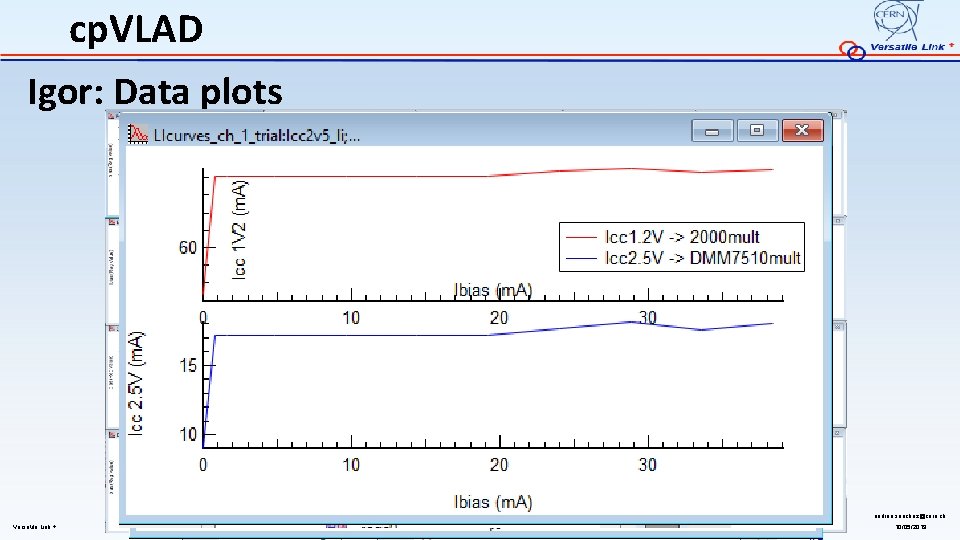

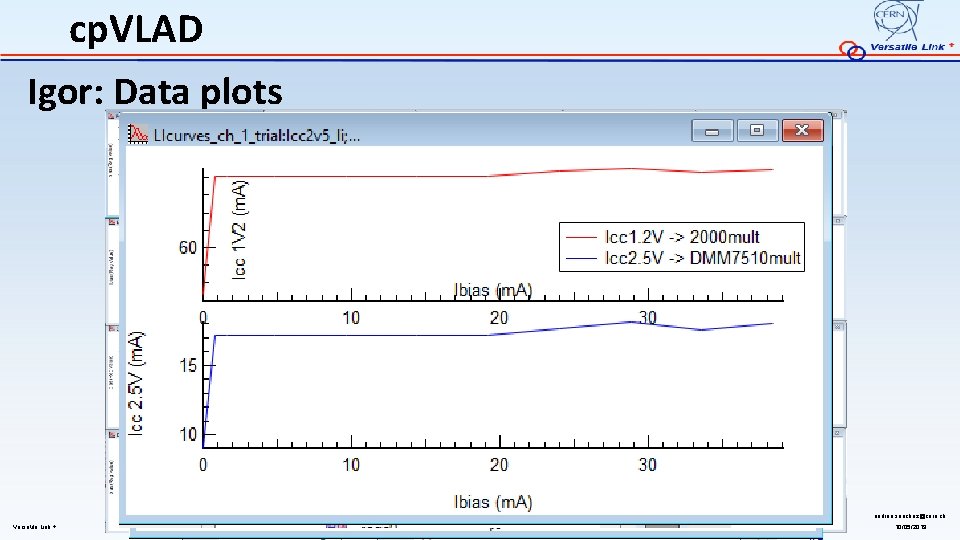

cp. VLAD Igor: Data plots andrea. sanchez@cern. ch Versatile Link + 10/05/2019

cp. VLAD END andrea. sanchez@cern. ch Versatile Link + 10/05/2019

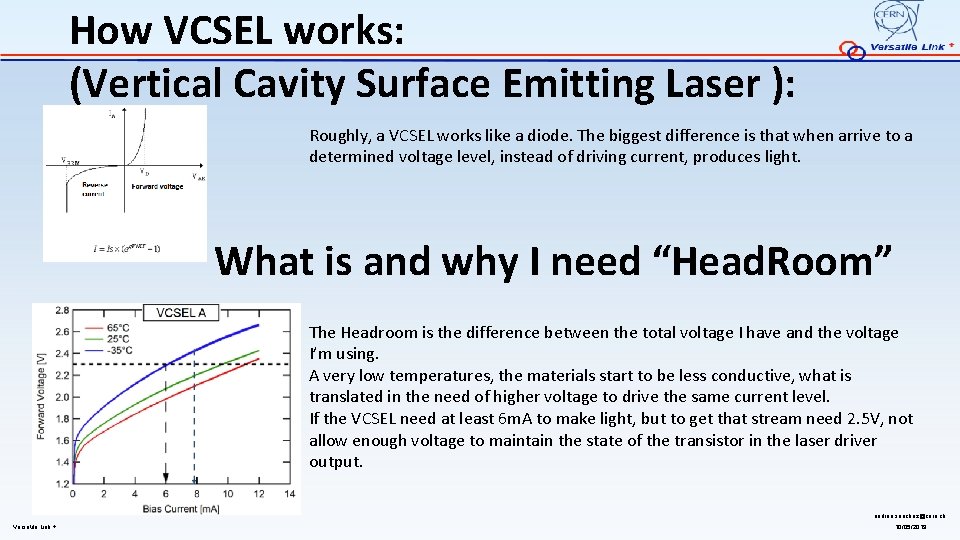

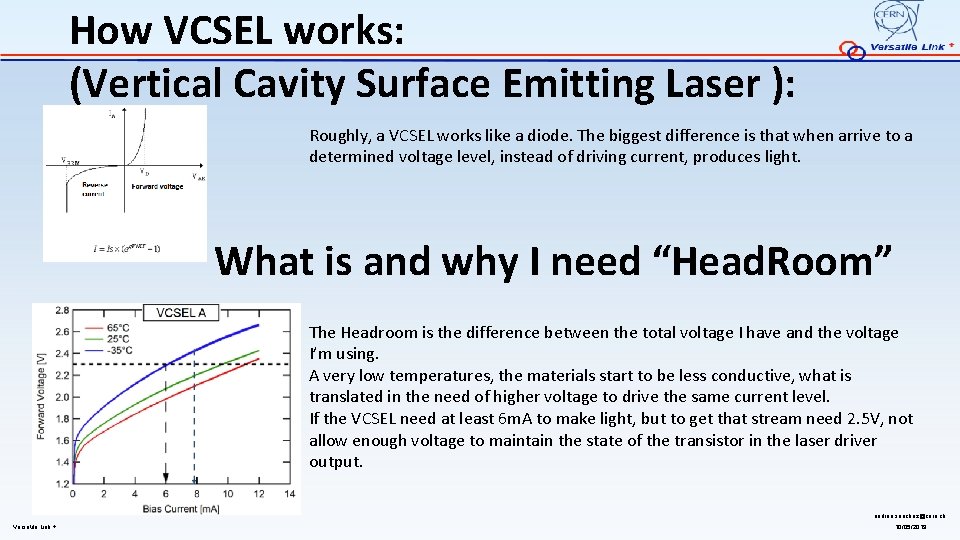

How VCSEL works: (Vertical Cavity Surface Emitting Laser ): Roughly, a VCSEL works like a diode. The biggest difference is that when arrive to a determined voltage level, instead of driving current, produces light. What is and why I need “Head. Room” The Headroom is the difference between the total voltage I have and the voltage I’m using. A very low temperatures, the materials start to be less conductive, what is translated in the need of higher voltage to drive the same current level. If the VCSEL need at least 6 m. A to make light, but to get that stream need 2. 5 V, not allow enough voltage to maintain the state of the transistor in the laser driver output. andrea. sanchez@cern. ch Versatile Link + 10/05/2019