Timing signoff with Prime Time Speaker Bob Tsai

Timing sign-off with Prime. Time Speaker: Bob Tsai Advisor: Jie-Hong Roland Jiang

Outline � Introduction � Flow � On Chip Variation (OCV) � Manual/automated netlist editing � Signal integrity and crosstalk

Introduction � Prime. Time VX, Prime. Time SI � Sign-off ◦ A collective name to a series of verification steps � Standard Parasitic Exchange Format ◦ Represent parasitic data of wires in a chip in ASCII format ◦ Used for delay calculation and ensuring the signal integrity

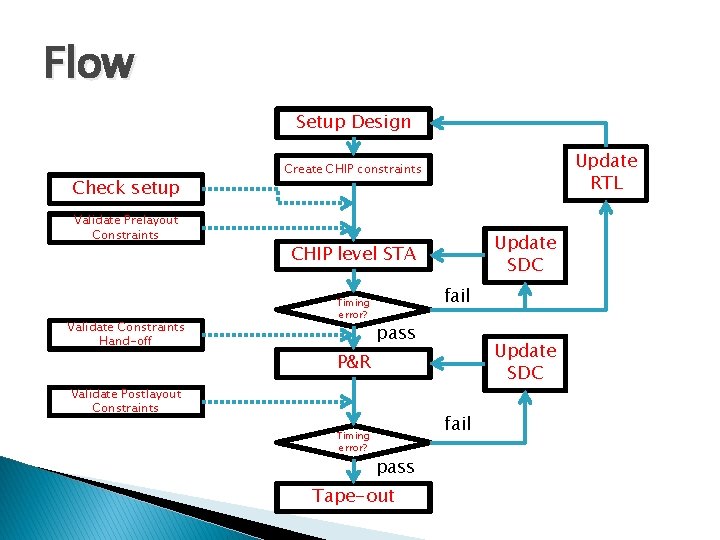

Flow Setup Design Check setup Validate Prelayout Constraints Validate Constraints Hand-off Update RTL Create CHIP constraints Update SDC CHIP level STA Timing error? fail pass Update SDC P&R Validate Postlayout Constraints Timing error? fail pass Tape-out

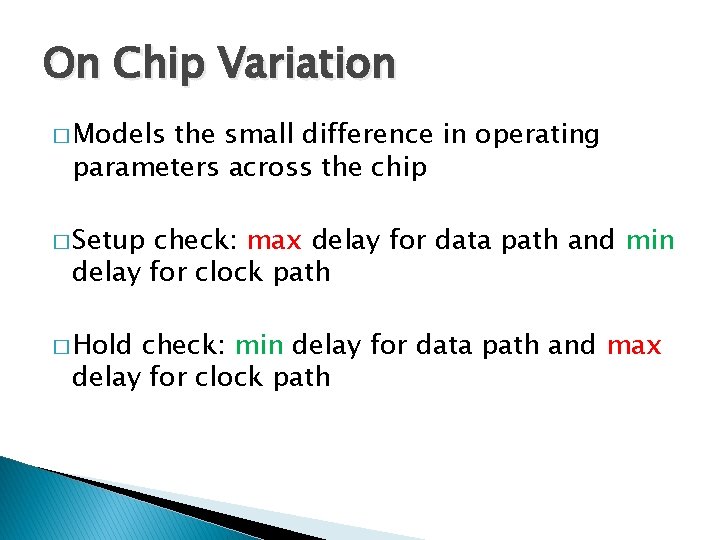

On Chip Variation � Models the small difference in operating parameters across the chip � Setup check: max delay for data path and min delay for clock path � Hold check: min delay for data path and max delay for clock path

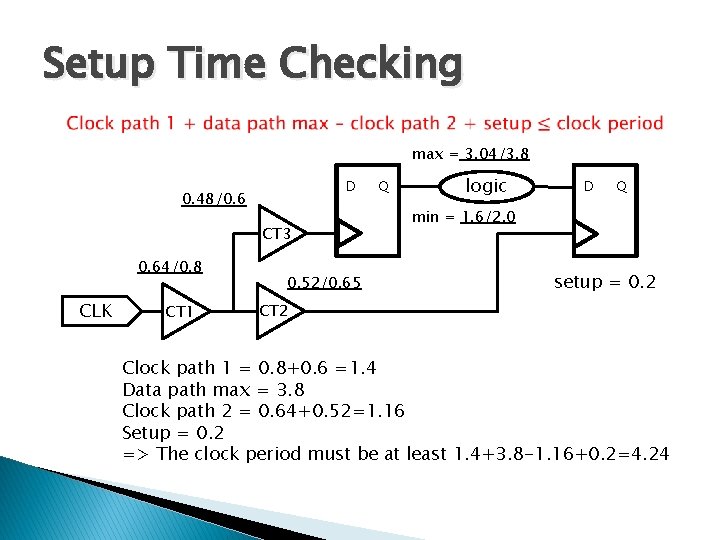

Setup Time Checking max = 3. 04/3. 8 D 0. 48/0. 6 CT 3 0. 64/0. 8 CLK CT 1 0. 52/0. 65 Q logic D Q min = 1. 6/2. 0 setup = 0. 2 CT 2 Clock path 1 = 0. 8+0. 6 =1. 4 Data path max = 3. 8 Clock path 2 = 0. 64+0. 52=1. 16 Setup = 0. 2 => The clock period must be at least 1. 4+3. 8 -1. 16+0. 2=4. 24

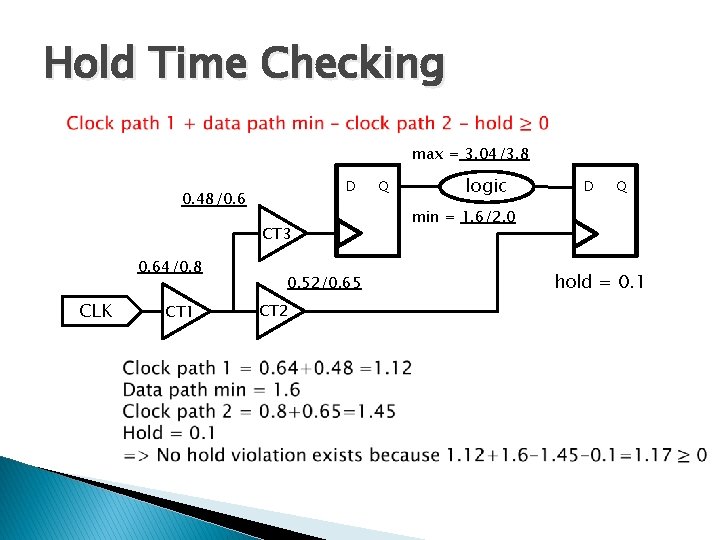

Hold Time Checking max = 3. 04/3. 8 D 0. 48/0. 6 CT 3 0. 64/0. 8 CLK CT 1 0. 52/0. 65 CT 2 Q logic D Q min = 1. 6/2. 0 hold = 0. 1

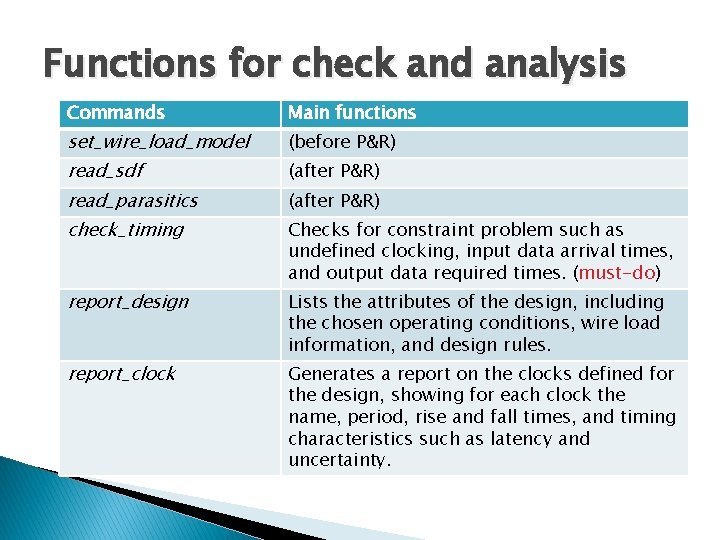

Functions for check and analysis Commands Main functions set_wire_load_model (before P&R) read_sdf read_parasitics (after P&R) check_timing Checks for constraint problem such as undefined clocking, input data arrival times, and output data required times. (must-do) report_design Lists the attributes of the design, including the chosen operating conditions, wire load information, and design rules. report_clock Generates a report on the clocks defined for the design, showing for each clock the name, period, rise and fall times, and timing characteristics such as latency and uncertainty.

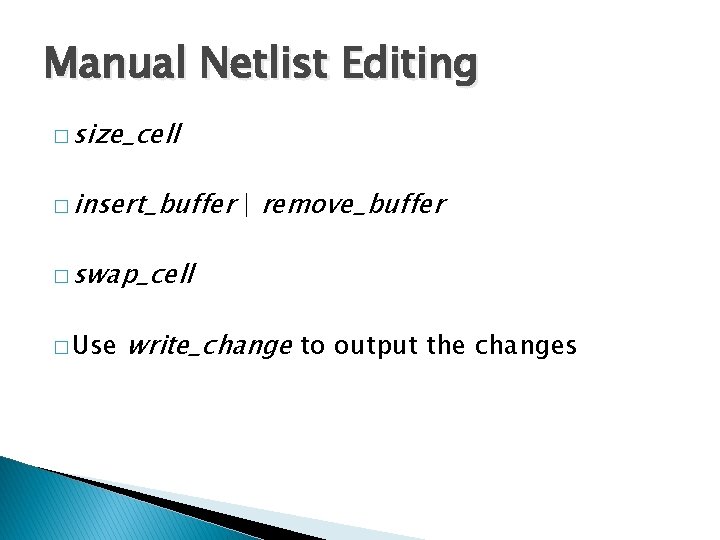

Manual Netlist Editing � size_cell � insert_buffer | remove_buffer � swap_cell � Use write_change to output the changes

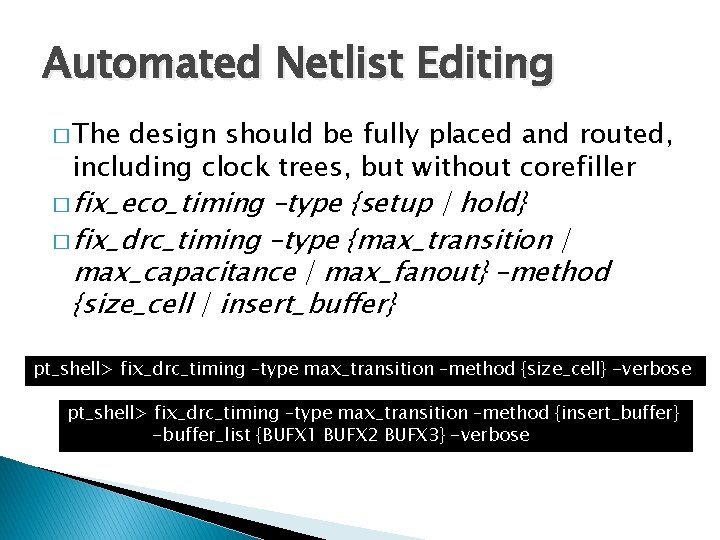

Automated Netlist Editing � The design should be fully placed and routed, including clock trees, but without corefiller � fix_eco_timing –type {setup | hold} � fix_drc_timing –type {max_transition | max_capacitance | max_fanout} –method {size_cell | insert_buffer} pt_shell> fix_drc_timing –type max_transition –method {size_cell} -verbose pt_shell> fix_drc_timing –type max_transition –method {insert_buffer} -buffer_list {BUFX 1 BUFX 2 BUFX 3} -verbose

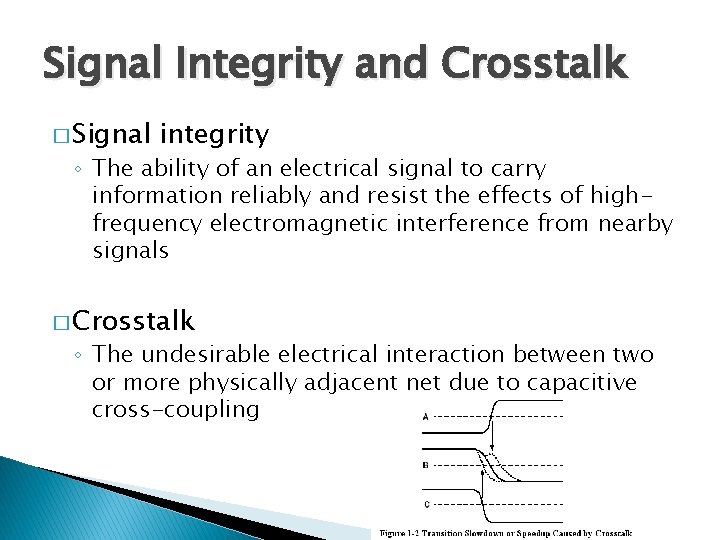

Signal Integrity and Crosstalk � Signal integrity ◦ The ability of an electrical signal to carry information reliably and resist the effects of highfrequency electromagnetic interference from nearby signals � Crosstalk ◦ The undesirable electrical interaction between two or more physically adjacent net due to capacitive cross-coupling

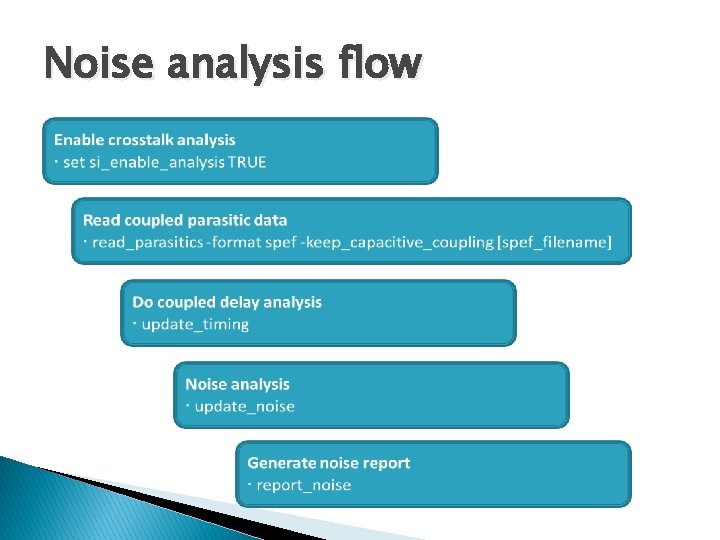

Noise analysis flow

Thanks for your attention

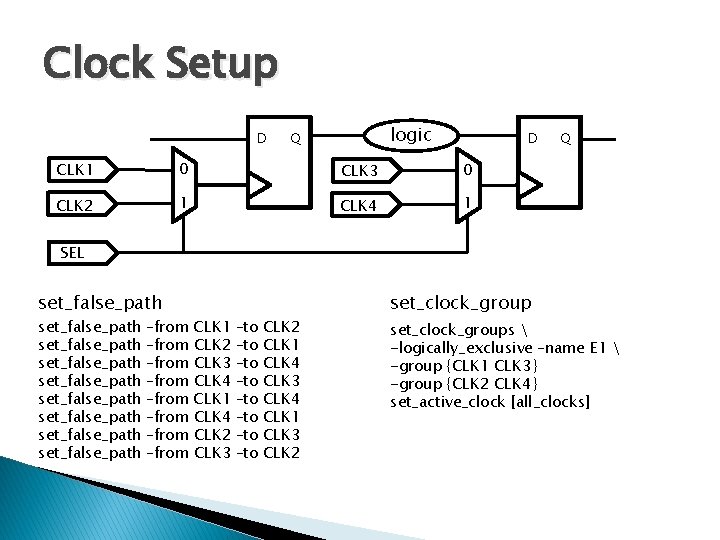

Clock Setup D logic Q D CLK 1 0 CLK 3 0 CLK 2 1 CLK 4 1 Q SEL set_false_path set_false_path set_false_path –from –from CLK 1 CLK 2 CLK 3 CLK 4 CLK 1 CLK 4 CLK 2 CLK 3 –to –to CLK 2 CLK 1 CLK 4 CLK 3 CLK 4 CLK 1 CLK 3 CLK 2 set_clock_groups -logically_exclusive –name E 1 -group {CLK 1 CLK 3} -group {CLK 2 CLK 4} set_active_clock [all_clocks]

- Slides: 14