Sharif University of Technology Department of Computer Engineering

- Slides: 10

Sharif University of Technology Department of Computer Engineering Behavioral Modeling 2 Alireza Ejlali

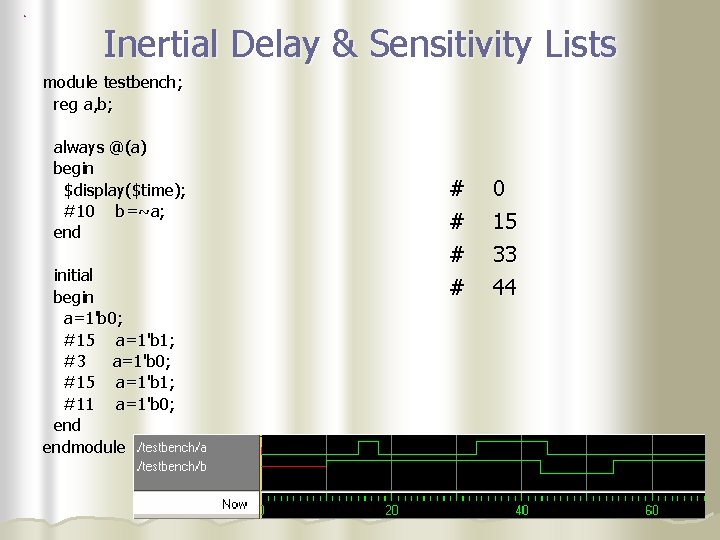

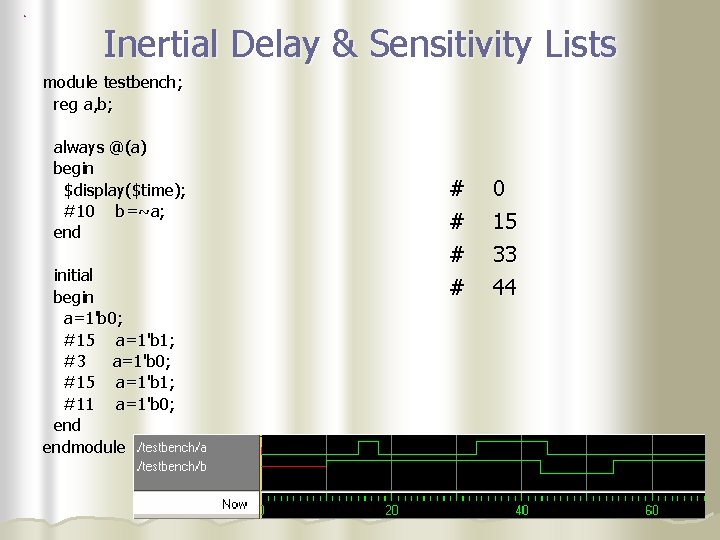

Inertial Delay & Sensitivity Lists module testbench; reg a, b; always @(a) begin $display($time); #10 b=~a; end initial begin a=1'b 0; #15 a=1'b 1; #3 a=1'b 0; #15 a=1'b 1; #11 a=1'b 0; endmodule # # 0 15 33 44

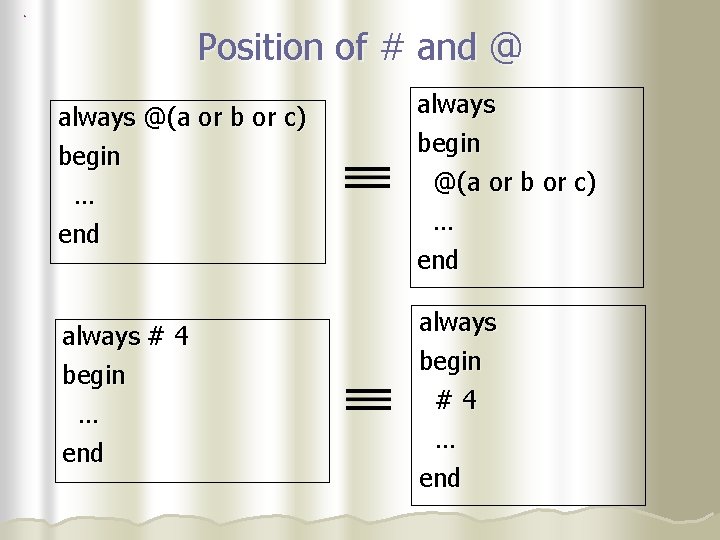

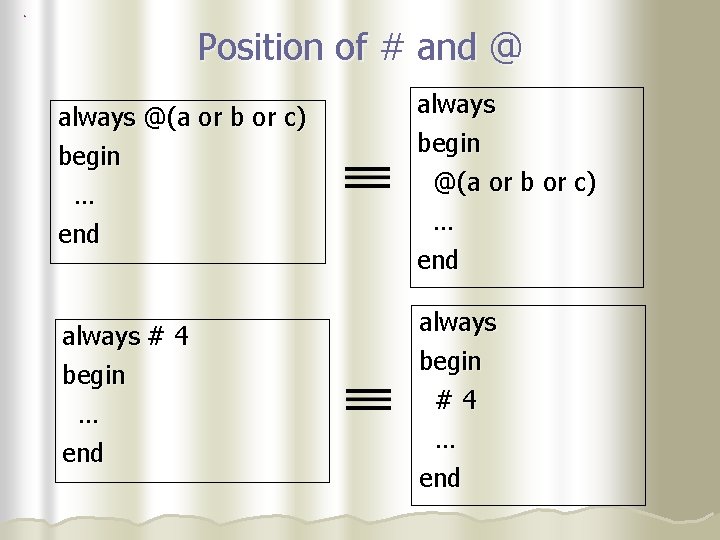

Position of # and @ always @(a or b or c) begin … end always # 4 begin … end always begin @(a or b or c) … end always begin #4 … end

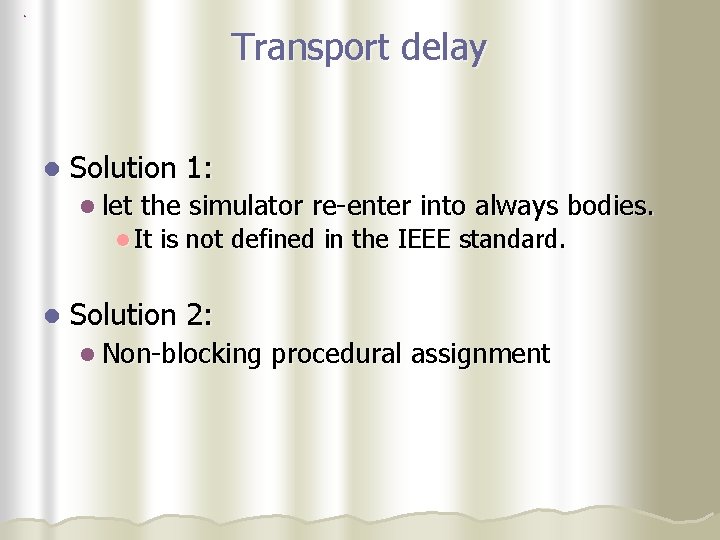

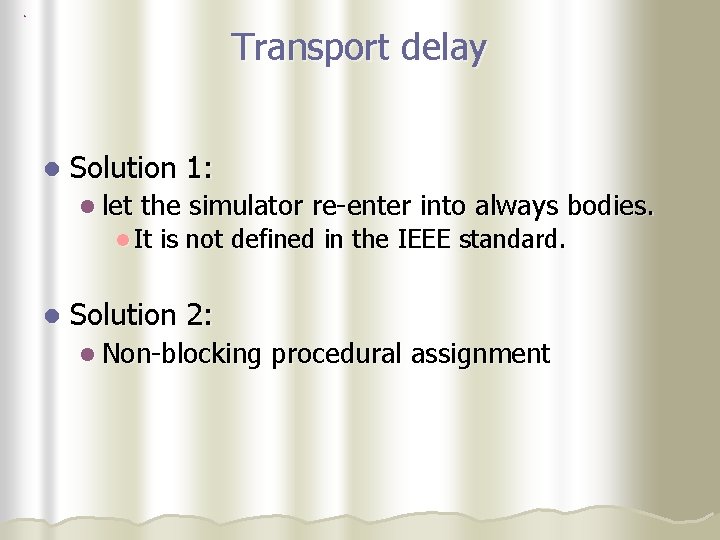

Transport delay l Solution 1: l let the simulator re-enter into always bodies. l It l is not defined in the IEEE standard. Solution 2: l Non-blocking procedural assignment

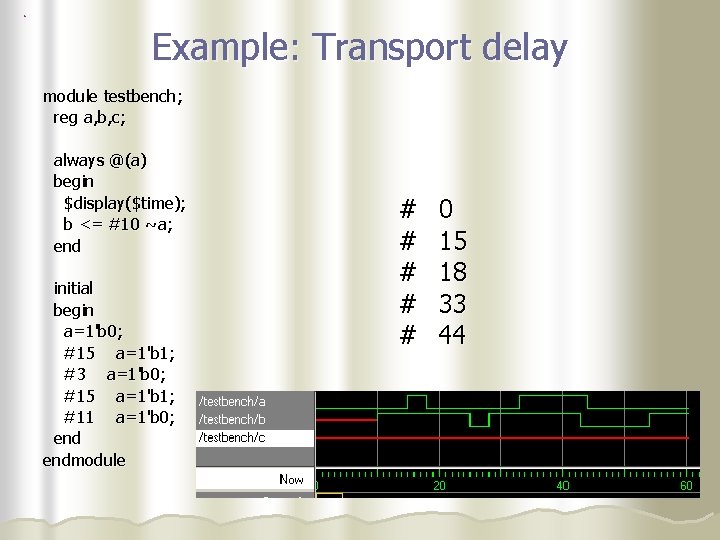

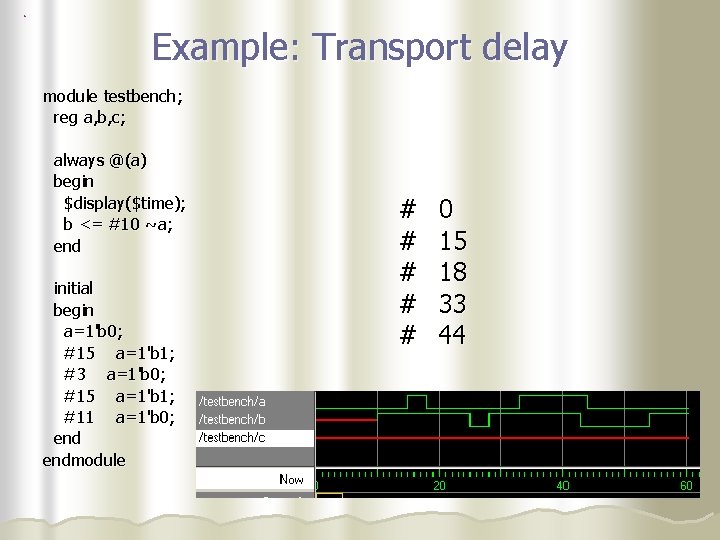

Example: Transport delay module testbench; reg a, b, c; always @(a) begin $display($time); b <= #10 ~a; end initial begin a=1'b 0; #15 a=1'b 1; #3 a=1'b 0; #15 a=1'b 1; #11 a=1'b 0; endmodule # # # 0 15 18 33 44

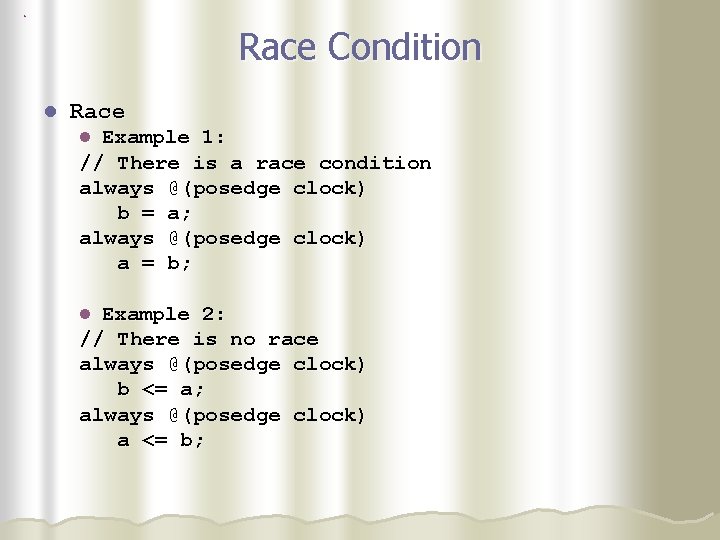

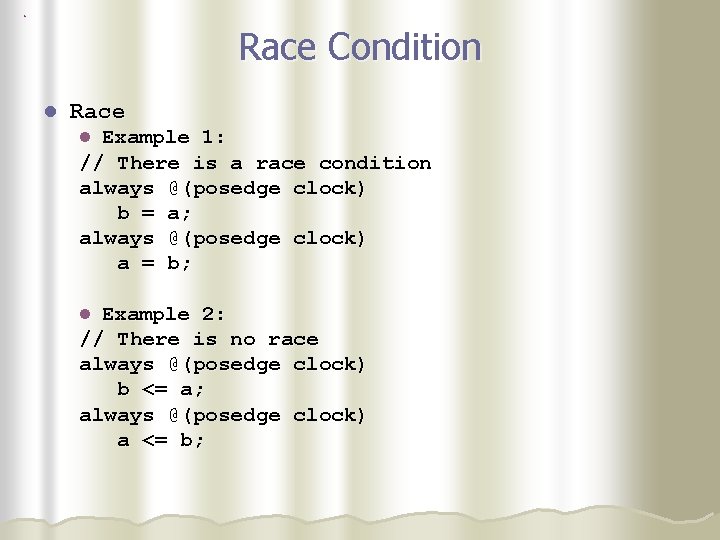

Race Condition l Race Example 1: // There is a race condition always @(posedge clock) b = a; always @(posedge clock) a = b; l Example 2: // There is no race always @(posedge clock) b <= a; always @(posedge clock) a <= b; l

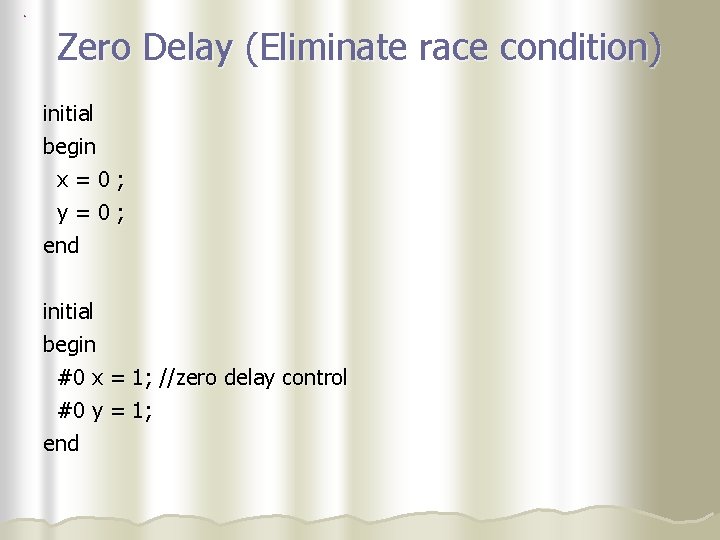

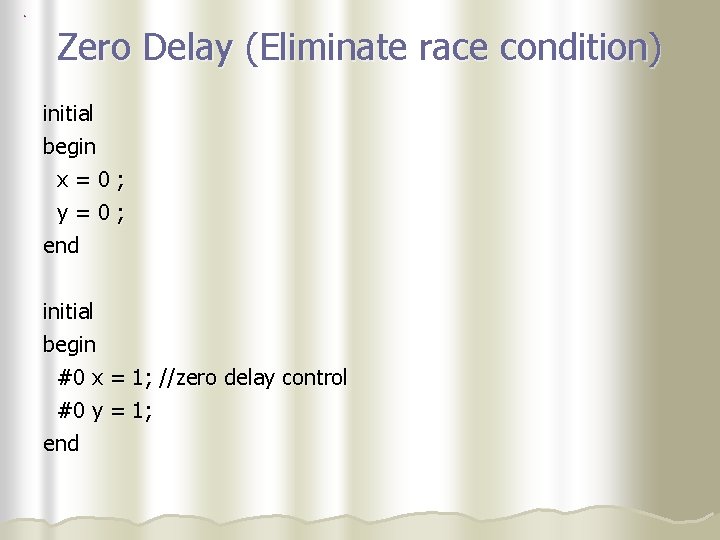

Zero Delay (Eliminate race condition) initial begin x=0; y=0; end initial begin #0 x = 1; //zero delay control #0 y = 1; end

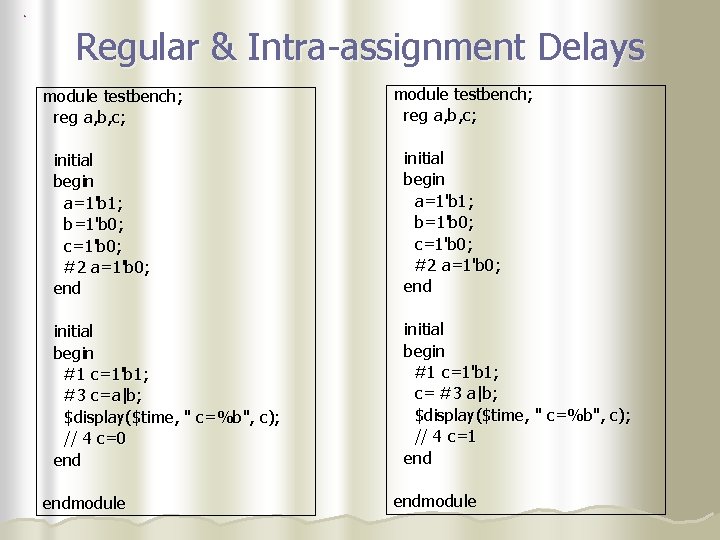

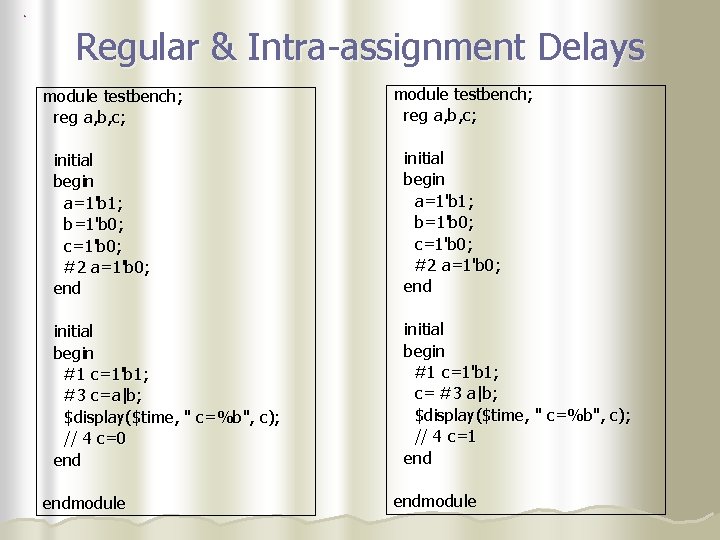

Regular & Intra-assignment Delays module testbench; reg a, b, c; initial begin a=1'b 1; b=1'b 0; c=1'b 0; #2 a=1'b 0; end initial begin #1 c=1'b 1; #3 c=a|b; $display($time, " c=%b", c); // 4 c=0 end initial begin #1 c=1'b 1; c= #3 a|b; $display($time, " c=%b", c); // 4 c=1 endmodule

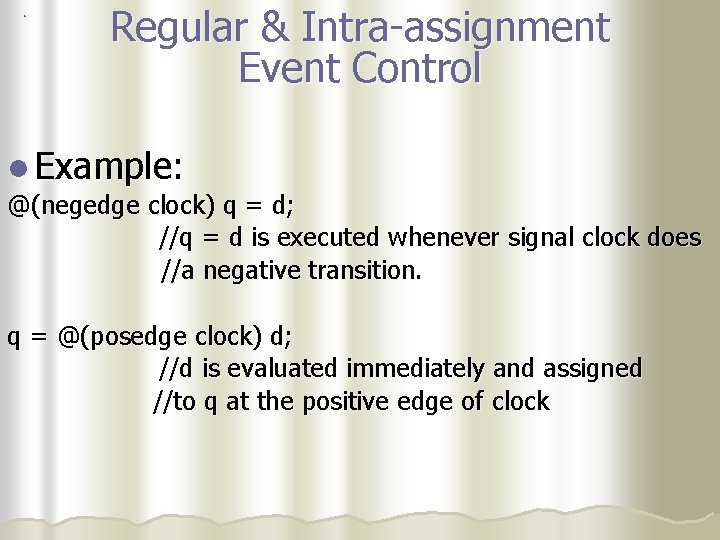

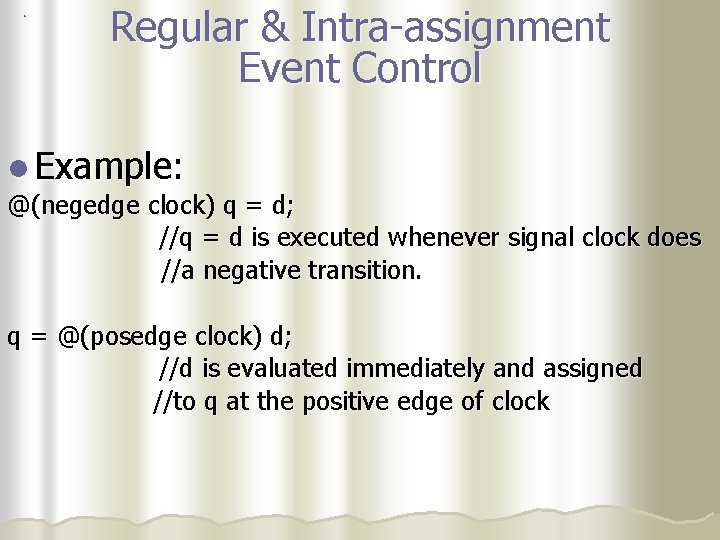

Regular & Intra-assignment Event Control l Example: @(negedge clock) q = d; //q = d is executed whenever signal clock does //a negative transition. q = @(posedge clock) d; //d is evaluated immediately and assigned //to q at the positive edge of clock

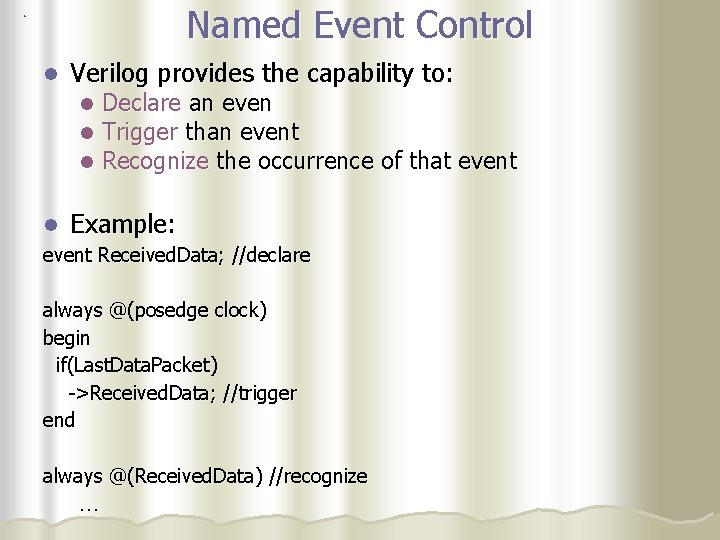

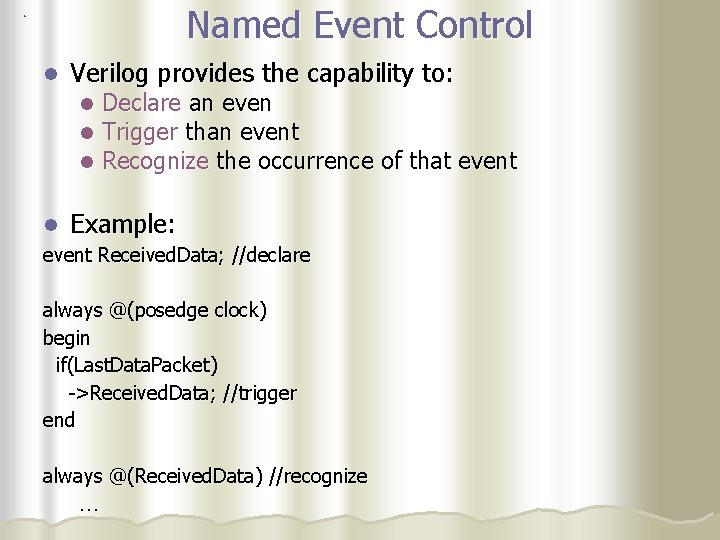

Named Event Control l Verilog provides the capability to: l l Declare an even Trigger than event Recognize the occurrence of that event Example: event Received. Data; //declare always @(posedge clock) begin if(Last. Data. Packet) ->Received. Data; //trigger end always @(Received. Data) //recognize …