ScanThroughTAP Combining Scan Chain and Boundary Scan Features

Scan-Through-TAP: Combining Scan Chain and Boundary Scan Features in SOC Z. Stamenković1, M. Giles 2, and F. Russi 2 1 IHP Gmb. H, Frankfurt (Oder), GERMANY 2 Synopsys Inc. , Mountain View, CA, USA 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

Introduction • What is Scan-through-TAP? Use of IEEE Standard 1149. 1 user instruction to concatenate the internal scan chain with the BSR chain to perform a single chain operation • What do we achieve implementing Scan-through-TAP? Reduction of the scan pins number Accessibility of the internal scan chains through the TAP controller Single shift path through for burn-in and diagnostics • What kind of EDA tools do we need? Standard synthesis, DFT, BSD, and ATPG tools 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

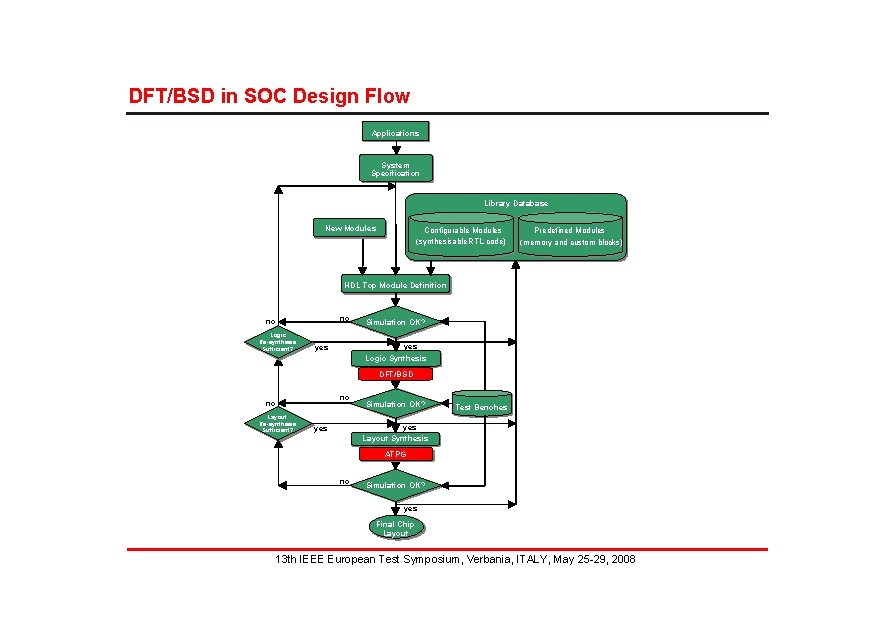

DFT/BSD in SOC Design Flow Applications System Specification Library Database New Modules Configurable Modules New Modules Customisable. RTL Modules (synthesisable code) (synthesisable RTL code) Predefined Modules (synthesised net-list, blocks) SDF (memory and custom and/or LEF) HDL Top. Model Module Definition HDL Definition no no Logic Re-synthesis Sufficient? Simulation OK? yes Logic Synthesis DFT/BSD no no Layout Re-synthesis Sufficient? Simulation OK? Test. Benches yes Layout Synthesis yes ATPG no Simulation OK? yes Final Chip Layout 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

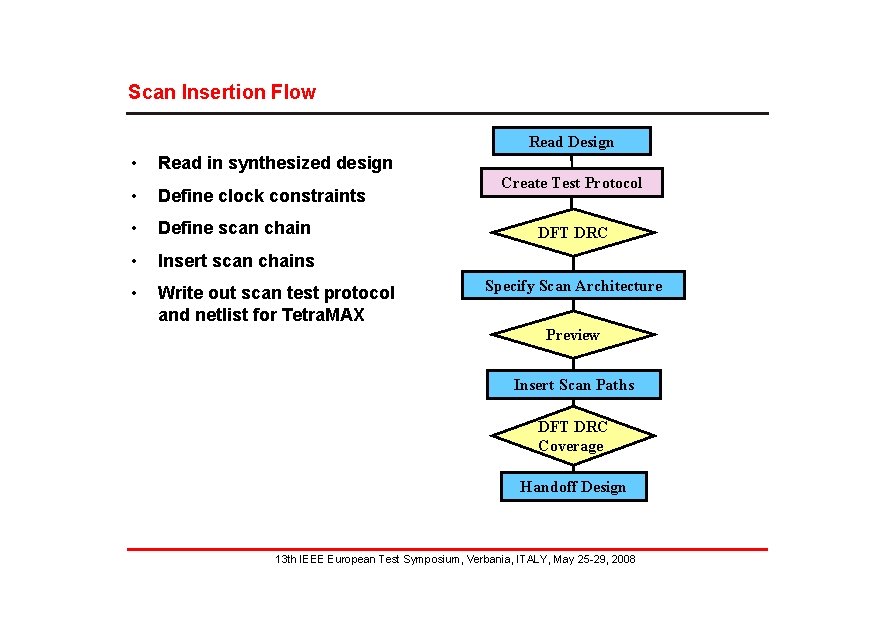

Scan Insertion Flow Read Design • Read in synthesized design • Define clock constraints • Define scan chain • Insert scan chains • Write out scan test protocol and netlist for Tetra. MAX Create Test Protocol DFT DRC Specify Scan Architecture Preview Insert Scan Paths DFT DRC Coverage Handoff Design 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

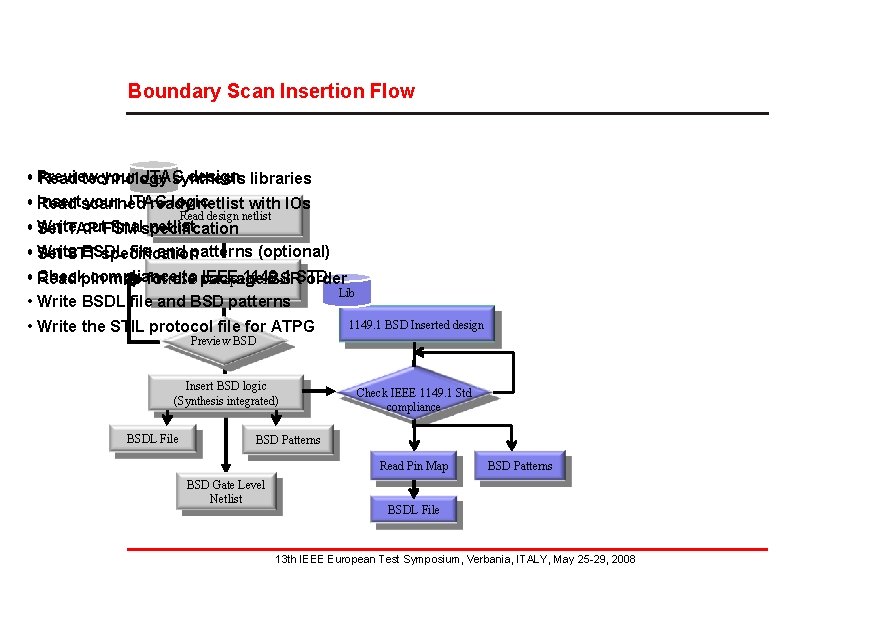

Boundary Scan Insertion Flow your JTAG design libraries • Preview Read technology Lib synthesis • Insert your JTAG logic Read scanned ready netlist with IOs Read design netlist • Write out. FSM finalspecification netlist Set TAP Write BSDL file and patterns (optional) • Set STT specification • Check compliance to package IEEE 1149. 1 Set die BSD STT specifications Read pin map for BSRSTD order • Write BSDL file and BSD patterns • Write the STIL protocol file for ATPG Lib 1149. 1 BSD Inserted design Preview BSD Insert BSD logic (Synthesis integrated) BSDL File Check IEEE 1149. 1 Std compliance BSD Patterns Read Pin Map BSD Gate Level Netlist BSD Patterns BSDL File 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

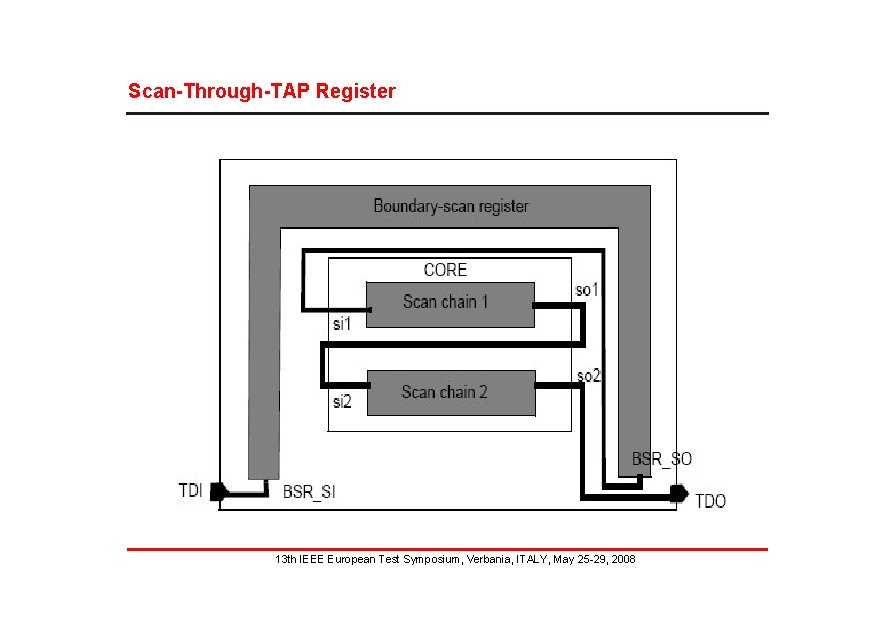

Scan-Through-TAP Register 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

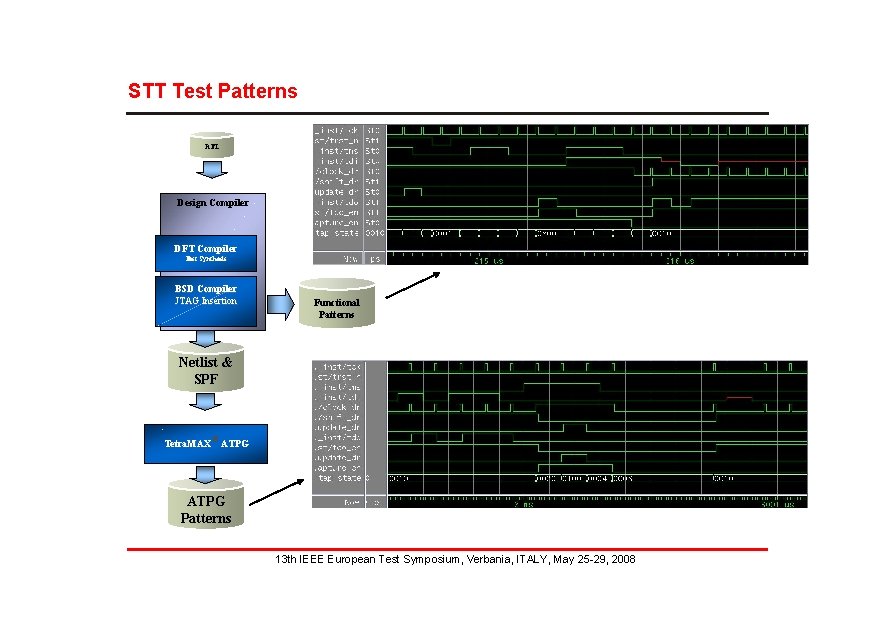

STT Test Patterns RTL Design Compiler DFT Compiler Test Synthesis BSD Compiler JTAG Insertion Functional Patterns Netlist & SPF Tetra. MAX® ATPG Patterns 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

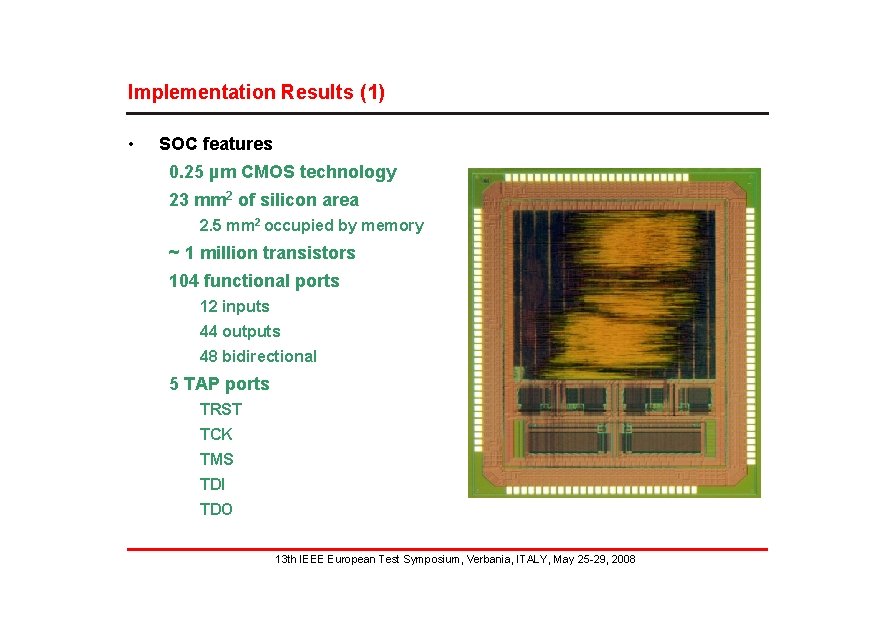

Implementation Results (1) • SOC features 0. 25 µm CMOS technology 23 mm 2 of silicon area 2. 5 mm 2 occupied by memory ~ 1 million transistors 104 functional ports 12 inputs 44 outputs 48 bidirectional 5 TAP ports TRST TCK TMS TDI TDO 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

Implementation Results (2) • Single scan register made of around 15000 scan flip-flops • Boundary scan register of 151 cell • 5 TAP instructions BYPASS EXTEST PRELOAD SAMPLE STT • 32000 BSD functional test patterns • 1151 ATPG test patterns • Chip area overhead below 7% Caused by insertion of scan flip-flops and boundary scan logic • Combined fault coverage is slightly above 94% 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

Summary • Scan-Through-TAP methodology provides the infrastructure for both testing of system’s internal nodes and testing of system’s boundary circuitry A good solution for pin limited SOC designs • A middle-size processor-based SOC used for implementation Results show small chip area overhead, acceptable number of test patterns, and high fault coverage 13 th IEEE European Test Symposium, Verbania, ITALY, May 25 -29, 2008

- Slides: 10