Outlay for Calorimeter Pulser Communication Summary of dedicated

- Slides: 8

Outlay for Calorimeter Pulser Communication Summary of dedicated D 0 calorimeter electronics meeting FNAL, 9/10/99 Fritz Barrtelet, Ursula Bassler, Mrinmoy Bhattacharjee, Leslie Groer, Frederic Machefert, Bob Mc. Carthy, Bob Olivier, Dean Schamberger Rampe update: 13/6/00

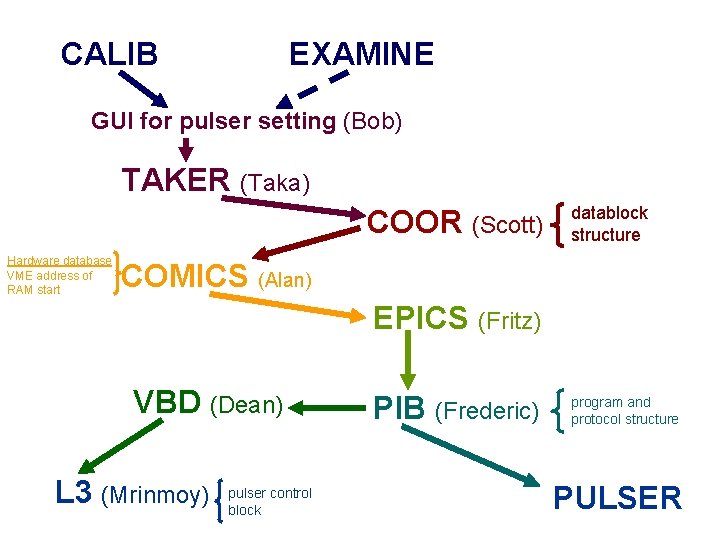

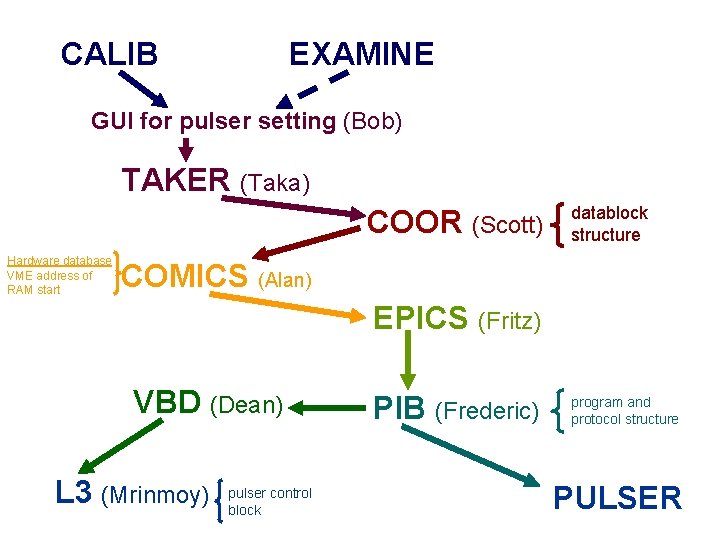

CALIB EXAMINE GUI for pulser setting (Bob) TAKER (Taka) COOR (Scott) Hardware database VME address of RAM start datablock structure COMICS (Alan) EPICS (Fritz) VBD (Dean) L 3 (Mrinmoy) pulser control block PIB (Frederic) program and protocol structure PULSER

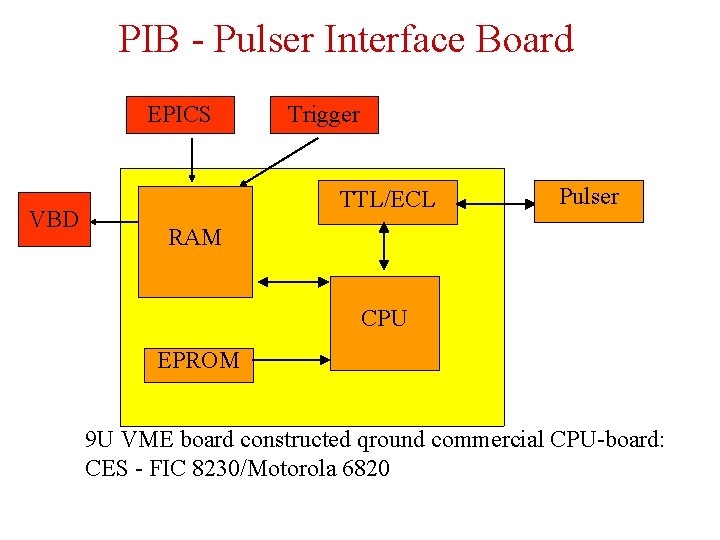

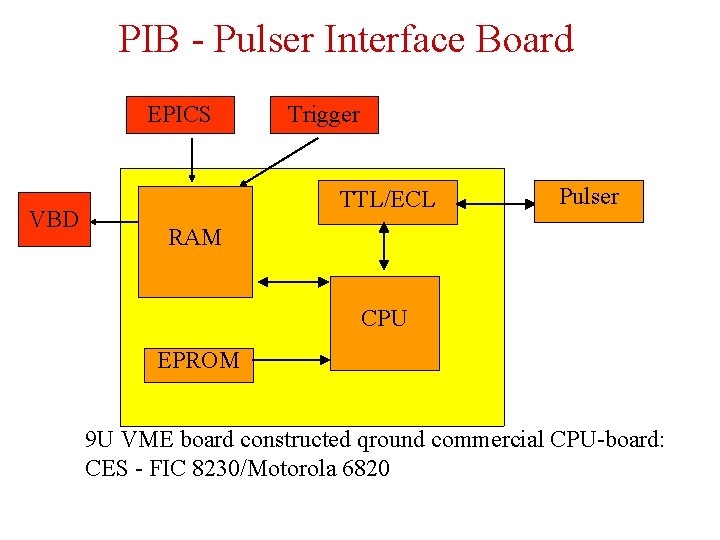

PIB - Pulser Interface Board EPICS VBD Trigger TTL/ECL Pulser RAM CPU EPROM 9 U VME board constructed qround commercial CPU-board: CES - FIC 8230/Motorola 6820

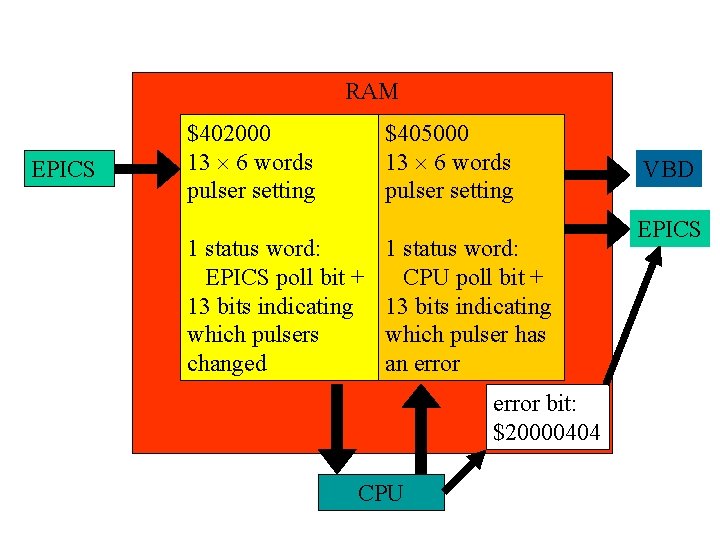

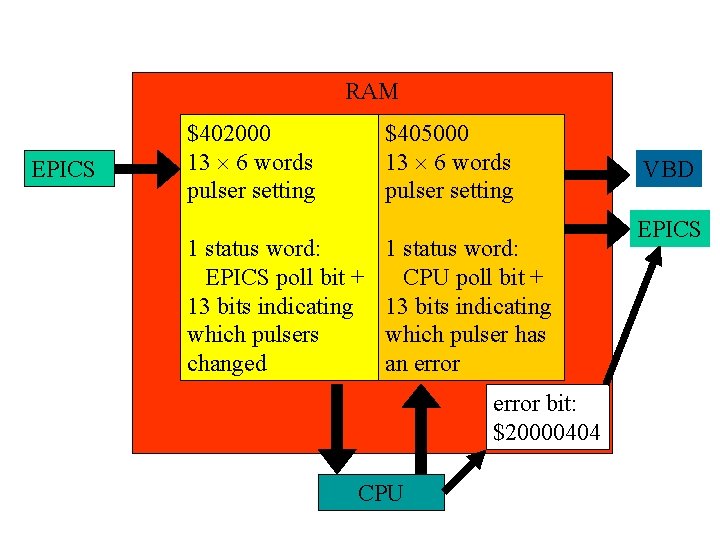

RAM EPICS $402000 13 6 words pulser setting $405000 13 6 words pulser setting 1 status word: EPICS poll bit + 13 bits indicating which pulsers changed 1 status word: CPU poll bit + 13 bits indicating which pulser has an error bit: $20000404 CPU VBD EPICS

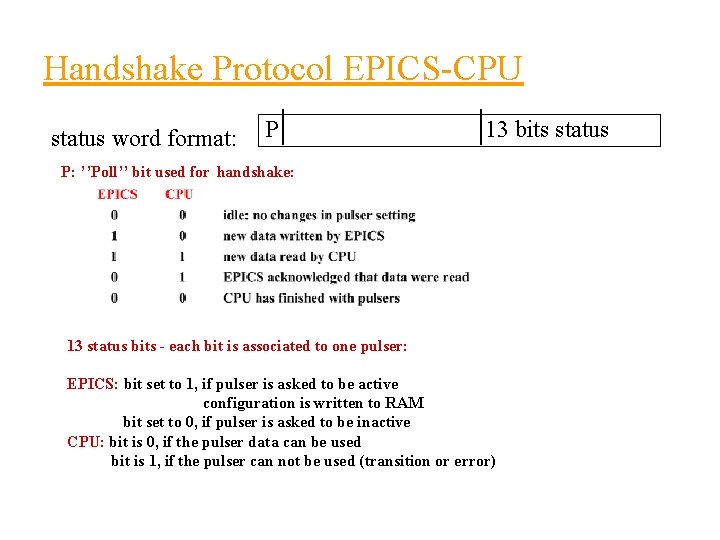

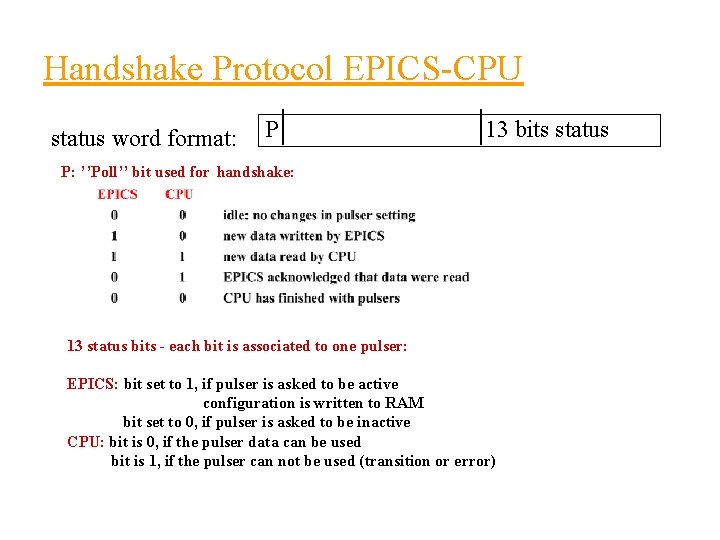

Handshake Protocol EPICS-CPU status word format: P | |13 bits status P: ’’Poll’’ bit used for handshake: 13 status bits - each bit is associated to one pulser: EPICS: bit set to 1, if pulser is asked to be active configuration is written to RAM bit set to 0, if pulser is asked to be inactive CPU: bit is 0, if the pulser data can be used bit is 1, if the pulser can not be used (transition or error)

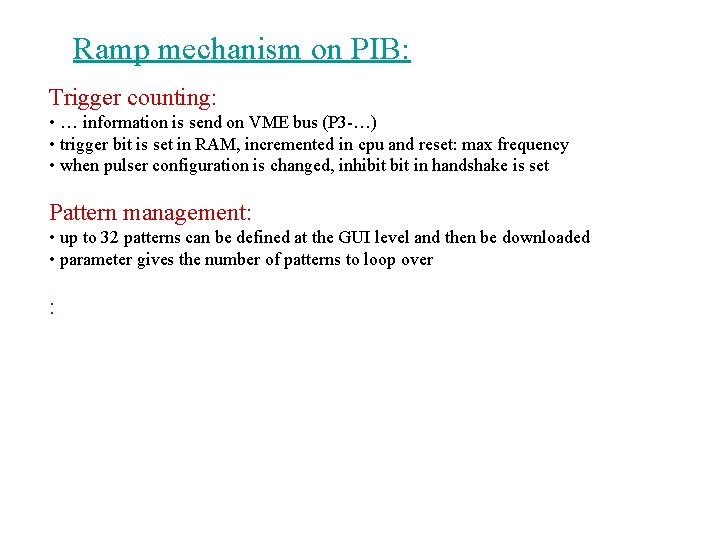

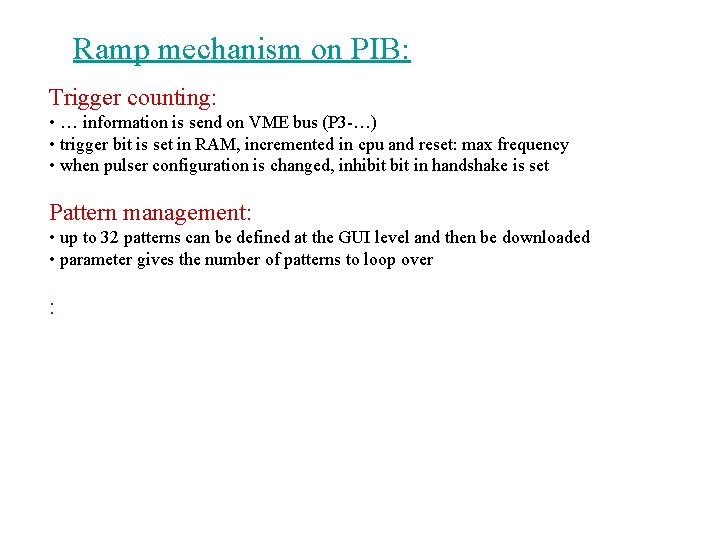

Ramp mechanism on PIB: Trigger counting: • … information is send on VME bus (P 3 -…) • trigger bit is set in RAM, incremented in cpu and reset: max frequency • when pulser configuration is changed, inhibit in handshake is set Pattern management: • up to 32 patterns can be defined at the GUI level and then be downloaded • parameter gives the number of patterns to loop over :

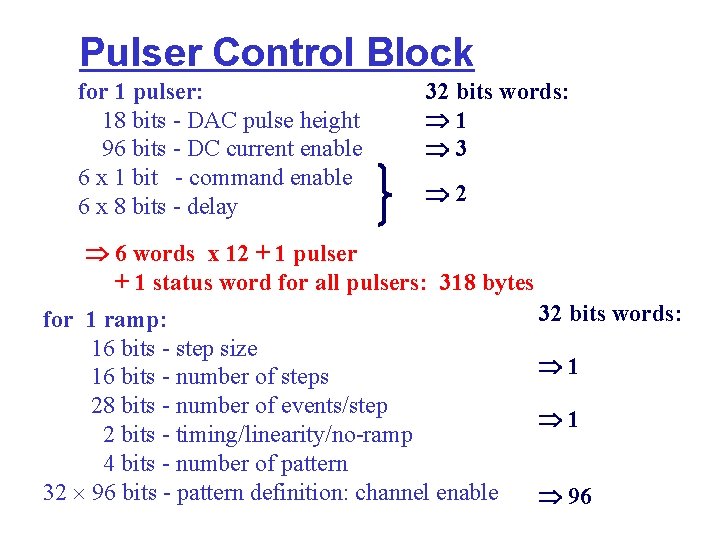

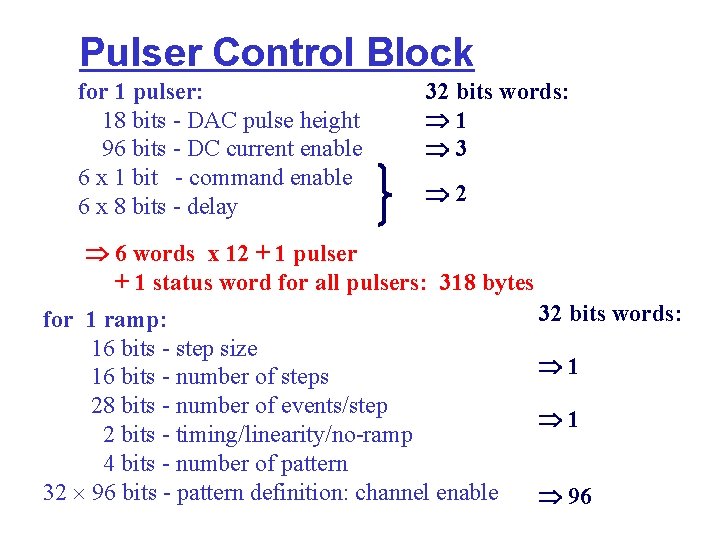

Pulser Control Block for 1 pulser: 18 bits - DAC pulse height 96 bits - DC current enable 6 x 1 bit - command enable 6 x 8 bits - delay 32 bits words: 1 3 2 6 words x 12 + 1 pulser + 1 status word for all pulsers: 318 bytes for 1 ramp: 16 bits - step size 16 bits - number of steps 28 bits - number of events/step 2 bits - timing/linearity/no-ramp 4 bits - number of pattern 32 96 bits - pattern definition: channel enable 32 bits words: 1 1 96

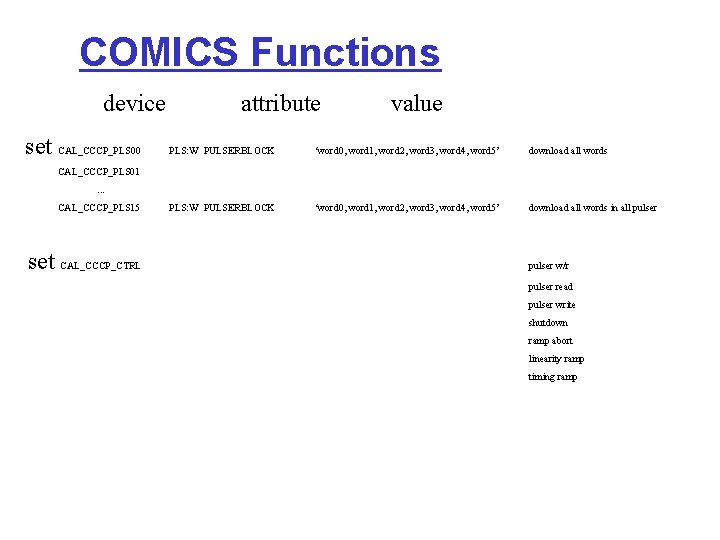

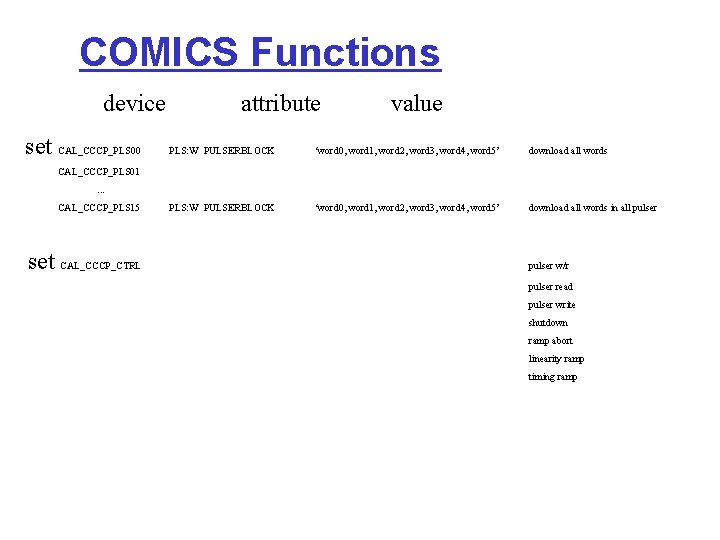

COMICS Functions device set CAL_CCCP_PLS 00 attribute value PLS: W PULSERBLOCK ‘word 0, word 1, word 2, word 3, word 4, word 5’ download all words in all pulser CAL_CCCP_PLS 01. . . CAL_CCCP_PLS 15 set CAL_CCCP_CTRL pulser w/r pulser read pulser write shutdown ramp abort linearity ramp timing ramp