Normal text click to edit RCU 3 RCU

- Slides: 13

Normal text - click to edit RCU 3 –> RCU 4 New Schematics Kjetil Ullaland, Bjørn Pommeresche, Ketil Røed, Johan Alme TPC Electronics meeting. CERN 13 -14. Jan 2005

Motivation for the design revision • After several beam tests it was found that the Single Event Normal textwas- on click to ofedit Functional Interrupt-rate the limit what we can tolerate. • Hence, a change in technology was required to provide better protection for upsets. • The Xilinx Virtex architecture provides readback and refresh of the configuration memory without disturbing the firmware.

Most important changes • The Virtex II replaces the Altera APEX as the main FPGA Normal text - click to edit of the RCU • A Flash based CPLD is introduced as a programming support circuit for the Virtex FPGA • A Flash RAM circuit is added in order to make the scrubbing of the configuration memory independent of the DCS-card

Minor changes in the design • The termination network of GTL buffers has been simplified. Normal text - click to edit • The number of control lines for the buffers are reduced • An ADC for current measurement is added • The option for 3. 3 or 2. 5 V as IO voltage is removed (the RCU IO is only 3. 3 V, the Xilinx core voltage is 1. 5 v) • The voltage regulators of the termination network are replaced for better power margin

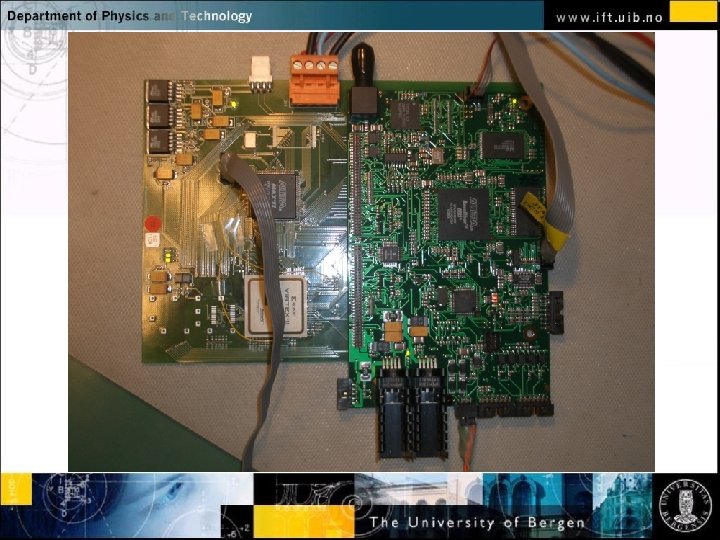

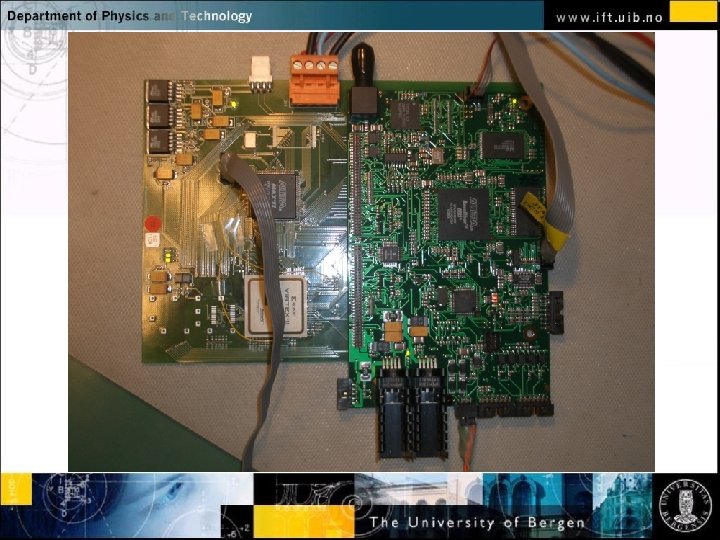

RCU testcard • A test card (RCU 3. 5 ) was designed to speed up testing Normal textscheme. - click to edit of the new configuration • It is populated with a Xilinx Virtex-II, an Altera Max-II CPLD and a Motorola Flash memory. • An optical transceiver is also provided in order to test the Rocket. IO feature of the Virtex-II 5

Normal text - click to edit

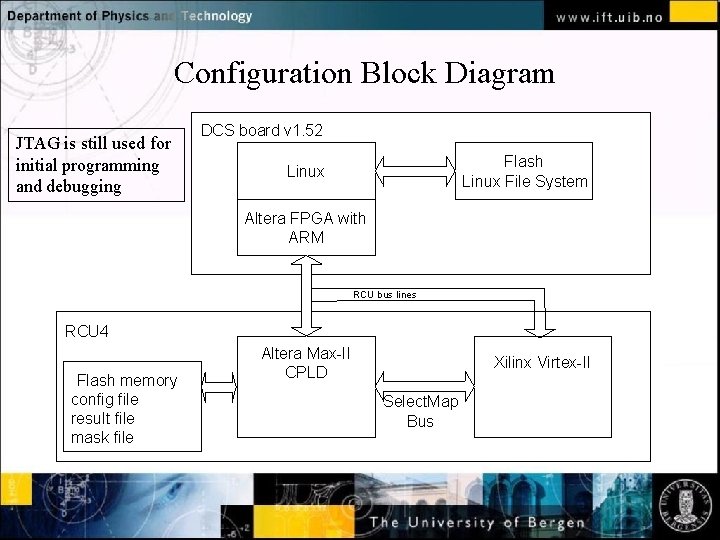

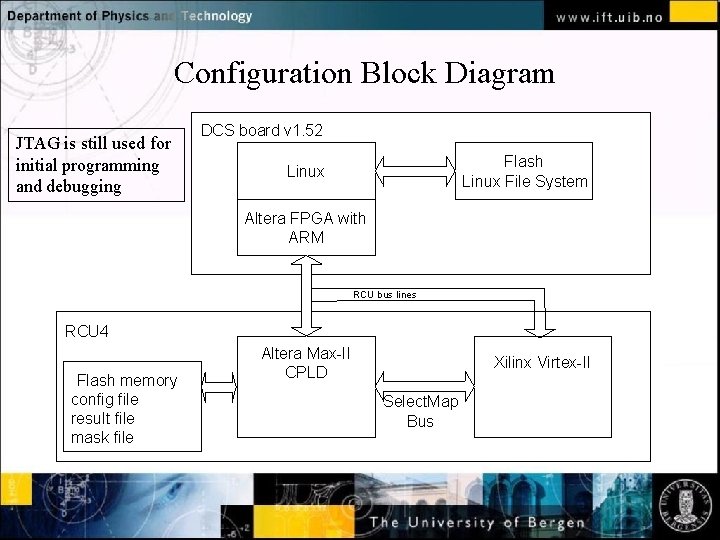

Configuration Block Diagram JTAG is still used for initial programming and debugging DCS board v 1. 52 Normal text - click to edit Flash Linux File System Linux Altera FPGA with ARM RCU bus lines RCU 4 Flash memory config file result file mask file Altera Max-II CPLD Xilinx Virtex-II Select. Map Bus

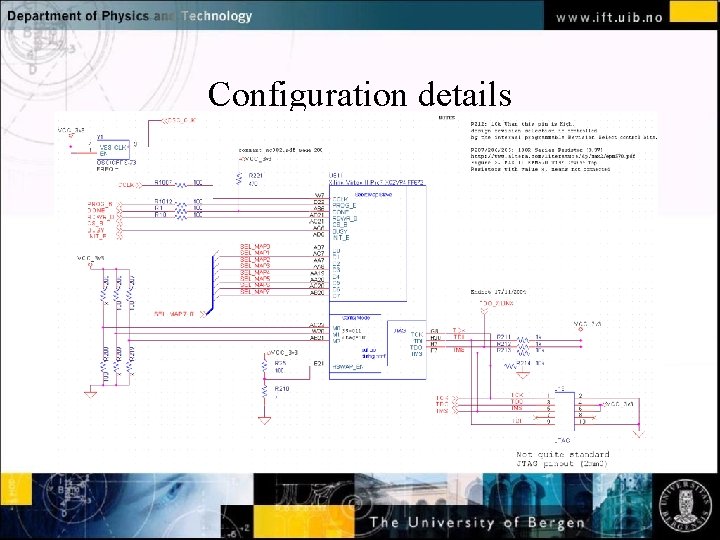

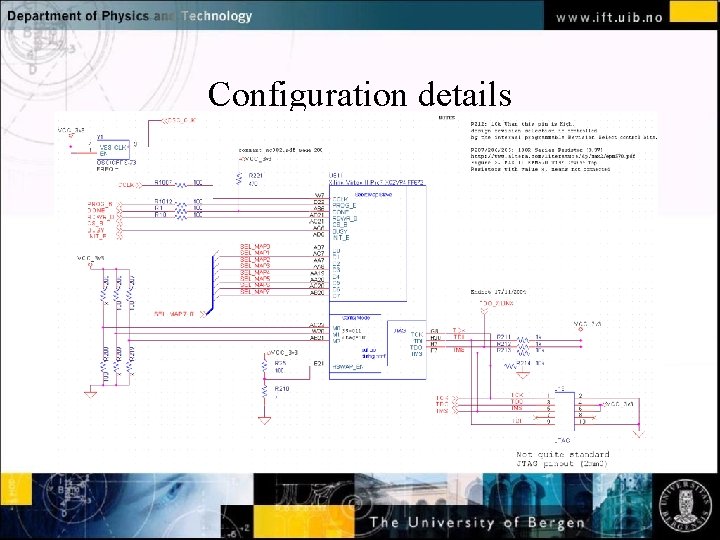

Configuration details Normal text - click to edit

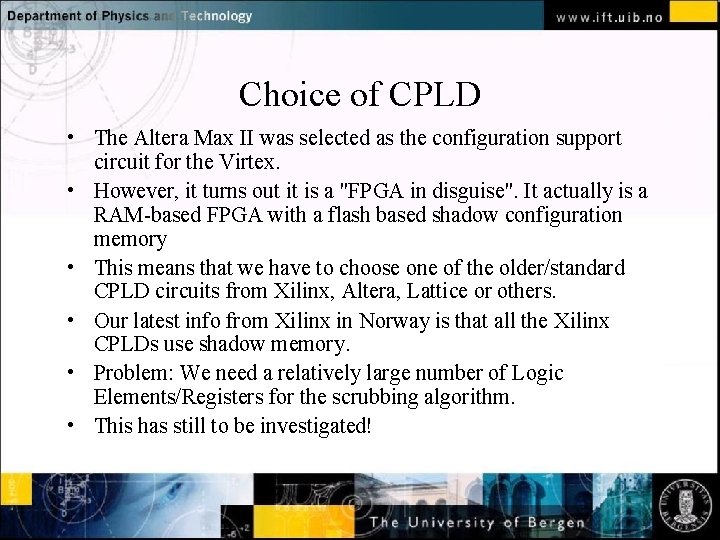

Choice of CPLD • The Altera Max II was selected as the configuration support circuit for the Virtex. • However, it turns out it is a "FPGA in disguise". It actually is a RAM-based FPGA with a flash based shadow configuration memory • This means that we have to choose one of the older/standard CPLD circuits from Xilinx, Altera, Lattice or others. • Our latest info from Xilinx in Norway is that all the Xilinx CPLDs use shadow memory. • Problem: We need a relatively large number of Logic Elements/Registers for the scrubbing algorithm. • This has still to be investigated! Normal text - click to edit

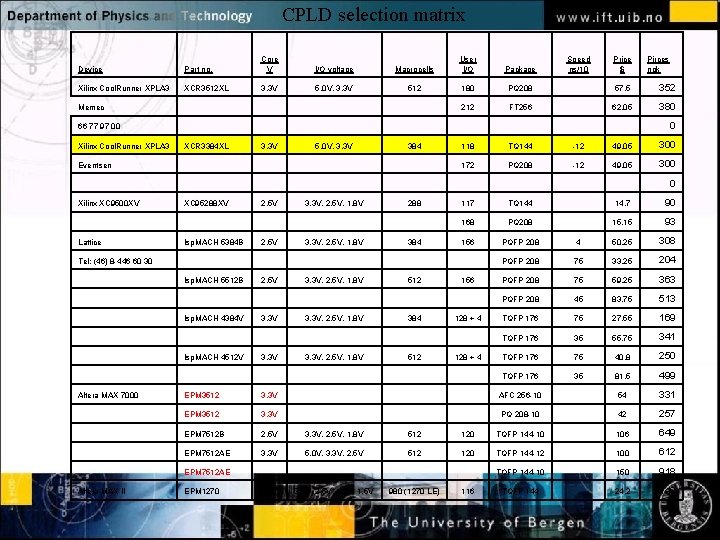

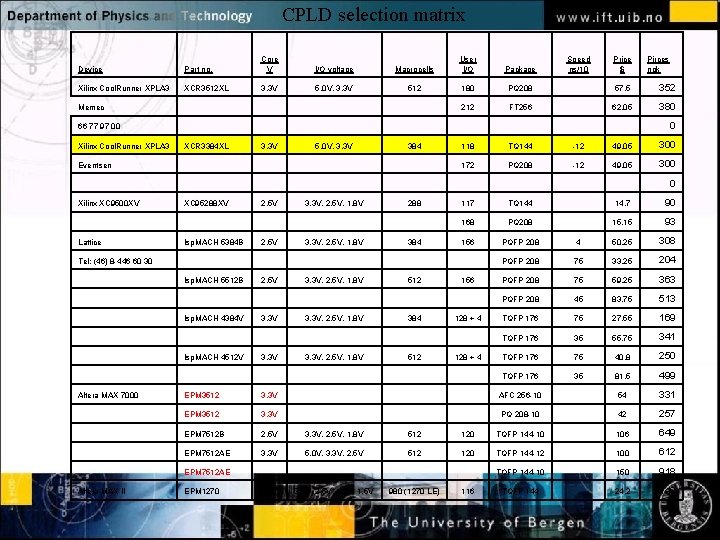

CPLD selection matrix Device Part no. Core V I/O voltage Macrocells User I/O Package Speed ns/10 Price $ Xilinx Cool. Runner XPLA 3 XCR 3512 XL 3. 3 V 5. 0 V, 3. 3 V 512 180 PQ 208 57. 5 352 Memec 212 FT 256 62. 05 380 66 77 97 00 Xilinx Cool. Runner XPLA 3 XCR 3384 XL 3. 3 V Eventsen 5. 0 V, 3. 3 V 384 118 TQ 144 Normal text - click to edit 172 PQ 208 Pirces nok 0 -12 49. 05 300 0 Xilinx XC 9500 XV XC 95288 XV 2. 5 V 3. 3 V, 2. 5 V, 1. 8 V 288 117 TQ 144 14. 7 90 168 PQ 208 15. 15 93 Lattice Isp. MACH 5384 B 2. 5 V 3. 3 V, 2. 5 V, 1. 8 V 384 156 PQFP 208 4 50. 25 308 Tel: (46) 8 -446 60 30 PQFP 208 75 33. 25 204 Isp. MACH 5512 B 2. 5 V 3. 3 V, 2. 5 V, 1. 8 V 512 156 PQFP 208 75 59. 25 363 PQFP 208 45 83. 75 513 Isp. MACH 4384 V 3. 3 V, 2. 5 V, 1. 8 V 384 128 + 4 TQFP 176 75 27. 55 169 TQFP 176 35 55. 75 341 Isp. MACH 4512 V 3. 3 V, 2. 5 V, 1. 8 V 512 128 + 4 TQFP 176 75 40. 8 250 TQFP 176 35 81. 5 499 Altera MAX 7000 EPM 3512 3, 3 V AFC 256 -10 54 331 EPM 3512 3, 3 V PQ 208 -10 42 257 EPM 7512 B 2. 5 V 3. 3 V, 2. 5 V, 1. 8 V 512 120 TQFP 144 -10 106 649 EPM 7512 AE 3. 3 V 5. 0 V, 3. 3 V, 2. 5 V 512 120 TQFP 144 -12 100 612 EPM 7512 AE TQFP 144 -10 150 918 Altera MAX II EPM 1270 1. 5 V 3. 3 V, 2. 5 V, 1. 8 V, 1. 5 V 980 (1270 LE) 116 TQFP 144 24. 2 148

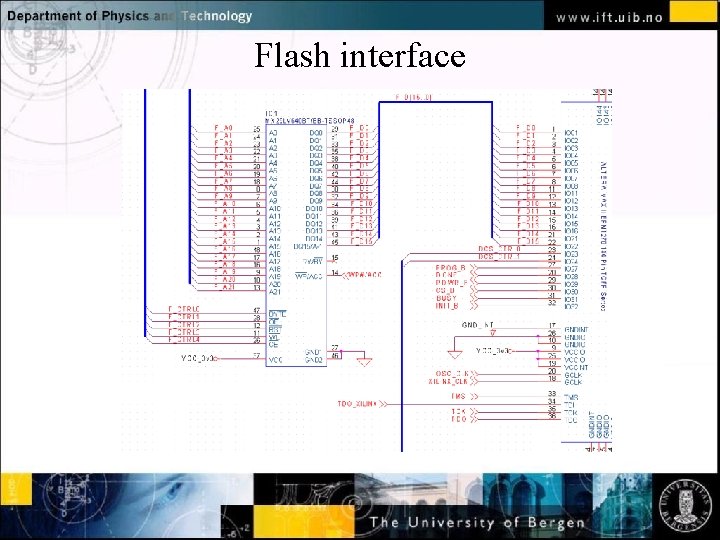

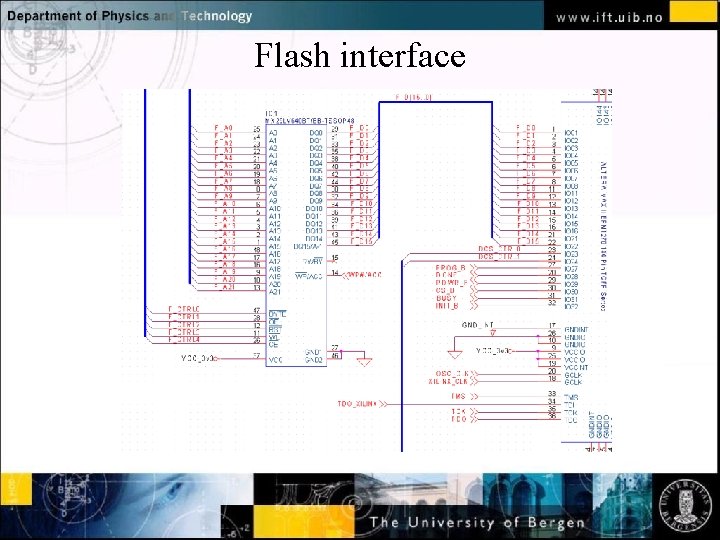

Flash interface Normal text - click to edit

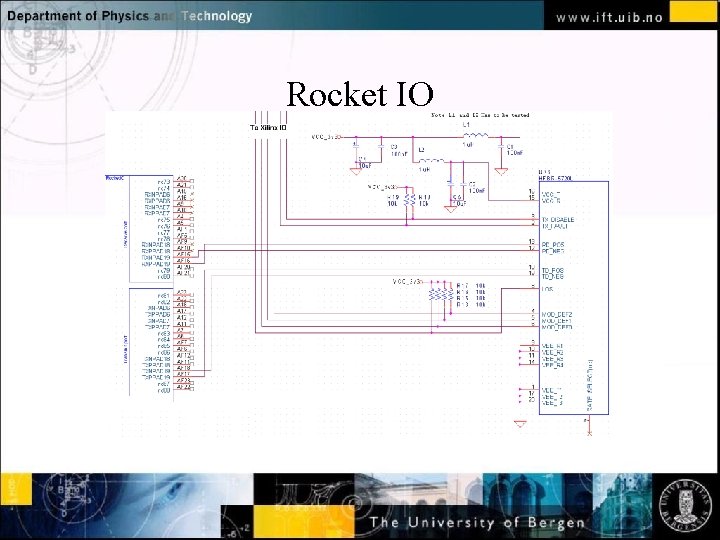

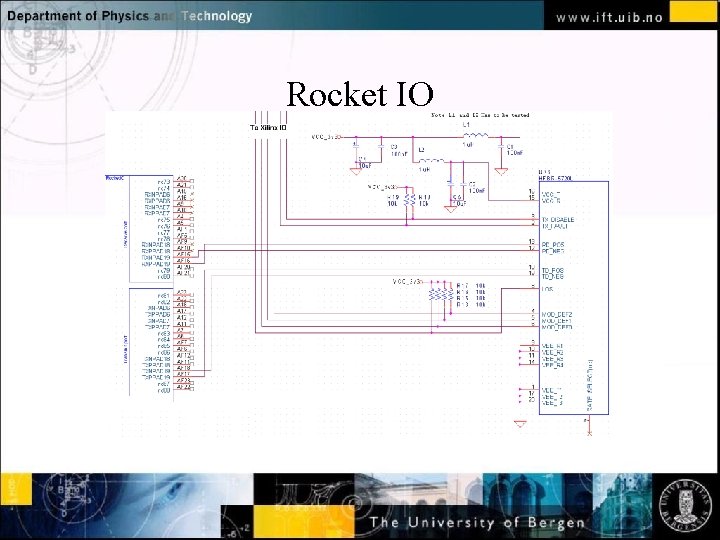

Rocket IO Normal text - click to edit

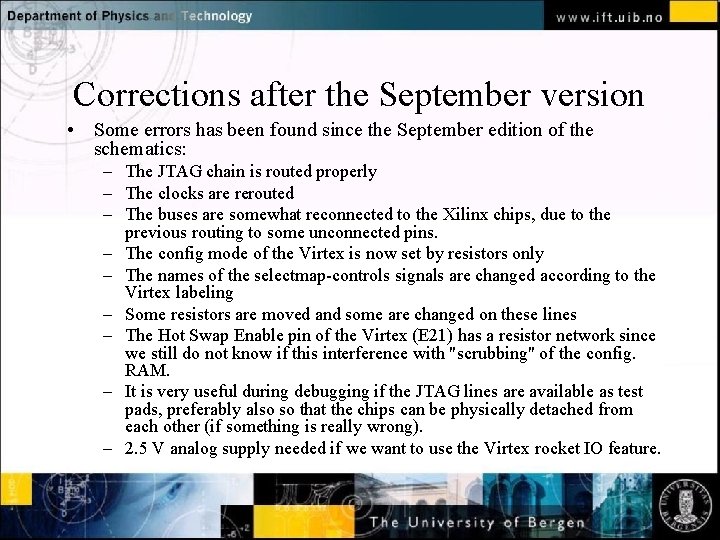

Corrections after the September version • Some errors has been found since the September edition of the schematics: Normal text - click to edit – The JTAG chain is routed properly – The clocks are rerouted – The buses are somewhat reconnected to the Xilinx chips, due to the previous routing to some unconnected pins. – The config mode of the Virtex is now set by resistors only – The names of the selectmap-controls signals are changed according to the Virtex labeling – Some resistors are moved and some are changed on these lines – The Hot Swap Enable pin of the Virtex (E 21) has a resistor network since we still do not know if this interference with "scrubbing" of the config. RAM. – It is very useful during debugging if the JTAG lines are available as test pads, preferably also so that the chips can be physically detached from each other (if something is really wrong). – 2. 5 V analog supply needed if we want to use the Virtex rocket IO feature.