IEEE Floating Point Adder Verification Using the IEEE

- Slides: 16

IEEE Floating Point Adder Verification Using the IEEE Floating Point Standard for an add/subtract execution units 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 1

Lecture overview o o The Interface Part by part A floating point adder design Verifying the design 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 2

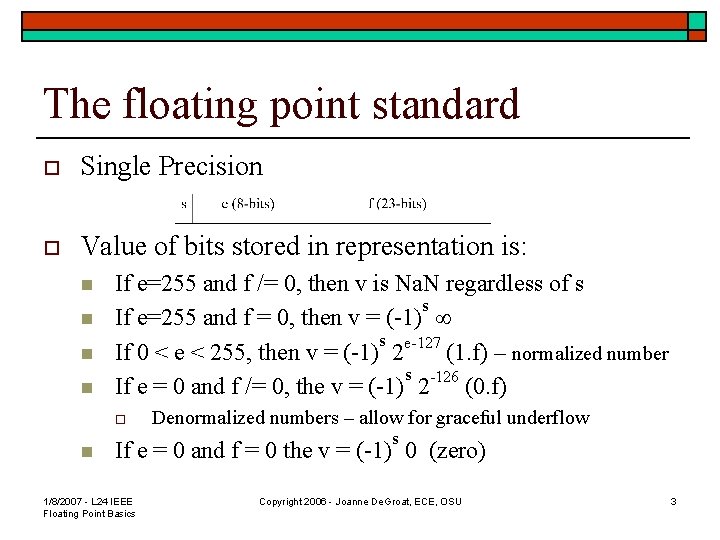

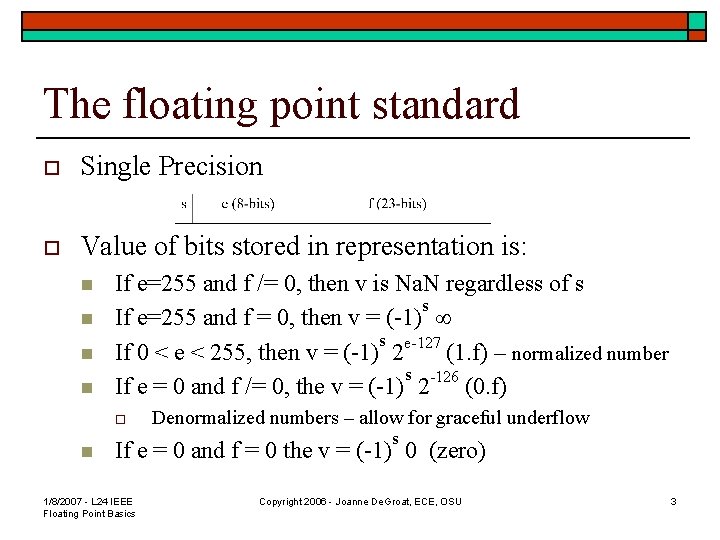

The floating point standard o Single Precision o Value of bits stored in representation is: n n If e=255 and f /= 0, then v is Na. N regardless of s s If e=255 and f = 0, then v = (-1) ¥ s If 0 < e < 255, then v = (-1) 2 e-127 (1. f) – normalized number s If e = 0 and f /= 0, the v = (-1) 2 -126 (0. f) o n Denormalized numbers – allow for graceful underflow s If e = 0 and f = 0 the v = (-1) 0 (zero) 1/8/2007 - L 24 IEEE Floating Point Basics Copyright 2006 - Joanne De. Groat, ECE, OSU 3

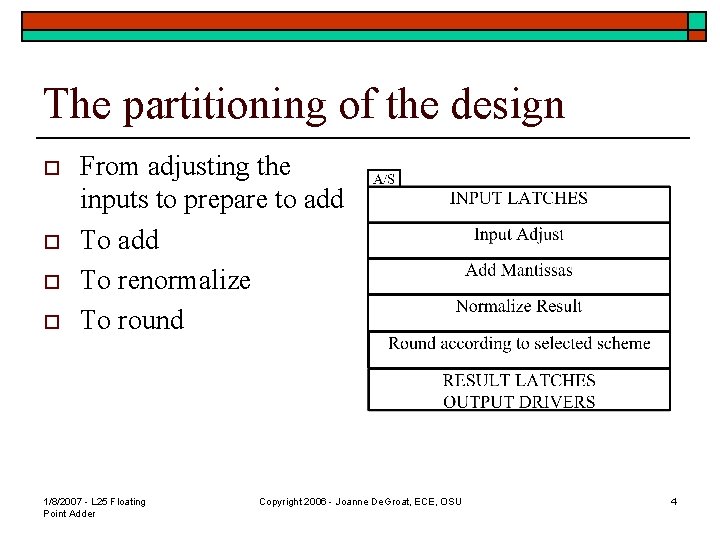

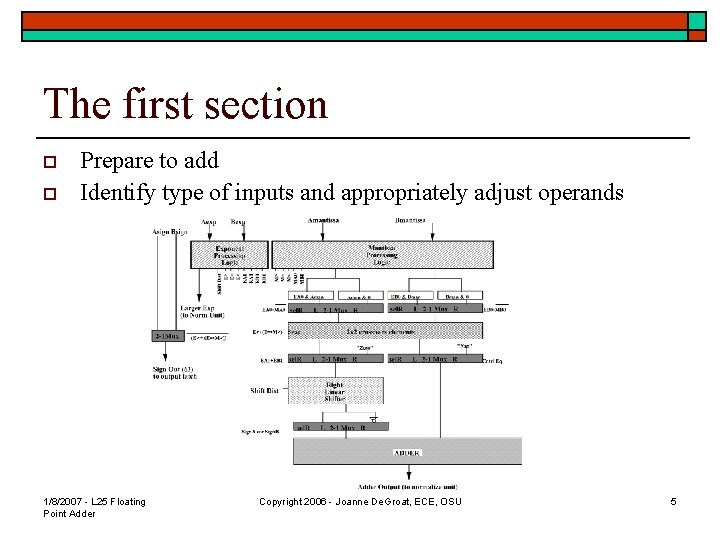

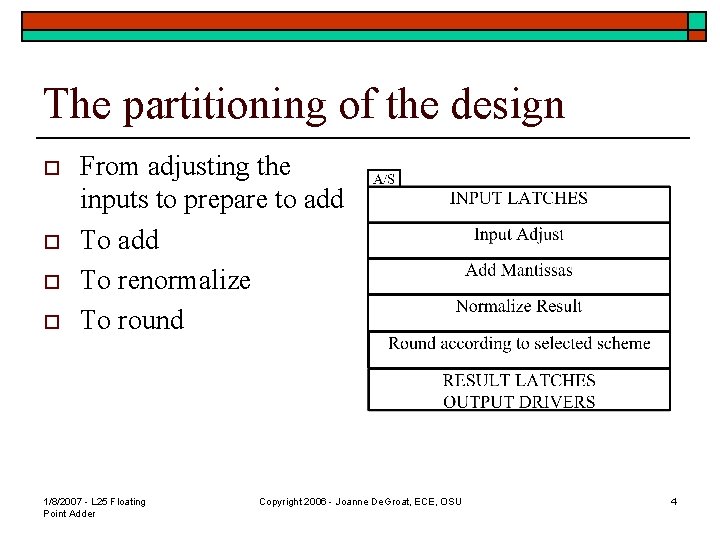

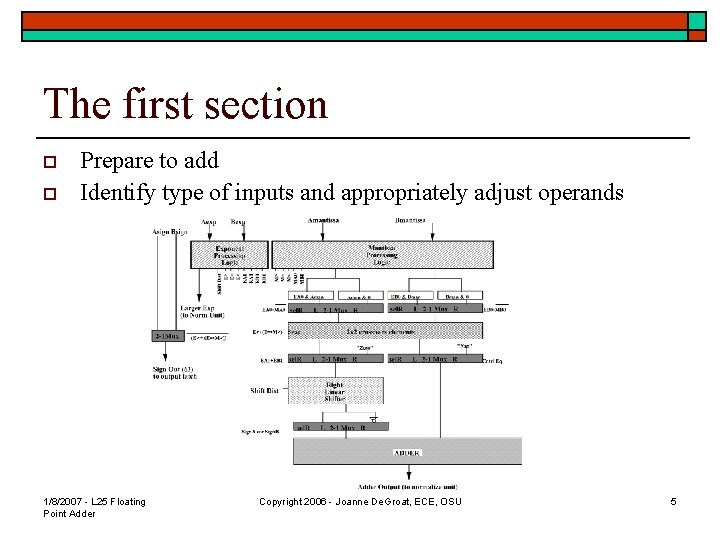

The partitioning of the design o o From adjusting the inputs to prepare to add To renormalize To round 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 4

The first section o o Prepare to add Identify type of inputs and appropriately adjust operands 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 5

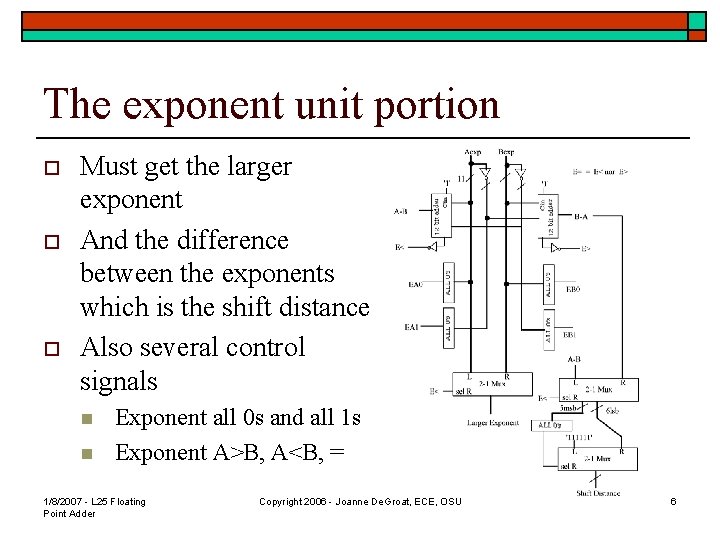

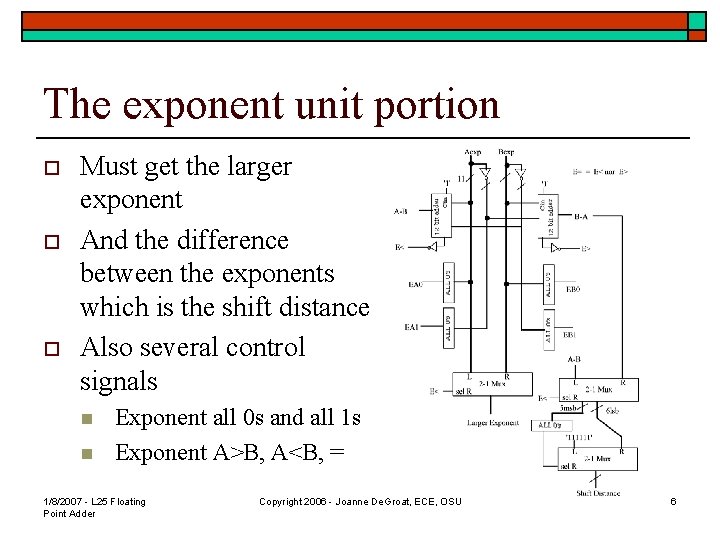

The exponent unit portion o o o Must get the larger exponent And the difference between the exponents which is the shift distance Also several control signals n n Exponent all 0 s and all 1 s Exponent A>B, A<B, = 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 6

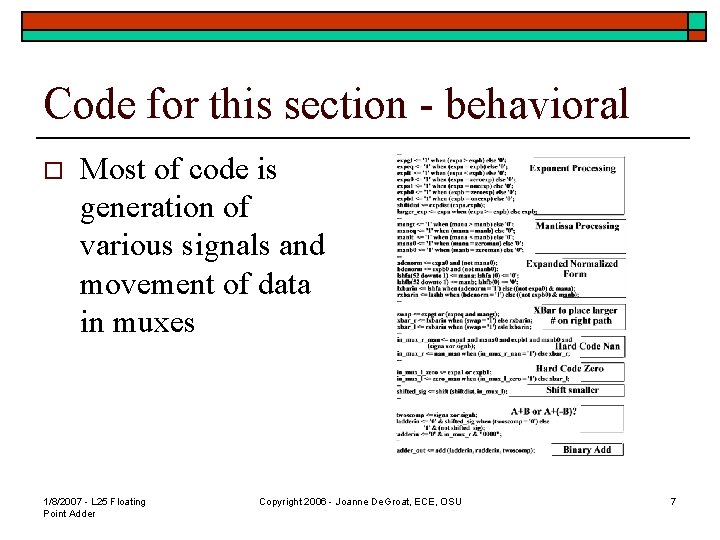

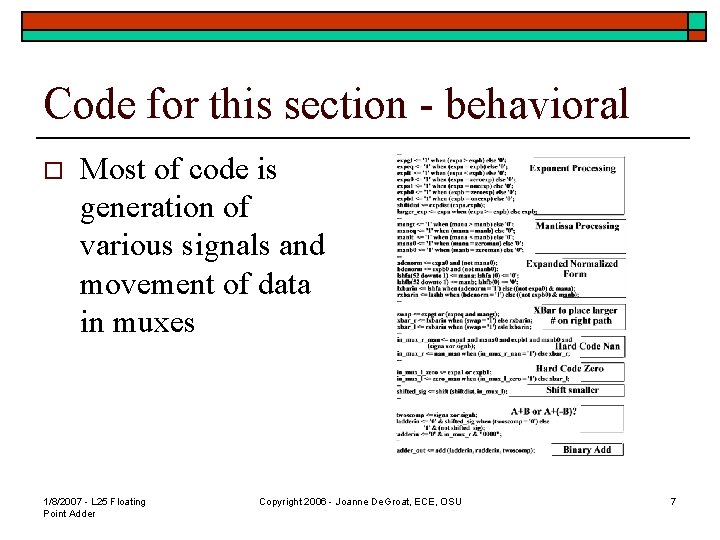

Code for this section - behavioral o Most of code is generation of various signals and movement of data in muxes 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 7

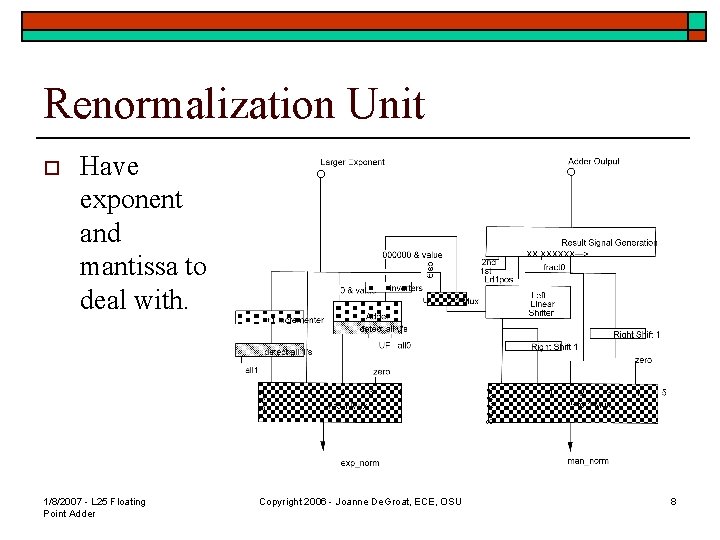

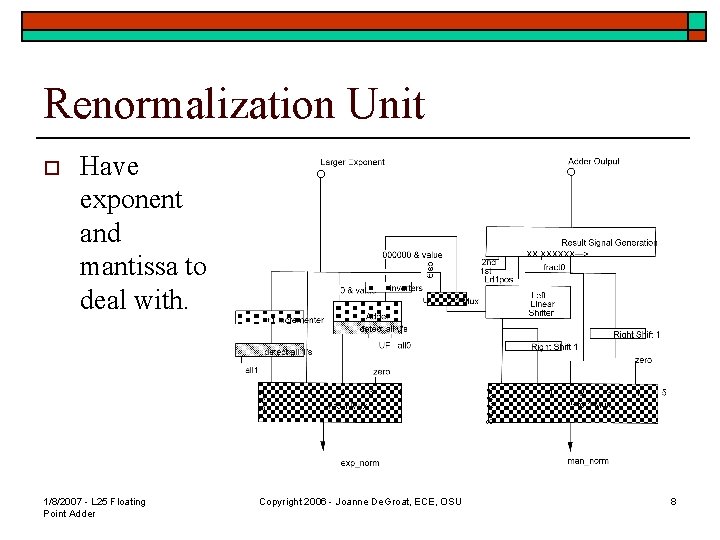

Renormalization Unit o Have exponent and mantissa to deal with. 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 8

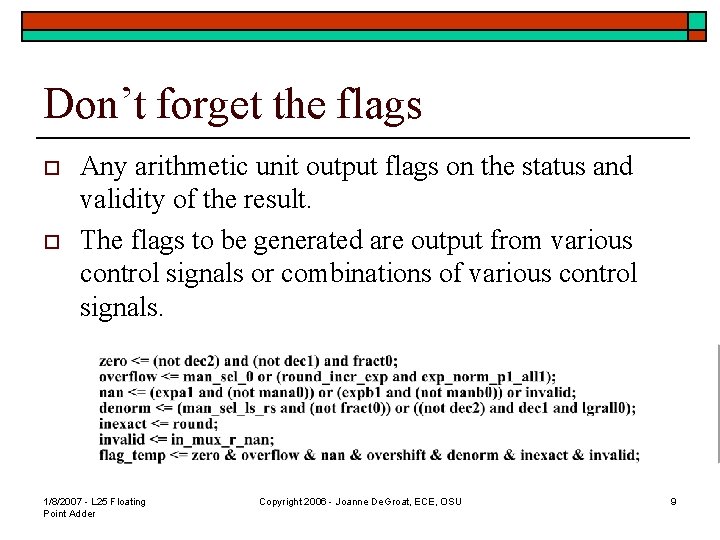

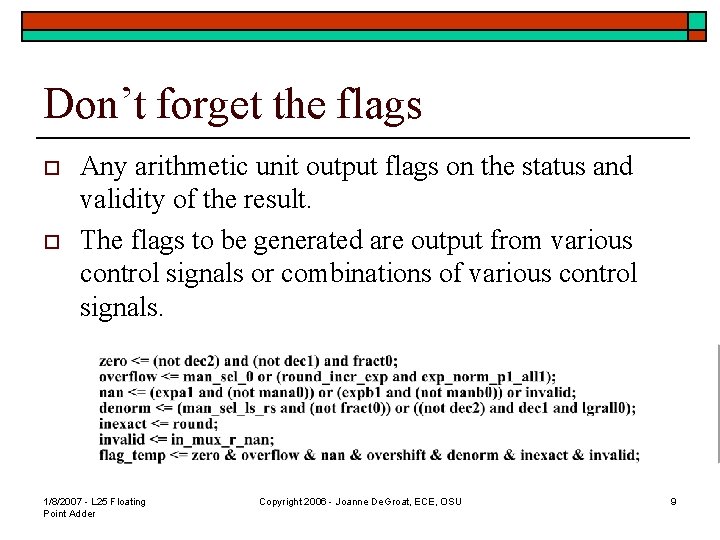

Don’t forget the flags o o Any arithmetic unit output flags on the status and validity of the result. The flags to be generated are output from various control signals or combinations of various control signals. 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 9

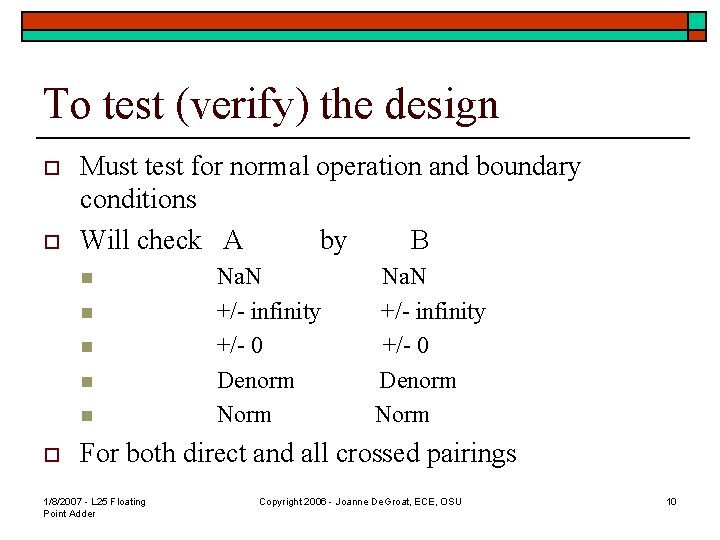

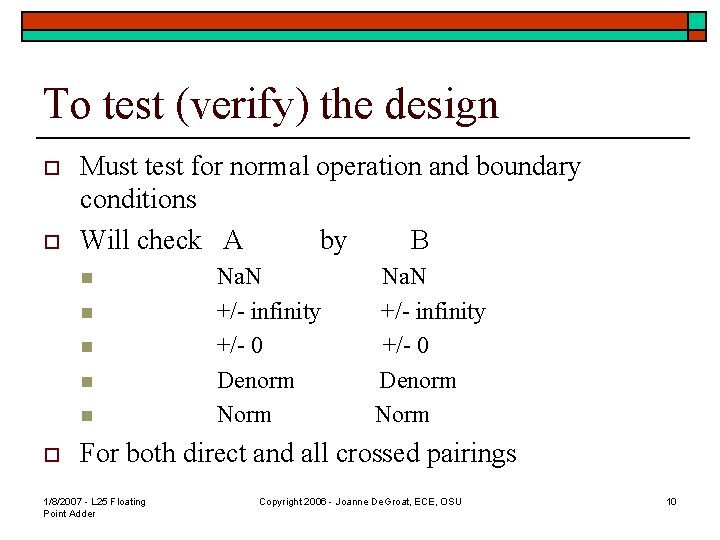

To test (verify) the design o o Must test for normal operation and boundary conditions Will check A by B n n n o Na. N +/- infinity +/- 0 Denorm Norm For both direct and all crossed pairings 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 10

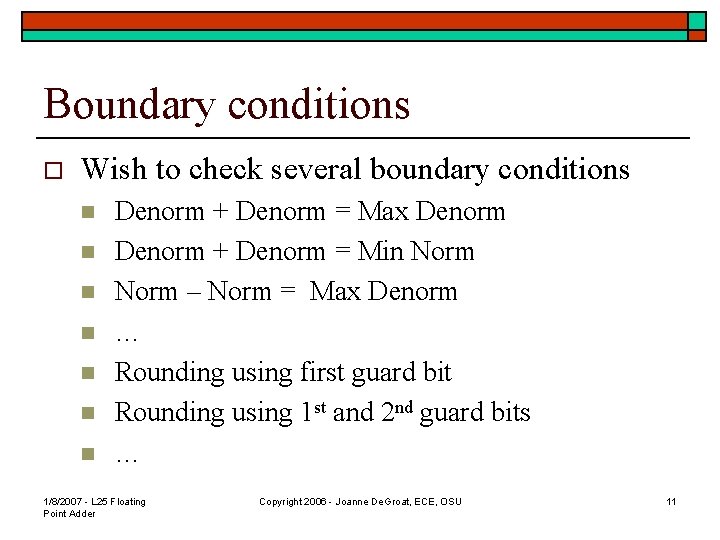

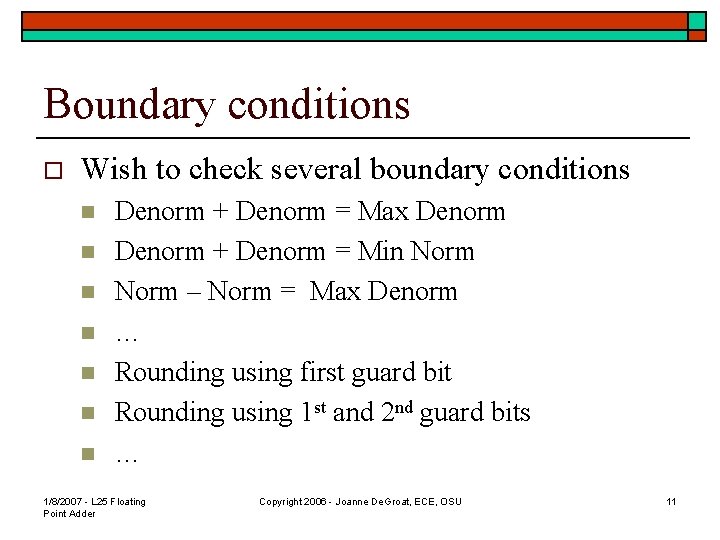

Boundary conditions o Wish to check several boundary conditions n n n n Denorm + Denorm = Max Denorm + Denorm = Min Norm – Norm = Max Denorm … Rounding using first guard bit Rounding using 1 st and 2 nd guard bits … 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 11

Testing o o Testing of the design code is not necessarily the same as the testing the would be done on the chip. The “testing” of the design is call verification and must insure that all possible input combinations produce the specified output. 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 12

Scan of entire architecture 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 13

Scan of the chip 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 14

So what goes into the test plan o o Test plan lays out what is to be verified Test plan outlines the test application methodology to be used. n n o o Outlines how the testbench will get the tests and apply them to the unit. Outlines how the results will be checked – this unit has complexity levels that visual check is not adequate. Test plan also details the vector test set to be applied. Provides rational as the level of functional coverage that this test set will provide. Clearly defines what is “success”. So you know when you are done!! 1/8/2007 - L 2 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 15

And then a final verification report o Details of implementation of the verification plan. n n What vectors were applied. Test that failed Detail of issues in the DUT that require fixing Details on how the test vectors were generated. o 1/8/2007 - L 2 Floating Point Adder Many be in programs other than HDL. Copyright 2006 - Joanne De. Groat, ECE, OSU 16