ICSFORTH Data Synchronization Issues in GALS So Cs

- Slides: 22

ICSFORTH Data Synchronization Issues in GALS So. Cs Rostislav (Reuven) Dobkin and Ran Ginosar Technion Christos P. Sotiriou FORTH

Outline • The Problem o Synchronization Failures in GALS So. Cs • Three solutions: o Timing verification o Synchronizers o Locally-delayed clocks • Analysis ICSFORTH 2

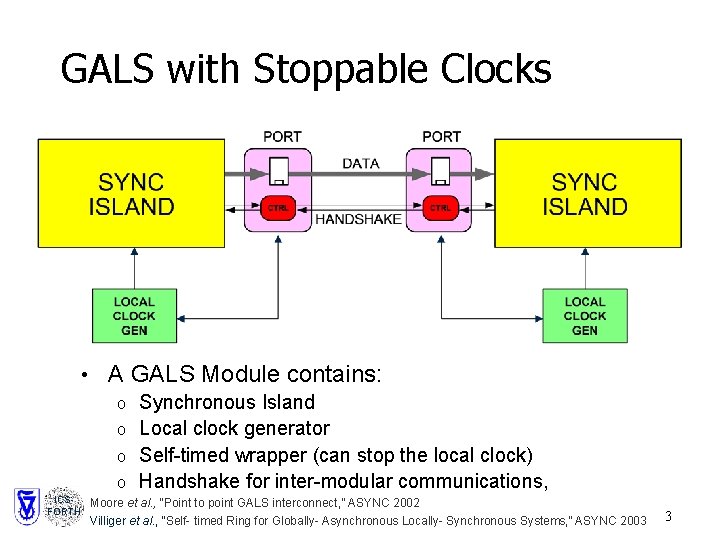

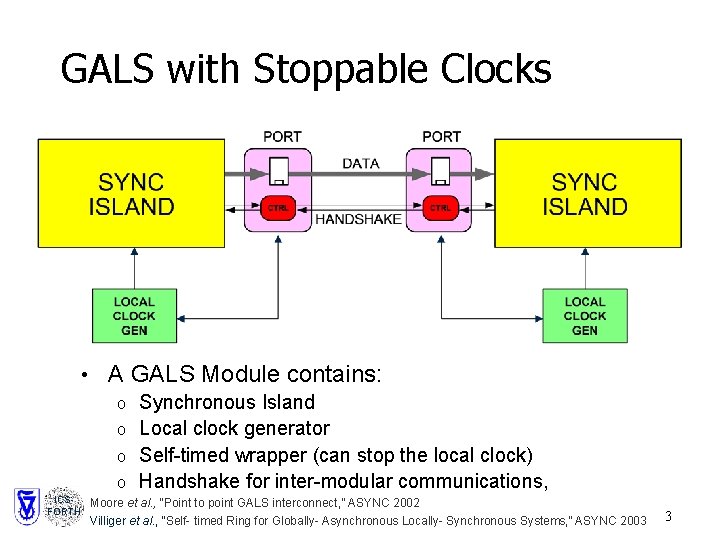

GALS with Stoppable Clocks • A GALS Module contains: o Synchronous Island o Local clock generator o Self-timed wrapper (can stop the local clock) o Handshake for inter-modular communications, ICSFORTH Moore et al. , “Point to point GALS interconnect, ” ASYNC 2002 Villiger et al. , “Self- timed Ring for Globally- Asynchronous Locally- Synchronous Systems, ” ASYNC 2003 3

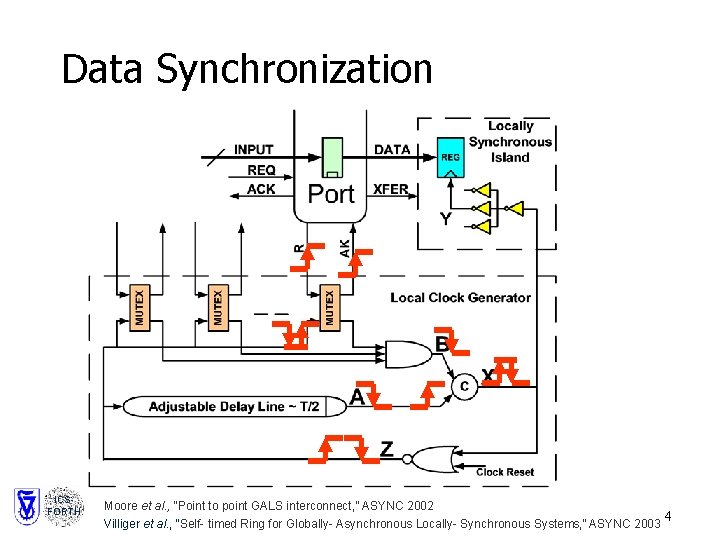

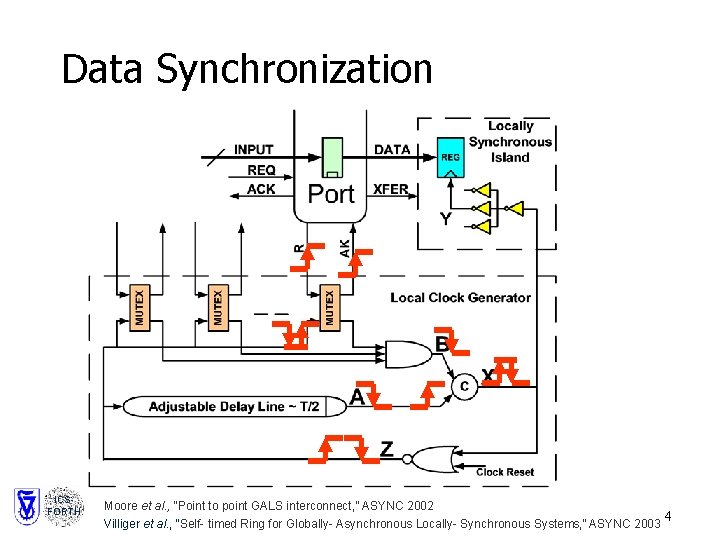

Data Synchronization ICSFORTH Moore et al. , “Point to point GALS interconnect, ” ASYNC 2002 4 Villiger et al. , “Self- timed Ring for Globally- Asynchronous Locally- Synchronous Systems, ” ASYNC 2003

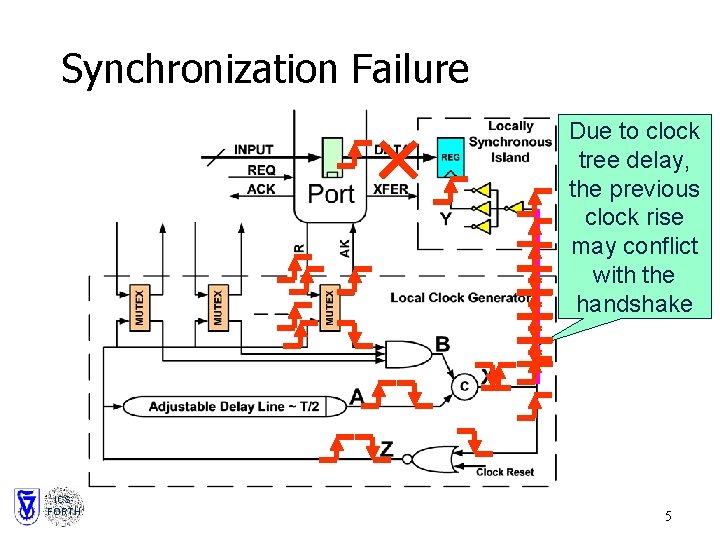

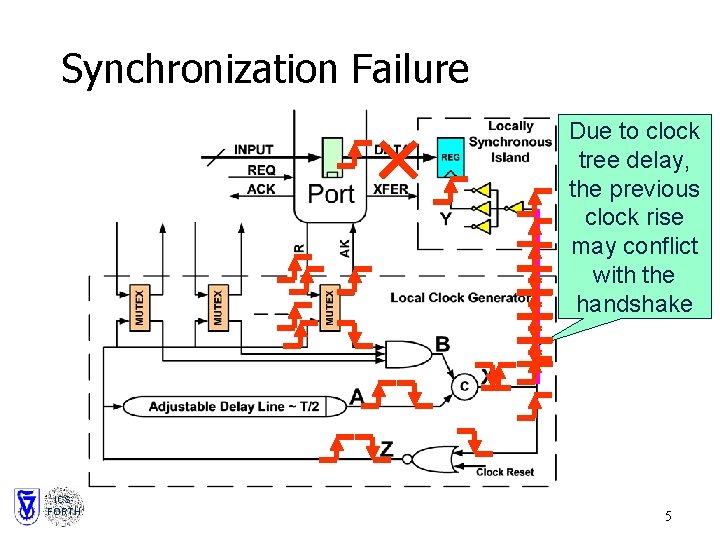

Synchronization Failure Due to clock tree delay, the previous clock rise may conflict with the handshake ICSFORTH 5

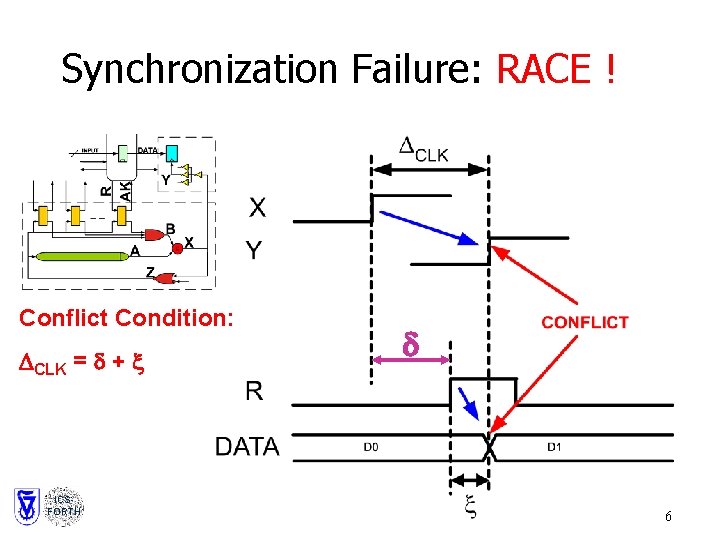

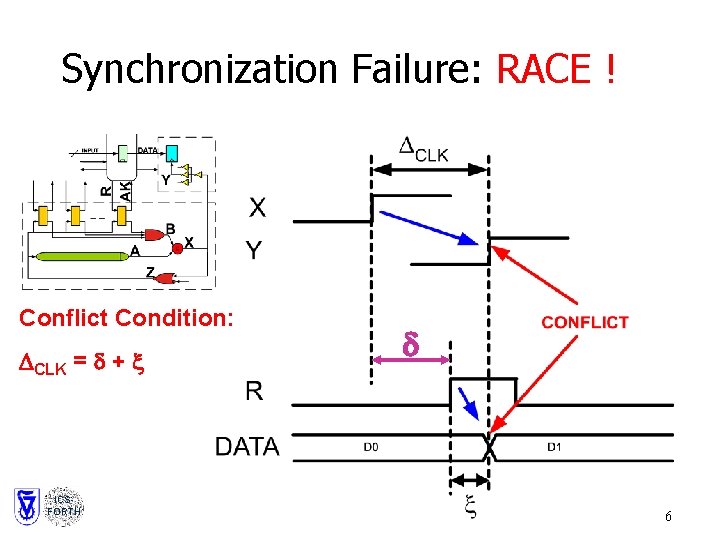

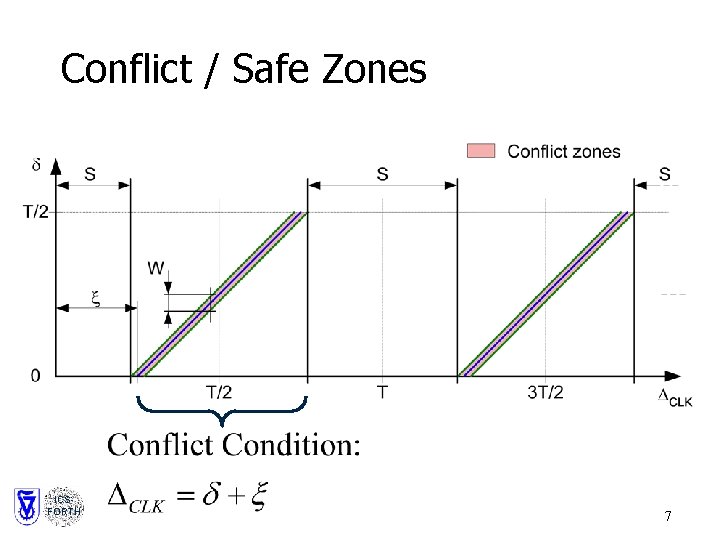

Synchronization Failure: RACE ! Conflict Condition: DCLK = d + x ICSFORTH d 6

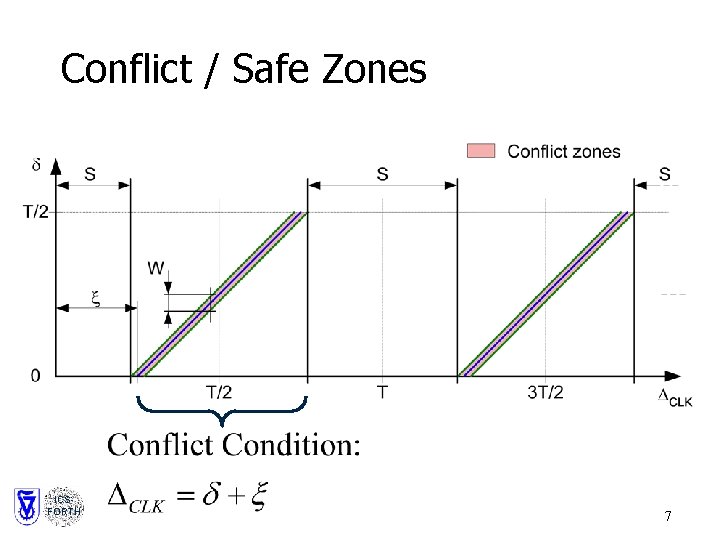

Conflict / Safe Zones ICSFORTH 7

Three Solutions

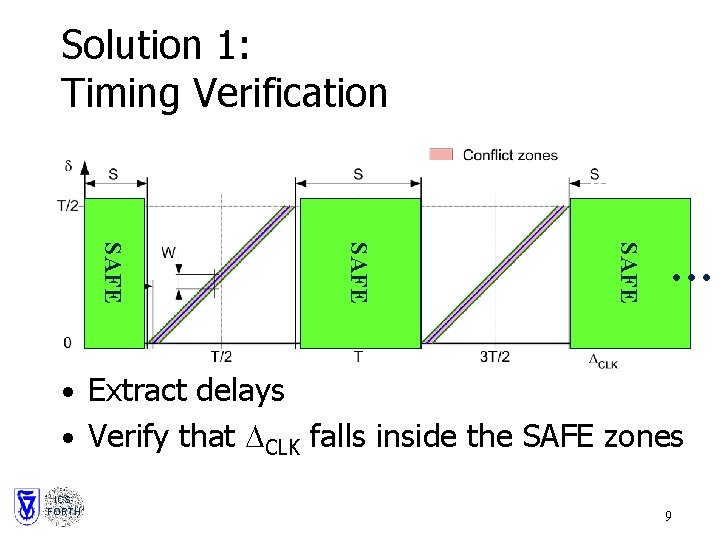

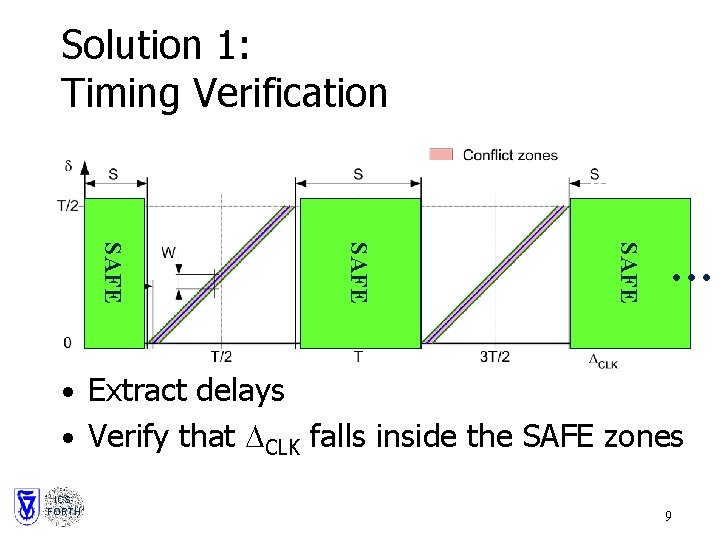

Solution 1: Timing Verification SAFE … • Extract delays • Verify that DCLK falls inside the SAFE zones ICSFORTH 9

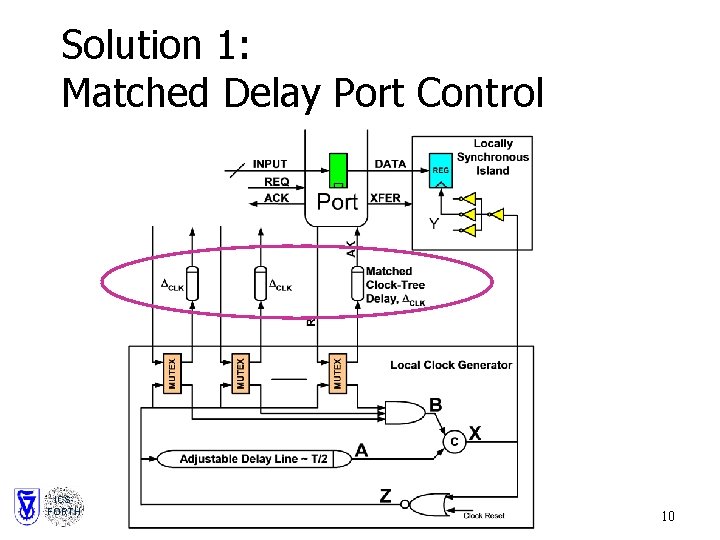

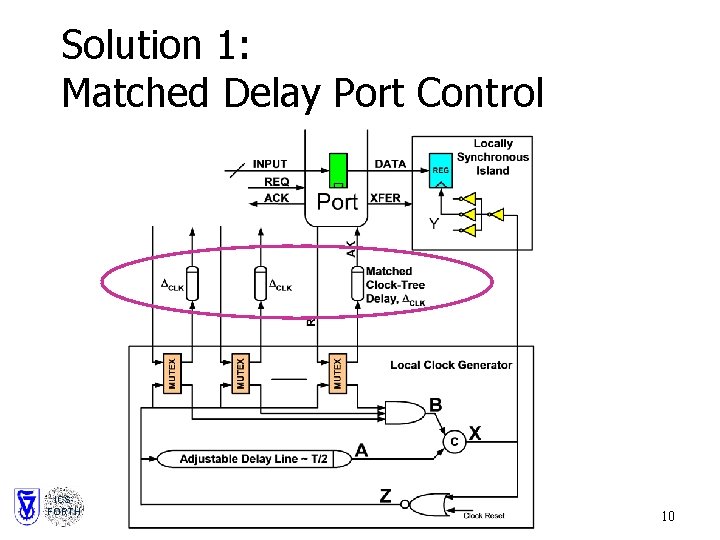

Solution 1: Matched Delay Port Control ICSFORTH 10

Solution 1: Disadvantages • Clock tree delays must be re-verified after each layout iteration • The solution is sensitive to thermal and voltage variations ICSFORTH 11

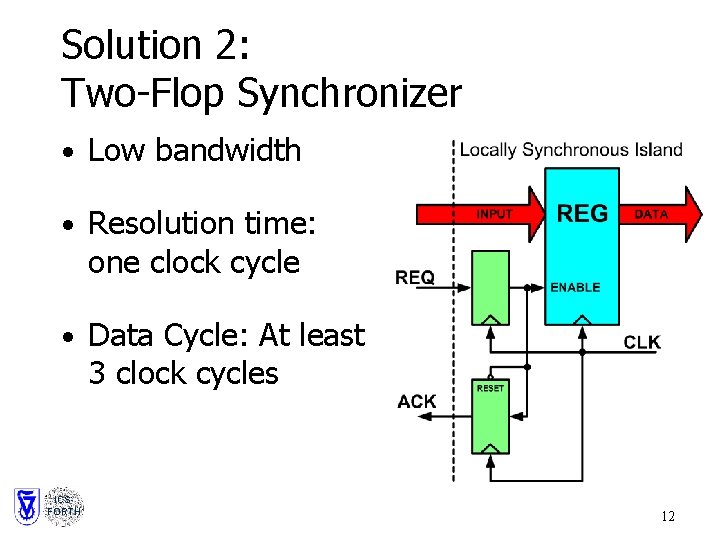

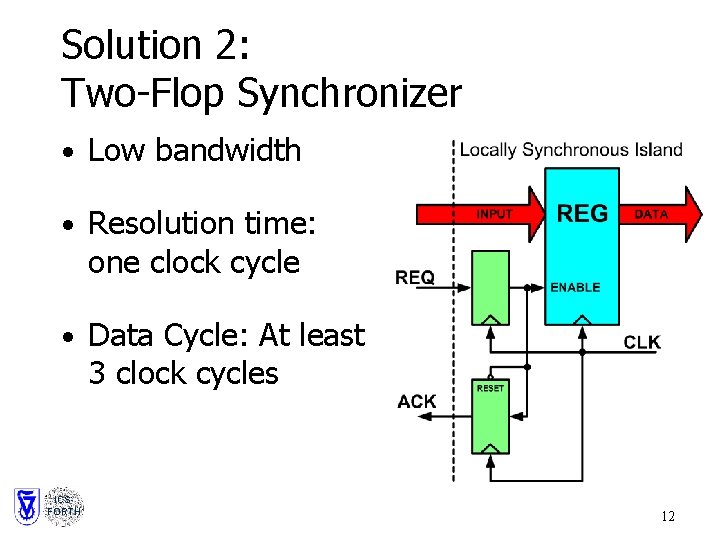

Solution 2: Two-Flop Synchronizer • Low bandwidth • Resolution time: one clock cycle • Data Cycle: At least 3 clock cycles ICSFORTH 12

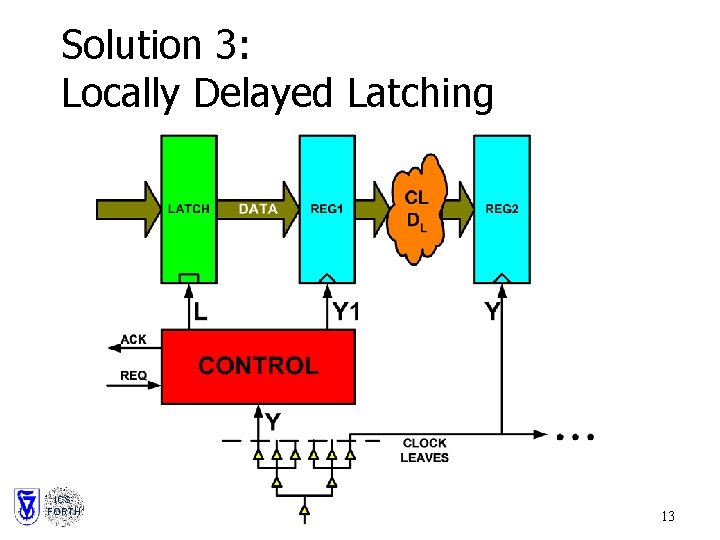

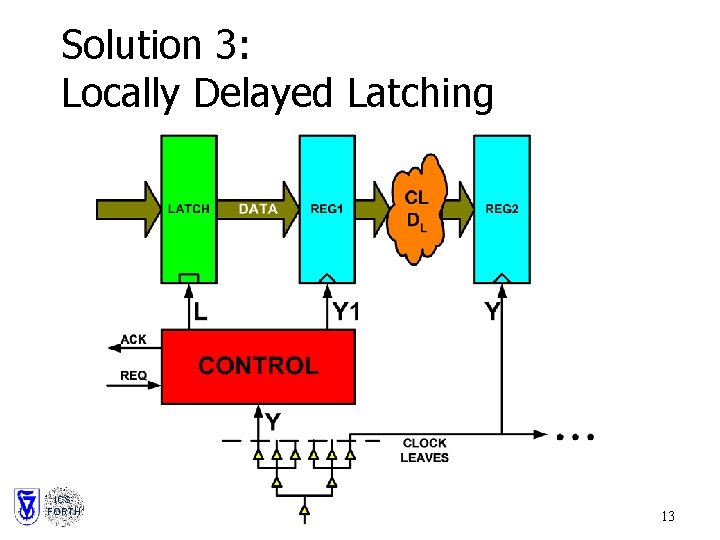

Solution 3: Locally Delayed Latching ICSFORTH 13

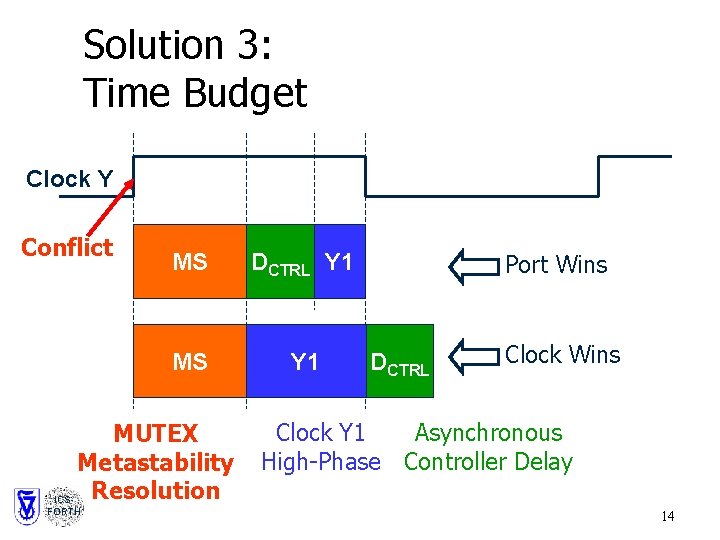

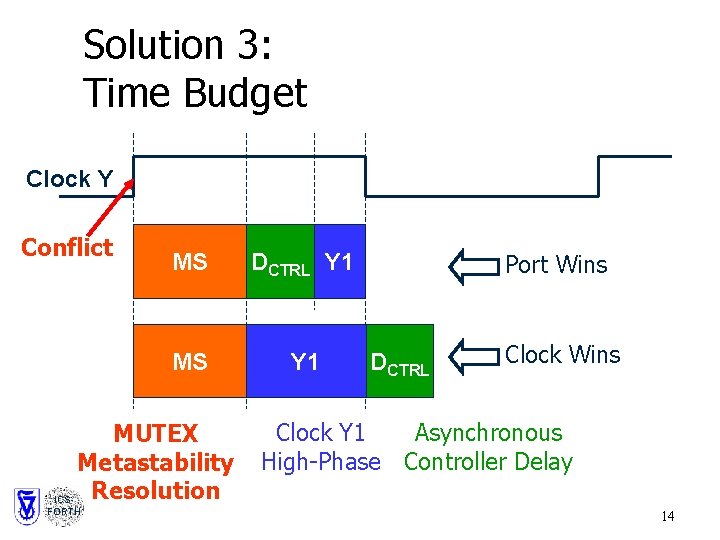

Solution 3: Time Budget Clock Y Conflict MS DCTRL Y 1 MS Y 1 MUTEX Metastability Resolution ICSFORTH Port Wins DCTRL Clock Wins Asynchronous Clock Y 1 High-Phase Controller Delay 14

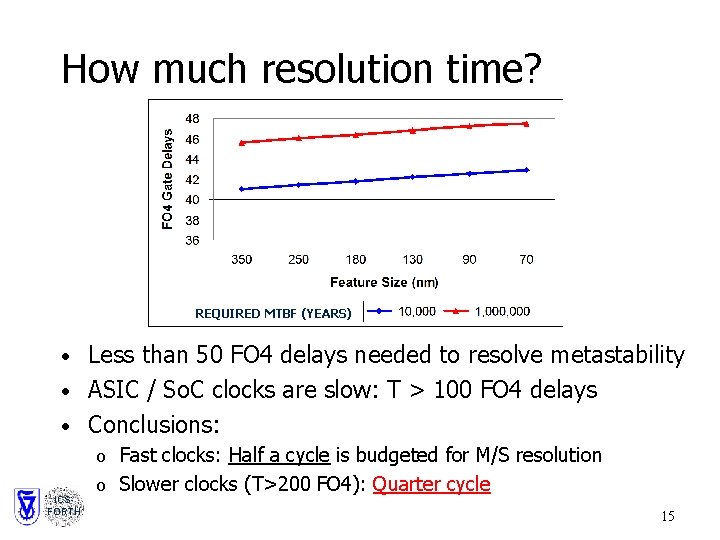

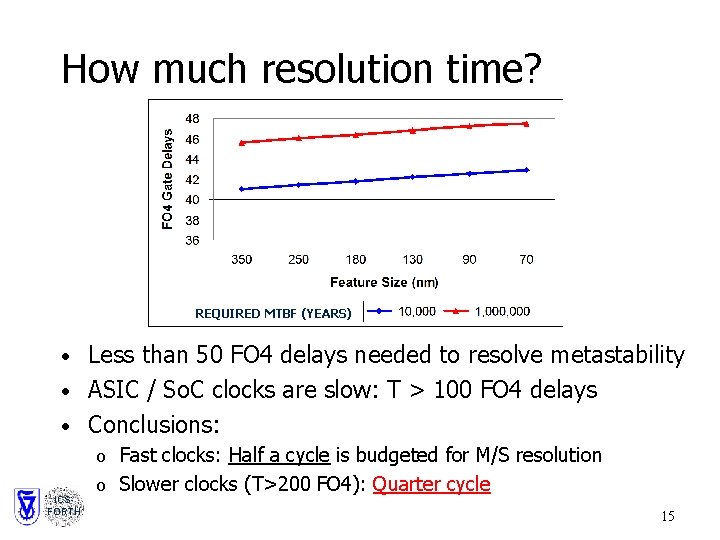

How much resolution time? REQUIRED MTBF (YEARS) • Less than 50 FO 4 delays needed to resolve metastability • ASIC / So. C clocks are slow: T > 100 FO 4 delays • Conclusions: o Fast clocks: Half a cycle is budgeted for M/S resolution o Slower clocks (T>200 FO 4): Quarter cycle ICSFORTH 15

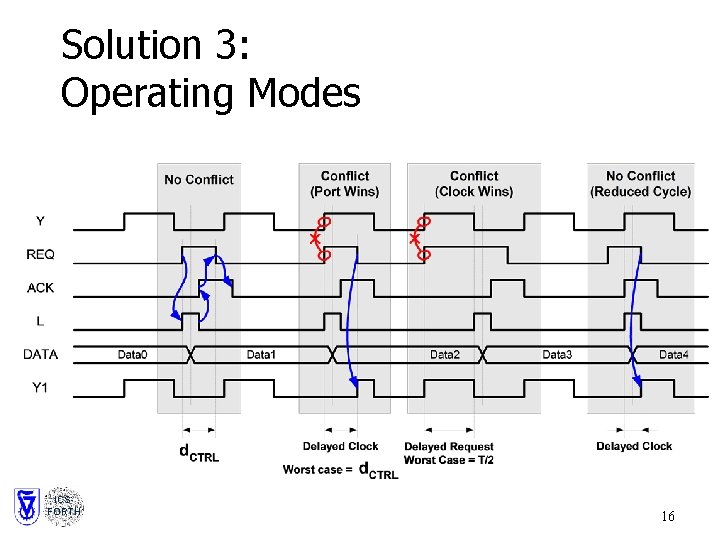

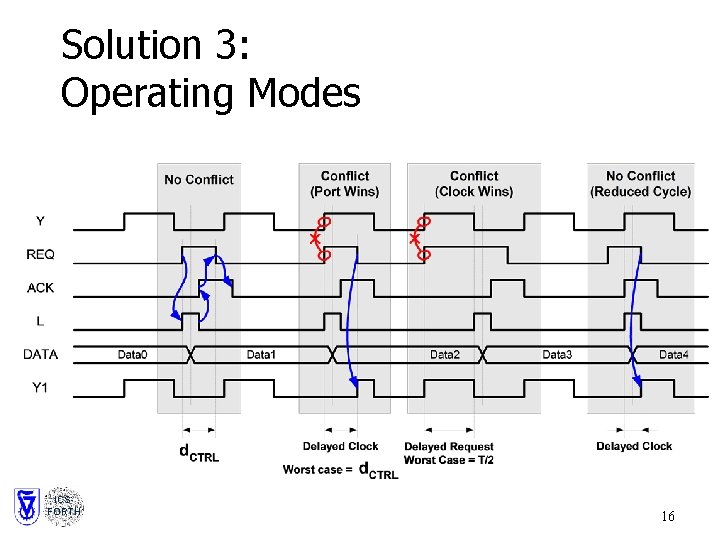

Solution 3: Operating Modes ICSFORTH 16

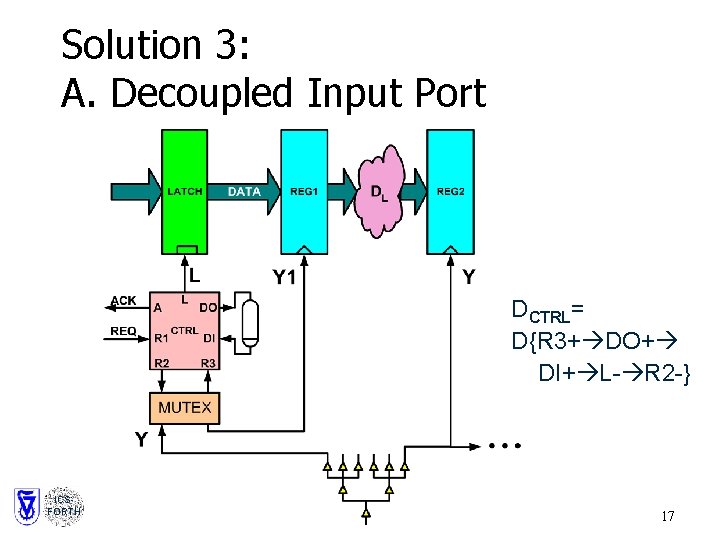

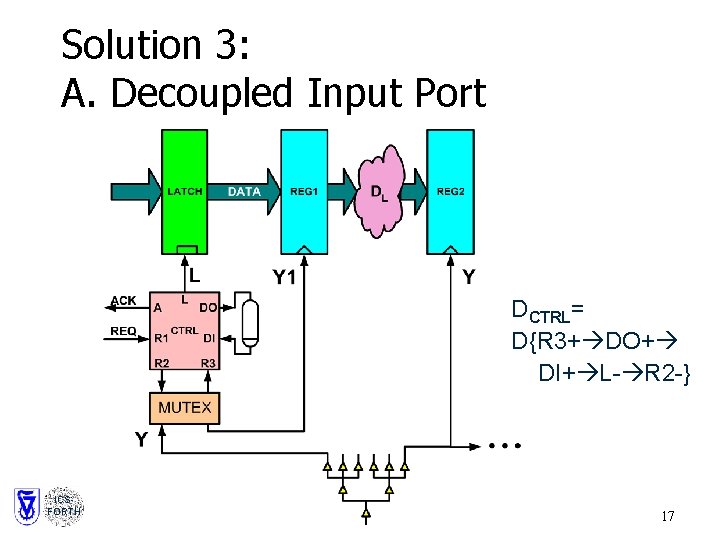

Solution 3: A. Decoupled Input Port DCTRL= D{R 3+ DO+ DI+ L- R 2 -} ICSFORTH 17

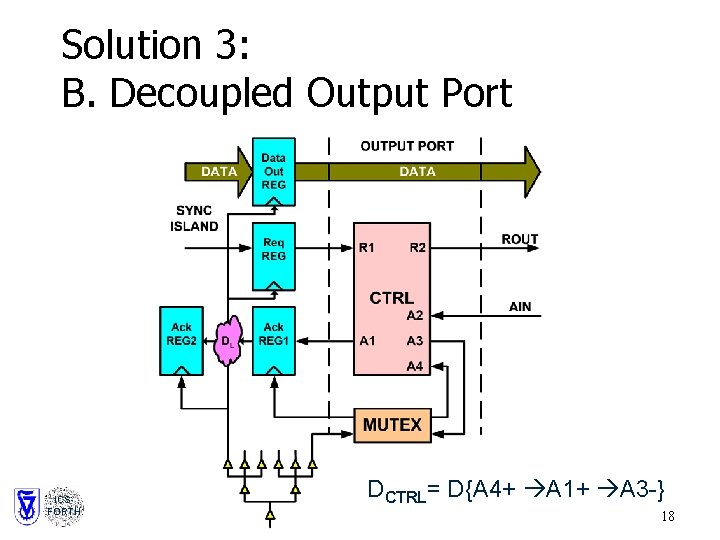

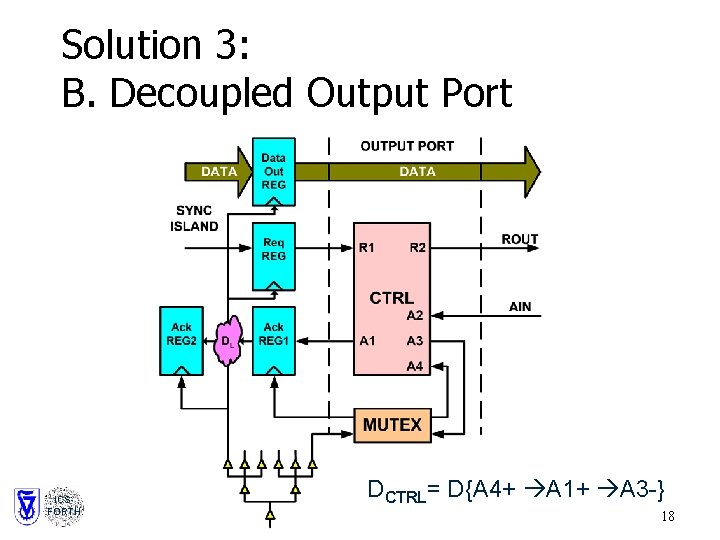

Solution 3: B. Decoupled Output Port ICSFORTH DCTRL= D{A 4+ A 1+ A 3 -} 18

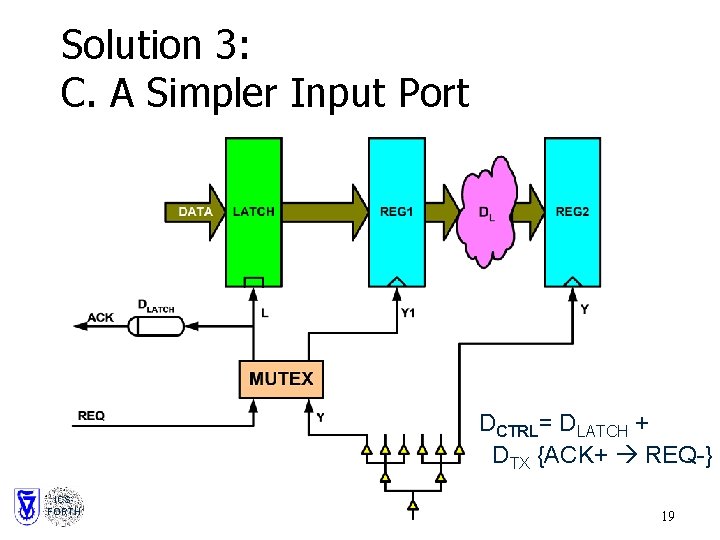

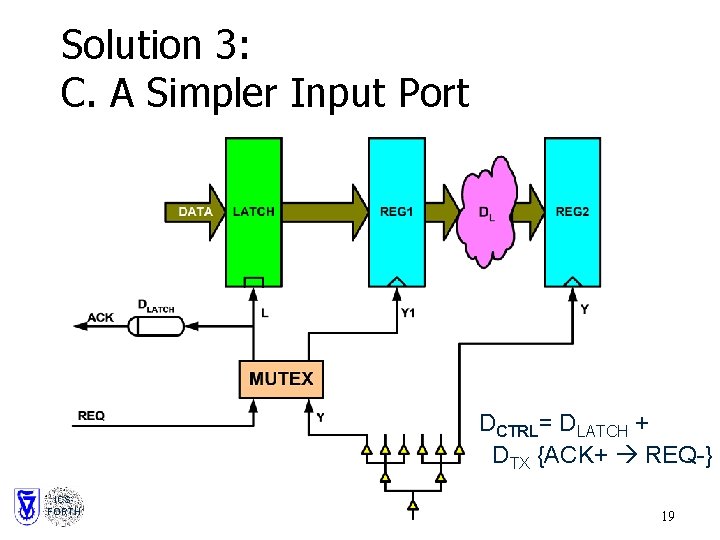

Solution 3: C. A Simpler Input Port DCTRL= DLATCH + DTX {ACK+ REQ-} ICSFORTH 19

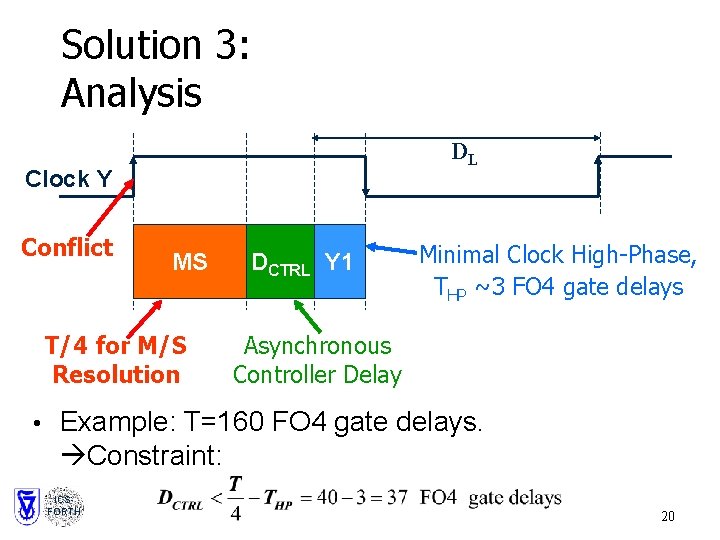

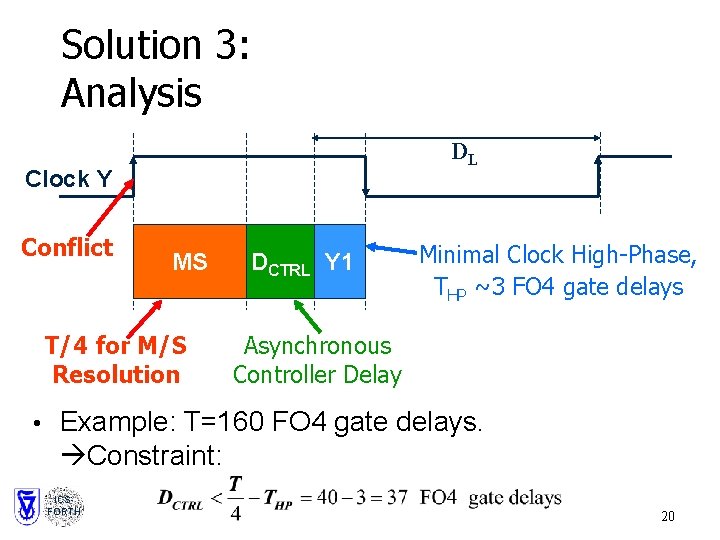

Solution 3: Analysis DL Clock Y Conflict MS T/4 for M/S Resolution DCTRL Y 1 Minimal Clock High-Phase, THP ~3 FO 4 gate delays Asynchronous Controller Delay • Example: T=160 FO 4 gate delays. Constraint: ICSFORTH 20

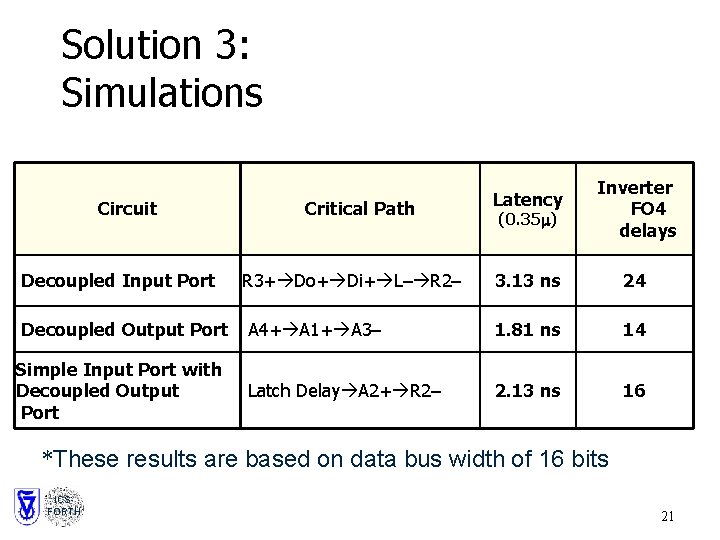

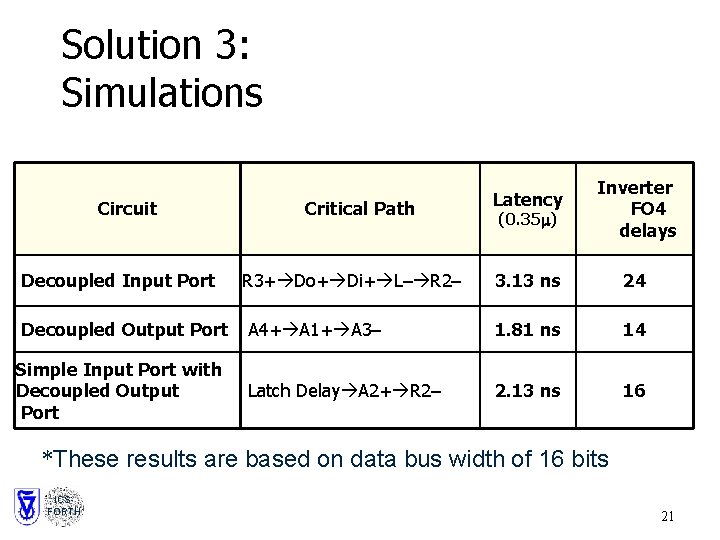

Solution 3: Simulations Circuit Decoupled Input Port Critical Path R 3+ Do+ Di+ L– R 2– Latency (0. 35 m) Inverter FO 4 delays 3. 13 ns 24 Decoupled Output Port A 4+ A 1+ A 3– 1. 81 ns 14 Simple Input Port with Decoupled Output Port Latch Delay A 2+ R 2– 2. 13 ns 16 *These results are based on data bus width of 16 bits ICSFORTH 21

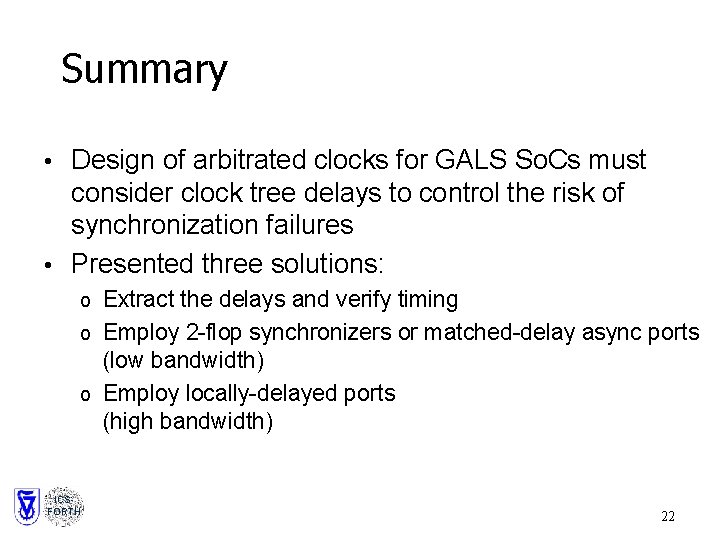

Summary • Design of arbitrated clocks for GALS So. Cs must consider clock tree delays to control the risk of synchronization failures • Presented three solutions: o Extract the delays and verify timing o Employ 2 -flop synchronizers or matched-delay async ports (low bandwidth) o Employ locally-delayed ports (high bandwidth) ICSFORTH 22