Hazards Static and Dynamic hazards Design of hazard

- Slides: 22

� Hazards - Static and Dynamic hazards- Design of hazard free circuits. Elementary ideas of Clock skew, synchronizer failure and metastability. DSD January 18, 2022 2

� John F Wakerly, Digital design principles & practices, Pearson Education. � Roth C. H. Jr. , Digital system Design using VHDL, PWS Pub. co. � Stephen Brown & Zvonko Vranesic, Fundamentals of Digital Logic with VHDL design, Tata Mc. Graw Hill. DSD January 18, 2022 3

� Steady state behavior of combinational logic circuits predicts a circuit’s output as a function of its inputs under the assumption that the inputs have been stable for a long time, relative to the delays in the circuit’s electronics. � Actual delay from an input change to the corresponding output change in a real logic circuit is nonzero and depends on many factors. DSD January 18, 2022 4

� Because of circuit delays, the transient behavior of a combinational logic circuit may differ from what is predicted by a steady state analysis. DSD January 18, 2022 5

�A circuit’s output may produce a short pulse, often called a glitch, at a time when steadystate analysis predicts that the output should not change. DSD January 18, 2022 6

�A hazard is said to exist when a circuit has the possibility of producing a glitch. � Whether or not the glitch actually occurs depends on the exact delays and other electrical characteristics of the circuit. DSD January 18, 2022 7

� Since such parameters are difficult to control in production circuits, a logical designer must be prepared to eliminate hazards even though a glitch may occur only under a worst -case combination of logical and electrical conditions. DSD January 18, 2022 8

� Static hazard. � Dynamic hazard. DSD January 18, 2022 9

�A static-1 -hazard is the possibility of a circuit’s output producing a ‘ 0’ glitch when we would expect the output to remain at a nice steady ‘ 1’ based on the static analysis of the circuit function. DSD January 18, 2022 10

�A static-1 -hazard is a pair of input combinations that: (a) differ in only one input variable and (b) both give a ‘ 1’ output; such that it is possible for a momentary ‘ 0’ output to occur during a transition in the differing input variable. DSD January 18, 2022 11

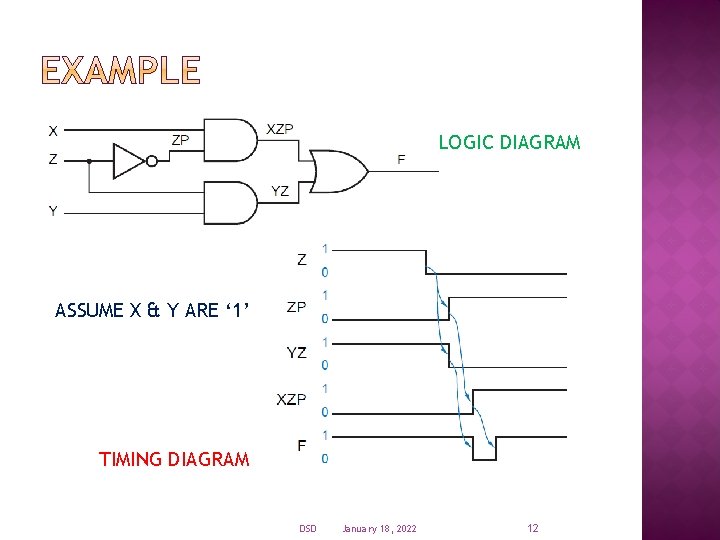

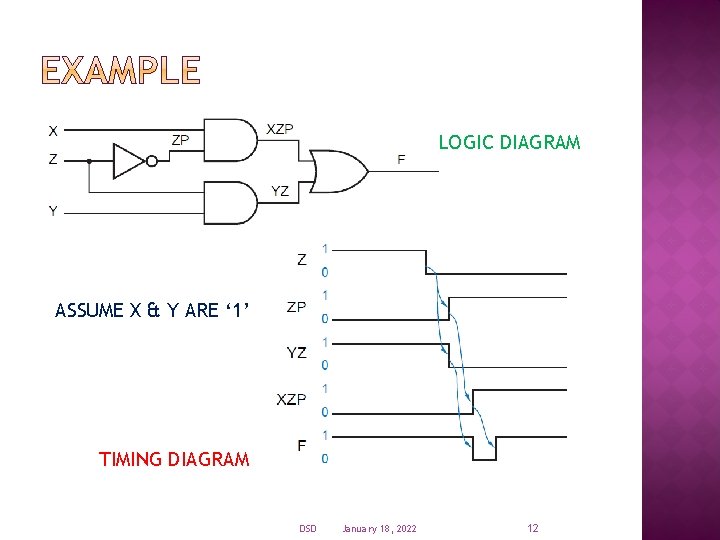

LOGIC DIAGRAM ASSUME X & Y ARE ‘ 1’ TIMING DIAGRAM DSD January 18, 2022 12

�A static-0 -hazard is the possibility of a glitch when we expect the circuit to have a steady ‘ 0’ output. DSD January 18, 2022 13

�A static-0 -hazard is a pair of input combinations that: (a) differ in only one input variable and (b) both give a ‘ 0’ output; such that it is possible for a momentary ‘ 1’ output to occur during a transition in the differing input variable. DSD January 18, 2022 14

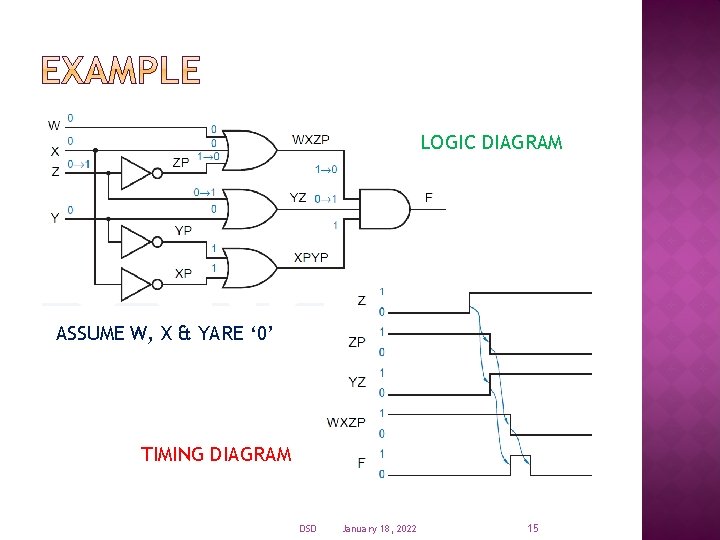

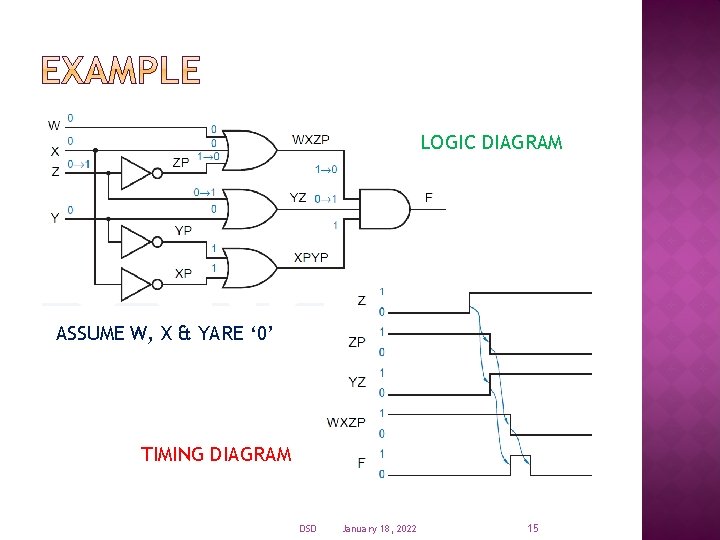

LOGIC DIAGRAM ASSUME W, X & YARE ‘ 0’ TIMING DIAGRAM DSD January 18, 2022 15

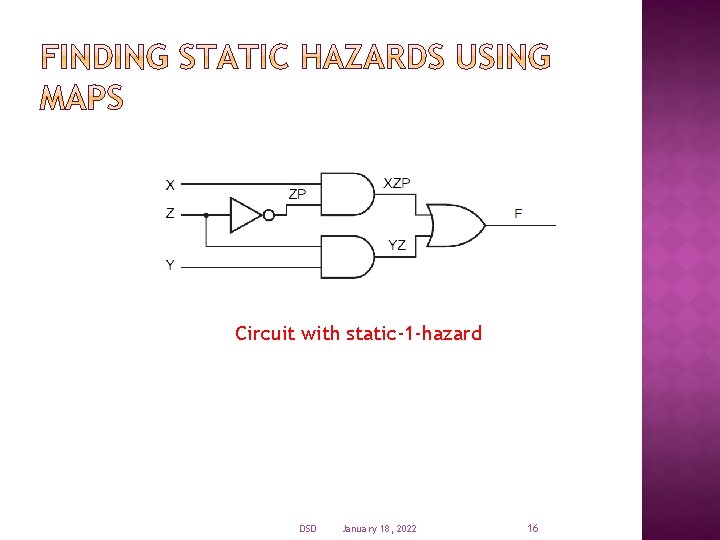

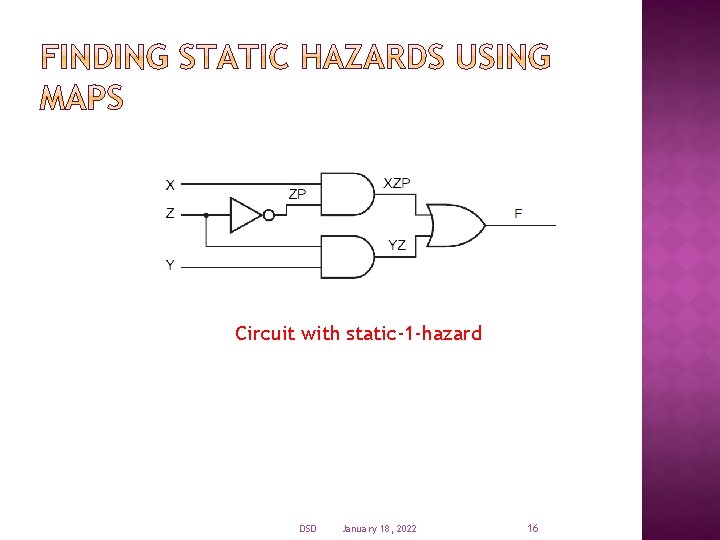

Circuit with static-1 -hazard DSD January 18, 2022 16

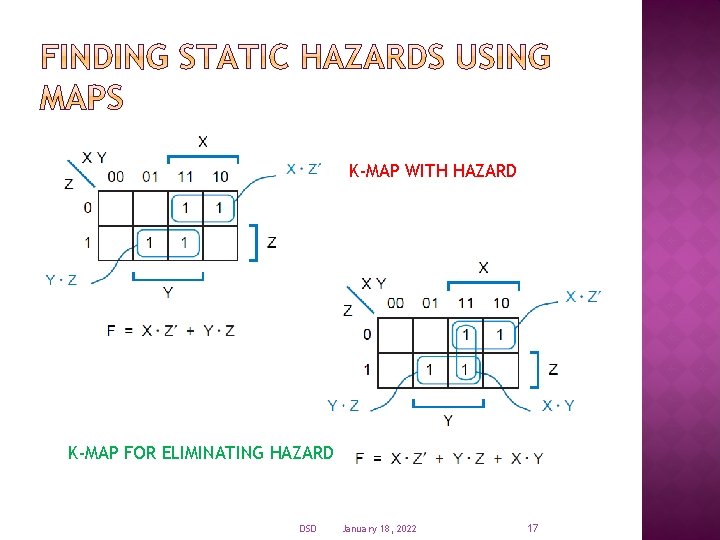

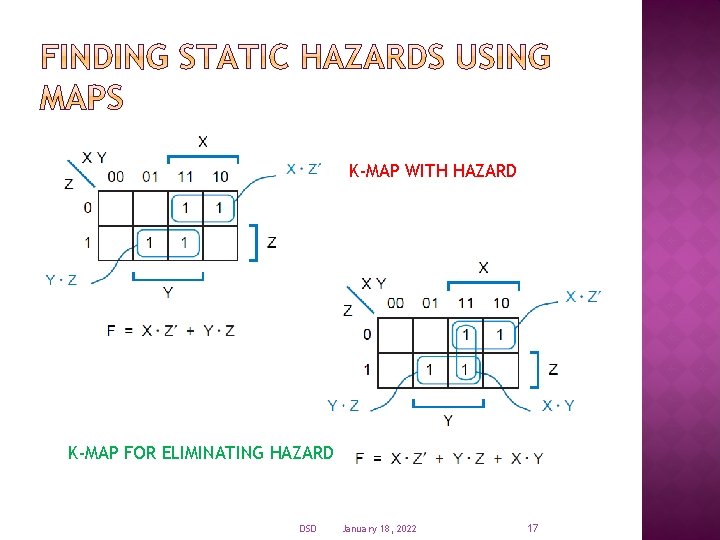

K-MAP WITH HAZARD K-MAP FOR ELIMINATING HAZARD DSD January 18, 2022 17

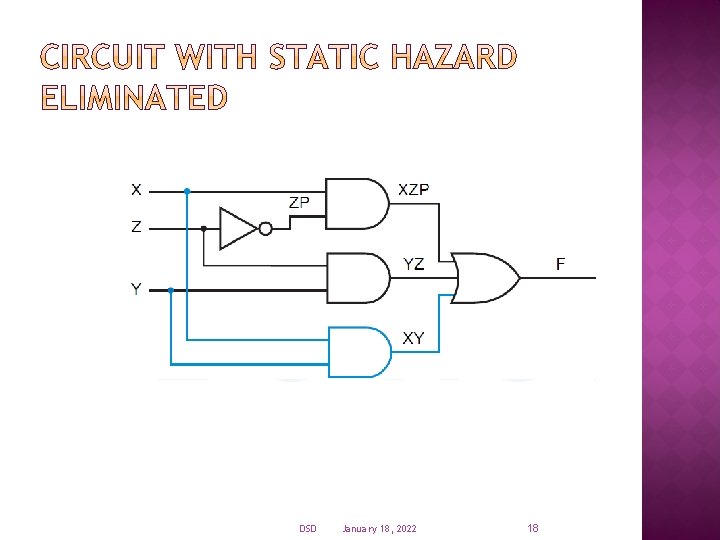

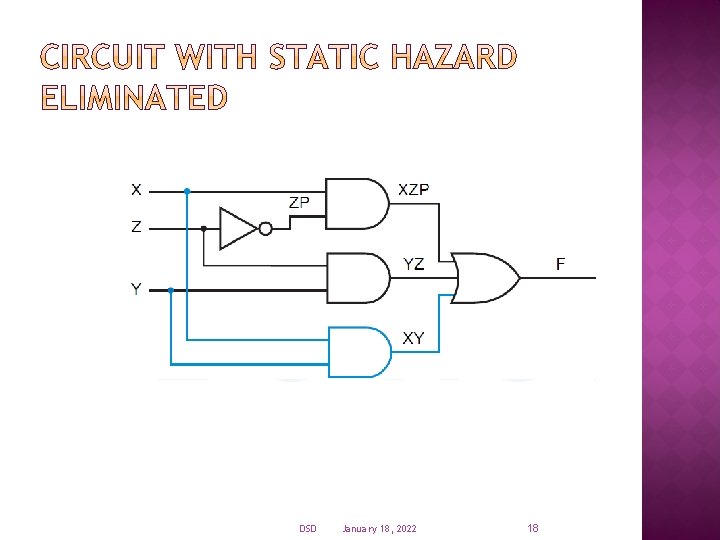

DSD January 18, 2022 18

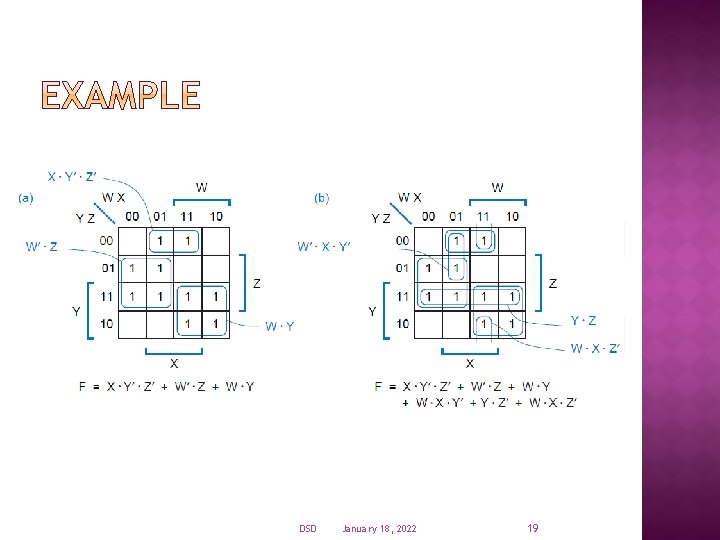

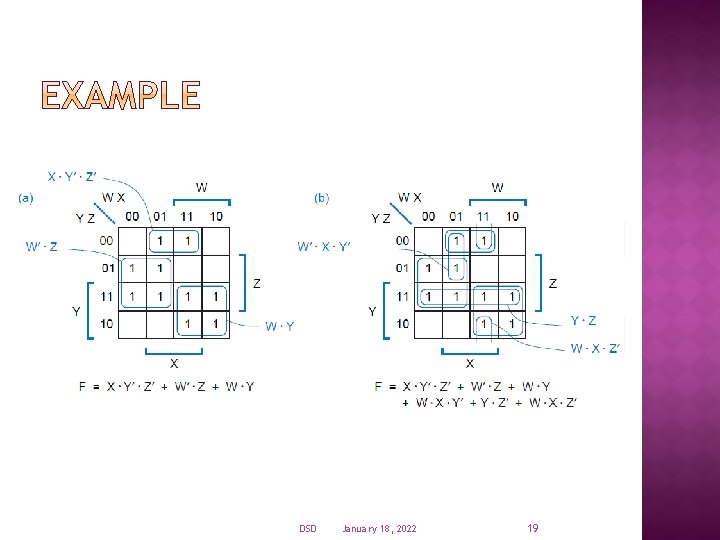

DSD January 18, 2022 19

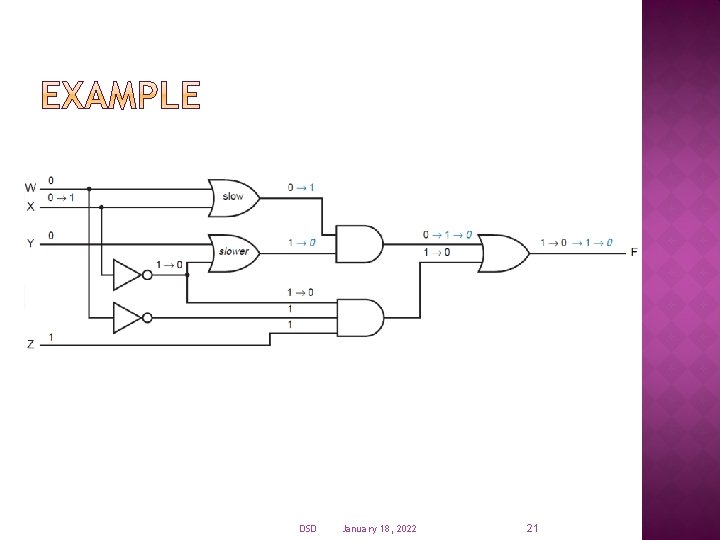

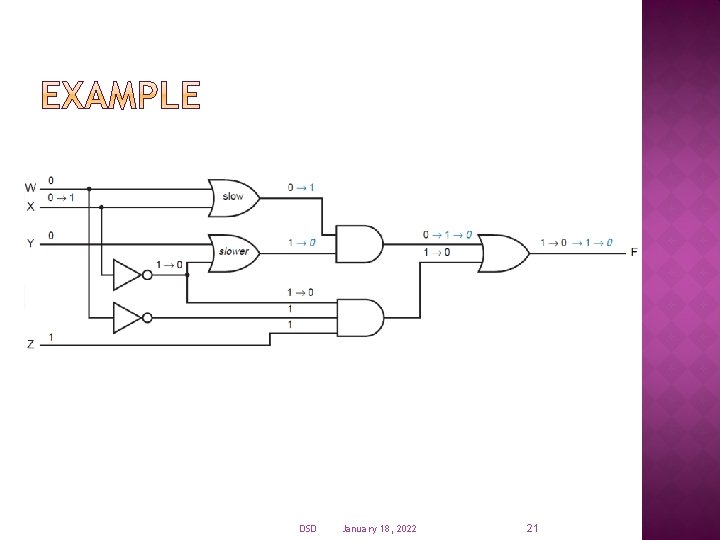

�A dynamic hazard is the possibility of an output changing more than once as the result of a single input transition. � Multiple output transitions can occur if there are multiple paths with different delays from the changing input to the changing output. DSD January 18, 2022 20

DSD January 18, 2022 21

DSD January 18, 2022 22