EE 319 K Introduction to Microcontrollers Lecture 7

- Slides: 7

EE 319 K Introduction to Microcontrollers Lecture 7: Finite State Machines 7 -

Finite State Machines - FSM Software abstraction q define a problem with a set of basic abstract principles q separate policies mechanisms Finite State Machine (FSM. ) q inputs, outputs, states, and state transitions q state graph defines relationships of inputs and outputs Ramesh Yerraballi The three advantages of this abstraction are 1. it can be faster to develop 2. it is easier to debug (prove correct) and 3. it is easier to change What is a state? q Description of current conditions What is a state graph? q Graphical interconnection between states What is a controller? q Software that inputs, outputs, changes state q Accesses the state graph 7 -2

Moore FSM q Output value depends only on the current state, and q Inputs affect the state transitions q Significance is being in a state q Input: when to change state q Output: how to be in that state Ramesh Yerraballi 7 -3

Mealy FSM q Output value depends on input(s) and current state q Inputs affect the state transitions q Significance is the state transition q Input: when to change state q Output: how to change state Ramesh Yerraballi 7 -4

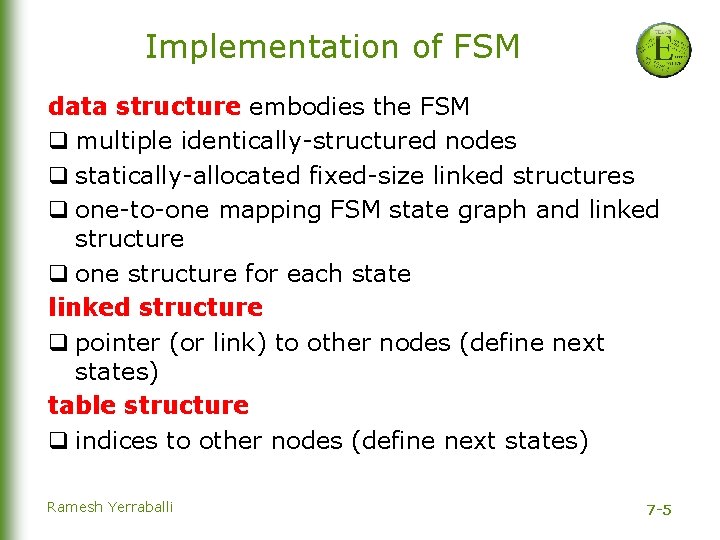

Implementation of FSM data structure embodies the FSM q multiple identically-structured nodes q statically-allocated fixed-size linked structures q one-to-one mapping FSM state graph and linked structure q one structure for each state linked structure q pointer (or link) to other nodes (define next states) table structure q indices to other nodes (define next states) Ramesh Yerraballi 7 -5

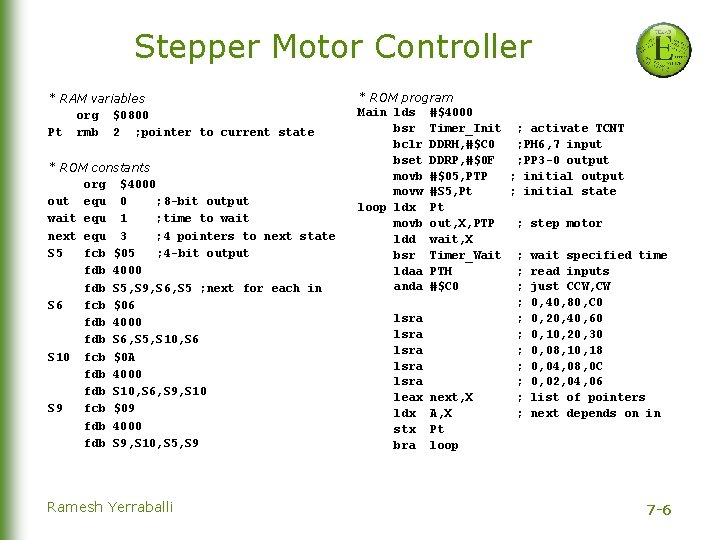

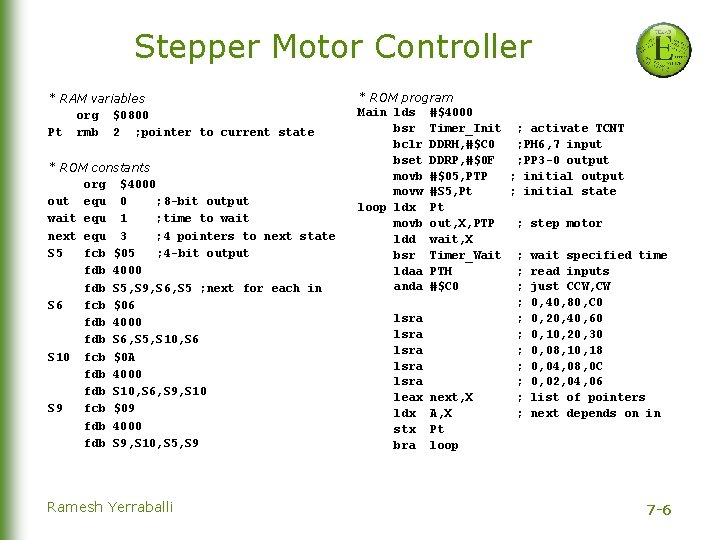

Stepper Motor Controller * RAM variables org $0800 Pt rmb 2 ; pointer to current state * ROM constants org $4000 out equ 0 ; 8 -bit output wait equ 1 ; time to wait next equ 3 ; 4 pointers to next state S 5 fcb $05 ; 4 -bit output fdb 4000 fdb S 5, S 9, S 6, S 5 ; next for each in S 6 fcb $06 fdb 4000 fdb S 6, S 5, S 10, S 6 S 10 fcb $0 A fdb 4000 fdb S 10, S 6, S 9, S 10 S 9 fcb $09 fdb 4000 fdb S 9, S 10, S 5, S 9 Ramesh Yerraballi * ROM program Main lds #$4000 bsr Timer_Init ; activate TCNT bclr DDRH, #$C 0 ; PH 6, 7 input bset DDRP, #$0 F ; PP 3 -0 output movb #$05, PTP ; initial output movw #S 5, Pt ; initial state loop ldx Pt movb out, X, PTP ; step motor ldd wait, X bsr Timer_Wait ; wait specified time ldaa PTH ; read inputs anda #$C 0 ; just CCW, CW ; 0, 40, 80, C 0 lsra ; 0, 20, 40, 60 lsra ; 0, 10, 20, 30 lsra ; 0, 08, 10, 18 lsra ; 0, 04, 08, 0 C lsra ; 0, 02, 04, 06 leax next, X ; list of pointers ldx A, X ; next depends on in stx Pt bra loop 7 -6

Stepper Motor FSM CCW: PH 6=1 & PH 7=0 CW: PH 6=0 & PH 7=1 Outputs connected to PP 3, PP 2, PP 1, PP 0 Control Stepper Motor For example, when in state S 9 the output is 1001 which is written to the pins PP 3(1), PP 2(0), PP 1(0) and PP 0(1) Ramesh Yerraballi 7 -7