Chapter 8 Synchronization Chapter 8 1 Synchronization refers

- Slides: 9

Chapter 8: Synchronization Chapter 8 1

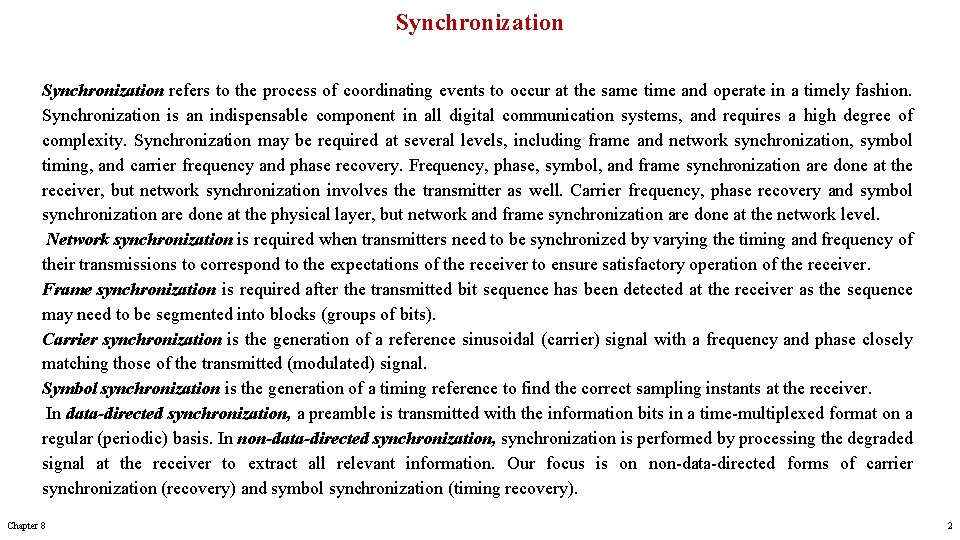

Synchronization refers to the process of coordinating events to occur at the same time and operate in a timely fashion. Synchronization is an indispensable component in all digital communication systems, and requires a high degree of complexity. Synchronization may be required at several levels, including frame and network synchronization, symbol timing, and carrier frequency and phase recovery. Frequency, phase, symbol, and frame synchronization are done at the receiver, but network synchronization involves the transmitter as well. Carrier frequency, phase recovery and symbol synchronization are done at the physical layer, but network and frame synchronization are done at the network level. Network synchronization is required when transmitters need to be synchronized by varying the timing and frequency of their transmissions to correspond to the expectations of the receiver to ensure satisfactory operation of the receiver. Frame synchronization is required after the transmitted bit sequence has been detected at the receiver as the sequence may need to be segmented into blocks (groups of bits). Carrier synchronization is the generation of a reference sinusoidal (carrier) signal with a frequency and phase closely matching those of the transmitted (modulated) signal. Symbol synchronization is the generation of a timing reference to find the correct sampling instants at the receiver. In data-directed synchronization, a preamble is transmitted with the information bits in a time-multiplexed format on a regular (periodic) basis. In non-data-directed synchronization, synchronization is performed by processing the degraded signal at the receiver to extract all relevant information. Our focus is on non-data-directed forms of carrier synchronization (recovery) and symbol synchronization (timing recovery). Chapter 8 2

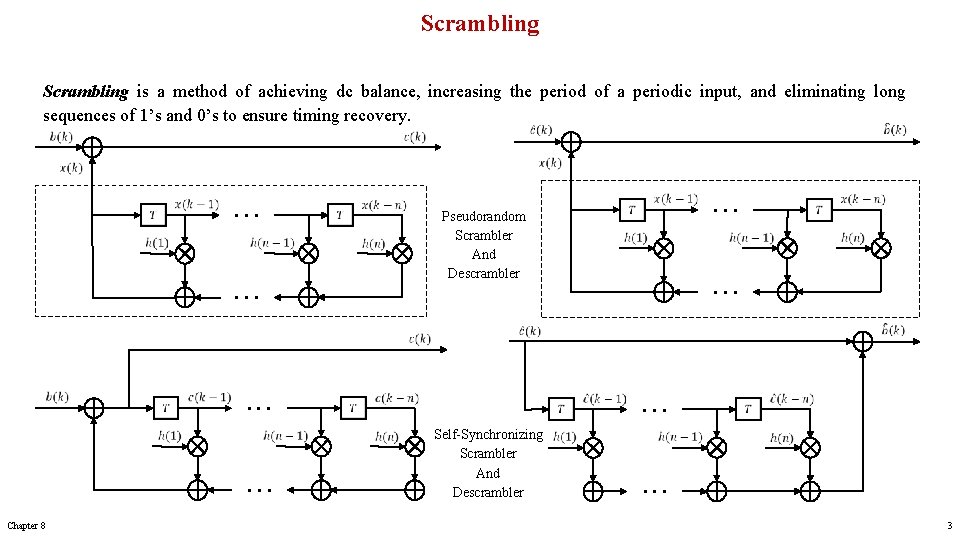

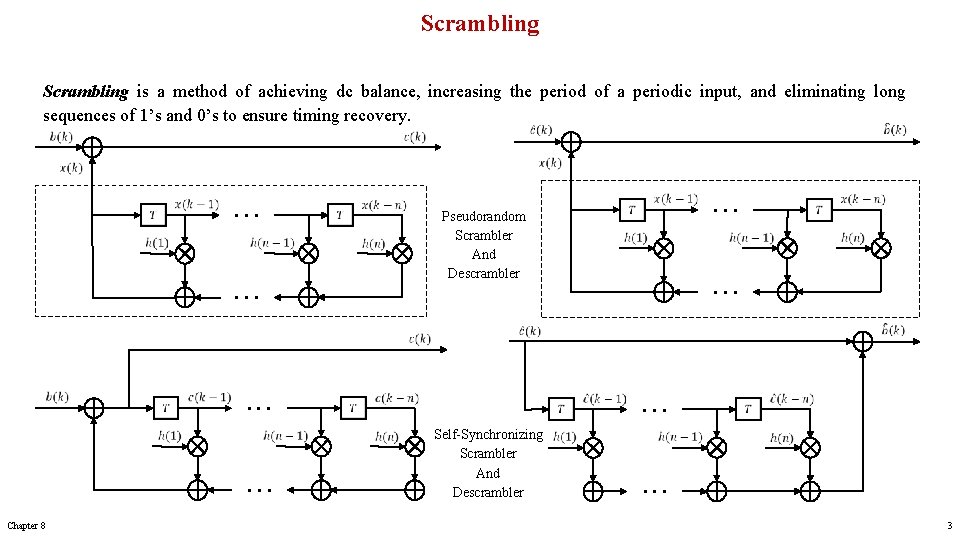

Scrambling is a method of achieving dc balance, increasing the period of a periodic input, and eliminating long sequences of 1’s and 0’s to ensure timing recovery. . . Chapter 8 . . . Pseudorandom Scrambler And Descrambler . . . Self-Synchronizing Scrambler And Descrambler . . . 3

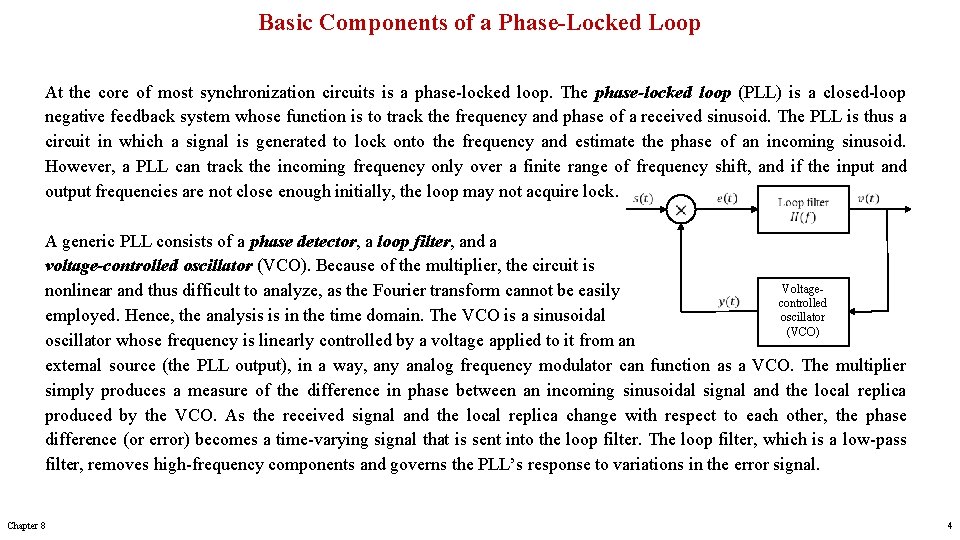

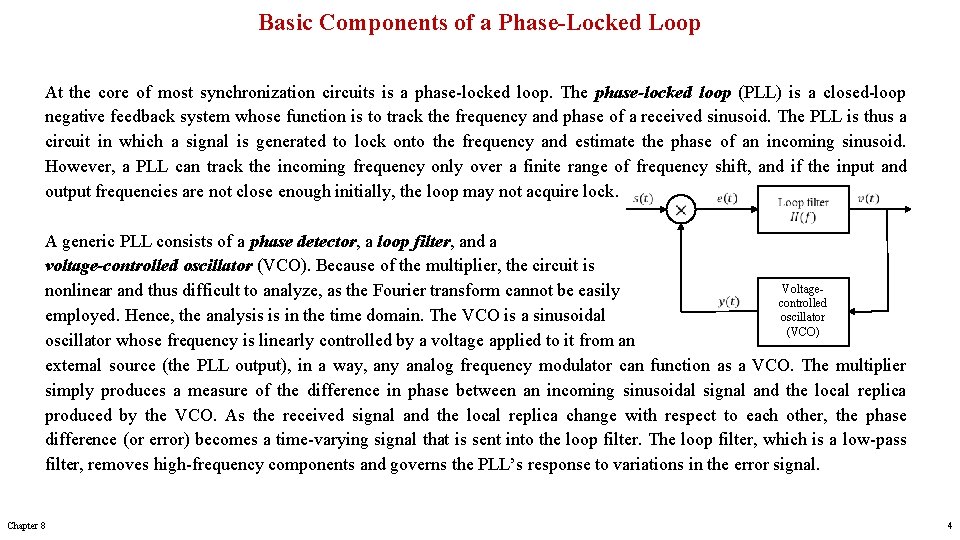

Basic Components of a Phase-Locked Loop At the core of most synchronization circuits is a phase-locked loop. The phase-locked loop (PLL) is a closed-loop negative feedback system whose function is to track the frequency and phase of a received sinusoid. The PLL is thus a circuit in which a signal is generated to lock onto the frequency and estimate the phase of an incoming sinusoid. However, a PLL can track the incoming frequency only over a finite range of frequency shift, and if the input and output frequencies are not close enough initially, the loop may not acquire lock. A generic PLL consists of a phase detector, a loop filter, and a voltage-controlled oscillator (VCO). Because of the multiplier, the circuit is Voltagenonlinear and thus difficult to analyze, as the Fourier transform cannot be easily controlled employed. Hence, the analysis is in the time domain. The VCO is a sinusoidal oscillator (VCO) oscillator whose frequency is linearly controlled by a voltage applied to it from an external source (the PLL output), in a way, any analog frequency modulator can function as a VCO. The multiplier simply produces a measure of the difference in phase between an incoming sinusoidal signal and the local replica produced by the VCO. As the received signal and the local replica change with respect to each other, the phase difference (or error) becomes a time-varying signal that is sent into the loop filter. The loop filter, which is a low-pass filter, removes high-frequency components and governs the PLL’s response to variations in the error signal. Chapter 8 4

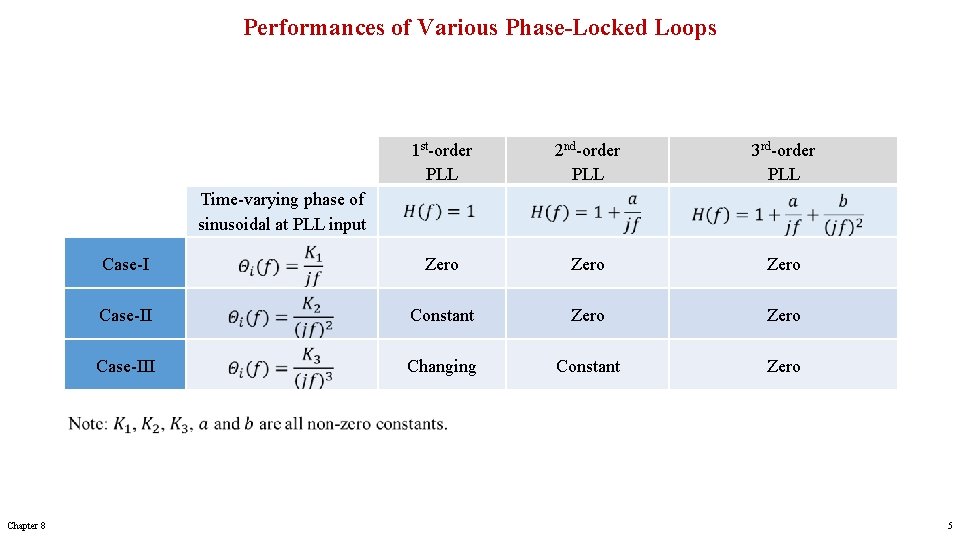

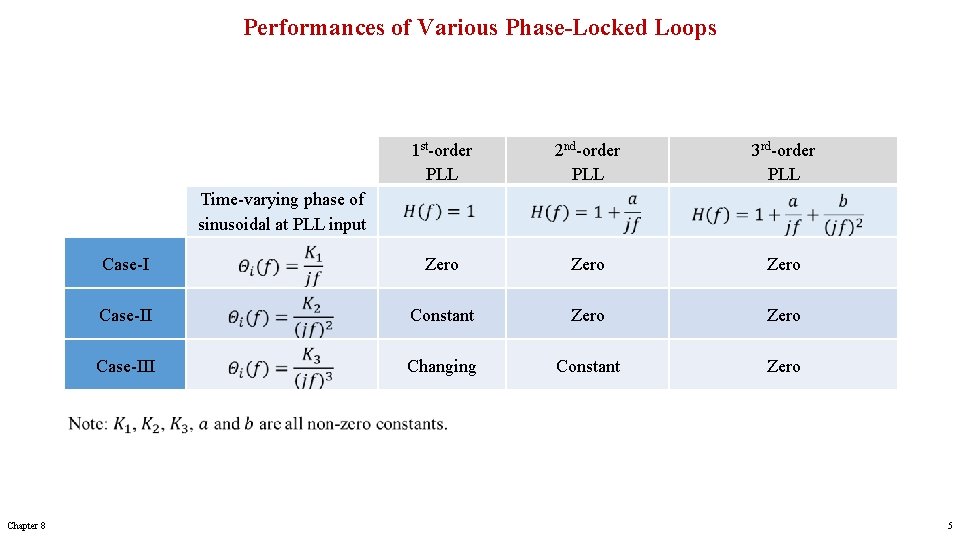

Performances of Various Phase-Locked Loops 1 st-order PLL 2 nd-order PLL 3 rd-order PLL Case-I Zero Case-II Constant Zero Case-III Changing Constant Zero Time-varying phase of sinusoidal at PLL input Chapter 8 5

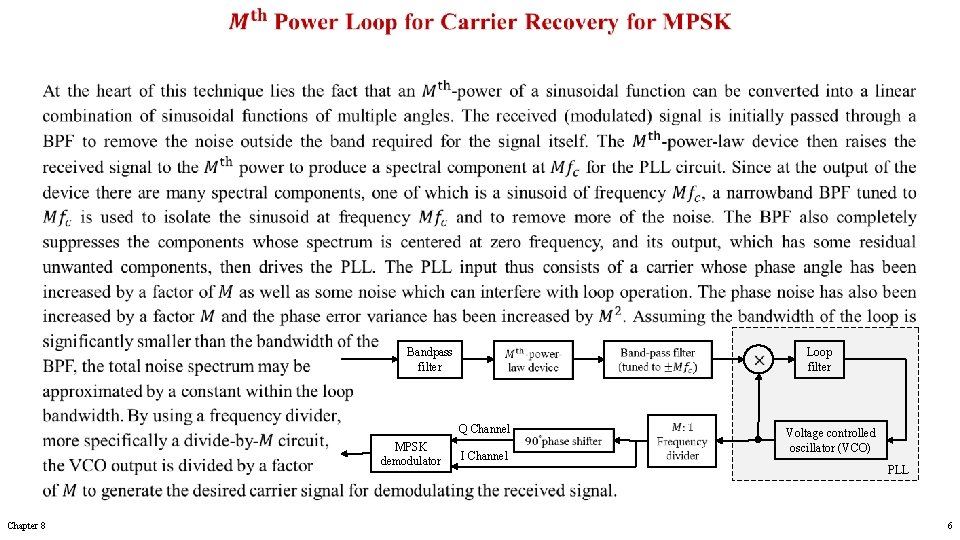

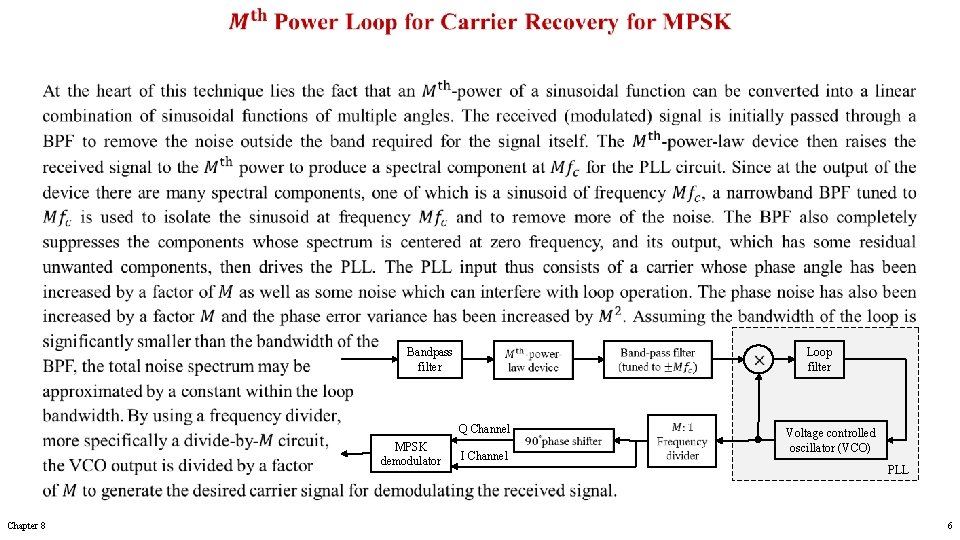

Loop filter Bandpass filter Q Channel MPSK demodulator Chapter 8 I Channel Voltage controlled oscillator (VCO) PLL 6

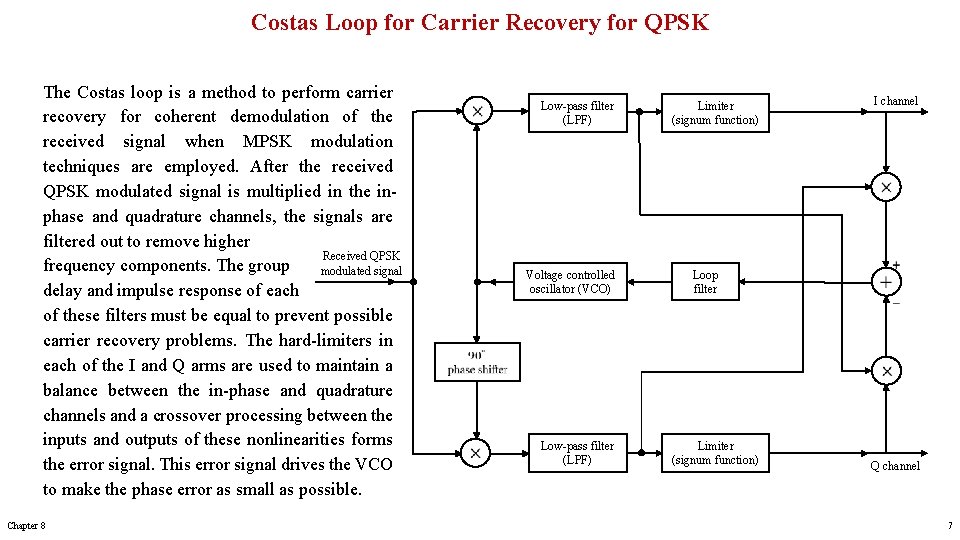

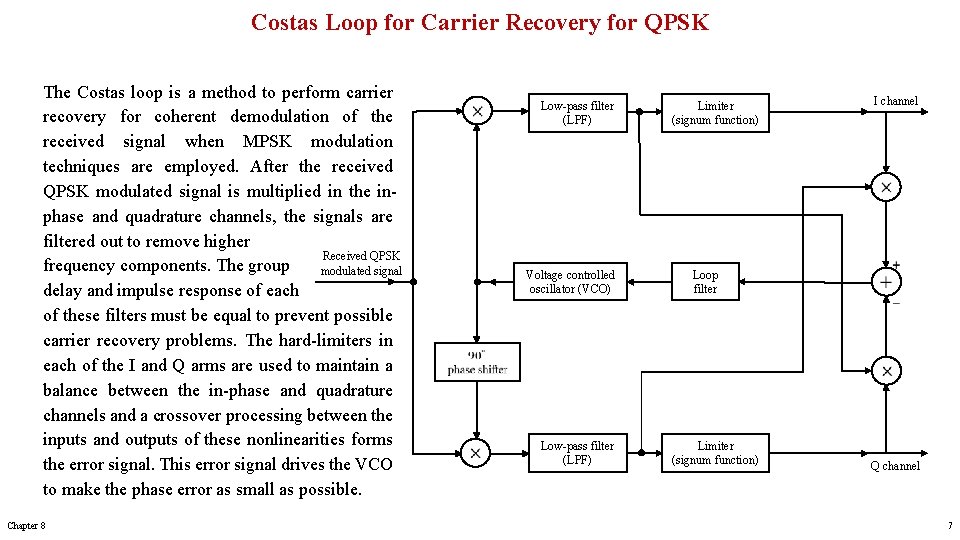

Costas Loop for Carrier Recovery for QPSK The Costas loop is a method to perform carrier recovery for coherent demodulation of the received signal when MPSK modulation techniques are employed. After the received QPSK modulated signal is multiplied in the inphase and quadrature channels, the signals are filtered out to remove higher Received QPSK frequency components. The group modulated signal delay and impulse response of each of these filters must be equal to prevent possible carrier recovery problems. The hard-limiters in each of the I and Q arms are used to maintain a balance between the in-phase and quadrature channels and a crossover processing between the inputs and outputs of these nonlinearities forms the error signal. This error signal drives the VCO to make the phase error as small as possible. Chapter 8 Low-pass filter (LPF) Voltage controlled oscillator (VCO) Low-pass filter (LPF) Limiter (signum function) I channel Loop filter Limiter (signum function) Q channel 7

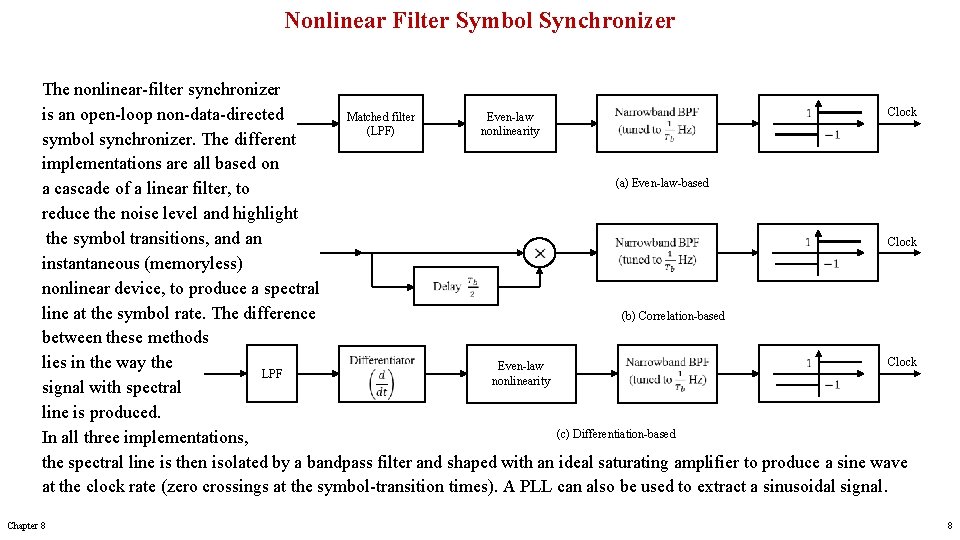

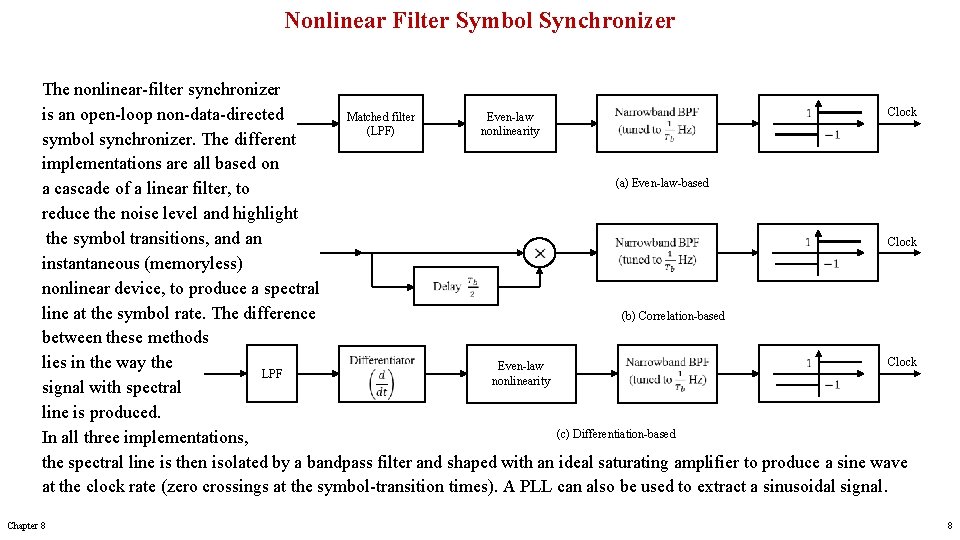

Nonlinear Filter Symbol Synchronizer The nonlinear-filter synchronizer Clock is an open-loop non-data-directed Matched filter Even-law (LPF) nonlinearity symbol synchronizer. The different implementations are all based on (a) Even-law-based a cascade of a linear filter, to reduce the noise level and highlight the symbol transitions, and an Clock instantaneous (memoryless) nonlinear device, to produce a spectral line at the symbol rate. The difference (b) Correlation-based between these methods Clock lies in the way the Even-law LPF nonlinearity signal with spectral line is produced. (c) Differentiation-based In all three implementations, the spectral line is then isolated by a bandpass filter and shaped with an ideal saturating amplifier to produce a sine wave at the clock rate (zero crossings at the symbol-transition times). A PLL can also be used to extract a sinusoidal signal. Chapter 8 8

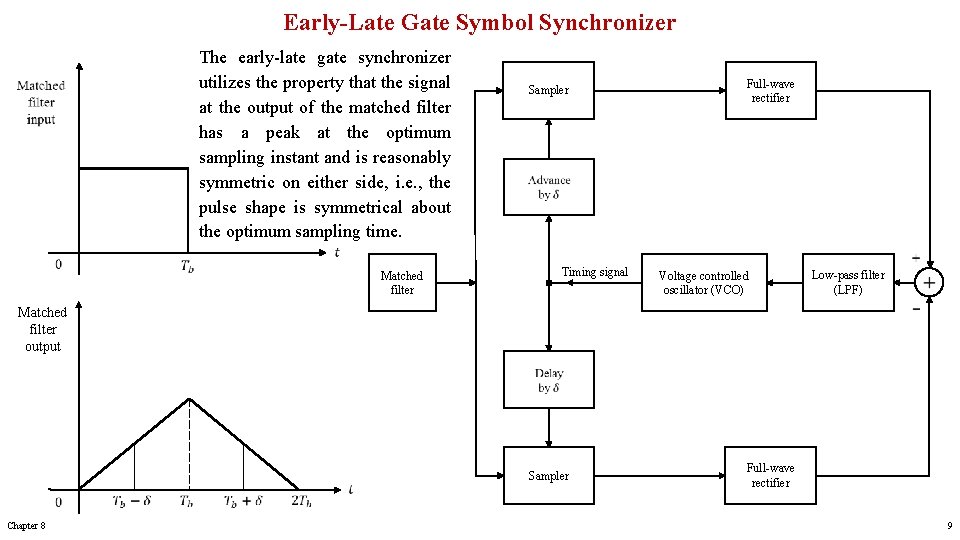

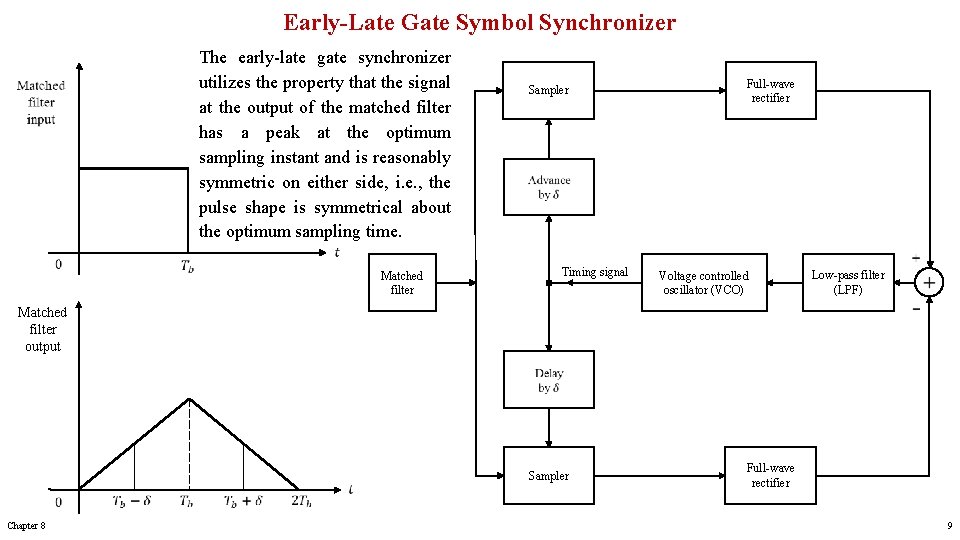

Early-Late Gate Symbol Synchronizer The early-late gate synchronizer utilizes the property that the signal at the output of the matched filter has a peak at the optimum sampling instant and is reasonably symmetric on either side, i. e. , the pulse shape is symmetrical about the optimum sampling time. Matched filter Sampler Timing signal Full-wave rectifier Voltage controlled oscillator (VCO) Low-pass filter (LPF) Matched filter output Sampler Chapter 8 Full-wave rectifier 9